# CIRCUTOR OF COMPUTER APPLICATIONS JOURNAL

November/December 1988 - - Vol. 1, No. 6 -

#### Circuit Cellar Ink

#### THE COMPUTER APPLICATIONS JOURNAL

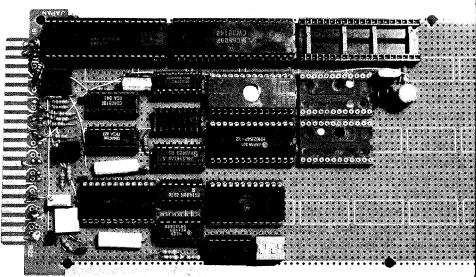

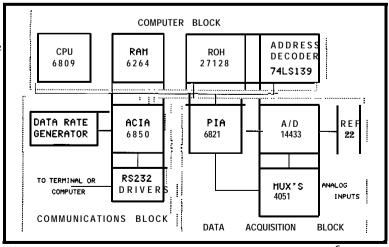

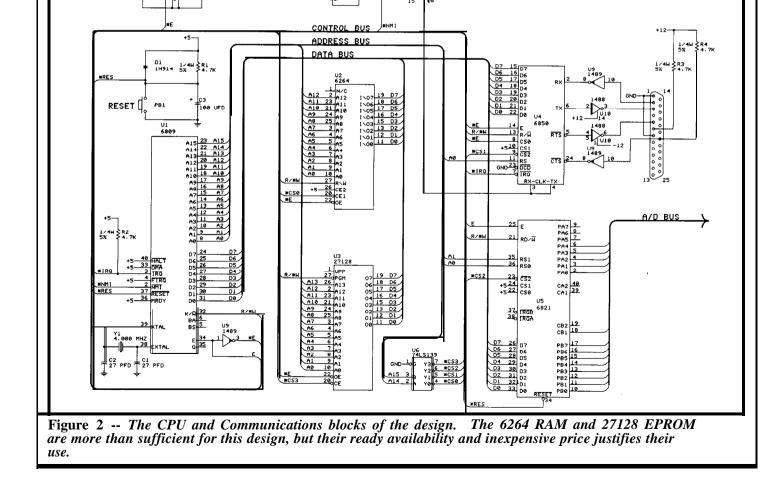

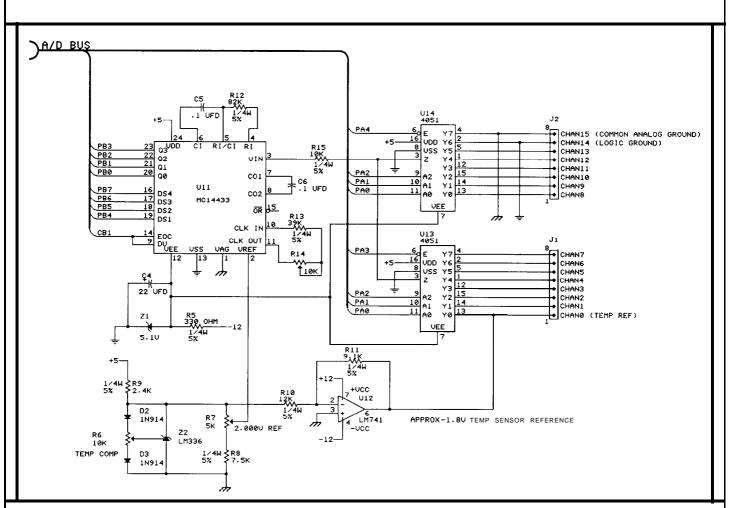

**45** Build a Remote Analog Data Logger -- Part 1 A Simple 6809-Based Data Acquisition System by R. W. Meister

Low component count and simple construction mark the hardware portion of this highly accurate **analog-to-**digital conversion system.

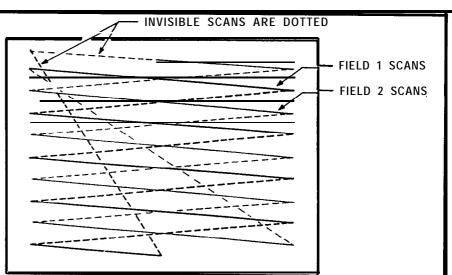

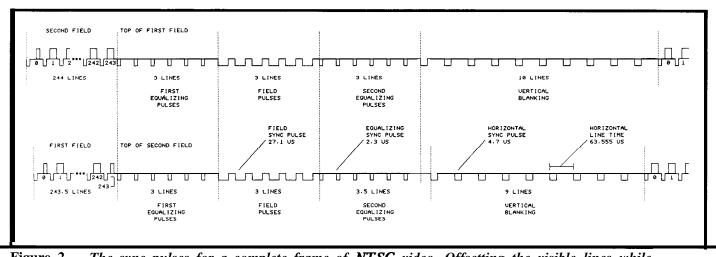

**36** ImageWise/PC -- The Digitizing Continues -- Part 1 Video Basics by Ed Nisley

A higher digitizing rate and more functionality introduced with the PC-bus (ISA) version of one of Steve Ciarcia's most popular projects-the **ImageWise** Video Digitizer.

Conducted by Ken Davidson

DDT-51 Revealed by Ed Nisley

A Gathering of Eagles

by Steve Ciarcia-

**Cover Illustration by Robert Tinney**

Circuit Cellar BBS - 24 **Hrs. 300/1200/2400** bps, **8** bits, no parity, 1 stop bit, 203-871-1988

The schematics provided in Circuit Cellar INK are drawn using Schema from Omation Inc. All **programs** and schematics in Circuit Cellar INK have been carefully reviewed to ensure that their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of the possible variation in the quality and condition of materials and workmanship of reader-resembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of readerassembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK.

CIRCUIT CELLAR INK (ISSN 0896-8985) is published bimonthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (203-875-2751). Second-class postage paid at Vernon, C1 and additional offices. One year (6 issues) charter subscription rate U.S.A. and possessions \$14.96, Canada \$17.96, all other countries \$26.96. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S bank. Direct subscription orders to Circuit Cellar INK Subscriptions, 12 Depot Sq. Peterborough, NH 03458-**9909** or call (203) 876-2199 POSTMASTER: Please send addrers changes to Circuit Cellar INK, Circulation Dept., 12 Depot Square, Peterborough, NH 03458-9909.

Entire contents copyright 1988 by Circuit **Cellar** Incorporated. All rights reserved. Reproductions of **this** publication in whole or in part without written consent from Circuit Cellar Inc. **is** prohibited.

1

Ctrl

# EDITOR'S I N K

## An Active and Growing Industry

n October, I went to a small computer show that had a lot of exciting displays and conference sessions. **BUSCON** '88 was held at the Javits Convention Center in New York, and featured exhibits from most of the big players in industrial control and general-purpose buses. There were companies exhibiting **Multibus I & II**, VME bus, STD and STE buses, **NuBus** and more, and it was good to see the rate of development for all of these architectures. Of course, being 1988, most of the talk centered on 16- and 32-bit buses, but there is still a lot of vitality in the mature 8-bit bus families.

If you read the general computer press, it's easy to get the impression that desktop platforms for word processing and spreadsheets are the only computers being built. The reality is that, while PCs and their kin are important, there's more happening in single-board and dedicated control applications than meets the eye. From machine vision and robotics to process control and data acquisition, we are part of a dynamic industry, an industry that develops many of the concepts that the desktop people pick up down the road. Right now I'm wondering whether I'll be as impressed by the products at COMDEX as I was by what I saw at **BUSCON**.

The products I saw ran from the inevitable (a PC-clone on a VME bus board) to the amazing (a Multibus II disk controller that uses an 80386 for its on-board intelligence). I talked to a lot of people, and you'll be seeing the results of some of those conversations in the months to come. One of the most important things coming your way will be the series on the various buses themselves. Engineers tend to get religious about their favorite bus, so we will try to give you the facts about the bus, its characteristics, advantages, limitations, and design goals, without getting stuck in the "My bus is better than your bus" debate.

#### into the Future of Circuit Cellar INK

In the world of publishing, there are large magazines that serve a diverse audience, and there are smaller magazines that speak to the particular needs of a special audience. Circuit Cellar INK is, thankfully, one of the latter. When we put together an issue of this magazine, we concentrate on how each article will appeal to one group of people: Those who design, build, and program working computer applications.

In the first year of publication, we have concentrated on articles that closely follow the format laid out by Steve Ciarcia in his popular "Ciarcia's Circuit Cellar" series in BYTE Magazine. Looking ahead to year number two, we will still have buildable application projects at our core, but we will be adding articles that we believe will help you broaden your applications horizons and deepen your understanding of current technology.

Starting in Issue 7, we will have some "software only" articles. The first will show you how to write a real-time operating system for a single-board computer. Later in 1989, we are planning to begin tutorial articles on various bus designs and the numerous serial communications standards. We will also have articles describing important new processors and controllers as they are introduced. The common thread through all of these articles will be information aimed at letting you take what you read and apply it to your applications. This has been a great year for Circuit Cellar INK. We've grown from a first issue that started life as a

This has been a great year for Circuit Cellar INK. We've grown from a first issue that started life as a newsletter to a magazine that is rapidly winning respect throughout the industry as the source for honest, genuine computer applications information. Since I came on board in late July, I have heard a lot of you tell me how glad you are that there is a Circuit Cellar INK, and I've gotten good suggestions on what you want to see in "your" magazine. We depend on your direct input for ideas and inspiration.

Take a minute and drop me a line or give me a call. I really want to hear from you.

Curtis Franklin, Jr. *Editor-in-Chief*

3

СМ

Κ

Ν

READER'S |

Letters to the Editor

[Editor's Note: A few weeks ago we asked folks on the Circuit Cellar BBS to tell us what they would like to see in upcoming issues of Circuit Cellar INK. Here are a few of their answers.]

Regarding articles on kit building, I have built many projects from kits, primarily Heath and CCI. I am not interested in things along the lines of "Building the Heathkit Something-or-other." I would be interested in articles that tell how to take a commercially available kit and modify it to do something else or that shows how it works. I subscribed to the Heathkit "Kit Builders Journal\*' for a while in the hope that it might contain some inside info from Heath. Sadly, it never appeared to have much in the way of technical articles. Short pieces on kits that are available from obscure manufacturers would be valuable (such as the PT-68K from Peripheral Technology). I will always be interested in projects that offer some form of kit for those of us that do not have the time or equipment to build from scratch.

Articles that I would like to see include:

- D/A for the BCC bus

- Motion control -- Stepper and servo motors

- Optical Encoders -- Feedback for motion control

- Software for data acquisition and control (Z-Transforms boggle my mind)

- □ How to use **RS-422/485** (SN75176 Transceiver)

- Building a logic analyzer (with parts sources)

- Applications ideas (like ROVER)

I enjoy reading Circuit Cellar INK and realize that not every article will interest me. I hope that INK will get ads from companies that can furnish the **hard-to**find parts. I think that this type of advertising will help ensure the long-term survival of INK.

William Giles

Being an amateur kit builder, I would like very much to see some articles about kit building. I realize that most of INK's readers are more advanced than I am, but I really need to know more about what I am doing. I would also like to see some product reviews, such as EPROM programmers and test equipment. As far as what type of projects I'd like to see, almost anything goes! Although I don't build every project, I have on many occasions taken part of the project and incorporated it into other things. To be honest, I read INK to learn about electronics. I'll be going back to college soon and hopefully by 1993 I'll have a BSEE degree. Until then, INK is my teacher.

#### **Brian Joseph**

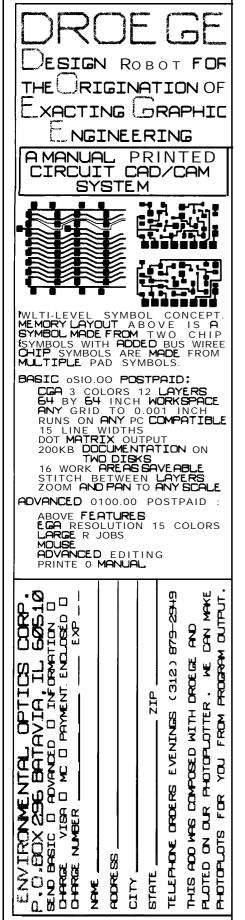

I would very much like to see stuff on design and fabrication tools. My company has spent several thousand dollars on PCB-CAD tools for the PC to find that most of them are junk. The industry trade magazines usually just republish press releases and so are of no use. What would be really useful would be an examination of design tools available to the serious experimenter/small company. I seem to see either articles about >\$100,000 systems or rehashed press releases.

#### John Dearmond

I am interested in IEEE-488 (GPIB). I don't know much about it technically, that is, what it would take to build a project from scratch for PC-compatibles. [I would like to use it as] a skeleton for managing multiple processes (e.g., an optical reader controlled from the PC console, with real-time counter updating, etc.). Thanks, and keep the Circuit Cellar **INKs** coming in the mail!

#### **Robert Schuh**

# If you're interested in Home Control talk to the World Leader!

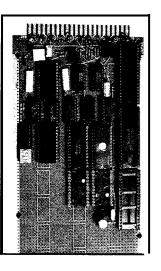

X-10 has been in the Home Control business since 1978 (formerly marketing under the brand name **BSR SYSTEM X-IO)**. We manufacture versions of the system under private labels as well as under the **X-10 POWERHOUSE** name. We have developed and manufactured O.E.M. versions of the system for many major corporations, and there are also compatible systems which use our protocol and transmit to **X-10** modules manufactured and supplied by us.

4

Our capabilities range from supplying "standard product" in any color with any name on it, to development of completely new systems which can take advantage of the large installed base of **X-70** modules.

The latest addition to the **X-10** line is the Power Line Interface, Model **#** PL513. This enables any O.E.M. product to couple an **X-IO** signal to the AC power line without having to bring 120V anywhere near the O.E.M. product. There will also be a 2-Way version available later this year which will allow an O.E.M. to transmit and receive **X-10** signals

The **X-IO POWERHOUSE** system is considered by many to be the "De Facto" standard for Power Line Carrier Transmission. So if you would like to add to your product - any product, the capability of controlling electrical devices over existing house wiring, or receiving signals from remote sensors, please call: Dave Rye at (201) 784-9700.

X-IO (USA) Inc., 185A LeGrand Ave., Northvale, NJ 07647

We've decided that it's high time we found out just what kind of hardware designers the Circuit Cellar INK readers are. To find out, and to give you a chance to work the kinks out of your mental muscles this winter, we're sponsoring the First Circuit Cellar INK Design Contest. This is your chance to see one of your designs published in the pages of Circuit Cellar INK without having to write an article. For this contest, the emphasis is on embedded controllers. You can design and build anything at all

For this contest, the emphasis is on embedded controllers. You can design and build anything at all for the contest, as long as it is based on a commercially available controller chip (8052, 8096, 68 11, 8742, etc.). The judges will be looking for utility, creativity, professionalism, and elegance in the designs.

To enter the contest, send for a complete set of rules and an official entry blank. Send a SASE to:

#### Circuit Cellar INK Design Contest P.O. Box 772 Vernon, CT 06066

All entries must be received by midnight on May 1, 1989. An individual may enter more than once, but each entry must be separate, and must be accompanied by a separate official entry form. Winners will be announced in the July/August issue of Circuit Cellar INK.

#### PRIZES"... PRIZES!!! PRIZES!!!

We couldn't hold a contest without prizes, now could we? First prize is worth \$500, Second prize is worth \$200, and Third prize is worth \$100. In addition, the judges may award Honorable Mention prizes worth \$50 and a 1-year subscription (or extension of an existing subscription) to Circuit Cellar INK.

#### TWO CONTESTS IN ONE!!!

In addition to the general awards mentioned above, we will award a set of prizes to the projects that feature the most cost-effective design. This criteria will give special consideration to those who use simple, low-cost controllers, such as the 803 1,6809, and Z8 in their designs. The prizes for the Most Cost-effective category are exactly the same as those for the general category.

1. All designs submitted must be the property of the person submitting them.

2. Each entry must consist of an Official Entry Form, complete legible schematics for the project, complete documentation for the project, and three (3) photographs of the completed project. All schematics, documentation, and photographs become the property of Circuit Cellar INK and cannot be returned. The actual design and the project itself remain the property of the person submitting them.

3. If your entry is chosen as a finalist, you will ship the completed project to Circuit Cellar INK, where it will be examined, verified, and photographed before being returned to you. All responsibility for shipping and insurance while in transit are the entrant's.

4. A First Prize (\$500), Second Prize (\$200), and Third Prize (\$100) will be awarded in the Open Category and in the Cost-Effective Category. In addition, the Judges may award an unspecified number of Honorable Mention Prizes (\$50 and a l-year subscription to Circuit Cellar INK) if the quality of entries makes this necessary.

5. Judging will be on the basis of utility, creativity, professionalism, elegance, and any other criteria the judges may choose to apply. The decision of the judges will, in all cases, be deemed final.

6. Employees of Circuit Cellar INK and their immediate families are not eligible.

## **ROVER: Remotely Operated Video- based IElectronic Reconnaissance**

nd in the continuing saga of 'As the Garage Turns,' our hero can be found patiently watching out the front window as the last of the garage's foundation is poured ..."

It's true. Mr. Wright finally came to his senses and issued the proper permits. The garage is coming along nicely, thanks in part to ROVER.

It's time to talk about just what makes ROVER tick. But for those who may have missed the last issue of INK and the action-packed tale of how ROVER earned its keep, let me fill in some details.

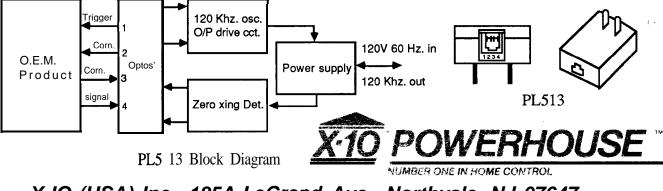

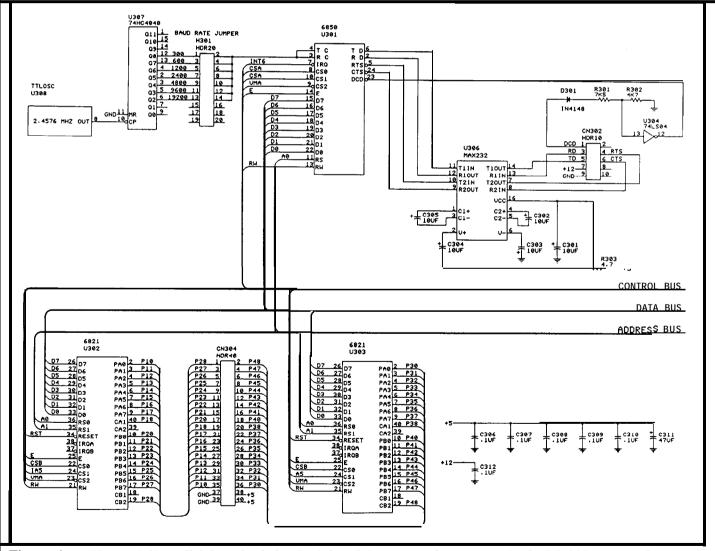

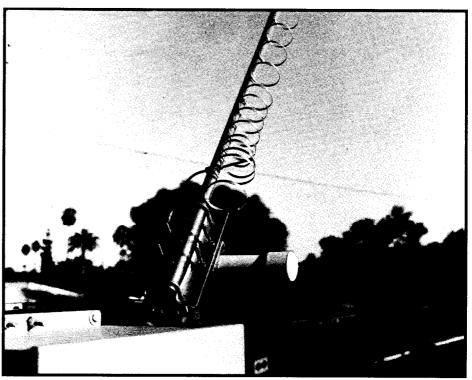

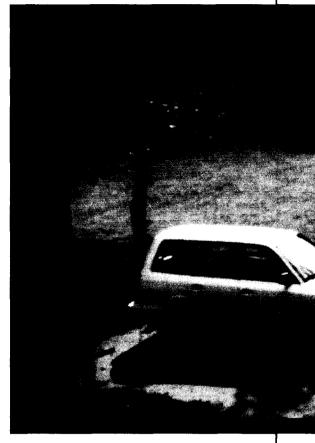

**ROVER** stands for Remotely Operated Video-based Electronic Reconnaissance, and consists of two parts: the digitizer/transmitter and the receiver/display. On the digitizer end is a video camera with a motorized zoom lens, mounted on a motorized pan and tilt mechanism. The video from the camera is digitized by an ImageWise serial video digitizer and is sent to a BCC180 computer/controller. Also under control of the BCC180 are all the motorized gadgets (the zoom lens and the pan and tilt). Finally, the BCC180 is connected to an optoisolated input board for reading alarm status and a 9600bps modem for talking to the outside world.

On the display end (which is built into a portable-computer case) is another **9600-bps** modem and BCC 180 computer. Connected to the BCC180 is an **ImageWise**

receiver/display board, capable of displaying a digitized 64-gray-level video image. When a switch is pressed on the the display unit. BCC180 directs the modem to place a phone call to the digitizer. Once connected, the digitizer sends video images from the camera to the receiver/display, where they are displayed on a video screen. Other switches on the display unit allow remote control of the zoom, pan, tilt, and other devices at the house. Status about the HCS and alarm systems sent from the house is displayed on lights on the receiver unit.

One of the nice parts about the system is that I can carry the display unit with me, call home from anywhere there is a telephone, and get instant video pictures of the whole house perimeter plus status information.

#### Off-the-shelf Boards

As I explained in part one, the vast majority of ROVER consists of off-the-shelf boards that can be readily purchased or built from plans

presented in Ciarcia's Circuit Cellar articles from BYTE Magazine. What little additional hardware was added can be classified as "bells and whistles."

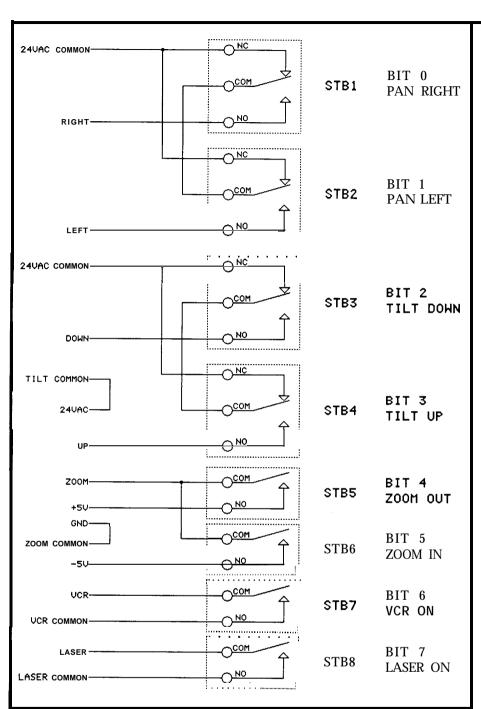

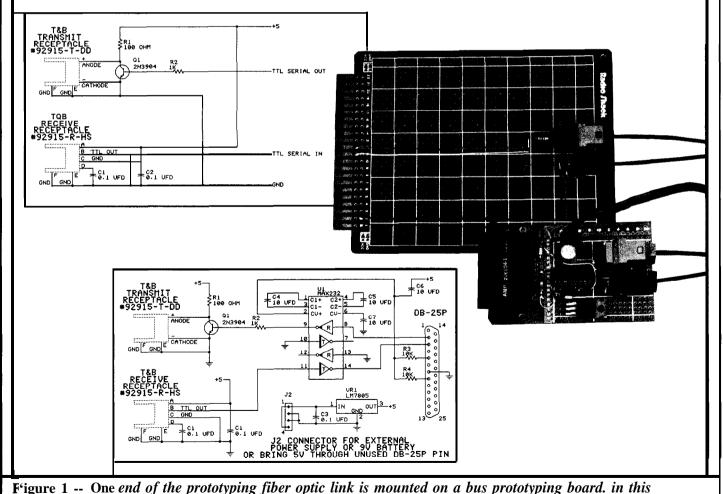

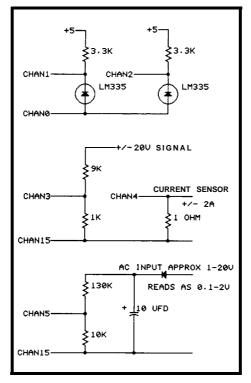

Figure 1 shows how the relays on the digitizer end are wired. Each of the eight relays on the

## Part 2 The Software

by Steve Ciarcia & Ken Davidson

BCC40R board is connected to one bit in an 8-bit byte. By sending a single byte to the BCC40R board, any or all of the relays on the board may be turned on or off.

The camera pan control has two separate wires for pan left and pan We could very easily just right. connect pan left to one relay and pan right to another relay, but what happens if a glitch in the software

> turns both relays on at once? Instead, the pan left and pan right wires are connected through a pair of relays wired such that both can't be activated at the same time. Panning left or right is still as easy as setting one bit or another, but if both bits are set at the same time, nothing will happen and no damage will be done.

> The same is true of the tilt controls. Tilting up or down is as easy as setting one of two bits, and if both bits become set at the same time, nothing will happen.

> Zooming is a bit easier since a single control wire is used, with the polarity of the voltage applied to that wire determining the direction of the zoom. Finally, two relays

are used for on/off control of a VCR and the laser.

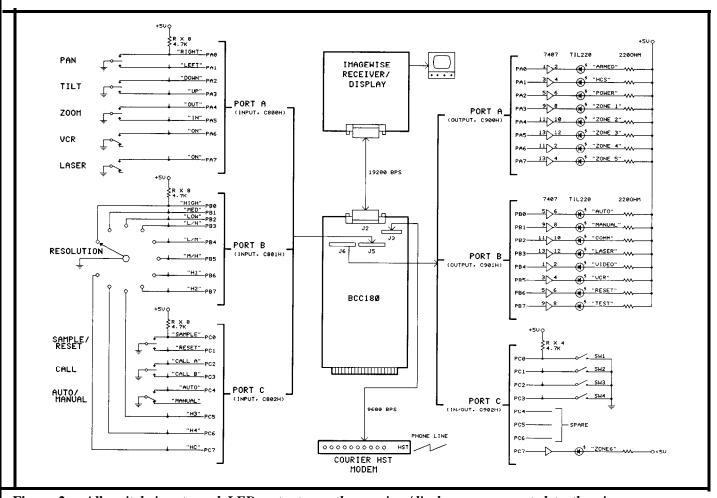

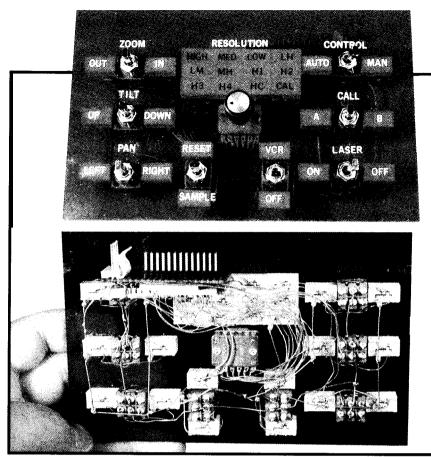

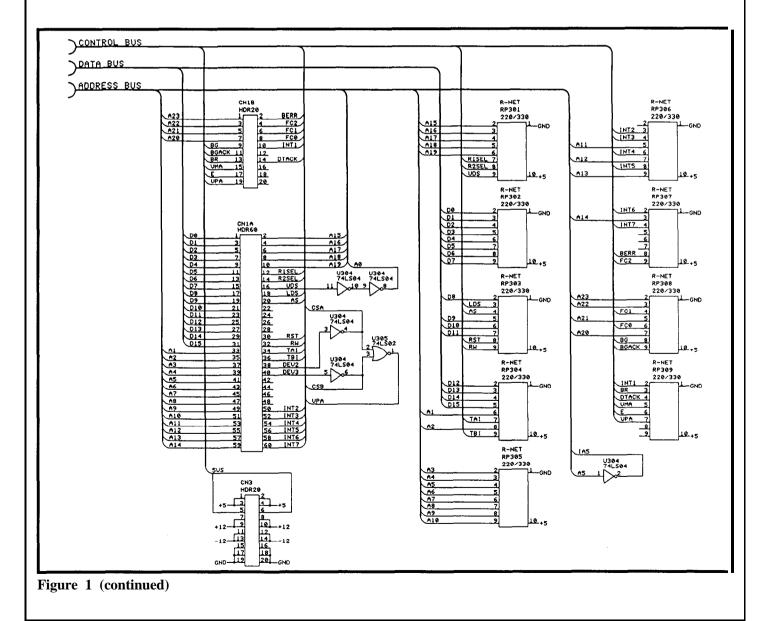

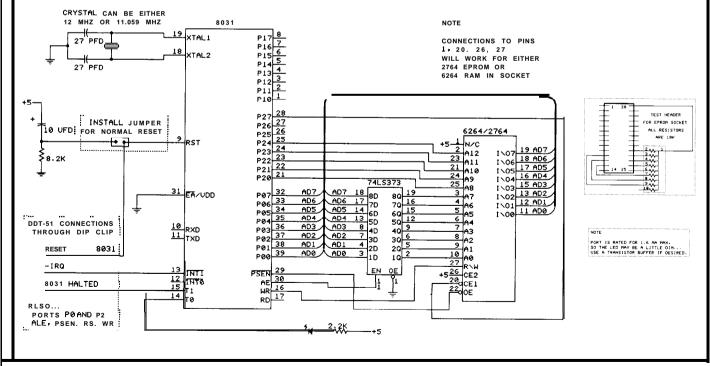

The extra circuitry added on the display end is more involved. Figure 2 shows how the switch inputs and LED outputs are wired to the BCC180's six parallel I/O ports. Since everything is in one box, protection from input transients is less important than on the rather vulnerable digitizing unit, so the switches are connected directly to the TTL inputs. Likewise, the LEDs are connected (through drivers) right to the TTL outputs. Active-low logic is used throughout. That is, when a switch on an input is open, a pull-up resistor keeps the input at a high level. When the switch is closed, the input is grounded, causing a low (active) level. Likewise, when an output bit is high, the LED connected to it is off. When the output goes low, the LED turns on.

If you want to build ROVER without doing all the extra hand wiring, the system can be built with a fixed camera (no pan, tilt, or zoom) and without status indicators using off-the-shelf devices and little else.

The real secret to making ROVER a reality, however, is the software.

Software for ROVER

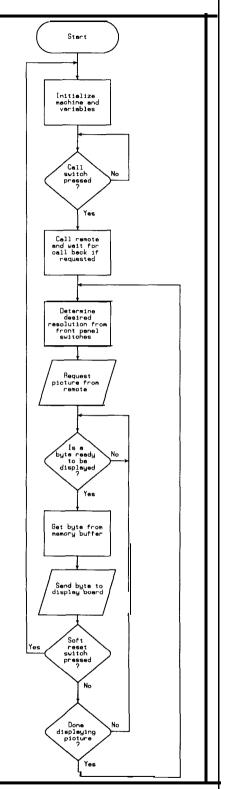

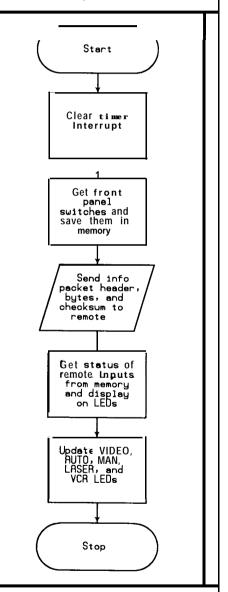

While small by today's programming standards (the total size of the assembled code for both ends is only about 2K), listing the source code for the ROVER software would take over 30 pages. Instead, we'll use flowcharts to show you where the code is going.

[Editor's Note: All software mentioned in this article is available from the Circuit Cellar BBS or on the Software Disk for this issue. For information on downloading and ordering, see page 35. ]

Photo 1 -- ROVER lets you make a single data call to receive images from. and control the autoiris/zoom/tilt/pan video camera (right) using the compact display unit (above).

Since off-the-shelf boards are used in the ROVER setup, very little prototype hardware design was needed (just the connections for the switches and LEDs). The functionality of the whole setup really centers around the software. Even though the BCC180 has a multitasking BASIC compiler available for it, the only way to write tight, efficient, real-time code is in assembly language, so all the ROVER control software is written in HD64180 (280) assembly language. For ease of explanation, the task is divided into two parts: the digitizer/transmitter end and the receiver/display end.

#### The Digitizer/Transmitter

At the digitizer end, the event sequence is very straightforward. Once the telephone connection is established (more on that later), the BCC180 receives a picture request from the modem. It passes that request on to the ImageWise digitizer board which digitizes the video signal coming from the camera on the roof. At that point, the BCC180 just passes the information straight through to the modem.

Why, then, do we need a host computer at all? Because I chose to incorporate two-way communication of status and control parameters in addition to one-way picture transmission in the design of ROVER, a computer is necessary to sift the data stream and channel it correctly. Every 200 milliseconds, the display unit sends two bytes containing front-panel switch information to the digitizer end. That information must be passed on to the relay output boards for use in moving the camera around, zooming in and out, and so on.

Also every 200 ms, the digitizer end reads its optoisolated inputs, which contain alarm status information, and sends them to the

Figure 1 -- Wiring for the eight relays of the BCC40R board. Since each is controlled by a single bit, all eight can be controlled with each byte sent to the board.

display end. The host computers in handle any real-time program-ROVER take care of adding and ming. Rather than waste processor stripping information to and from the serial stream so the ImageWise boards think they are talking directly to each other.

resources waiting for an event to happen, ROVER's processor relies heavily on interrupt processing to maximize efficiency.

Interrupts are the best way to

The HD64 180's on- board serial

Figure 2 -- All switch inputs and LED outputs on the receiver/display are connected to the six parallel ports on the **BCC180**.

ports support both receive and transmit interrupts. words, an interrupt will be generated when a character has been received, and an interrupt will be generated when the transmit buffer has emptied and is ready to send another character. We just have to be sure not to enable the transmit interrupt until we actually have a block of data to send. In the case of the digitizer end, we'll use the receive interrupt on the digitizer serial port and the transmit interrupt on the modem serial port.

We start by sending the picture request to the digitizer. We then enable the serial receive interrupt. When picture information starts coming in, the receive interrupt

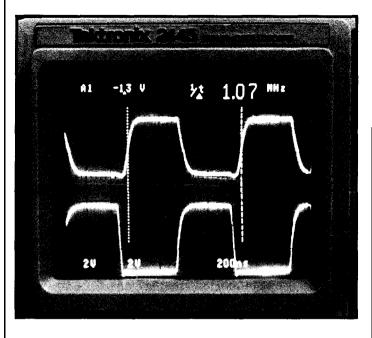

service routine is invoked once per In other character, and it saves the character to a buffer in memory. Communication with the digitizer is at 19200 bps while communication with the modem is at 9600 bps. As such, once the buffer begins to fill, no matter how fast characters are taken from it, it will always fill faster than it empties (until we stop filling it, of course). So once characters start to fill the buffer, we can enable the serial transmit interrupt to start emptying the buffer as fast as possible.

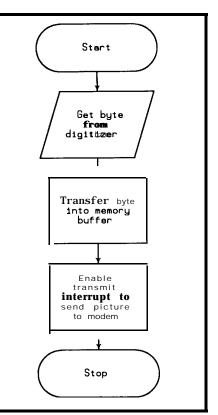

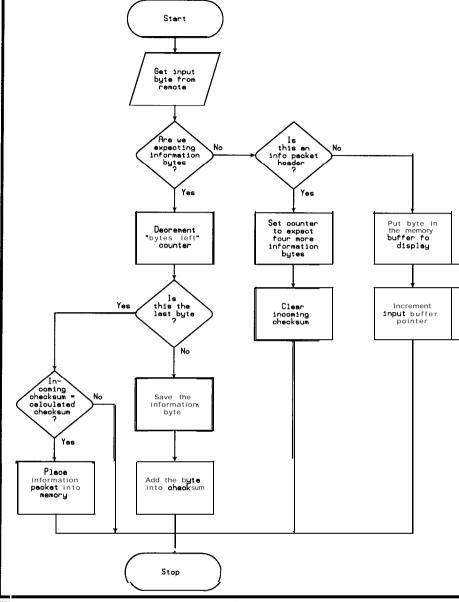

> The interrupt service routine for the serial receive interrupt (Figure 3a) takes care of enabling the transmit interrupt. interrupt service routine sees that it is sending the "end of picture" char

acter, it disables itself so no more transmit interrupts come in. You can see, then, that once the foreground code sends the picture request to the digitizer, transfer of the picture from input to buffer to output takes place automatically and completely in the background.

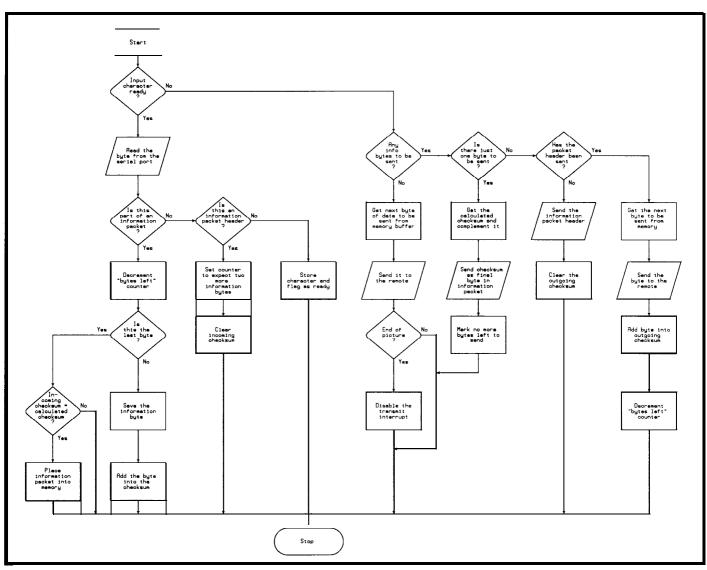

The next task to handle is the switch information coming in from the display end. We'll use the receive interrupt shown in Figure 3b on the modem serial port to handle this. The information packet begins with a special header byte. The next byte contains the on/off status of eight switches. When the transmit Finally, a two's complement checksum of the information (in this case just one byte) is received.

Should the checksum of the information byte disagree with the received checksum, all the information is thrown away (the last thing we need is a run-away pan or tilt!). Since the reception of the information packet is interrupt driven, it is again handled automatically and in the background.

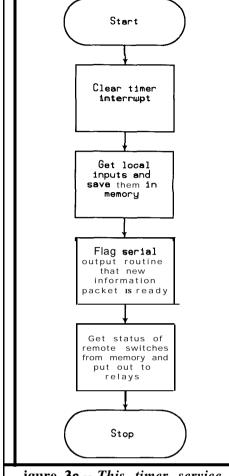

The final task is sending status information to the display. We'd like to send it every 200 ms, regardless of what else is going on. The HD64180 has two on-board programmable timers that can be set up to generate an interrupt on fixed intervals of time. Since the timers can't be slowed down enough to generate an interrupt every 200 ms, a 100-ms heartbeat interrupt is established, but information is only sent on every other interrupt. The timer service routine in Figure 3c reads the optoisolated inputs and formats them in the same way as the information packet described above. A header byte is sent, followed by the information byte, then the checksum.

We now have a conflict. The information packet and the digitized picture data both want to be sent out the same port at the same time. We rely on two different interrupt service routines for the information, but only one can talk to the port. To solve the dilemma, we set a flag in the timer interrupt routine which tells the serial transmit interrupt routine that there is an information packet to be sent. Interrupts are then reenabled. The next time a serial transmit interrupt is received, the service routine first checks to see if an information packet is ready. If so, it checks to see what portion must be sent next (header byte, information, or checksum) and sends the appropriate byte. After the last byte of the packet has been sent, the flag is cleared so transmission of picture data can resume. It turns out that sending the information packets every 200 ms only adds about 1.5% to the overall transmission time.

So what's left for the foreground

**Figure 3a** -- Most of the programming for ROVER involves generating and servicing interrupts. The routine for the serial receive interrupt takes care of enabling the transmit interrupt.

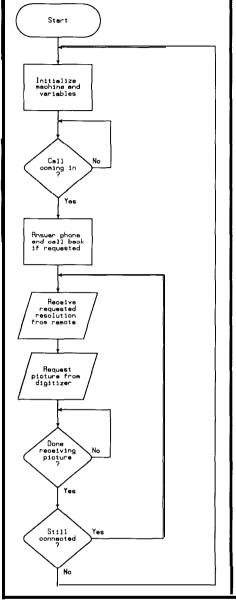

code diagrammed in Figure 3d to do? Since everything is interrupt driven, not much. After it sends out the picture request to the digitizer, the foreground code sits back and relaxes, checking the serial transmit interrupt enable bit to know when the picture transmission has finished. (Recall that the transmit interrupt is automatically disabled when the picture has been completely sent.) The code then loops back to the top and waits for another picture request from the modem.

#### The Receiver/Display

The activities on the digitizer and display ends are very similar. Once we determine the resolution

**Figure** 3b -- The interrupt service routine for the modem port handles information sent from the switches on the front panel of the display unit and also empties the local picture buffer.

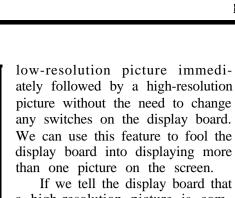

of the picture we want, a request is sent to the modem. Once data starts coming in, it is passed through to the ImageWise receiver/display **b**oard. Information packets are sent to the digitizer every 200 ms, and information packets received **are displayed** on the front-panel LEDs.

One of the basic premises of the digitizer end is different than the receiver end, though. On the digitizer end, the buffer is filled by the digitizer faster than it is emptied by the modem, so we can use interrupts to perform both filling and sent, a buffer input pointer and a emptying. On the display end, however, communication with the modem is at 9600 bps and communication with the display board is at 19200. In this configuration, the buffer can potentially be emptied faster than it is filled, so it doesn't make sense to use Likewise, the buffer output interrupts for both operations. Instead, we fill the buffer using an interrupt (serial receive interrupts are always easier to use than transmit interrupts) and empty the buffer in the foreground code.

After the picture request has been

buffer output pointer are set up. The buffer input pointer is the address within the buffer of the last byte received. When a byte is received, the pointer is incremented and the byte is placed in the buffer. pointer is the address of the next byte to be sent to the receiver/ display board. The foreground code is shown in Figure 4a (I'll describe the telephone functions in a moment).

Next, the serial receive inter-

igure 3c -- This timer service nutine reads the optoisolated puts and sends data to the dislay unit every 200 ms.

**pt** is enabled. The foreground de then starts comparing the uffer output pointer to the buffer **put** pointer. As long as the two re the same, there isn't any new nformation to be sent to the dislay board. Once a serial receive nterrupt has been received and a ew character is in the buffer; the nput pointer will be greater than he output pointer, so the foreround code picks up the new haracter, sends it to the display oard, and increments its pointer. 'his process is repeated until the end of picture" character is ensed. We then jump back to the op to request another picture.

Figure 3d -- The foreground code for the digitizer/transmitter does little more than send a picture request to the digitizer and then wait for the transmission to end.

Just like the code on the digitizer end, the interrupt service routine for the serial input (Figure 4b) checks for the header byte of an information packet. Upon sensing one, it strips the information from the incoming data stream before it can make it to the picture buffer and stores the information for use in updating the

Figure 4a -- The foreground code for the receiver/display is much busier than that for the digitizer/transmitter since it has to empty and keep track of the image input buffer.

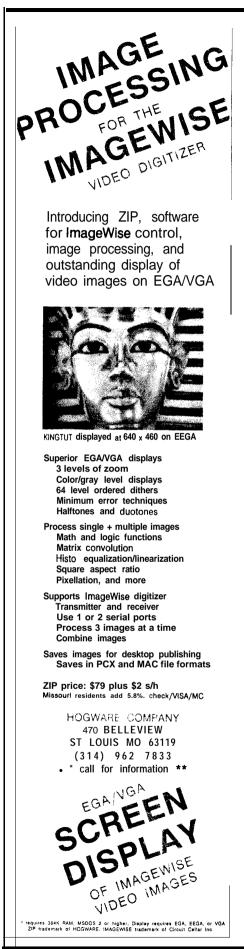

a high-resolution picture is coming, but instead send it a lowresolution picture, the picture will be displayed in the upper left corner of the screen, taking up just one sixteenth of the screen. If we tell the display board that a medium-resolution picture is coming, then send it a low-resolution picture, the picture will be displayed in the upper left quarter of the screen.

Such a technique yields several useful combinations of resolutions. We can, for instance, request ten consecutive low-resolution pictures and display them on a medium-resolution screen. Each picture takes about five seconds to send and is displayed in the upper left quarter of the screen. After ten pictures, we can request a highresolution picture and display it on a high-resolution screen. This takes about 50 seconds and fills the whole screen.

When we start requesting lowresolution pictures again, threefourths of the high-resolution picture remains on the screen until we request another high-resolution picture, and low-resolution pictures are constantly updated in one corner of the screen. Using this sequence, it's possible to monitor an area with relatively fast lowresolution pictures, then get an occasional high-resolution version of the scene.

There is a front-panel rotary switch on the ROVER receiver that receiver/display selects which resolution combination to use. A look-up table is used by the support code to determine how to handle each switch setting.

We also incorporated an auto-

**Figure 4b** -- The serial input routine for the receiver is similar to the transmitter routine shown in Figure 3a.

front-panel LEDs.

Also like the code on the digitizer end is the heartbeat timer interrupt used to send out information packets (Figure 4c). Since we don't have to worry about adding the information packet to any other outgoing data, the timer interrupt service routine can send the information to the serial port itself without having to flag another routine to do the operation for it. way, the host computer can display a

#### Multiple Display Resolutions

ROVER's display has the added burden of determining what resolution to request and how to display the resulting picture.

Beginning with version 1.2 of the ImageWise EPROM, the display board allows the host computer to tell it what resolution is coming down the line. That

**matic** mode and a manual mode. In the automatic mode, pictures are requested continuously and displayed in the requested resolution combination. In manual mode, once a picture has finished being scanned onto the display, no new pictures are requested until the "Sample" switch is pressed. At that time, a picture at the set resolution is requested and displayed.

#### The Telephone Connection

One thing not discussed yet is how the phone connection is established. Ken said that this task was almost as cumbersome as everything else in the project put together. I felt bad but explained that "it was the price of success."

The front-panel switches include center-off momentary-contact toggle switch labeled "Call A" and "Call B." When the switch is thrown to "Call A," the display unit tells the modem to pick up the phone, dial a number, and establish a connection with the remote digitizer unit. While this sounds easy on the surface, what happens when the remote doesn't answer, is busy, or there isn't any dial tone? In order to do the implementation correctly, all kinds of error control needs to be incorporated. In the present software, any of the above errors result in a system reset.

In order to accommodate more than one phone number, the camera movement switches are read at the same time as the "Call" switch is thrown. Using the Pan, Tilt, and Zoom switches, a total of seven phone numbers can be stored in memory.

The "Call **B**" switch invokes a slightly different sequence of events. In actual use, I make a connection from my office to the house and leave it in place for hours on end. We eventually realized that the phone line that I was using was billed on a per-minute basis, making **8-hour** phone calls very expensive (someone

down in finance gave me a call!). The phones at my house, on the other hand, are billed flat rate no matter how long a call lasts. When the "Call B" switch is thrown, the display unit places a call to the digitizer unit, sends it a call-back phone number, and hangs up. The digitizer immediately calls the receiver back at the number it was given. This way a short, lo-second

Figure 4c -- The timer interrupt for the receiver is even simpler than the routine shown in Figure 3c, since it doesn't have to add any additional information packets to the data stream.

Photo 2 -- The control panel of the receiver/display writ sends camera positioning digitizing commands to the digitizer/transmitter. and has status lights that are updated by the transmitter.

phone call can initiate the 8-hour connection and the connection will be billed at a flat rate.

#### An Open Door

That just about covers ROVER. You really have to see him in action to appreciate him. The reaction of most people when shown ROVER is "Neat!" There just isn't anything on the commercial market that does auite what ROVER does.

ROVER also opens the doors to some new project ideas. We still have that laser mounted on top of the camera, controlled by a switch on the display unit. Perhaps a laser-guided tracking and targeting system will be the next installment of the ROVER Series. The complete source code for ROVER is available on disk (see page 35) or can be downloaded from the Circuit Cellar BBS. For a reprint of the Image-Wise Serial Video Digitizer articles presented by Steve Ciarcia in May-June '87 BYTE, order DT/DR Reprint. Send \$3 for postage and handling.

Add \$10 for the two ImageWise assembly and user's manuals.

For a reprint of the BCC180 Multitasking Computer/Controller articles presented by Steve Ciarcia in Jan.-Mar. '88 BYTE, order BCC180 Reprint. Send \$4 for postage and handling.

Add \$6 for the BCC180 assembly and user's manual.

Send all manual and reprint requests (mail order only, please) to:

Circuit Cellar INK Reprints P.O. Box 772 Vernon, CT 06066

| • 30 day money back guarantee<br>• 1 year warranty on all products<br>• Toll-free technical support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Wirewrap prototype cards</b><br>All are FR4 epoxy glass laminate with gold-plated<br>edgecard fingers, plated holes and silkscreened<br>legends. +5V and ground planes. Mounting brackets<br>and complete documentation included.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| S-bit card <b>for XT \$27.95</b><br>All 62 bus pins are <b>labelled</b> on both sides of the card<br>to simplify wire wrapping and soldering.<br>JDR-PRI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8-bit w/decode for XT \$29.95<br>Decode support for a wide range of applications!<br>Use the decode and buffering circuitry as designed,<br>or modify it to suit your applicahon. Test points<br>and components are labeled on both sides. I<br>JOR-PR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16-bit card for A J     \$34.95       Programmable Logic Devices speed up card design process. Pre-wired buffers, address decoding.     JDR-PR10       JDR-PR10     JDR-PR10-PK Parts Kit (Req. for decoding)     \$12.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>16-bit for PS/2 \$49.95</b><br>I/O decoding for Microchannel! With the optional<br>parts kit, this card has the decode circuitry to design<br>Microchannel interface cards. Logic supports soft-<br>ware programmability. card enable/disable&more<br>• software programmable I/O address<br>• programmable I/O address<br>• programmable I/O address<br>• programmable I/O channel ready delay<br>IDR-PR16<br>IDR-PR16 Sents Kit (decode circuitry) \$15.95<br>IDR (16 K H 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| JDR-16V       16-bit Prototype card w/Video       \$33.95         (Extended edge connectors for video applications) <b>32-bit card for PS/2 \$69.95</b> Microchannel compatible! Full-length card routes power and ground signals throughout the board for quiet operationideal for use in a high speed bus.       With power & bypass capacitor installation sites.         JDR-PR32 <b>*</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Order toll free 800-538-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| JDR'S extender cards<br>For prototype debugging, testing & trouble-shooting.<br>FR4 epoxy glass laminate PC board. Ground plane<br>for quiet operation. Gold plated edge fingers, labelled<br>trace lines. Solder-masked to prevent shorting.<br>EXT-8088 For XT System \$229.95<br>EXT-80286 For AT System \$239.95<br>EXT-122 32-bit card for Microchannel \$99.95<br>EXT-16 16-bit card for Microchannel \$69.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Image: Non-Fride         Image: Non-Fride         Image: Non-Fride         Image: Non-Fride           10 KNOWLES DRIVE. LOS GATOS. CA 95030         Image: Non-Fride         Image: Non- |

| Minimum order \$10. Add \$2.50 shoping hundling for UPS ground<br>\$3.50 UPS are. Orders over 11b and foreign orders may require<br>additional stopping charges - presection contact our stalls. Dept. CA<br>residents include applicable sales tax. Prices subject to change<br>without notice. We are not responsible to substitute manufacture<br>Reserve the right to limit auxihities and to substitute manufacture<br>All merchandise subject to prior sales. A full copy of our terms is<br>available wator request. Tens pictured may only be representative<br>COPRIGHT 1988 JDR MicRoDeViceS Continental us and canada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Ctrl

## VISIBLE **INK** Answers; Clear and Simple

#### Letters to the INK Research Staff

#### Of Disk Drives and Sine Waves

I have a ZAP computer that I built using Steve Ciarcia's book "Building Your Own **Z80** Computer." I also have a Radio Shack Model III computer with one disk drive. I was planning to buy a Shugart disk drive, model 410. From what I have gathered so far, it is a single-sided/single-density drive. Is this drive compatible with the Model III? If it is, how should I strap it to identify it as drive 1? I already have a working drive as drive 0.

I need a circuit to produce a sine wave output. I will need a frequency bandwidth of 10 Hz to 50 Hz with an adjustable RMS value from 20 **mV** to 800 **mV**. The distortion should be below 0.1%. I know that this is asking a lot from a circuit, but I'm confident in Circuit Cellar INK's ability to give me an answer. By the way, the signal from this circuit will be connected to geophones used in the geophysical oil industry.

Thanks in advance for any help you can give me. Keep up the good work on the articles and projects. They are the one thing that keeps me in the learning mode while having fun.

Sam Maldonado, Jr.

Missouri City, TX

Inquiries at Radio Shack indicate that the Shugart 410 should be compatible with your system.

Drive selection is usually accomplished using jumpers or shorting blocks (available from sources such as JDR Microdevices) on the drive's analog board. The "drive select" jumpers will usually be labeled DSO, DS1, DS2, and DS3. First, be sure that your current drive is jumpered for DSO; it may be jumpered so that it's selected by any active DS line. Then jumper the new drive for DS1.

Other jumpers, with labels like MM, MS, HM, and HS should initially be set the same as similar jumpers on your current drive, but you may have to change them for reliable operation. Getting drives jumpered properly is something of a black art. Patience and systematic experimentation usually yield success.

While there are a few monolithic waveform generator ICs available (the EXAR 2206C is one example), I know of none with the distortion spec as low as you require. The 2206C offers a typical maximum distortion of 0.5% if carefully adjusted, however, and it might meet your needs if used with carefully selected precision components. Jameco Electronics (1355 Shoreway Rd., Belmont, CA 94002) carries an inexpensive function generator kit utilizing the 2206C as its central component. This kit would enable you to easily conduct experiments to determine the IC's suitability for your application.

#### -- INK Research Staff

#### **Reconfiguring CONFIG.SYS**

Please give me an education on CONFIG.SYS file device drivers. I am experiencing some confusion about device drivers, specifically how they are loaded and removed from memory.

Recently this has become an increasingly frustrating problem. I am using an 80386 IBM clone for desktop publishing. This system has a 19" NEC Monograph display, an HP LaserJet Series II printer, and an HP **ScanJet** scanner. The software we are trying to use is Xerox's Ventura Publisher and Z-Soft's Publisher's Paintbrush.

This is my situation: The HP scanner requires a device driver called SJDRIVER.SYS to be loaded with a DEVICE= command in CONFIG.SYS. I understand this driver is sitting in memory all the time, even when I am using programs that do not address the scanner. This was an offensive situation, but not catastrophic until I installed Publisher's Paintbrush. It requires two drivers: one for the HP scanner (HPSCAN.SYS) and one for the extended memory manager (EXMM.SYS).

Now I have three device drivers automatically loaded into memory when I boot up my computer. Guess what? Ventura Publisher no longer has enough memory to operate!

Why do these drivers have to sit in memory all the time? Isn't it possible to load and unload them with a batch file when I am using a program that needs them? I asked HP and Z-soft technical support this question -- they said no. The only solution they could propose is to have a separate boot disk with a CONFIG.SYS file

that contains all these drivers. I would have to boot the computer from different disks for Publisher's Paintbrush and Ventura. This is terribly inconvenient.

Any alternatives you could provide me would be greatly appreciated. Thank you.

#### Herald S. Herrington

Jerome, AZ

Device drivers of the type loaded by CONFIG.SYS are a convenient way to fit the software needed to drive special-purpose hardware into the minimum amount of memory. Once loaded, however, they are there to stay. The reason they can't be changed while the computer is up is because under normal conditions they can only be loaded by CONFIG.SYS, which can only be run at boot time. If you could unload one after DOS is loaded you wouldn't free the memory, anyway, because it would not be contiguous with the normal DOS program memory. It would just leave a hole in memory.

There are at least a couple of ways to make the reboot process less aggravating than two or more boot disks. One method I have used in a similar situation is to make two AUTOEXEC files, one named AUTOEXEC.BAT and one named AUTOEXEC.ALT, and similarly, two CONFIG files named with SYS and ALT extensions. The file extensions are switched by another batch file named RECONFIG.BAT. If the computer does not have the correct set of drivers installed you just enter the RECONFIG command and the filename extensions are swapped and the machine reboots. A variation on this can be used to reconfigure the machine for any number of different applications. We'll show you how to do this below.

Probably the most convenient method for your purposes is to incorporate the reconfiguring process into the batch files that load Ventura Publisher and Publisher's Paintbrush. If we assume that you want some way to return to DOS, you will need four CONFIG files and four AUTOEXEC files.

The first pair of AUTOEXEC and CONFIG files will be named AUTOEXEC.BAT and CONFIG.SYS. These will be set up to boot the system as you normally would for general use with all the PATH, PROMPT, etc. you now have. The computer will boot and stop at the DOS prompt.

The second pair will be named AUTOEXEC.DOS and CONFIG.DOS, and will be identical to the first pair. The reason for this should become obvious in just a couple of paragraphs.

Now, to set up for Ventura Publisher, find the VP.BAT file that loads Ventura Publisher. This file is made by Ventura Publisher during installation, and has commands that are needed. Rename this to VENPUB.BAT. Next, make three batch files as follows:

1. An AUTOEXEC replacement named AUTOEXEC.VP, containing at the least: REM AUTOEXEC.VP PATH=C:\;C:\VENTURA; ... CALL VENPUB REM The following commands are executed REM on exit from Ventura Publisher COPY AUTOEXEC.DOS AUTOEXEC.BAT COPY CONFIG.DOS CONFIG.SYS REM end

- 2. A CONFIG replacement named CONFIG.VP containing at least: FILES=20 BUFFERS=20 [or whatever number you need] DEVICE= [whatever drivers you need for Ventura J

- 3. A new version of VP.BAT as follows: COPY C:\AUTOEXEC.VPC:\AUTOEXEC.BAT COPY C:\CONFIG.VPC:\CONFIG.SYS WARMBOOT

This completes the setup needed to automatically configure the system to run Ventura Publisher. Now, let's walk through a bootup and loading of VP.

When the computer first boots up it calls **CONFIG.SYS and AUOTEXEC.BAT. These set up the** computer in whatever default configuration you define. Now when you enter the usual VP command to load Ventura Publisher, DOS begins execution of the new The first thing this does is change VP.BAT. AUTOEXEC.BAT and CONFIG.SYS to the ones containing the drivers needed for that program. The two **COPY** commands take care of this. Next, WARMBOOT is executed, which reboots the computer running the new CONFIG and AUTOEXEC files, and calls the old Ventura loader VENPUB.BAT (remember that we renamed this from VP.BAT). This loads Ventura in the normal way, but when you exit from Ventura the next two copy commands will be executed and the default DOS configuration will be restored. Another WARMBOOT at the end would go ahead and reboot the computer in the original configuration.

You will, of course, need a similar setup for Publisher's Paintbrush and any other programs that need special drivers.

Now for WARMBOOT. This is a little program that you make with DEBUG. If DEBUG didn't come with your DOS, try to find DOS version 2.1, and use the DEBUG with that. To create WARMBOOT:

1. Load DEBUG. At the DOS prompt enter the command DEBUGWARMBOOT.COM. You will see the message "file not found" followed by a "-", which is the DEBUG prompt.

2. Enter the following data exactly as shown here. We show what you will be entering in lower case, and DEBUG's response in CAPs. <enter> means that you should press the Enter key. -a100 XXXX:0100 mov ax,1234<enter> XXXX:0103 mov bx, 40<enter> XXXX:0106 mov es,bx<enter> XXXX:0108 es:<enter> XXXX:0109 mov [72],ax<enter> XXXX:010C jmp ffff:0000<enter> XXXX:0111 ret<enter> XXXX:0112 <enter> -rcx<enter> cx 0000 :112<enter> -w<enter> WRITING 0112 BYTES

Now, to check your program, enter the following "u" command and DEBUG will list the program. If you don't get the correct response, go back to the "a100" command and try again. You should see:

-u ZOO 112<enter> XXXX:0100 MOV AX,1234 XXXX:0103 MOV BX,0040 XXXX:0106 MOV ES,BX XXXX:0108 ES: XXXX:0109 MOV [0072],AX

#### *XXXX:010C JMP FFFF:0000 XXXX:0111 RET*

If all is well, you can enter "q" at the DEBUG promp to exit DEBUG. Now, typing WARMBOOT should reboot exactly as if you had hit the <ctrl><alt><del> key combination.

#### -- INK Research Staff

In Visible Ink, the Circuit Cellar Research Staff answers microcomputing questions from the readership. The representative questions are published each month as space permits. Send your inquiries to:

> INK Research Staff c/o Circuit Cellar INK Box 772 Vernon, CT 06066

All letters and photos become the property of CCINK and cannot be returned.

# **68000 POWER**

#### HARDWARE

Consider the **PT68K-2** for general computing, control, education, experimenters. 512 or **1024K** no-wait-state RAM, 4 serial and 2 parallel ports, clock/calendar, battery-backed static RAM, floppy disk controller, debugger and Basic in ROM. Advanced 68000 system fits into an XT/clone cabinet, its six XT-compatible slots accept color or monochrome video boards, hard disk controller, keyboard. Expandable in stages, starting with the Basic Kit (8 MHz, **w/o** DRAM, FDC, DOS) at **\$200**; 10 MHz Kit (with **512K, FDC**, ports, SK\*DOS) \$575; Assembled board (12.5 **MHz**, lmeg, SK\*DOS) \$899. OS-9, other systems available.

#### **PERIPHERAL TECHNOLOGY**

1480 Terrell Mill Rd. **#870C** Marietta GA **30067** (404) 984-0742

#### SOFTWARE

Consider SK\*DOS for general computing, control, education, experimenters. Full DOS documentation plus on-line help, multiple directories, **user**installable device drivers, RAM disk, disk cache, floppy or hard drives to 64 megabytes each, I/O redirection, time/date stamping, batch files, read and write MS-DOS disk files. Includes powerful utilities such as copy-by-date, undelete, show differences between files, prompted delete, text file browse, editor, assembler, Basic, more. Included with **PT68K-2** computer (left), **\$140** for other systems. Compilers, editors, cross- & disassemblers, communication programs, other software available.

#### STAR-K SOFTWARE SYSTEMS CORP.

P. 0. Box **209C** Mt. **Kisco** NY 10549 (914) 241-0287 / Fax (914) 2418607

#### **MICROMINT'S** Gold Standard in Single Board **Computers and Industrial Controllers** Annonacing Announising

BCC40D-\$139.00

\$395.00

The BCCT80, only 4.5" x 8.5" uses the same 64180 CMOS Z80 instruction compatible processor as Micromint's SB180 and SB180FX instruction compatible processor as Micromint's SM180 and SM180FX single board computers. Configured primarily for process control wy 384K of memory, 6 parallel I/O ports, console serial port, RS-232/422/ 485 selectable auxiliary serial port, and an interrupt driven ROM-resident multitasking BASIC-180 compiler, the r+f subset uses the same 44-pin I/O expansion bus as Micromint's BCC52 controller board.

CMOS HD64180, 9.216MHz 8-bit CPU, 68-pin PLCC package

- Up to 38K bytes total memory on-board L28K of either static RAM (62256) or EPROM (27256) 256K dynamic RAM SIMM Full-function &K ROM monitor included

7.1 - 11.1.1.2. Conois RS-22 serial port with auto baud rate select to 19 200 baud Peripheral serial port, 150-19,200 baud, selectable RS-232, RS-422. or RS-485 48 bis bidicetonal parallel (VO 64K I/O available through the BCC bus edge connector

- Correction and a strategy in the correction degree burnetion ID built 24(1):56(2) degree connector Compatible with all Miccronin RCC-series I/O expansion boards Two 26-pin headers for six bidirectional parallel ports 23-pin DB-25 for RS-232 coussiliary serial port 4 screw termination for RS-242 console I/O 4 screw termination for RS-242 console tion

9MHz assembled and fully socketed BCC180 Computer/Controller with 32K, bytes of static RAM, ROM Monitor, BASIC-180 development software and BCC (80+3+20 \$395.00

user's manual For Additional 256K DRAM add \$100.00 BCC180-1 100 Quantity w/32K RAM w/o ROM Monitor \$209.00

- fi

## BCC52 — \$189.00 BASIC-52 Computer/Controller

The BCCS2 Computer/Controller The BCCS2 Computer/Controller is Micromint's hottest selling standalone single board microcomputer. Its cost-effective architecture needs only a power supply and terminal to become a complete development or end-use system, programmable in BASIC or machine language. The RCCS2 uses Micromoresor which companies a

Micromints new 80C22-BGCC2Uses microprocessor #Which contains a BASIC-52 interprote floating point BASIC-52 interprote floating point intelligent 2764/128 EPROM pro-grammer, 3 parallel ports, a serial tertional port with auto baut rate se-letion a serial printer port, and it is buc ompatible with the full line of BCC-bus expansion boards. The HCCS2 bridges the gap between ex-pensive programmable controllers and hard-to-justify price sensitive port with gato between ex-pensive programmable controllers and hard-to-justify price sensitive flective disginal allows it to be considered for many new areas of im-plementation. It can be used both for development and end-use ap-plications. BASIC 62 is between ex-

plications. Since the BASIC-52 is bus oriented, it supports the following Micromint expansion boards in any of Micromint's card cages with optional power supplies:

| BCC22 Smart terminal board<br>ADP500 User vocabulary, digitized | BCC40R 8-Channel relay output<br>board |

|-----------------------------------------------------------------|----------------------------------------|

| speech board                                                    | BCC53 Memory and 6 port I/O            |

| BCC25 LCD display board                                         | expansion board                        |

| BCC33 3 port I/O expansion board                                | BCC13 8-bit and BCC30 12-bit           |

| BCC40D 8-Channel optoisolated                                   | A/D converter boards                   |

| I/O expansion board                                             | BCC18 Dual channel serial I/O          |

BCC52 BASIC 52 Controller Board BCC-SYST.5 "52 PAK" Starter System includes: BCC52,ROM A&B UTIL.,CC01,MB08,UPS10 \$189.00 \$449.00

BCC52 OEM 100 Quantity Price -- \$140,00 BCC52 CLower power all CMOS version of the BCC52 \_\_\_\_\_199,00 NOTE: The BCC52 series is available in Industrial Temperature Range, fully tested at temperature. Prices start as low as \$294.00 in single quantities. Be sure to call for a quote on your specific Industrial OEM requirements.

Features: • Uses Z\$ single chip microcomputer • On-board imy BASIC interpreter • On-board parallel ports & serial port • for interrupts (4 external) • Just connect a terminal and write control programs in BASIC • 6K bytes of RAM or EPROM memory on-board • Baud rates 110-9600 bps • Data and address bus available for 56K memory and I/O expansion • Consumes only 1.5 waits at +5, +12, and -12V and -12V

\* Now Available in Industrial Temperature Range

SECTERCATION Latched outputs Uses industry-standard OAC5, ODC5, IAC5, IDC5 type module Dual-ported module addressing LED on/off indicator on each LED on/off indicator on each channel Can be used concurrently with BCC40R and other BCC-bus pe-tipherals Operates on +5V Operating conditions: tempora ture: 0.50°C (32-122°F) data (32-22°F) (0.15°°) edge connec-tor 16-terminal screw connector (#14 wire)

OFM 100 Quantity pricing starts at \$95.00

-\$169.00

BECARD 6 without modules \$139.00 \$189,00 \$229.00

The Micromint  $H(C_{40R})$  is an 8-channel relay output expansion board designed for use with Micromint's family of BCC-bus Computer /Con-trollers. Using efficient mechanical relays, the  $H(-c_{10R})$  provides con-tact-closure on/off control of eight AC- or DC-powerd devices for data acquisition and control applications. Up to 16 R(-CaPR branch set to be used together in a single system to provide a total of 128 relay output channels. The relays are controlled by writing to a board-specific 1/O ad-dress. The relays are controlled by writing to a board-specific 1/O ad-dress. The relays at a single 1/O address or individual relays at eight separate 1/O addresses.

Individual relays at eight separate **Contract of the set of the se**

have single-pole-single-throw (SPST) output connection

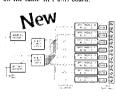

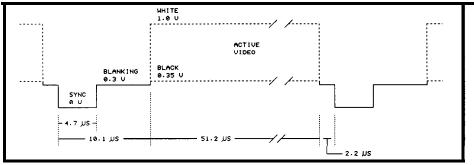

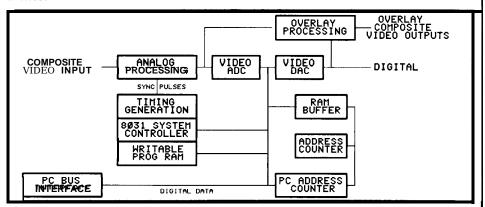

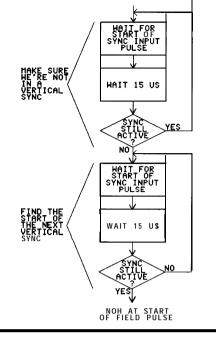

| SPICIFICATIONS<br>Contacts rated for: 1/10 HP, 3A 120V<br>resistive, or 3A 30VDC                                                     | New |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |