# CIRCUITARUNK®

THE COMPUTER APPLICATIONS JOURNAL

### EDITOR'S INK

### The Revolution Continues

As I write this, COMDEX is a two-week-old memory. I've had a chance to sit down and sift through the mountain of press releases, media kits, catalogs, and business cards that I brought back with me, and I've got to admit that I'm a little disturbed. Between networks, multiuser systems, and OS/2, the emphasis was almost entirely on (relatively) big computers and central control of programs and data. In this world, if you're not locked into a large project team at a multinational hardware or software manufacturer, you have no business mucking around inside the box. As a matter of fact, if you're trying to do anything at all outside the "mainstream" of modern corporate computing, it's obviously because you're a sinister sociopath, lurking in the shadows until you can crash our national defense system. As 1 walked the aisles of the Las Vegas Convention Center, I wondered if the "Microcomputer Revolution" had taken 12 years to bring us back to minicomputers and a white-coated DP priesthood.

When I left the main hall of the show, and visited the smaller companies in the hotels, I finally saw evidence that the microcomputer revolution still flourishes. A number of companies showed me products that make putting your computer in touch with the real world easier and more effective than ever before. There were single-board computers and controllers in a few booths, and tools for hardware and software engineers and designers in a few more. Looking at the components, adapters, and tools made me realize that there is a lot of very high-quality work going on in the smaller companies within our industry. There seems to be something about a small company that leads engineers to concentrate on practical, cost-effective, real-world solutions to problems. It made me feel good when I found that these working problem-solvers are often Circuit Cellar INK readers. I finally decided that much of the truly revolutionary work going on today is happening in small companies, just like it did in the beginning. I like that, and I'm glad that Circuit Cellar INK is able to play a part in the ongoing computer revolution.

Give Us an Earful

The response to our first reader survey was so helpful (Steve talks about the results of the survey in his column on the last page of this issue) that we decided to make it easier for you to tell us what you think of the magazine. Starting with this issue, there are three numbers printed at the end of each article. Please take a moment to decide which number matches your feelings about the article, go to the Reader Service Card in the back of the magazine, and circle the number. When you're through, tear out the card (it's postage paid) and drop it in the mail. The response we get to articles will have a direct impact on the type of articles we have in future issues. I'll say thanks in advance for helping us keep Circuit Cellar INK on the right track.

Beyond giving the editors feedback from you, the Reader Service Card that begins in this issue does two things: First, it makes it easier for you to get information on those products that interest you. Second, it gives our advertisers positive feedback on the investment they've made. Our readers are the reason we work so hard to make this magazine; our advertisers are the reason we can afford to make this magazine.

We're all looking forward to the new year. We're going to be growing and improving, but never losing sight of our mission to serve the people who design and build computer applications. From where I sit, it looks like a fun year ahead.

Curtis Franklin, Jr. *Editor-in-Chief*

**EDITORIAL** DIRECTOR/ **FOUNDER** Steve Ciarcia

**PUBLISHER** Daniel Rodrigues

> **ASSOCIATE PUBLISHER** John Hayes

EDITOR-in-CHIEF Curtis Franklin, Jr.

> **TECHNICAL EDITORS**

Ken Davidson Jeff Bachiochi Edward Nisley

**CONTRIBUTING EDITOR** Thomas Cantrell

**CONSULTING EDITOR** Har v Weiner

**CIRCULATION COORDINATOR** Rose Mansella

CIRCULATION CONSULTANT Gregory Spitzfaden

**PRODUCTION** MANAGER Tricia Dziedzinski

BUSINESS MANAGER Jeannette Walters

**STAFF** RESEARCHERS

#### Northeast

Eric A lbert William Curlew Richard Sawyer Robert Stek **Midwest** John Elson

Tim McDonough West Coast Frank Kuechmann Mark Voorhees

# Cincuit CFI

#### **FEATURES**

c8 ImageWise/PC -- The Digitizing Continues -- Part 2

by Ed Nisley

In the second of three parts, Ed Nisley shows the hardware details of this ISA bus gray scale digitizer, and contrasts the design with that of the original serial ImageWise. The starting point is the fundamental design decisions for an IBM/PC I/O bus board.

Build a Remote Analog Data Logger -- Part 2 22 The Soft ware

by R. W. Meister

In the final installment of the article, we explain the C language software for the Motorola 6809 controller. Bob Meister uses descriptions and examples to cover program logic flow, interrupt handling, and coding for specific routines.

#### **DEPARTMENTS**

| Editor's ink                                                          |    |

|-----------------------------------------------------------------------|----|

| The Revolution Continues                                              |    |

| by Curtis Franklin, Jr.                                               | I  |

| Reader's Ink Letters to the Editor                                    | 5  |

| Visible Ink Letters to the CCINK Research Staff                       | 20 |

| Ink Spot Guest Editorial A Call for Dedication by Ezra Shapiro        | 34 |

| From the Bench AC Power Line Transmission Conducted by Jeff Bachiochi | 42 |

#### THE COMPUTER APPLICATIONS JOURNAL

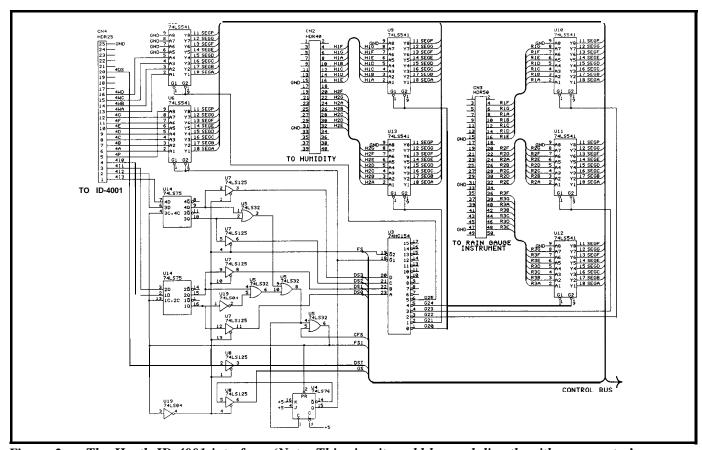

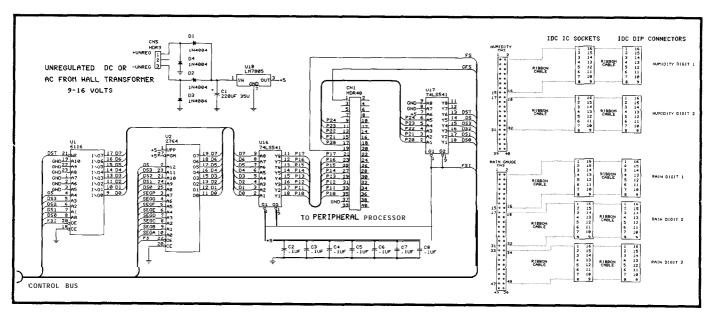

The Home Satellite Weather Center -- Part 7

Finishing the Firmware for the 68000 Peripheral

Processor

by Mark Voorhees

As the 68000-based Peripheral Processor moves closer to completion, Mark Voorhees wraps up the controlling firmware for the system. This installment shows how to integrate Weather Facsimile (WEFAX) reception and interface the Heathkit ID-4001 and ID-5001 weather instruments to the Peripheral Processor.

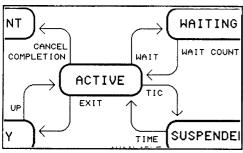

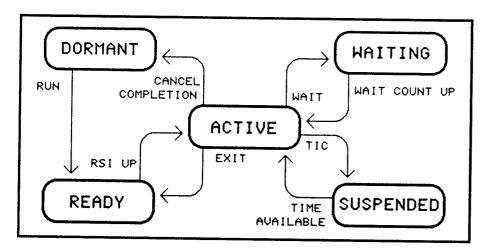

Writing A Real-Time Operating System -- Part 1

A Multitasking Event Scheduler for the HO64180

by Jack Ganssle

In the first of two parts, Jack Ganssle explains the concepts behind a real-time operating system (RTOS) and shows how an RTOS differs from a general-purpose operating system. He then moves into the beginning of the actual code with the scheduling algorithm and central Task Control Block.

Cover Illustration by Robert Tinney

Circuit Cellar BBS - 24 Hrs. 300/1200/2400 bps, 8 bits, no parity, 1 stop bit, 203-871-1988

The schematics provided in Circuit Cellar INK are drawn using Schema from Omation Inc. All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure that their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore. because of the possible variation in the quality and condition of materials and workmanship of readerassembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or in-formation published in Circuit Cellar INK.

CIRCUIT CELLAR INK (ISSN 0896-8985) is published bimonthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (203-875-2751). Second-class postage paid at Vernon, CT and additional offices. One year (6 issues) charter subscription rate U.S.A. and possessions \$14.95, Canada \$17.95, all othercountries \$26.95. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank. Direct subscription orders to Circuit Cellar INK, Subscriptions, 12 Depot Sq., Peterborough, NH 03458-9909 or call (203) 875-2199 POSTMASTER: Please

send address changes to Circuit Cellar INK, Circulation Dept., 12 Depot Square, Peterborough, NH 03458-9909. Entire contents

Entire contents copyright 1988 by Circuit Cellar Incorporated. All rights reserved. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

### READER'S! NK

#### Letters to the Editor

I'd Like to See ...

For future editions, please consider a digital music mixer for the IBM PC/AT (including a MIDI interface), or a video-recorder data-backup device, or a video camera-to-IBM disk device.

John Lee Chicago, IL

[For a video camera-to-disk device, I think that the ImageWise/PC, which continues in this issue, will be hard to beat. I haven't seen a project for any sort of data backup device here, but I would certainly be happy to look at a proposal from one of the Circuit Cellar INK readers. Finally, we're planning an issue on "Applications in the Arts" for later this year. If anyone has done work with MIDI, graphics, or other artistic applications, drop me a line to see about article possibilities. Ed. ]

I received issue #5 this week and thoroughly enjoyed it. I especially enjoyed the article on "10-MHz/8-bit Digitizing Board for the IBM PC." I would like to see more articles on video design including articles on frame grabbers, text overlay, and simple image processing. Thanks again for an enjoyable publication.

Steve **Horacek** Boulder. CO

[Gee, it looks like we started ImageWise/PC just in time! We're working on bringing more video projects to Circuit Cellar INK, so hang in there. I think that Circuit Cellar INK in 1989 will have some articles that are right up your (video) alley. Ed.]

Thanks for the great magazine. I am pleased with

the issues so far. I am glad that you are publishing technical articles of all types, not just strictly computer articles.

I hope that we'll see some articles written by Apple [I enthusiasts. I'd like to see more information on the GIF graphics format mentioned in Circuit Cellar INK #3. I'm disappointed at the lack of Apple [I software for the ImageWise digitizer. Perhaps GIF will be the answer.

Rolf Taylor North Salem, NY

[OK Apple fans, here's your chance. If you've written ImageWise software for the Apple ][, or if you're building applications around this venerable platform, let me know. Circuit Cellar INK tries to present applications based on many different computing platforms, and is dedicated to no particular architecture or operating system. Ed.]

I have worked with computers for 20 years, have progressed from computer operator to programmer to systems analyst to computer scientist, and have been delighted with being able to make any computer "sing" for me. I never had any interest in electronics until I saw Steve Ciarcia's "Why Microcontrollers" in the August 1988 issue of BYTE. That did it for me. I have now gone hog-wild, researching the University of Houston technical library and every other source I can get my hands on which will expand my understanding and knowledge as pertains to all forms of ICs and peripherals. I have also undertaken several concurrent 803 1 -controlled projects which I thought up.

Will you be addressing any aspect of ASICs and PLDs in future issues, or should I just go ahead and study other sources to satisfy my interest in that area?

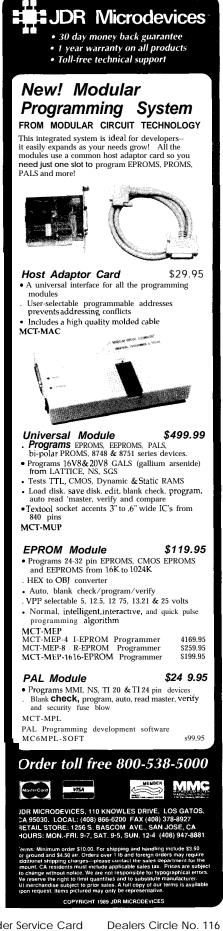

Allen R. Summers Pasadena, TX [We certainly do have projects which use ASICs and PALs, as well as tutorials on how to design with them, in the works. One of the problems in this area is trying to offer projects that don't require a \$30,000 development system, and we're working in that direction. Stay tuned. Ed.]

I have enjoyed all the articles in Circuit Cellar INK. I am very interested in video processing, and in converting from one standard to another. I also like electromechanical projects, and have built such things as solenoid- and servo-operated gearboxes for R/C models.

Keep up the X-10 projects. I have 14 modules around my house operating lights, fans, TVs, and so on from a programmable timer, a maxi controller, and two mini controllers. I have a separate system for my ham shack made up of recovered units and their controls purchased at a ham fair for \$4.

Adrian **M. Zeffert** East Northport, NY

Circle No. 124 on Reader Service Card

#### An Important Theme

The nicest thing about Circuit Cellar INK is that I feel good reading it. It doesn't make me feel guilty about having forgotten the propagation theory back in '63, but still does give me the information about new and fun projects I want to dream about (even if I can't afford to build all of them). I am glad that you provide the necessary background (such as the stepper motor article) without patronizing. It reminds me of the days on the roof tuning our cubical quad, with the transmatch my father and I built from scratch (coils, chassis, and even the six-inch-long variable capacitor -- plates and all) feeling sure we knew all there was to know on antennae.

More important, though, is the theme I think I sense here. A willingness to share, the courage to do it yourself in a snotty-pants peer society that thinks itself so high and mighty, riding on big expensive systems, but can any of the members of the society even begin to calculate what brings the signal across three inches of PCB into the DRAM? HA! In Circuit Cellar INK I see, once again, a hope for the generation my kids will have to be members of.

My only regret now is that I won't be able to access the Circuit Cellar BBS. Are there any plans to get a Tymnet link? How about opening a conference on CompuServe? If you do get Tymnet, Telenet, or a CompuServe conference, please let us international readers know!

#### Steve Chandler Israel

[First, thanks for the kind words. One of the principle motivations behind a publication like Circuit Cellar INK is the feeling that you can help people improve their engineering and design skills; that you can help them be better doers, not just better shoppers.

We are constantly looking at ways to make the Circuit Cellar BBS accessible to more people, and we've talked about doing all the things you mention. The biggest limit right now is human resources. There's one overworked engineer/editor who already spends several hours a day just keeping up with the current Circuit Cellar BBS. If we expand the system's scope, it will take at least one full-time person to direct traffic. We're still looking and talking, though, and you can be sure that any changes will appear in the pages of Circuit Cellar INK before they show up on the board. Ed.]

#### Corrections

Issue#5, Sept/Oct '88 -- 10-MHz/8-bit Digitizing bard for the IBM PC Page 30 -- U3 pin 4 should go to -5V through R8. Pm 7 should go lo +5V through R7. Pin 8 is unused.

Issue #6, Nov/Dec '88 -- ImageWise/PC -- The Digitizing Continues

Pages 38 8 41 -- Swap photos 1 and 3, leaving the captions in place. The caption

for Photo 3 should refer back to Photo 1.

# **ImageWise/PC -- The Digitizing Continues**

by Ed Nisley

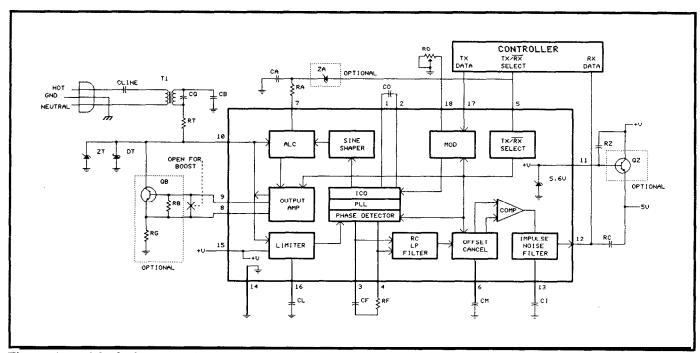

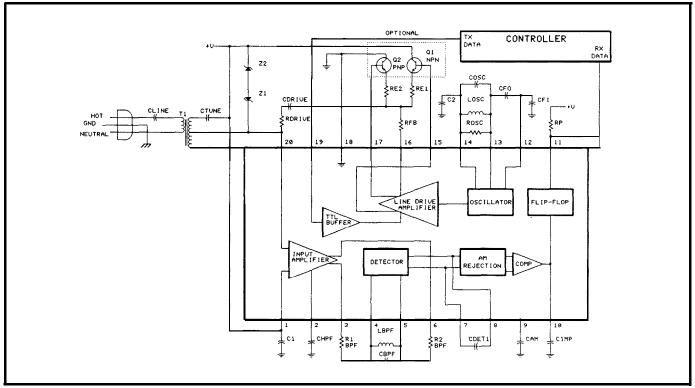

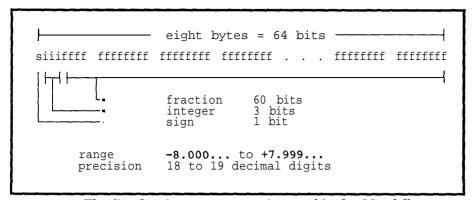

erhaps the fundamental truth of engineering is that you can't have everything. There are always conflicting requirements: speed, power, board space, design time, parts use, and complexity must all be balanced against each other. Throughout this article I will discuss the tradeoffs we made in the ImageWise/PC design so you can see why it works the way it does.

Because most of you are familiar with the original ImageWise design presented in the May and June '87 Ciarcia's Circuit Cellar articles in BYTE, I'll concentrate on what's new and different about the ImageWise/PC hardware. The starting point is the fundamental design decisions for an IBM PC I/O bus board.

Where's the Buffer?

The heart of the ImageWise/PC circuitry is 64K bytes of static RAM, enough to hold one digital image. The video ADC (Analogto-Digital Converter) translates each scan line of the incoming video signal into 256 separate pels (picture elements), so the buffer can hold up to 256 such lines, although one scan line is reserved for internal use. NTSC video has about 244 scan lines, which is the standard I will use throughout this article. PAL and SECAM video have about 280 scan lines, but only 255 can be held in the buffer. The

additional 25 lines normally fall within the monitor's overscan region, so aren't visible anyway.

The video ADC produces eight bits of data for each pel, resolving the image into 256 shades of gray. The video DAC translates this data back into an analog voltage resulting in a good reproduction of the original scene.

In order for the ImageWise/PC to be useful, the IBM PC must also have access to the buffer memory, The most obvious method is to assign 64K bytes of the PC address space to the ImageWise/PC video buffer. The memory maps in Figure 1 show why this simply won't work: while there are some 64K slots free in a bare-bones PC, a mod-

erately well-equipped AT doesn't have any available memory addresses!

The AT's memory map does have some "holes" that are unused, so the ImageWise/PC buffer could be mapped into a hole in sections. For example, there may be 32K available in segment C000 hex next to the Disk BIOS ROMs. We decided that the added complexity

of the mapping hardware outweighed the advantages of direct access, particularly since the buffer's starting address would still have to be picked to match the peculiarities of each system.

We finally made a tradeoff that avoids memory mapping entirely! The video data can be moved through a single I/O port using I/O instructions instead of memory

# Part 2 The Hardware

| 5000:<br>4000:<br>3000 :<br>2000 :<br>1000 : |

|----------------------------------------------|

|                                              |

The ImageWise/PC can combine analog and digitized images as either digital over analog, or analog over digital image screens.

| FØØØ: 0000         | ROM BIOS                                        | ROM BIOS                                |

|--------------------|-------------------------------------------------|-----------------------------------------|

| EØØØ: 0000         | RESERVED                                        | RESERVED                                |

| <b>DØØØ</b> : 0000 | FREE                                            | EMS RAM                                 |

| CØØØ: 0000         | FREE                                            | DISK BIOS                               |

| BØØØ: 0000         | MDA BUFFER                                      | EGA BUFFER                              |

| A000 : 0000        | FREE                                            | EGA BUFFER                              |

| 9000: 0000         | RAM                                             | RAM                                     |

| 8000 : 0000        | RAM                                             | RAM                                     |

| 7000 : 0000        | RAM                                             | RAM                                     |

| 6000: 0000         | RAM                                             | RAM                                     |

| 5000: 0000         | RAM                                             | RAM                                     |

| 4000: 0000         | RAM                                             | RAM                                     |

| 3000 : 0000        | RAM                                             | RAM                                     |

| 2000 : 0000        | RAM                                             | RAM                                     |

| 1000:0000          | RAM                                             | RAM                                     |

| 0000 : 0000        | RAM                                             | RAM                                     |

|                    | IBM PC<br>MONOCHROME<br>DISPLAY<br>NO HARD DISK | IBM AT EGA DISPLAY HARD DISK LIMEMS RAW |

Figure 1 -- A memory map for the PC/XT and PC/AT shows why using an I/O port was chosen for the ImageWise/PC as an alternative to memory mapping.

transfers. A counter on the ImageWise/PC board generates RAM addresses so the PC program can simply read or write bytes from the port.

I/O instructions are slower than memory transfers but the difference is relatively small. The key point is that even though the transfer takes somewhat longer, the ImageWise/PC board can be used in a "full-up" PC or AT with no problems.

Access Control

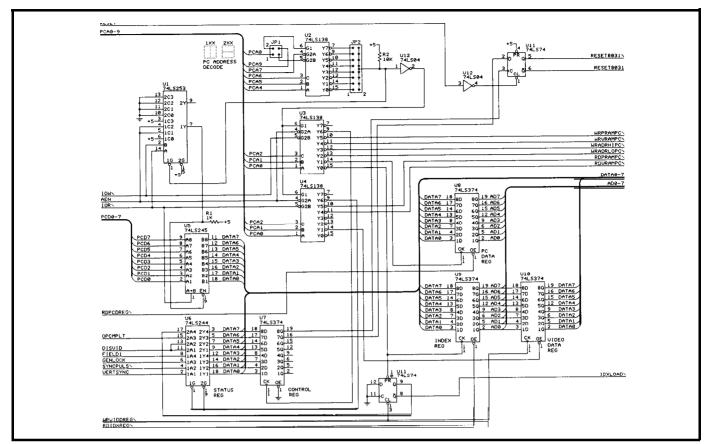

The ImageWise/PC board uses an Intel 8031 microcontroller to handle many logic functions that would ordinarily require a lot of "glue" chips. While we could use an ASIC (Application-Specific Integrated Circuit) chip to merge these functions into a custom design, the microcontroller offers far more flexibility to handle require-

ments that crop up after the board is designed and manufactured.

Because the 8031 can also read and write the video buffer, there are six ways to get data into or out of that RAM! Ideally we would like to allow simultaneous read/write access by the ADC, DAC, PC, and 8031. That way the software doesn't have to take conflicts into account. But there are some thorny problems along the way ...

Each scan line on the screen presents 256 bytes of data in about 5 1 microseconds, or one byte every 200 nanoseconds. The ADC will produce one byte and the DAC will consume one byte at that rate throughout the visible part of the image, although the ADC is active only when acquiring an image. Neither access can be delayed in the least because there is no way to "pause" the analog video signal. Therefore the ADC and DAC must have uninterrupted access to the Image RAM.

When the ADC or DAC are accessing the buffer, all other uses must be squeezed in between successive samples. Dividing the

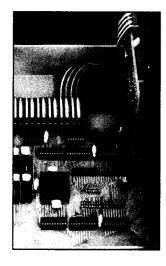

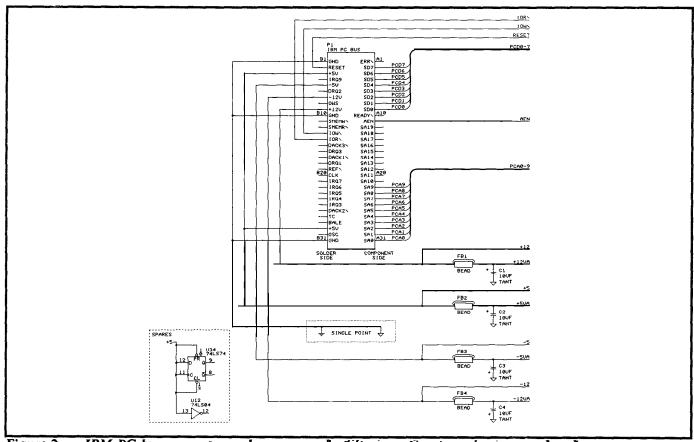

Figure 2 -- M'M PC bus connector and power supply filtering. Great emphasis was placed on power supply noise elimination because of the analog circuitry on the board.

available time equally allows only 100 per access and allowing time for register and buffer delays means that the Image RAM must cycle in about 75 ns. While using a 64K buffer of 75-ns RAM is possible, the cost of the buffer and the additional circuitry gets out of hand quite rapidly.

We decided the best solution was also the simplest: allow only one device to access the Image RAM at any one time. The ADC and DAC have unrestricted use during active video, and the PC and 8031 must disable the video entirely or squeeze accesses into the blanking intervals to prevent collisions.

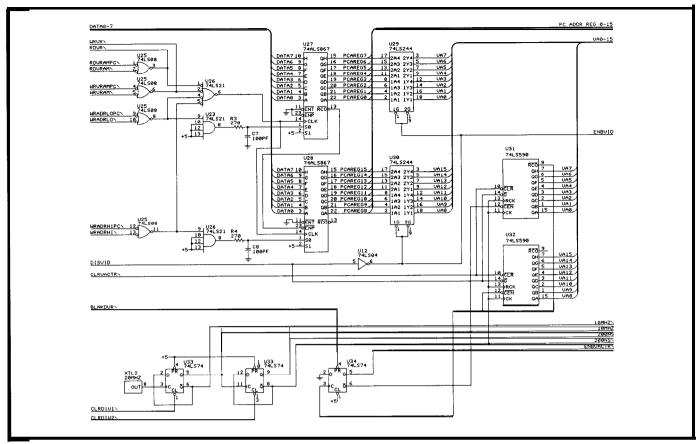

Now that you understand why the ImageWise/PC uses I/O-mapped accesses, it's time to get into the details. Figures 2 through 8 show the ImageWise/PC logic. Each schematic concentrates on the

logic for a particular section of the design.

#### PC Interface Logic

From the PC's point of view, all access to the ImageWise/PC circuitry occurs through seven I/O ports. Two jumpers on the Image-Wise/PC board set the base address for these ports, which is normally 110 hex. Figure 9 shows the default port assignments.

Figure 3 shows the port decoding logic and the registers that transfer data between the PC and the 8031 firmware. Although the board uses seven I/O addresses, it occupies 16 bus addresses because the decodes are not complete. For example, address bit 3 does not enter into the decoding logic so the board will respond to accesses at 110 or 118 hex with the same action.

The ports fall into three classes: hardware control, RAM access, and firmware interface. Because I started out by describing the reasoning behind Image RAM accesses, I'll begin with the RAM

Figure 3 -- IBM PC bus interface circuitry. The board can be jumper-selectively addressed at one of 16 base port addresses.

The entire **ImageWise/PC** board fits into a single full-length 8-bit ISA (PC-Bus) slot.

control circuitry.

All image data is transferred through the VRAM port. Each access uses the current value of the PC Address Counter (U27 and U28), which is loaded by writes at ports ADDRHI and ADDRLO. Each VRAM access increments the address counter, so reading the full buffer requires a single address followed by 244 x 256 reads.

The port at CTL\_STAT contains all of the hardware control and status bits, which are itemized in Figure 10. Writes to this port set the controls, while port reads return the current status bits. I will describe the reset functions in more detail when I explain the Program RAM.

Firmware Interface

The INDEX and DATAREG ports provide a communication link

between the PC program and the firmware running on the 8031 processor. The board has great flexibility because nearly all of the board's functions can be adjusted on the fly. I will describe the firmware in more detail in the next article, but the hardware merits separate discussion.

There are several dozen variables controlling everything from the duration of horizontal sync pulses to the overall video signal level. These variables are grouped into the firmware registers shown in Figure 11.

Rather than provide a separate I/O address for each register, the ImageWise/PC firmware uses the INDEX port to specify which register will appear at the DATAREG port. Changing the contents of a firmware register requires writing the new value to DATAREG and writing the regis-

Figure 4 -- Main system controller, including the 8031 processor, control program storage, and programmable interval timer.

ter number to INDEX. Similarly, reading the current value is accomplished by writing the register number to INDEX and reading DATAREG.

There are actually two DA-TAREG registers. U8 holds the value written by the PC program and U10 latches the corresponding value from the 8031 firmware. Each is readable by the other processor.

The 8031 monitors the output of U11B to discover when the PC writes an INDEX value. The U11B flip-flop is cleared when the 8031 writes a value into U10, which is ordinarily the last step in the firmware's response to the INDEX value.

The firmware presets the values of all the registers after a hardware reset so the PC doesn't have to load anything unless the defaults are not correct.

#### Program RAM

There is one port I have not mentioned yet: PRAM. This port gives access to the Program RAM holding the 8031 firmware program. In ordinary use, the PC will not have to read or write anything from this port because most Image-Wise/PC boards store their programs in EPROM.

Close scrutiny of Figure 4, though, shows that the circuitry can handle static RAM chips or EPROMs, with either 8K- or 32K-byte capacity. Bus buffer U17 allows the PC to read and write the Program RAM much as it does the Image RAM. U17 is omitted from boards using an EPROM because there is no need to access the EPROM.

Because the 8031 must be reset during program loading, the Image RAM will be inactive. Rather than

include a separate Program RAM address counter, the PC Address Counter also provides the address for the Image RAM through multiplexers U13 and U14. These chips are omitted from EPROM-only

Figure 5 -- Video RAM addressing section plus master clock generation. Synchronous counters are used to simplify the task of addressing memory.

boards.

Once the starting address is loaded into ADDRHI and AD-DRLO, reads and writes to the PRAM port access the Program RAM. Unlike VRAM accesses,

though, these accesses do not increment the PC Address Counter. After reading or writing the PRAM port, the program must access VRAM to step to the next address.

RAM storage does introduce one complication, though: the ImageWise/PC cannot begin operation until the Program RAM contains a valid program. The solution to this is to provide a reset function controlled by an I/O port as shown in Figure 3 instead of using the I/O bus RESET signal.

The output of U1 IA is connected to the 803 1 Reset line so that the processor is disabled whenever the flip-flop is cleared. A bus RESET signal clears the flip-flop, ensuring that the 8031 is halted when you turn on the power. Bits 6 and 7 in the CTL\_STAT port control the state of the latch; bit 6 sets or clears it, while a O-to-l transition on bit 7 clocks bit 6 into

the latch.

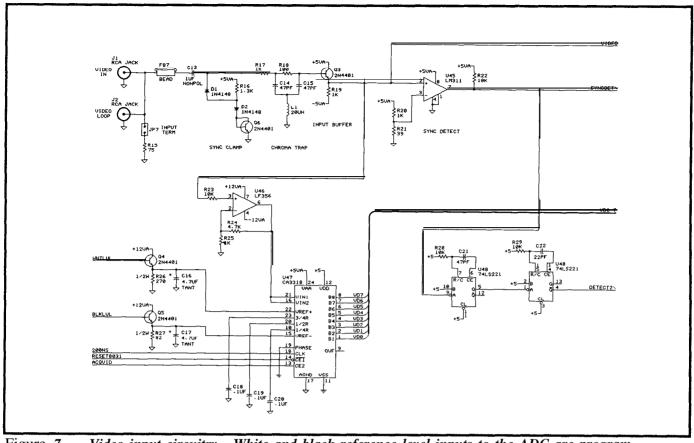

Analog Video Input

The analog video input circuitry shown in Figure 7 has several improvements over the standalone ImageWise design, although you're certain to recognize the similarities.

The circuitry must clamp the incoming sync tips to ground level so that the video signal levels are at a known voltage. The new design has better temperature compensation and clamps the tips closer to ground level.

The older design used a simple RC filter to eliminate the **subcar**rier from color signals. Although we intended that board for use with monochrome cameras, I have to admit we should have done better. The new **chroma** trap was suggested by a caller on our BBS; it works just

Figure 6 -- Video RAM and data buffers. One 256 x 244 picture fits nicely in the 64K of RAM provided on the board.

fine and we're glad to adopt it. Incidentally, the value of the inductor (L1) is different in the PAL and SECAM boards because the chroma signals use different frequencies.

The ImageWise/PC uses the CA3318 8-bit flash ADC (U47) to capture video signals. This IC is the "big brother" of the CA3306 used in the stand-alone serial ImageWise transmitter, but the circuitry required to drive it is significantly different.

Flash ADCs require one analog comparator for each voltage level, so the CA331 8 has 256 comparators. The CA3306 needed only 64, so you can imagine the increased chip complexity! Each comparator decides whether the input signal exceeds a reference voltage set by a resistive divider driven from the Vref+ and Vref- inputs. A logic network encodes those 256 binary

signals into just eight output bits.

The increased number of resistors in the reference divider requires a higher voltage to provide sufficient reference current. Unfortunately, that means the analog signal must be higher as well, so we added an LF356 op amp (U46) to provide about 5 volts of video to the CA33 18 input.

The reference voltages define the analog signal levels that will be converted into the 00 and FF (hex) digital codes. We used two outputs of the AD7226 quad DAC (U41) to set these voltages so you can match different camera levels without removing the PC's cover. The AD7226 doesn't have enough output drive capability to handle the CA3318 reference inputs, so Q4 and Q5 buffer the voltages.

An LM3 11 (U45) compares the video signal against a fixed reference to produce a digital signal

whenever a sync pulse occurs. As in the older design, the 8031 determines the pulse duration to find vertical **syncs**. Several people have asked where we hid the sync detection circuitry; there simply isn't any!

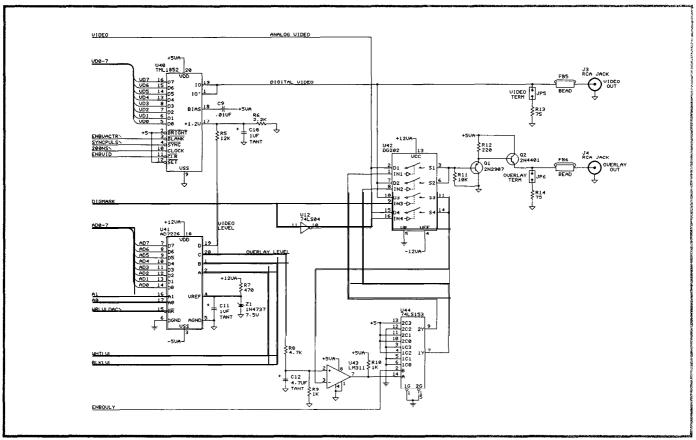

Analog Overlays

Although the ImageWise/PC uses the same TML 1852 video DAC (U40) to convert the digital values into analog waveforms, the surrounding circuitry as shown in Figure 8 is completely different! Because the same board has both the input and output video signals, adding some circuitry to overlay the two was both irresistible and fairly simple.

Although the term "overlay" implies that one image is placed atop the other, the actual hardware is a pair of switches (U42) with

Figure 7 -- Video input circuitry. White and black reference level inputs to the ADC are programmable via the DAC found in Figure 8.

their outputs connected together. One switch is connected to the live analog video input, while the other is connected to the stored digital image. Each switch can transmit or block its video input; only one switch can be turned on at any time.

The analog switches are controlled by a second LM311 (U43) which compares a video signal against a reference voltage supplied by an output of the AD7226 quad DAC. Whenever the video exceeds the reference, the switches send the stored digital image to the output buffer. Conversely, when the video drops below the reference, you'll see the analog input.

We used the other two analog switches in U42 to select the overlay comparator's video signal input. This provides the flexibility to compare the level of either video signal; there are useful applications for both. Further, because the overlay reference is set by a DAC, the switching level can be set anywhere from black to white.

Of course, the TML1852 video DAC output also goes to a separate jack so you can monitor the digital image directly even while an overlay is in effect. By setting the overlay level to a very low value you can see the entire live and digital images on two monitors at the same time, which simplifies camera focusing a lot!

The fourth AD7226 DAC output controls the amplitude of the TML1852 DAC, so you can adjust the output brightness directly. This is particularly useful because the signal level depends on the number of terminations on the DAC output. You can also fine-tune the level to match the analog input level so overlaid images are comparably bright.

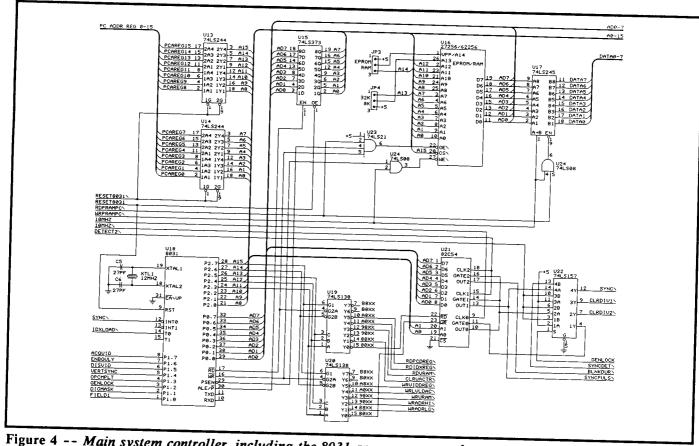

#### Genlock Sync

Creating overlays requires that the output sync pulses occur at the same time as the input pulses so that the two images are stable with respect to each other. TV production studios have a single sync generator that produces master timings for the entire installation; all of the video gear is "genlocked" to this single generator. The ImageWise/PC has a somewhat more relaxed definition of genlocking that is sufficient for our overlays.

Because both the input signal and the ImageWise/PC use crystal oscillators for their basic timing you might think that they are stable enough to get away with no locking at all. Even cheap oscillators have frequencies accurate to about 100 parts per million, which ought to be close enough. Unfortunately, that's just not so.

Figure 8 -- Video output circuitry and level DAC. Note the solid-state switch used to provide overlay capabilities for the output.

The basic line timing is 63.5 microseconds, so an error of 100 parts per million is 6.35 ns. After one frame of 525 lines the accumulated error is 3.33 µs, which means that the scan lines would be displaced about 5%. After one second, the error is nearly 100 µs, or one-and-a-half lines! Obviously we have to do much, much better than 100 ppm to have stable sync.

True genlocking requires an analog phase-locked loop that tunes the internal clock frequency to exactly match the external sync input. The design of this PLL is extremely critical for color TV signals because it must precisely match the phase of both color subcarriers. Because the subcarrier phase determines the colors you see on the screen, any error is immediately and painfully obvious.

The ImageWise/PC sync timings are created by an Intel 82C54

Programmable Interval Timer (U21) dividing a IO-MHz clock by the appropriate values to produce regular horizontal sync pulse intervals and widths, as well as horizontal blanking durations. U33A creates the IO-MHz clock from the 20-MHz output of XTL2, a crystal oscillator.

The IO-MHz signal is further divided by U33B to get the basic 5-MHz pel clock used by the Image RAM circuitry. The hardware resets U33B at the start of each scan line, because otherwise the phase would flip on successive lines and cause obvious jitter. Think about it. . . the lines are 63.5 microseconds long and 5 MHz is 0.2 microseconds.

The 20-MHz oscillator is **free**-running and isn't synchronized to anything at all. When the **Image**-Wise/PC is not genlocked, the **10**-MHz divider is also free-running,

because there is no reason to reset it. The **5-MHz** divider is reset on every scan line and all is right with the world.

When genlocking is in effect, U22 switches several signals that control the dividers and 82C54. The external sync signal now determines the horizontal line time, so **82C54-2** Timer 0 is programmed to create a short pulse immediately after the start of the external sync. The IO-MHz and **5-MHz** dividers are both reset by pulses from U48 so that their phases have a known relationship to the input sync. Finally, the 8031 is interrupted by external sync instead of the 82C54 output so that it can track the external video.

Resetting the IO-MHz divider has an interesting side effect because it is the **82C54** PIT clock input. When the clock stops, all timings are suspended! The **firm**-

```

INDEX

110

index register and register write flag

DATAREG

111 data I/O register

112 address register low byte

113 address register high byte

ADDRIO

ADDRHI

VRAM

114 video RAM data I/O

PRAM

115 program RAM data I/O

CTL STAT

116 control output/status input

Addresses are in hex.

Default jumper settings are assumed.

```

Figure 9 -- All access to the ImageWise/PC takes place through seven I/O ports. The default is for port 110 to be the beginning port for the ImageWise/PC.

```

Bit

Writing

Reading

unused

+Index Loaded

Operation Complete

unused

unused

unused

unused

unused

unused

+Field 1

unused

+Genlocked

+Enable 8031

-Sync Pulse Active

+Strobe Enable Latch

+Vertical Retrace

```

Figure 10 -- All of the hardware control and status bits for the ImageWise/PC are routed through the CTL\_STAT port at de fault address 116.

```

Registers 00 through OF contain control and status bits, set overall operating conditions, and handle other miscellany.

Program control bits

Program status bits (read only)

Setup bits

02

03-07

reserved

ADC white level

ADC black level

08

09

ΟA

Overlay switching level

Digital video Output level

Genlock retry limit

reserved

ΩD

Firmware version (major and minor hexits)

OE

Firmware version (two's complement of Reg OE)

Registers 10 through 1F control internal sync generation.

10-11

12-13

Horizontal line period

Horizontal sync duration

Horizontal blanking duration

14-15

Equalizing pulse duration

Vertical sync duration

Number of active video lines

Number of equalizing syncs

1B

Number of vertical syncs

1D

Number of syncs during vertical blanking

reserved

reserved

Registers 20 through 2F control external sync generation,

which is used during genlock operation.

Horizontal sync delay

22-23

Horizontal sync duration

Horizontal blanking duration

26-27

Equalizing pulse duration

28-29

Vertical sync duration

Number of active video lines

Number of equalizing syncs

2A

2B

Number of vertical syncs

2c

Number of syncs during vertical blanking

2E-2F

Camera horizontal blanking

```

Figure 11 -- Variables stored in the firmware registers control most of the attributes of the ImageWise/PC. Quantifies occupying two registers (16-bit values) are stored with the least-signi jicant byte in the lowest-numbered register. Time intervals are in units of 100 microseconds.

ware compensates for the typical value of the reset pulse, so the resulting timings are still accurate.

Unlike a true analog PLL design, the ImageWise/PC genlock circuitry can only adjust the internal timings in units of 50 ns (half of the 10-MHz period). This is 1/4 of a pixel width and is generally not noticeable, but under some circumstances you may see a slight "crawl" on sharp vertical edges. Most of the cameras and monitors we've tested work just fine, so you probably will not encounter it.

#### And More to Come

Although we have gone through the hardware design, some parts of the ImageWise/PC can be understood only if you see how the firmware controls the gates. In the next article I will describe the firmware required to make the board work, as well as some interesting PC utility software.

IRS=

201 Very Useful202 Moderately Useful203 Not Useful

**The** following is available from:

CCI 4 Park Street, Suite 20 Vernon.,CJ. 06066

For information and orders. Tel: (203) **875-2751 FAX: (203) 872-2204**

Item 1: ImageWise/PC PC board experimentor's kit Comes with 4-layer PC bard, and assorted key components including 27C256 EPROM, TML1852 D/A, AD7226 D/A, CA331 8 A/D, RCA jacks, ferrite beads, user's manual, and ImageWise/PC utilities on IBM PC format diskette.

A procurement list for **all ImageWise/PC** bard **com**ponents is posted on the Circuit Cellar BBS. Full **kit**are not currently available. **ImageWise/PC** is avail-**able** assembled and tested.

All payments should be made in U.S. dollars by **check** money order, **MasterCard** or Visa. Shi**p**ping and **han**dling: surface delivery add \$6.60 for U.S. Call for **Canada** and air freight delivery elsewhere.

### IT'S NOT TOO LATE!

You have until May 1, 1989 to enter!

of applications designers the readers of Circuit Cellar INK are. To **find** the answer, we're sponsoring the first Circuit Cellar Design Contest. This is your chance to win the acclaim of your colleagues, the admiration of Circuit Cellar INK readers everywhere, and some pretty nifty prizes.

We've tried to make this a simple contest. The emphasis is on embedded control applications, and *you can use* any commercially available controller chip (8052, 8096, 6811, 8742, etc.) in your design. Our team of judges will be looking for utility, creativity, professionalism, and elegance in the designs. Within these easy guidelines, the choices are yours: make it prosaic or outlandish, simple or complex, the choice is yours!

**Prizes!** Of course there are prizes! **First** prize is \$500, Second prize is \$200, **and Third** prize is \$100. In addition, we'll award as many Honorable Mention prizes (\$50 and a l-year subscription to Circuit Cellar INK) as are deserved. On top of all these prizes, winning entries may be the subject of **full** Circuit Cellar INK articles.

The winners will be announced in the July/August 1989 issue of Circuit Cellar INK. To enter, you must have an official entry form. To receive an official entry form, send a SASE to:

Circuit Cellar INK Design Contest P.O. Box 772 Vernon, CT 06066

#### Build Steve Ciarcia's

### HAL=4

EEG Biofeedback Brainwave Analyzer

The HAL-4 kit is a complete battery-operated **4-channel** electroencephalograph (EEG) which measures a mere 6" x 7'. HAL is sensitive enough to even distinguish different conscious **states**—between concentrated mental activity and pleasant daydreaming. HAL gathers all relevent alpha, beta, and theta brainwave **signals within** the range of 4-20 Hz and presents it in a serial digitized format that can be easily recorded or analyzed.

HAL's operation is straightforward. HAL samples four channels of analog brainwave data 64 times per second and transmits this digitized data serially to a PC at 4800 bps. There, using a Fast Fourier Transform to determine frequency, amplitude, and phase components, the results are

graphically displayed in real time for each side of the brain.

- . Stand-alone-not bus dependent

- . PC demo display software included

- . RS-232 serial output

- 'Sale battery operation"

- \* Complete software source code available

HAL-4-KIT......\$179.00 (plus S&H)

**WARNING:**

The Circuit Cettar Hemispheric Activation Level detector is presented as an engineering example of the design techniques used in acquiring brain-wave signals. This Hemispheric Activation Level detector is not a medically approved device, no medical claims are made for this device, and it should not be used for medical diagnostic purposes. Furthermore, the safe use of HAL requires that the electrical power and communications isolation described in its design not be circumvented. HAL is designed to be battery operated only!

To order please call **CCI**: (203) 875-2751 TELEX: 64333 1

FAX: (203) **872-2204**

Circuit Cellar Inc. 4 Park St.'- Suite 12 Vernon, CT 06066

SPECIAL: Mention this ad when placing your order and receive a set of HAL disposable electrodes........FREE

Circle No. 107 on Reader Service Card

### VISIBLE INK Answers; Clear and Simple

### Letters to the INK Research Staff

Field Data Collection

I suppose this is just one of the tons of letters you receive each day, so I'll be brief. The subject of my questions concerns field data collectors, known also as portable data terminals. Before replying, I want you to know that your answers to the following questions will be highly appreciated.

What is the state of the art in field data collectors? What are their virtues and drawbacks? Are they expensive? What are the costs for a given storage capacity and quality? Are costs expected to go down significantly in the near future?

I'm interested in this matter because I am finishing the design of a field data collecting system. Its main (not all) features are:

#### Collector:

- Size: 110 x 70 x 23 mm (4.33 x 2.75 x 0.9 in.) (about the size of a cassette box, but thicker)

- Weight: 10 oz.Storage: 48 Kb

- One- hand operation

- Waterproof, dustproof, shockproof

- Protected against electromagnetic and radio frequency interference

- Operating temperature: -25 to 160°F

- Altitude: up to 25,000 feet

- Price: Approx US\$300

- Ability to scan recorded data, to delete last entries, to label bad data, etc.

#### Interface:

- Size: 110 x 70 x 35 mm (4.33 x 2.75 x 1.37 in.)

- Weight: 25 oz.

- Data format: ASCII

- Data Transfer: Serial RS-232

- Data Rates: 300, 1200, 4800, 9600 bps

- Collector not needed to transmit data

- Price: Approx US\$300

Do you think there's any chance for a system like this to be sold reasonably in the market?

I'll be very grateful for your help in all these points, and any other that you might consider important.

#### Roberto Garcia S.

Chile, South America

There are several subdivisions of the data collector market, each specialized for a particular type of data. We'll go over what we know on the subject so you can decide if your devices fit.

The simplest data collection devices are intended for manual data entry at a location where a standard PC isn't practical. These are typically a keyboard of some sort, a display (usually an LCD with one to four lines and 16 to 80 characters), and an 8-bit microprocessor driving some battery-backed RAM. Usually there is a serial link used for uploading the collected data. This sounds like the type of device you are describing.

Next in line are collectors that have analog and digital inputs for direct connection to measuring devices. The controller will have some programming capability, generally a dialect of BASIC, to allow device setup and calibration. These are more expensive because they need precision analog circuitry and a more capable computer (perhaps with 16 bits or a faster clock).

Finally, there are complete data acquisition and control systems that can collect, analyze, and transmit data in real time. These are more like "real" computer systems and are usually installed in a fixed location.

They're hardened against environmental stress and may come in rack-mount versions for industrial applications.

Although there is some market for the "remote terminal" type of data collector, these devices are being squeezed by the low end of the laptop computer market. For about US\$700 you can now purchase a Toshiba 1000 laptop: a PC clone with a 25x80 LCD display, full keyboard, 720K floppy drive, serial and parallel ports, and 640K of RAM.

Now, admittedly, the Toshiba is much larger and heavier than your collector and it's not hardened against the full range of environmental hazards. On the other hand, it's only about US\$100 more than your device and is far more capable. In fact, what some folks do is write a dedicated program that handles full-screen data entry and editing and saves the result on diskette. The user doesn't even know that the computer can do anything else! For most applications, the Toshiba makes a lot of sense.

In short, it's quite likely that your collector has value for the market niche that needs small size, light weight, and relatively limited data entry capabilities. However, you will have to convince yourself that it can compete against the devices already on the market that are attempting to fill that niche, as well as survive against more capable units like laptops that will always have a significant cost advantage because of their volume production.

You must make a very careful market survey before proceeding. We can't help you with that because you need to collect specific information on all the devices currently available, decide what features the "next generation" will have, and how your device will be positioned against them.

Keeping Lightning off the Lines

I have just completed a power strip built into an Apple I power supply enclosure with an EM1 filter and three MOVs. The question is, can I be fully assured that, in case I forget to turn this thing off and it gets hit by lightning, the EM1 line filter will get the kick since it is wired closest to the line cord?

Next, what kind of similar protection can I use for modems? I believe there are commercial gadgets for this, but what about a DIY version?

James Lek Singapore

The power strip you describe should, if properly constructed, function well in normal use. However,

there is nothing that will offer complete protection for equipment (including the outlet box itself) from a direct or nearby lightning strike.

If frequent lightning strikes in your vicinity pose a problem, the best remedy is probably an array of fast-acting lightning arrestor equipment installed where the power line enters your building. Such protection is expensive and therefore reasonable only in unusual circumstances.

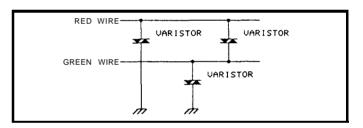

We assume that, in your desire to protect a modem, you want surge suppression on the phone lines rather than, say, on an RS-232 hook-up. With all the different technical specifications for telephone systems in various parts of the world, it's difficult to give an exact MOV circuit. However, we can provide a diagram showing a common method for phone line protection here in the U.S.

As the diagram below shows, there are commonly two phone wires, one with red insulation and one with green insulation. One MOV is installed across these wires: another MOV is installed between each wire and earth ground. Since the peak ring voltages sometimes approach those of the AC line, 130-VRMS MOVs are used. With suitable adjustments to allow for conditions in your country, this type of circuit offers good protection at reasonable cost.

204 Very Useful205 Moderately Useful206 Not Useful

In Visible Ink, the Circuit Cellar Research Staff answers microcomputing questions from the readership. The representative questions are published each month as space permits. Send your inquiries to:

> INK Research Staff c/o Circuit Cellar INK Box 772 Vernon, CT 06066

All letters and photos become the property of CCINK and cannot be returned.

## Build a Remote Analog Data Logger

by R.W. Meister

# Part 2 The Software

n the first part of this article (Circuit Cellar INK #6), I described the hardware for a remote data logging system. In this final portion of the article, I'll talk about the software that controls the hardware, why I wrote it the way I did, and how it works.

#### Why C?

Although C is considered a high-level, third-generation language, it can reference specific addresses in memory and communicate with hardware at a level that approaches assembly language. I could have written this program in assembly language, which would have provided us faster execution time (in an environment that relies on delays inherent in the hardware), but no one else would have been able to maintain the program. In addition, assembly language would have restricted the program to one kind of processor. Anyone with a different CPU would have to know both M6809 assembly language and their own CPU's assembly language, making translation difficult if not impossible. By using a high-level language, I have attempted to remove the CPU dependency from the program. The limited amount of assembly language is fairly easy to implement on other processors and may not even be required in some implementations. Of course, my own familiarity and preference, as

well as the "challenge" of the project, had something to do with the choice.

The software was a major part of this project. Parts of the 1000+ lines of heavily commented C code are being reproduced so you can refer to the program while reading this text.

[Editor's Note: Complete software for this article is available for downloading from the Circuit Cellar BBS or on Software On Disk #7. For downloading and ordering information, see page 62.]

Most C programs, when compiled, rely on rather extensive libraries of support subroutines, many of which are large, to handle transcendental functions such as sine, cosine, and square root, and the usually necessary input and output operations to terminals and storage devices. Even a simple program that prints "hello" can produce an executable file as large as IOKB! This program was designed to be fully self-contained (i.e., not require any external library subroutines) and makes only minimal use of assembly language routines. It is very modular, with only one routine spanning more than one page of code in the listing. Because of the lack of support subroutines from libraries, terminal input and output routines had to be written for the A/D program. There are no storage devices to deal with, and limited formatted output.

Hardware-Specific Programming

I wrote two interrupt service routines to do very small amounts of work in the shortest time possible, essentially setting flags, storing characters, or counting events. One handles the real-time clock, the other handles characters coming in from the device connected to the serial interface. The M6809 CPU handles interrupts by saving all of its registers on a stack. It then transfers program control to the interrupt service routine which, when finished, returns control to the interrupted program using an instruction that restores all of the saved registers. These service routines had to be written in assembly language to properly interface to the M6809. These routines then call the C subroutines directly. There was also an anomaly in the C compiler that was used on the M6809 development system: it used subroutines to perform multiplication and division when required by the running program. Some other systems use in-line code or even single CPU instructions for these operations. These routines were disassembled and rewritten in assembly language as part of the source program, again to preclude the necessity of needing any support library functions. A small initialization routine was also written in assembly language to set the hardware stack pointer, enable interrupts, and call the main C function.

There are several interrupt inputs on the M6809. One, called the Non-Maskable Interrupt (NMI), is always recognized by the CPU and can never be ignored or masked. The others are maskable, meaning that the CPU can suspend their action under program control for some amount of time. The

A/D box uses NMI for the clock and the Interrupt Request (IRO) line for characters from the ACIA.

The nonmaskable interrupt is generated by the 601-Hz signal from the data rate circuit. This event calls a C function that decrements a "tick" counter. When it reaches 0, it is reset to 601, and a

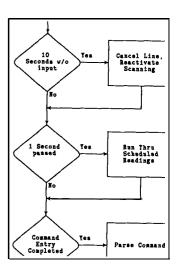

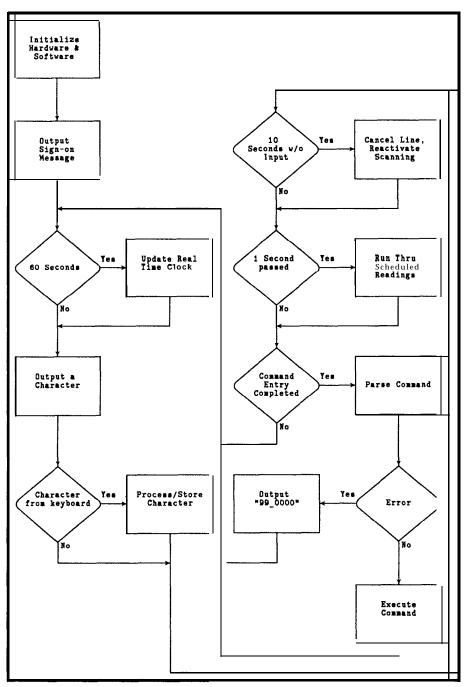

Figure 1 -- The flowchart for the data logging software shows that the program exists as a large loop that waits for data, and calls one of several subroutines when necessary. Modular programming and polling techniques mean that there are few situations when data is lost because of conflicts over CPU time.

# Need A Sophisticated Logic Analyzer But Cannot Afford One ?

#### the ID320

Logic Analyzer Card for the IBM PC/XT/AT May be Your Answer

State of the art design brings you high-end performance at ow-end price

#### Features:

- 32 channels 2K deep

- 25 MHz state analysis50 MHz timing analysis

- Variable Threshold Input Pods

- Single Slot Design

- Multi-level triggering

- Selective Data Capture

- Software Performiance Analysis

- Disassemblers for popular 8/16 bit microprocessors

- Test Development Language supports ATE applications

- Friendly User Interface

From \$1395

Satisfaction Guaranteed or your money back

14640 Firestone Blvd., Ste. C La Mirada, CA 90638 Tel: 714-521-5454

Circle No. 113 on Reader Service Card

"seconds" counter is incremented. The CPU then returns to the part of the program that was being executed when it was interrupted. Later on, the program recognizes that the "seconds" have changed, and adjusts the real-time clock. In a similar manner, characters received by the ACIA generate an interrupt that calls a C function. This function resets some pointers if the input buffer is empty, deals with Ctrl-S (XOFF) and Ctrl-Q (XON) by setting or clearing a flag, and then stores the character in the input buffer. The M6809 logic disables (masks) any further interrupts from the ACIA while the interrupt service routine is executing. When it finishes, the CPU will acknowledge and deal with any other interrupts that have occurred while it was busy. In actuality, the 4800-bps maximum data rate gives the interrupt service routines all the time they need to correctly process interrupts.

#### Into the Main Loop

The main part of the program is a big loop that checks to see if: one second has passed and the real-time clock needs adjusting; the user has typed enough characters for one command; it is time to output a reading; or a character can be sent out to the terminal. The attempted outputting of characters every so often is known as "polling." It depends on the fact that the program is looping over and over again, and judiciously placed attempts at outputting data will allow the CPU to do something useful (i.e., output to the terminal) while waiting for user input or the completion of an A/D conversion. The entire software design is based on small functions that spend very little time working and put their results into an output buffer whose characters are periodically sent to the terminal.

As in all good programs, we

first initialize the hardware and storage areas. The PIA needs to be set up for various input and output lines. We then tell the ACIA how many data and stop bits to utilize, and set up flags and buffer pointers as appropriate. A sign-on message is loaded into the output buffer, part of it is output in a loop, then we enter the main program where the rest of the sign-on message is output as part of the regular polling operation. At this point the program loops, processing the realtime clock, accumulating user command input, taking readings and outputting them (if any have been scheduled), and attempting to output characters to the terminal if any remain in the output buffer. While this is happening, the CPU is being interrupted at a 601-Hz rate (the real-time clock) and the user may be typing characters on a keyboard that cause interrupts so the characters can be stored and interpreted as a command.

The flowchart in Figure 1 shows the various operations that are handled in the main routine. Most of the time, the program is looking for something to do. When you complete entry of a command, the program performs the appropriate action according to the command letter and values associated with it. Each command routine uses very little processor time, and feeds all program-generated output into one periodically polled output buffer. In this way, timecritical events can still occur with a high probability of being detected and handled. For example, the "R" command reads the specified channel by: selecting channel 0 (to get the temperature sensor reference voltage), reading the voltage, selecting the specified channel, reading its voltage, then selecting the original channel again (because the scheduler expects the correct channel to be ready). Now that a valid reading has been obtained, the channel's formatting information sets up temperature conversion, decimal point location, timestamping parameters, and places the value in the output buffer. This reading will be sent to the terminal along with any other buffered output when normal polling takes place.

The MAIN program also keeps track of the time spent between typed characters. When you are in the middle of entering a command, the program simply places the characters into an input buffer and doesn't act upon the line until it has been terminated with a Return. If you begin entering a command and delay more than 10 seconds between any two characters, the program cancels the line and reverts to its normal polled operation. This time-out feature deals with occasional line noise when using the A/D box with a modem.

The SCHED routine is com-

plex, dealing with the event tables that govern which channels will be read, how many seconds elapse between readings, upper and lower limits, and channel formatting The MAIN program has data. already stored this information in several tables that contain all of these parameters along with which channels will be processed. If a desired active channel is in one of these tables, then a fresh A/D sample is taken, the next channel is selected, and the value is formatted according to temperature conversion. The elapsed timer is decremented by 1 each time the scheduler is called, and if it gets to 0, the channel's value is output. If either an upper or lower limit is set, and the current value exceeds either limit, then the channel's value is output. By selecting the next channel immediately after reading the desired one, the A/D converter has

adequate time to sample its input before a new value is requested by the program, especially due to the extra reading that is necessary when the input voltage changes polarity. With 16 different inputs, the box has no idea of the voltage level it will have to convert as it scans from channel to channel.

The scheduler is governed by two very important data structures. One is an array of 16 channel parameters that contains lower and upper limits, time interval, time remaining, current value, and some individual bits that are set by the channel-specific commands in the MAIN program (listed in Table 2). All of the information that the scheduler requires to process a given channel is kept in this array. Upper and lower limits are checked only if they have been specified. The time remaining is counted down each second and reset to the

#### **Powerful, Low-Cost Data** Acquisition and Control with Commodore C64 & Cl28

80-line Simplified Digital I/O Board with ROM cartridge socket Model SS100 Plus \$129. Additional \$119.

Original Ultimate Interface Universally applicable dual 6522 versatile interface adapter board. Model 64IF22 \$169. Additional \$149.

16-Channel, 8-bit analog-to-digital conversion module. Requires model 64IF22. Model 64IF/ADC0816 \$69.

Interface boards include extensive documentation and program disk. Manuals available separately for examination. Call or write for detailed brochure.

#### Resources for Serious Programmers.

- Symbol Master Multi-Pass Symbolic Disassembler. C64 & C128. \$49.95

PTD6510 super-powerful Symbolic Debugger. C64. \$49.95

- MAE64 6502/65C02 Macro Editor/Assembler. \$29.95

- C64 Source Code Book. Kernal and Basic ROMs. \$29.95

#### SCHNEDLER SYSTEMS

Dept. C, 25 Eastwood Road, P.O. Box 5964 Asheville, North Carolina 28813 Telephone: (704) 274-4646

Circle No. 122 on Reader Service Card

#### **VOICE MASTER KEY® VOICE RECOGNITION SYSTEM**

#### FOR IBM, PC, XT, AT AND COMPATIBLES

GIVES A NEW DIMENSION TO PERSONAL COMPUTING The amazing Voice Master Key System adds voice recognition to just about any program or application. You can voice command up to 256 keyboard macros. Requires under 64K. Instant response time and high recognition accuracy Works with CAD, desktop publishing, word processor, spread sheet, games, even other TSR programs! Voice Master Kay can also be called from within a program for adding voice recognition to custom applications. A genuine productivity enhancer. Easy and fun to use-the manual has you up and running in under an hour A price/performance

> breakthrough equal to other systems costing \$\$\$ more!.

ALL HARDWARE INCLUDED Consists of a short plug in board that fits in any available slot. External ports include microphone and line level inputs. High gain flat response headset microphone included. High quality throughout.

ONLY \$129.95 COMPLETE

ORDER HOTLINE: (503) 342-1271 Monday-Friday, 8 AM to 5 PM Pacific Time

Add \$5 for shipping and handling on all orders. Add an additional \$3 for 2nd day delivery. All goods shipped UPS. Master Card and VISA, money order, cashiers check or personal checks accepted (allow a 3 week shipping delay when paying by personal check). Foreign inquiries contact Covox for C&F price quotes. Specify computer type when ordering. 30 DAY MONEY BACK GUARANTEE IF NOT COMPLETELV SATISFIED. ONE YEAR WARRANTY ON HARDWARE.

Call or write for FREE product catalog.

#### COVOX INC.

675-D Conger Street, Eugene, OR 97402 Telex 706017 (AV ALARM UD)

TEL: 503-342-1271 FAX: 503-342-1283

Circle No. 109 on Reader Service Card

time interval when it gets to 0. Another array or list is generated by the INILIST subroutine every time a command is processed. This list contains the channel number of every channel that is currently active as defined by certain bits in the individual channel's parameter Once each second, the array. scheduler processes only those channels whose numbers are in this short list rather than all channels. This eliminates the delay waiting for the A/D conversion to finish on channels that have nothing connected to their inputs. Channel 0 is always entered in the list as the first and last channel for temperature conversion.

Another important routine, **GETAD**, actually reads and forms the value from the A/D chip. This routine is the only one that must actually spend time waiting for While it's waiting, something. however, it attempts to send characters out to the terminal. When the A/D chip has completed sampling the selected channel, its EOC (End Of Conversion) signal is detected and GETAD starts accepting digits. The first digit becomes the thousands digit. The hundreds digit is next, then the tens digit, and finally the units digit. Other status information accompanies the thousands digit and is dealt with after a value has been accumulated. If the sign bit is one, then the value is negated. If the value is zero and this is the first of two possible readings for this particular channel, then the process repeats to obtain a valid reading due to the change in polarity anomaly discussed earlier. If the overrange bit is one, a value of 9999 is returned. The digits are presented to the program at approximately 5000 per second, but even if the program misses one, they continuously repeat for the entire time between sampling. In actuality, the program operates fast enough to never miss a digit.

One of the first routines writ-

```

main()

register struct CHAN * C;

/* general integer */

/* dummy variable */

register int i;

/* initialize hardware and software once only */

inimem(1);

/* all variables */

inilist();

/* channel list */

/* PIA and ACIA */

inithw();

foo = (ocount / 2) + 1;

while (ocount >= foo)

/* force half of string out */

outc();

while (gchar() != -1)

/* empty input buffer */

/* main processing loop */

/* handle real-time logging clock */

if (seconds >= 60) {

seconds -= 60;

/* in case someone takes a long time */

if (++minutes >= 60) {

minutes = 0;

if (++hours >= 24)

hours = 0;

}

/* output characters in buffer */

/* output something if possible ●

outc();

/* handle keyboard characters in buffer */

/* characters in input buffer? */

/* deal with them */

if (icount)

gline():

/* handle timeout to resume scheduler */

/* output cr or cr/lf */

schar(CR);

lpos = lbuf; /* reset pointer */

onesec = inhibit = 0; /* resume */

/* handle scheduler */

if (onesec AND !inhibit)

/* clock requesting service? */

sched();

/* do appropriate things */

/* handle completed command line */

/* end of input line? */

/* break it up */

if (eol) (

parse();

if (!(error)) {/* parsed successfully */

c = (struct CHAN *) &ad[chnum];

switch (cmdltr) {

/* see what to do */

case A: /* set clock at value */

i = cmdval / 100;

cmdval = cmdval = (i * 100);

if (i >= 24 OR cmdval >= 60)

goto erred: /* invalid time value */

else {

hours = i; /* set clock */

minutes = cmdval;

seconds = 0:

break:

case 'C':

/* crlf handling */

crlf = cmdval:

break;

/* decimal point */

c->mode &= (-1-3);

c->mode = (cmdval & 3);

break:

```

Listing 1 -- (continued on page 27)

```

case 'E': /* echo handling */

echo = cmdval;

break:

case 'I': /* interval time */

if (cmdval) /* value to use */

c->mode |= IBIT;

else  /* no value, turn mode off */

c->mode &= (-1-IBIT);

c->tleft = c->intrvl = cmdval;

break:

e 'L': /* low limit */

c->mode |= LBIT;

c->lolim = cmdval;

case 'L':

break:

/* once-only mode */

case '0':

c->mode &= (-1-OBITS);

if (cmdval)

c->mode |= OBIT;

break:

p'P': /* parity handling */

parity = cmdval & 3:

case 'P':

break:

/* read a/d */

case 'R':

i = select(0): /* select zero */

getad(); /* bogus reading */

getad(); /* channel zero value */

getad(); /* true value */

getad(); /* bogus reading */

getad(); /* true value */

select(j); /* select previous */

select(j); /* select previous "/

if (i = (c->mode & TBITS))

dotemp(i); /* convert for temperature */

log = (c->mode & WBIT):

dot = (c->mode & DOTS):

outad(chnum,advalue); /* show value */

break:

c 'S': /* status */

c = (struct CHAN *) &ad[0];

sumdig = 1: /* flag for active channels */

for (i = 0; i < NUMCHAN; ++i) {

if (c->mode& SBITS) (

case 'S':

dostat(c,i);

sumdig = 0; /* got one */

/* next */

++c;

if (sumdig) {    /* anything? */

schar('N');

schar('o');

schar('n');

schar('e');

schar (CR);

break:

e'T': /* temp mode */

c->mode &= (-1-TBITS);

case 'T':

cmdval &= 3:

cmdval &= 3:

if (cmdval & 1) /* centigrade ● /

c->mode |= CBIT;

if (cmdval & 2) /* fahrenheit */

c->mode |= FBIT;

break; /* both on means kelvin */

c->mode = UBIT;

case 'II':

c->hilim = cmdval;

break:

```

Listing 1 -- (continued on page 28)

#### THE INTERCHANGE"

Bi-diitional DataMigration Facility for IBM PS/2, AT, PC, PORTABLE and Compatibles

#### Features:

- \*Parallel port to parallel port.

- \*Economical method of file tranefer.

- \*Bi-Directional file transfer easily achieved.

- \*Support8 all PS/2 systems (Models SO, 50, 60, and 80).

- \*Supports IBM PC, XT, AT, Portable and 100% compatibles.

- \*Supports 31/2 inch and 5 If 4 inch disk transfers.

- \*Supports hard disk transfers.

- Supports RAMdisk file transfers.

- \*The SMT 3 Year Warranty.

ONLY \$39.95

#### **FastTrap™**

The pointing device of the future is here!

- \*Two and three axis pointing capability.

- \*High resolution

- trackball for X and Y axis input.

- \*High resolution fingerwheel for Z axis input.

- \*Use with IBM®PC's, XT's, AT's and compatiblea.

- \*Three input buttons.

- \*Full hardware emulation of Microsoft ® Moure.

- \*Standard RS-232 serial interface.

- \*Includes graphics drivers and menu generator.

- \*Easy installation.

- \*1 year warranty.

- \*Made in U.S.A.

ONLY \$149.00

LTS/C Corp. 167 North Limestone Street Lexington, Kentucky 40507 Tel: (606) 233-4166

Orders (800) 872-7279

Data (606)252-8968[3/12/2400 8-N-I)

VISA, Mastercard, Discover Card,

TeleCheck

Circle No. 117 on Reader Service Card

ten was PARSE, the user command parser. This routine separates the typed input line into its various parts and validates each component. PARSE deals directly with the user's input and is very stringent and demanding on exactly what it will let squeeze through. The rest of the software expects good data, so this routine has to ensure that valid commands pass and invalid commands don't.

A command is formed from numbers and letters. You enter a string of optional digits specifying the channel number from 0 to 15, followed by a letter, which can be upper or lower case specifying the actual command to be performed, then another sequence of optional digits which may be preceded by a hyphen to indicate a negative value, and terminated with the Return key. For example, 3 15, 10 L 1500, 10 U -1674, 8 D 3. Blanks may be inserted for readability but they will be ignored. Since 16-bit integers are used for variables within the program, the values must be between 0 and 65535. In the computer's numbering system, 65535 is equal to -1, 65534 equals -2, and so on. To make the box more human compatible, a negative number is accepted and converted to its equivalent 16-bit value. This value is used by some commands where a value is significant; it is ignored by other commands. Any characters other than numbers, letters, and hyphens are eventually stripped from the input data. When you terminate the line by pressing Return, the command is broken down into its three components. If any of the numeric parts are missing, they will default to a value of zero. Any input line that does not meet the above format criteria is ignored and an error indication consisting of a zero value for channel 99 is output to the terminal as 99 0000. If the value presented exceeds the usable range of the particular function, then undeter-

```

case 'W':

/* whether to log or not */

c->mode &= (-1-WBIT);

if (cmdval)

c->mode |= WBIT;

case 'X':

/* miscellaneous functions */

if (cmdval == -1)

inimem(0);

inimem(0); /* reset all channels */

else if (cmdval == -2) (

c = (struct CHAN *) &ad[0];

for (i = 0; i < NUMCHAN; ++i) {

c->tleft = 1;  /* synchronize */

++c;  /* next */

break:

e'Z': /* zero mode, time, limits */

c->tleft = c->intrvl = c->mode = 0;

case 'Z':

c->lolim = c->hilim = c->curval = 0;

break:

/* end switch */

inilist(); /* update channel list */

else (

erred:

log = dot = 0;  /* output as 0000 */

outad(99,0);  /* channel 99 is error */

inhibit = eol = 0; /* accept another line */

got0 loop:

/* loop until power turned off */

} / * end main() */

```

Listing 1 -- (continued from page 27)

```

getad()

/* get a/d reading */

register char * p; /* -> port */

register int bcd; /* BCD digit */

int status: /* negative, overange */

int zflag: /* zero reading flag */

int toc;

/* timeout counter */

p = (char *) PIA; /* setup pointer */

zflag = 1:

again:

toc = -1:

/* set timeout delay */

bod = p[2];  /* dummy read clears flag */

while (!(p[3] & 0x80)) {    /* MSB = end of conversion */

outc();    /* output something while waiting */

if (--toc == 0) (

advalue = 8888; /* timed out waiting for ready */

return: /* that's all, folks */

}

while (!((status = p[2]) & 0x80))

wait for thousands digit */

advalue = (status & 0x08) ? 0 : 10: /* (0 or 1) * 10 */

while (!((bcd = p[2]) \& 0x40))

/* wait for hundreds digit */

advalue += (bcd & 0xF); /* merge it in */

advalue *= 10;

while (!((bcd = p[2]) & 0x20))

/* wait for tens digit */

advalue += (bcd & 0xF); /* merge it in */

advalue *= 10;

```

Listing 2 - (continued on page 29)

Listing 2 -- (continued from page 28)

```

parse()

/* parse command line */

register char * p: /* -> line buffer */

register char * q: /* -> line buffer */

/* value sign */

int sign;

p = q = lbuf:

/* prepare to verify */

while (*p) {

if (*p == '-' OR (*p >= '0' AND *p <= '9') OR

(*p >= 'A' AND *p <= 'Z'))

*q++ = *p; /* only allow these characters */

++p;

\star q = ' \setminus 0';

/* null-terminate */

while (*p >= '0' AND *p <= '9') /* channel number is first */ chnum = chnum * 10 + (*p++ - '0');

if (chnum >= NUMCHAN)

/* invalid channel number? */

/* seems to be */

error = 1;

/* then command letter */

/* was there a command? */

if (*p)

cmdltr = *p++;

else

error = 1;

/* apparently not */

'sign = 0;

if (*p == '-')

/* presume positive value */

/* minus sign? */

/* remember it */

sign = *p++;

if (sign)

/* negate result */

/* end parse() */

```

Listing 3

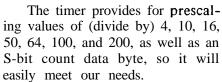

mined results may occur.