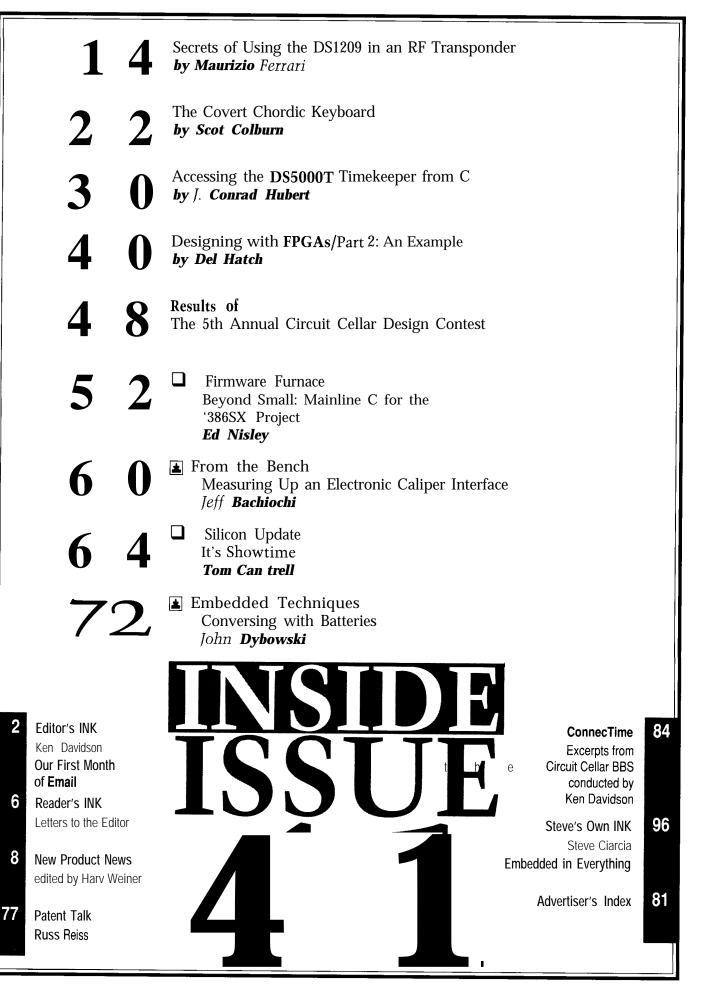

### CIRCUIT CELLAR

# THE COMPUTER APPLICATIONS JOURNAL

December 1993 - Issue #41

I N K ®

### EMBEDDED CONTROL

The Covert Chordic Keyboard

RF Transponder using the DS1209

Embedded Borland and Microsoft C Code

**Design Contest Winners**

\$3.95 U.S. \$4.95 Canada

## EDITOR'S INK

### Our First Month of Email

t has certainly been an interesting month. We made our first successful connection between the Circuit Cellar BBS and our Internet host two days before I wrote my editorial for the last issue. It worked so well that I took a gamble telling everybody about the connection so early in the testing. It turns out my gamble paid off. We've had no major problems with the connection, and usage has blown well beyond my expectations.

The kind of traffic we've been seeing has also been very different from what I expected. Those on the outside coming in have been requesting the information file, the list of available files, and an occasional article-related file. These are all handled automatically by the system. I've also received many very nice notes from readers welcoming us to the outside world.

Users of the BBS looking out have been sending a lot of test messages to try out the new gateway (as I didexpect). Many are sending notes to colleagues with whom they haven't made contact in a long time. A handful have subscribed to mailing lists (which alone can increase the message traffic dramatically and is why I try to keep such subscriptions to a minimum). We even have some parents keeping in touch with kids away at college.

What I haven't seen as much of as I'd hoped for is reader feedback about the magazine and its content. Mail from our readers has always been on the slow side. I expected that opening up a new, more convenient avenue might bring in more letters to the editor, but so far it's still been slow. If you haven't taken the time to request our information file (send Email to info@ circellarcom) or send your comments, drop me a line (ken.davidson@ circellarcom). I'd love to hear from you.

One area where we did get excellent turnout is our Fifth Annual Circuit Cellar Design Contest. We had more entrants this year than last, making the judging even harder. There was a definite increase in PIC-based projects, which shows a tendency toward compact, low-cost solutions to problems that could only be solved with much larger processors not too long ago. I want to congratulate all our entrants and winners on a job well done and encourage you to write full-blown articles about your projects so all of our readers can see just what you've accomplished.

In our features this month, we have two articles that deal with Dallas Semiconductor parts (which always seem to show up in embedded designs). The **DS1209** can be used in an RF transponder, but there are some tricks the data sheet won't tell you; and adding assembly language routines to your C code to access the clock/calendar in the **DS5000T** is easy if you know the right steps. Next, take notes in a crowded lecture hall or on a bumpy bus without anyone knowing it using the Covert Chordic Keyboard. Finally, we conclude our two-part introduction to field-programmable gate arrays.

2 Issue **#41** December 1993 The Computer Applications Journal

### CIRCUIT CELLAR INK. THE COMPUTER APPLICATIONS JOURNAL

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

EDITOR-IN-CHIEF Ken Davidson

TECHNICAL EDITOR Michael Swartzendruber

ASSOCIATE EDITOR Rob **Rojas**

ENGINEERING STAFF Jeff Bachiochi & Ed Nisley

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS John Dybowski & Russ Reiss

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR Lisa Ferry

GRAPHIC ARTIST Joseph Quinlan

CONTRIBUTORS: Jon Elson Tim **McDonough** Frank Kuechmann **Pellervo** Kaskinen

Cover Illustration by Bob Schuchman PRINTED IN THE UNITED STATES

PUBLISHER Daniel Rodrigues PUBLISHER'S ASSISTANT

Susan McGill

CIRCULATION COORDINATOR Rose Mansella

CIRCULATION ASSISTANT Barbara **Maleski**

CIRCULATION CONSULTANT Gregory Spitzfaden

> BUSINESS MANAGER Jeannette Walters

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK. THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0896-8985)(spublished monthly by Circuit Cellar Incorporated, 4 Park Street. Suite 20, Vernon, CT 06066 (203)875-2751 Second class postage paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate U.S A and possessions \$21.95, Canada/Mexico \$31 95, all other countries \$49.95. All subscription orders payable in U.S. funds only, viainternational postal money order or check drawn on U.S. bank. Direct subscription orders and subscription related questions to The Computer Applications Journal Subscriptions, P 0, Box 7694. Riverton, NJ 06077 or call (609)786-0409. POSTMASTER: Please send address changes to The Computer Applications Journal, Circulation Dept P 0 Box 7694, Riverton, NJ 08077

**HAJAR ASSOCIATES** NATIONAL ADVERTISING REPRESENTATIVES

NORTHEAST Debra Andersen (617) 769-8950 Fax: (617) 769-8982 MID-ATLANTIC Barbara Best

(908) 741-7744

Fax: (908) 741-6823

SOUTHEAST Christa Collins (305) 966-3939 Fax: (305) 985-8457

MIDWEST Nanette Traetow (708) 789-3080 Fax: (708) 789-3082 WEST COAST Barbara Jones & Shelley Rainey (714) 540-3554 Fax: (714) 540-7103

Circuit Cellar BBS--24 Hrs. 300/1200/2400/9600/144k bps,8 bits,no parity, 1 stop bit, (2033871-1 986.24001 9600 bps Courier HST, (203) 871-0549

All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects. Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from Jans, descriptions, or information published in *Circuit* Cellar INK

Entire contents copyright © 1993 by Circuit Cellar Incorporated All rights reserved. Reproduction of this sublication in whole or in part without written consent from Circuit Cellar Inc. Isprohibited.

#### Fluke Pickup

I thoroughly enjoyed Derek Matsunaga's article on the data acquisition system for the Fluke 80-series multimeters (October '93). My favorite type of design work is finding unusual ways to use undocumented "features" of hardware, whether at the component or at the system level, and the article struck close to home.

I would, however, like to offer some suggestions concerning the front end of his system. Derek mentions his use of a telephone "microphone" to pick up the meter's acoustic output, and its attendant pickup of EMI/RFI. In my experience, these transducers are not microphones (in that they do not respond to acoustic energy) at all, but are induction coils wound around a permeable core. They respond instead to the varying magnetic field present in the dynamic (moving coil or moving iron) transducer in the earpiece of the telephone receiver. As such, they make very good antennas when properly oriented!

I believe a far better solution would be to use one of the miniature electret capacitor omnidirectional microphone elements, such as the Panasonic WM-60AY sold by Digi-Key, in close proximity to the multimeter's loudspeaker. The necessary supply voltage for the internal FET follower is already available in his system, as is the required amplification, and the microphone's wide frequency response and reasonable sensitivity should yield more than satisfactory results. Stray EMI/ RFI pickup shouldn't be any problem, while stray acoustic pickup will be minimized by the small working distance. Retuning the already-present single-pole highpass filter to just below **16** kHz will provide an extra measure of protection from low-frequency acoustic interference.

Steve Hebrock Akron, Ohio

#### Furnace Safety

renjoyed your article on furnace control in the October issue. This is the sort of article I like seeing (i.e., a comprehensive treatment of the overall subject written so as to be generally understandable). I am going to get me one or more of the R2868 tubes and play!

Without wishing to be critical of the article per se, I would like to say that I do not think such an article should be published without some reference to the danger of explosion and safety measures to prevent same. If at any time, the flame has been lost and a combustible fuel/air mixture has continued to flow into the combustion chamber [CC), even for a short time, there is a strong probability that the CC will remain filled with an explosive mixture for quite some time and any attempt to restart the furnace before the CC has been purged will very likely result in a serious explosion. I have seen a 300-megawatt water tube boiler with all of the furnace wall tubes bent outward by such an explosion,

I appreciate that the design is a simple one, not for industrial use, but I do think any application of the system should include at least a simple protective device which can be easily applied using some fairly easily written software. I believe that a simple pressure switch, capable of sensing the burner channel back pressure just downstream of the fuel feed tube orifices to guard against any possible blockage which restricts combustion air flow but not fuel flow. With such a switch, we could furnish software which would, on sensing loss of combustion air pressure, shut down the furnace and could also be used to validate a preignition CC purge cycle which should be implemented at any starting or restarting of the furnace. I noted in the article a mention of pilot lights, but cannot remember any reference to these being included in the control description. Quite obviously if the furnace control is off/on as described, then the pilots have to be visible to the R2868 tubes and remain lit while the main fuel is off.

The software associated with the combustion air pressure switch could be configured as follows:

1) At power up, if the flame sensor is true (i.e., it says that a flame is present), then under no circumstances should any attempt be made to start the furnace and an alarm of indication signifying lockout should be effected. Possible causes are R2868 tube failure or afterglow due to visible or infrared radiation from some furnace system component which has been heated by furnace combustion. At this point, if the combustion air fan (CAF) is running, then it could be left running-with the fuel valve closed.

2) Whenever it is desired to start or restart the furnace (other than controlled admission of fuel subsequent to a short fuel-off period during which pilots have been continuously ignited), then the CAF should be run [with continuous validation by the pressure switch) for a timed purge period (say about 30 seconds for such a small furnace) in order to remove combustible mixtures from the CC before an ignition attempt.

3) After satisfaction of condition (2) above, then ignition can be attempted by energizing the spark plug(s) and opening the main fuel valve. If a flame has not been detected after, say, 15 seconds, then the sequence should

# **READER'S INK**

be aborted with a new prepurge sequence being run before another ignition attempt.

4) After flame has been continuously present for, say, three seconds, then the spark plug(s) can be deenergized and normal operations assumed.

5) After normal operation is commenced/assumed, then shutdown should be effected on any detection of loss of flame for more than, say, one second or on failure of CAF as signified by the combustion air pressure switch.

Although I hesitate to suggest more complex controls, I think it might also be desirable to implement a simple thermocouple upscale burnout features. If the thermocouple shorts somewhere in the circuit or goes open circuit (either of which would be interpreted as a low temperature without this feature), then this would be interpreted as a high temperature which would restrict fuel flow or fuel valve open time according to which control system was adopted.

**Bill Brown** Katy, Tex.

#### Contacting Circuit Cellar

We at the Computer Applications Journal encourage communication between our readers and our staff, so have made every effort to make contacting us easy. We prefer electronic communications, but feel free to use any of the following:

Mail: Letters to the Editor may be sent to: Editor, The Computer Applications Journal, 4 Park St., Vernon, CT 06066.

Phone: Direct all subscription inquiries to (609) 786-0409. Contact our editorial offices at (203) 8752199.

Fax: All faxes may be sent to (203) 872-2204.

BBS: All of our editors and regular authors frequent the Circuit Cellar BBS and are available to answer questions. Call

(203) 871-1988 with your modem (300-14.4k bps, 8N1). Internet: Electronic mail may also be sent to our editors and regular authors via the Internet. To determine a particular person's Internet address, use their name as it appears in the masthead or by-line, insert a period between their first and last names, and append "@circellar.com" to the end. For example, to send Internet Email to Jeff Bachiochi, address it to jeff.bachiochi@circellar.com. For more information, send Email to info@circellar.com.

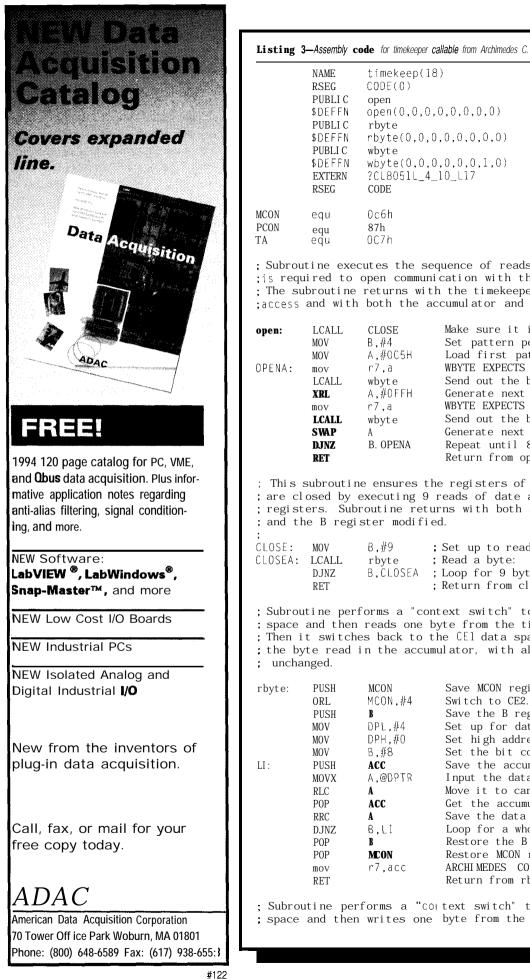

#### LOW-COST DATA ACQUISITION BOARD

ADAC has announced a high-speed data acquisition board for the PC/XT/286/386/486 family of computers. The **5508LC** is one of the lowest priced A/D converter boards available and features 100-kHz A/D throughput with 12-bit resolution. The half-sized board contains eight analog inputs and offers automatic channel scanning.

The 5508LC eliminates hardware and software compatibility problems with a unique Universal Software Interface (USI). USI allows true cross compatibility between software and hardware from different vendors. Through a unique use of custom ASIC technology, USI enables ADAC's plug-in boards to change their software interface to the PC bus. This enables the cards to match the Control and Status Registers of other manufacturers' plug-in boards and become instantly compatible with their software.

USI also provides compatibility with virtually every DOS- and Windows-based data acquisition and control software package available. Some of the software

packages that the 5508LC is compatible with include ADAC's Adlib PC DOS drivers, LabVIEW and LabWindows from National Instruments, Driver LINX Windows driver package, Genesis, ASYST, Control EG, and Keithly/Metrabyte drivers. The 5508LC High-Speed Data Acquisition board sells for **\$245**.

ADAC Corp. 70 Tower Office Park Woburn, MA 01801 (800) 648-6589 Fax: (617) 938-6553

#500

#### SINGLE-USER PC NETWORK

PC InterConnect has introduced the **One-Man-LAN**, a single-user personal computer network. This product is for the individual who works with more than one PC

and would like to have LAN capabilities without the complexity and expense of a conventional LAN. It also can be used to keep an older computer from becoming obsolete.

With One-Man-LAN, a user seated at a main (or primary) PC can access files located on one or more secondary PCs as if they were located within the main PC. Any of the user's PCs can be temporarily converted into a

secondary (or server) PC by typing "OML." Typing "Q" turns it back into a primary PC. The user can also redirect output to a printer attached to a secondary machine.

The One-Man-LAN hardware implements a highspeed, bidirectional serial data communication path that can interconnect PCs point-to- point or through one or more hubs. A PC can be interfaced using either an add-in card or a special parallel port interface module. The data transport medium is an industry-standard 8-conductor cable and is usable with lengths in excess of 100 feet. Extremely fast data rates are maintained; files on a second, third, or fourth PC can be accessed as rapidly as if they were in a network file server.

One-Man-LAN is compatible with sector-level disk utility programs, and such programs handle disk volumes installed on the secondary PC as though they were installed on the primary PC. DOS commands such as DISKCOPY are not usable with conventional LANs, but are fully functional with One-Man-LAN. One-Man-LAN consists of

two half-size ISA add-in cards, a

thin 12-foot interconnect cable, software, and an installation and user guide. Additional cards and cables are available to allow connection of additional PCs. One-Man-LAN sells for **\$199**.

PC InterConnect, Inc.

106 Library Plaza • 15 North 100 East • Provo, UT 84606 (801) 374-8880 Fax: (801) 374-2306

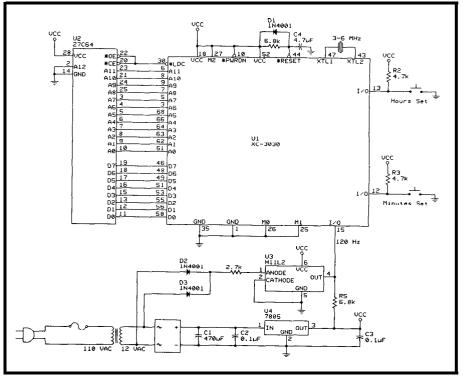

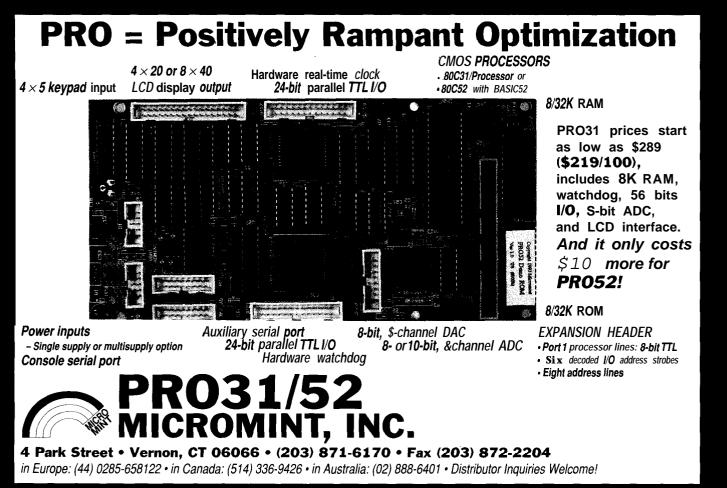

#### FULL-FEATURED MICROCONTROLLER

A powerful, general-purpose, full-function control and data acquisition system has been announced by Intec Inoventures Inc. The Freedom **16** microcontroller offers speed, memory, and I/O capabilities to address virtually any requirement.

The Freedom 16 is built around the 16-bit Motorola M68HC 16, a chip designed specifically for microcontroller applications. Control of specific features such as pulse counting, high-speed inputs and outputs, PWM, and 8 channels of fast 10-bit A/D conversion are included, as well as DSP capabilities. RS-232, RS-485, debug ports, a dedicated LCD and keypad port, 34 programmable digital I/O channels, and an expansion header (containing both Motorola and Intel Read & Write

signals) are also included. With its on-board regulation, the entire board can be powered by a battery or common AC adapter.

Programmability in C and up to 256K bytes each of RAM and flash memory (64K of each is standard) along with an extensive, well-documented library of functions makes for fast, reliable development. By using flash memory and a novel debug cable, the Freedom 16 frees the designer from the need for an expensive emulator and the programming of EPROMs.

Development tools include IASM16—an MS-DOS based editor, cross-assembler, and communications package blended into a single environment. This is combined with the Dunfield C compiler to provide in a single package everything needed for software development in C, assembler, or combinations of the two. Preprocessor, optimizer, and many utilities such as MAKE and TOUCH are included with the package.

The Freedom 16 can be used as an in-circuit debugger/emulator by using P&E's ICD16 software and ICD (in circuit debugging) cable. The ICD software talks to the M68HC16 processor's background mode via the ICD cable which connects to a standard PC printer port on one end and a Motorola 10-pin Berg connector on the target system. With this interface, any target system processor can be turned into its own in-circuit emulator/debugger. The ICD16 runs on any MS-DOS-based PC with 512K RAM and a printer port. The Freedom 16 microcontroller sells for \$299 (U.S.). The controller with all the necessary C software development tools sells for \$499 (U.S.).

Intec Inoventures, Inc. • 2751 Arbutus Rd. • Victoria, B.C. V8N 5X7 • (604) 721-5150 • Fax: (604) 721-4191

#502

#### MOTORIZED WINDOW CONTROLLER

The Win-Trol M-2100 converts virtually any crankoperated window or skylight into a power window. Casements, awnings, vents, and roof or skylight windows can be easily motorized whether they are made of aluminum, wood, vinyl, or composites. The unit can be installed in new construction or retrofitted to existing windows or skylights in commercial or residential applications. The M-2100 is operated with a simple touch-and-run switch.

The conversion system requires one wall switchstyle mounted control unit for each individually operated window/skylight. For groups of windows, one controller will operate as many as three motor-equipped windows sequentially.

The motor is encased in a unit that attaches to the window to be controlled, replacing the crank handle. The

unit has proven extremely reliable and the cover is available in several colors. The wall switch controller unit replaces a standard light switch and is connected to each motor to be controlled.

Other options to the M-2100 include electric latches, rain sensors, battery backup, power distribution for large applications, connections for external triggering (X-10, thermostats, humidistats, home automation systems), and remote control.

The Model 2100 Wall Switch Controller Unit retails for \$170 and the Model 2100 Motor with Cover and Installation Hardware retails for \$180. Quantity discounts are available.

Win-Trol, Inc. P.O. Box 4425 • Helena, MT 59604 (406) 449-6616 • Fax: (406) 449-3666

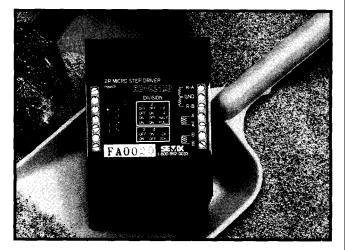

#### COMPACT MICROSTEP DRIVER

SEMIX has announced a low-current and voltage stepper motor driver that features extremely small size and high performance. The **RD-021M8** is an inexpensive driver that is capable of selectable microstepping and provides a selectable clock.

The low current (0.1 to 1.5 amp/phase) makes the RD-021M8 ideal for 11 to **23** frame size stepper motors. The driver accepts voltages as low as 10 V and as high as 40 V, allowing it to be used in applications powered by a **12-V** battery.

The RD-021M8 measures 1.25" x 1.97" x 3.15", allowing it to be designed into tight places. It can execute full, half, quarter, and one-eighth steps to achieve as many as 3200 steps/revolution with a 0.9" motor.

Additional features include photocoupler-isolated inputs, selectable current settings with external resistance, low-voltage protection circuitry, and automatic current limiting (one-half of full current when motor is stationary). The RD-021M8 sells for \$175 and is available at quantity prices.

SEMIX, Inc. • 4160 Technology Dr. • Fremont, CA 94538 • (510) 659-8800 • Fax: (510) 659-8444

#504

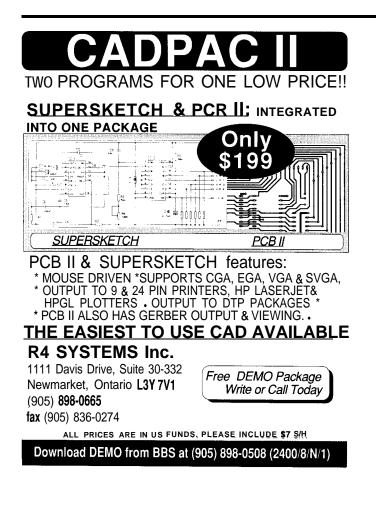

#### SCHEMATIC CAPTURE PACKAGE

Tsien has released an intelligent schematic capture package, **BoardCapture**, for electronics engineers. This powerful new PC-based software tool completes the company's track layout and autorouter packages. The complete bundled BoardCapture/BoardMaker/ BoardRouter system provides an end-to-end design-tomanufacture environment for both prototype and production requirements at a surprisingly low cost.

BoardCapture automates the generation of schematic circuit diagrams, with direct output of netlist data for BoardMaker. Completely hierarchical, the package will accommodate virtually any size design, from simple modules with a few components to the most complex designs requiring A0 or larger schematics.

One of BoardCapture's most powerful features is speed of operation. Everything the designer needs, from

device libraries to the BoardMaker PCB CAD package, resides in memory simultaneously, allowing schematic creation in one fast, fluid operation. This includes smooth scrolling around drawings and multipage diagrams.

Tsien has taken particular care with the look and feel of fundamental schematic creation mechanisms. Connectivity information is available instantly on every element of the schematic by simply pointing and clicking, even if connections are on other drawing pages. Bus and port naming is a further basic procedure that has been automated, freeing the designer to concentrate on the core task.

Software will automatically flag a host of potential errors from overshoots to bad design practices. Also offered are nested undo/redo facilities as well as contextsensitive operation.

BoardCapture comes complete with a comprehensive device library and powerful editing tools, including a graphical library editor for creating free-format symbol outlines, and a table-based editor to simplify the entry of pin details. BoardCapture sells for £395 (approximately \$612 U.S.) and the complete bundle of BoardCapture, BoardMaker, and BoardRouter sells for £795 (approximately \$1230 U.S.).

Tsien (UK) Limited Aylesby House • Wenny Rd. Chatteris • Cambridge PE16 6UT • United Kingdom Tel: +44 (0)354 695959 • Fax: +44 (0)354 695957

#### EPROM EMULATOR

J&M Microtek has released the **ROMY-16 EPROM Emulator,** which is an emulator for EPROMs or static RAMs for 8- or 16-bit microcontroller systems. With the ROMY-16, program code can be downloaded, tested, and results seen immediately without the need to remove the EPROM, reprogram it, and reinstall it in the target system.

The ROMY-16 emulates

EPROMs from 2716 to 27010 and static RAMs from 6116 to 628 128. For EPROM emulation, a PC can be used to read data from and write data to the ROMY-16 memory while the target CPU reads from the memory. For RAM emulation, both the PC and target CPU can access the emulator's memory. The ROMY-16 allows the size and type of memory to be varied without hardwire changes.

For 16-bit microcontrollers, the ROMY-16 is set up

to emulate two EPROMs which share the same address lines but have separate data lines. With S-bit microcontrollers, the lower byte memory is mainly used to emulate the target ROM or RAM. Eight pins (D8–D15) on the higher byte memory can be used as hardware breakpoints to provide triggers to a timer, two interrupts (IRQ and NMI), or to provide a halt signal to the CPU.

The ROMY- 16 EPROM

Emulator sells for \$195 (for EPROM types 2716–27256) and \$245 (for EPROM types 2716-27010). The optional UMPS V2.1 program sells for \$100 each CPU.

J&M Microtek, Inc. 83 Seaman Rd. • West Orange, NJ 07052 (201) 325-1892. Fax: (201) 736-4567

#### PHONE LINE SHARING DEVICE

Telephone Products has introduced Switchboard, a telephone-line sharing device that allows customers to use one phone line for phone, fax, and modem communications, each with an individual number. Switchboard offers an inexpensive, easy way to give a home office the professional image of a larger office-separate numbers for fax and phone, with no clicks or tones.

Using the local phone company's "distinctive ringing" service, Switchboard automatically sends an

x 1.25" case and weighs only 12 ounces. It needs only to be plugged into a phone jack; it requires no additional power and is not affected by power surges or outages. Switchboard works with any combination of two, three, or four devices, including phones, answering machines, faxes, or modems. Using only one phone line, instead of as many as four, can save users hundreds of dollars per year. Switchboard (Model T-4) sells for \$129.00 and is backed by a five-year warranty.

incoming call to the appropriate device. Distinctive ringing services are known in different areas by names such as Smart Ring, Custom Ringing, Personalized Ring, Identa-ring, Intel-a-ring, Ring Mate, Multi-Ring, and Ringmaster.

Switchboard is packaged in a 6.5" x 4.5"

Telephone Products P.O. Box 31203 Seattle, WA 98103 (800) **829-5960** Fax: (800) **829-3940**

#507

| ប                  | SU-MAR                                                                                    |

|--------------------|-------------------------------------------------------------------------------------------|

|                    | ENTERPRISES                                                                               |

| INFO (410)437-4181 | O R D E R S (800)477-4181 ORDERS(410)437-2324                                             |

|                    | EDERAL EXPRESS NEXT DAY AVAILABLE PASADENA, MD 21122                                      |

| x-10               | HOME AUTOMATION MODULES & CONTROLLERS                                                     |

| LEVITON            | HOME AUTOMATION MODULES & CONTROLLERS                                                     |

| STANLEY            | X-10 COMPATIBLE GARAGE DOOR OPENER                                                        |

|                    | MPATIBLE 4 CHANNEL DPTP RELAY \$160                                                       |

|                    | GITAL INPUTS. ANALOG INPUTS & RELAY OUTPUTS TO X-10                                       |

| ECS SOFTWAR        | -                                                                                         |

|                    | ROL SOFTWARE UPGRADE FOR X-10 CP290P<br>SE DUSK AND DAWN CONTROL \$49 95 OR \$20 W/CP290P |

|                    | HOME AUTOMATION BOOK ON X-10 \$18.99                                                      |

|                    | ECTRONICS ONE-FOR-ALL REMOTES FROM \$11.24                                                |

|                    | SURROUND SOUND DECODERS, AMPS & SPEAKERS                                                  |

|                    | PARTNERS COMPUTER SELF POWERED SPEAKERS                                                   |

| FOSGATE            | HTS & IN-WALL SPEAKERS                                                                    |

| PANASONIC          | HYBRID PHONE SYSTEM                                                                       |

| PANASONIC          | PHONES, FAX & ANSWERING MACHINES                                                          |

| MAGNAVOX           | CLOSED CIRCUIT TV SYSTEM \$399 00                                                         |

| RAINDRIP           |                                                                                           |

| PC TELE-VISIO      | N WATCHTVON COMPUTER WITH WINDOWS \$44900                                                 |

| CAPTURE VIDEO FRO  | M TV, CAMERA OR VCR COMES WITH STEREO SPEAKERS                                            |

|                    | CHRISTMAS SPECIALS!!                                                                      |

| ES1400e            | X-10 TWO-WAY COMPUTER INTERFACE \$319.00                                                  |

| WITH LATEST SOF    |                                                                                           |

| CD1200             | INTERACTIVE CD PLAYER WITH COMPTON'S \$499.00                                             |

|                    | ENCYCLOPEDIA INCLUDED \$299 VALUE<br>VRITE FOR CATALOG                                    |

|                    |                                                                                           |

| DEALEF             | RS PLEASE WRITE ORFAX ON COMPANY LETTERHEAD                                               |

|                    |                                                                                           |

### DO YOU NEED CONTROL ?

If you're looking for a temperature sensor that allows your computer to not only monitor the temperature but respond to it, *look no further.*

Temp-A-Chip,, is a solid state temperature sensor - providing truly linear measurement of temperature. The Temp-A-Chip™ is an intelligent, user configurable sensor which interfaces with your computer. No batteries are needed to operate the Temp-A-Chip™, it plugs into any standard RS232 interface.

### Temp-A-Chip

| 🚊 LCD Display                                                                                                                                                         | 💻 Solid State Design |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| 📃 No Batteries Req'd                                                                                                                                                  | RS-232 Interface     |  |  |

| 🚊 Easy To Install                                                                                                                                                     | 📃 Easy To Use        |  |  |

| Can You Afford Not to Call Today?         \$149.00         \$5.00         P&H         (800)         274-8699         Unime Discounts Available (606)         278-4701 |                      |  |  |

#### POWER SUPPLY REFERENCE BOOK

A new 32-page book "Considerations When Specifying Switchmode Power Supplies" is available free of charge from MicroENERGY Corporation's Orlando Engineering Development Center.

This book is packed with useful information on topics such as reliability, agency approvals, EMC, power factor correction, strife testing, power density, and valuable appendices including major safety and quality agencies.

CONSIDERATIONS WHEN SPECIFYING A SWITCHMODE POWER SUPPLY

MicroENERGY, Inc. 745 W. State Rd. 434 Longwood, FL 32750-4909 (407) 831-2000 Fax: (407) 831-I 100

#### #508

#### APPLICATIONS REFERENCE MANUAL

Analog Devices' 1993 Applications Reference Manual is a collection of technical articles, application notes, tutorial material, and design ideas reprinted from a wide variety of sources including trade press articles. This compendium greatly helps any engineer working on analog, mixed-signal, or DSP designs where realworld signals must interface to electronic systems. Topics range from fundamentals (e.g., noise and grounding) through advanced topics (e.g., multichannel systems).

The book is divided into 24 sections such as audio, communications, multiplexers, and switches. The 1993

Applications Reference Manual is available for \$9.95.

Analog Devices, Inc. 181 Ballardvale St. Wilmington, MA 01887 (617) 937-I 428 Fax: (617) 821-4273

#509

| 0<br>μLAN<br>0<br>The 9-Bit<br>0<br>Solution<br>0<br>is the<br>0<br>Answer to                                                    | The Cimetrics Technology<br>9-Bit Solution is a complete<br>microcontroller network<br>(µLAN) that supports the 8051,<br>68HC11, 80186, and many<br>other popular processors. The<br>9-Bit Solution takes full                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0your0Embedded00Network000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000       | microcontroller serial ports.<br>Our flexible software and<br>hardware allow developers to<br>create powerful, yet<br>inexpensive master/slave<br>multidrop embedded controller                                                                                                        |

| 0 0<br>0 PC/XT/AT<br>0 8051<br>0 8096 0                                                                                          | <ul> <li>Up to 250 nodes</li> <li>16-bit CRC error checking with<br/>sequence numbers</li> <li>Low network overhead and low<br/>resource requirements</li> <li>RS-485 interface card for the PC</li> <li>Complete source code included</li> <li>Comprehensive documentation</li> </ul> |

| 0         80C186EB/EC         0           68HC11         0         68HC16         0           0         Z180         0         0 | TECHNOLOGY                                                                                                                                                                                                                                                                             |

<section-header> **3-AXIS STEP MOTOR DRUER**Buy our 6006-DB 3-Motor Drive for \$165

we'll throw in up to 3 motors\* for \$25ea

\*Drives 3 axes independently.

1.25 Amps per phase.

\*Half-step, full-step and wave drive modes. Remote disable.

4 Ampere switching power supply. Adjustable from 5 - 28VDC.

\*Clock and Direction inputs. Led's indicate motion and direction.

\*Complete. Ready to plug-in and run. Includes all cables.

Includes software for running from an IBM PC printer port.

60 oz-in. 1500 steps/sec, size 23, 1.8°/step. *Offer ends December 31st*, 1993

Kursen and Anterestation.

After for our FREE Catalog

### <u>FEA</u>TURES

40

Secrets of Using the DS1209 in an RF Transponder

The Covert Chordic

Accessing The **DS5000T** Timekeeper from C

Keyboard

### FEATURE ARTICLE

#### Maurizio Ferrari

# Secrets of Using the **DS1209** in an RF Transponder

Designing With FPGAs

The DS1209 is a general-purpose wireless-to-3-wire interface that can be used in many applications. Explore its use in an RF transponder, and find out some tricks the data sheets don't tell you about the part.

ontactless identification has wery large commercial appeal due to its enormous range of applications. Automated factory environments, livestock identification, security, and personnel management are just some fields where this idea has already been applied with success. And there are many more, huge, untapped markets. For example, think about replacing the paper tags on your flight luggage with an electronic transponder so conveyor belts would know where to route the baggage at the beginning and at the end of a trip.

With this kind of market potential, it's no wonder chip makers have developed a host of custom, and very specialized, devices. Some, like TI, have come up with extremely small, powerless tags for animal ID (TIRIS), but the resources required to design a fully customized IC are still far beyond the reach of most individuals.

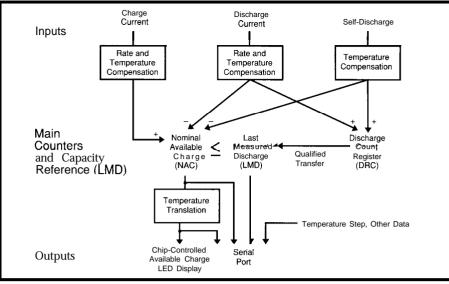

Leave it to Dallas Semiconductor to come to the rescue. In this article, I will explore their DS1209, a low-power device ideal for use as the core of a transponder design. This transponder runs with a small battery, provides read/write capabilities, and has an optional password for secured access.

Dallas Semiconductor has established itself as a major supplier of RAMified real-time clocks for PCs. Their catalog shows an impressive range of other niche devices. One point that makes Dallas very attractive to the small developer is their direct sale policy.

#### THE SYSTEM

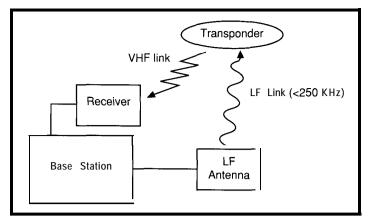

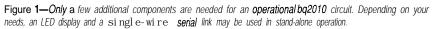

Why would we want a transponder? First of all, humans tend to be lazy. We generally forget things like arming alarms and sliding badges through readers. In fact, we forget to do things whose desired effect is to signal that we exist at a certain place at a certain time. Is there any other possible method we could use to signify our presence or our absence? A transponder system is one approach to solving this problem. A basic transponder system is shown in Figure 1.

The VHF link and receiver provide the means by which the transponder communicates its data to the central or reader station. What I'm describing here is a way to trigger such a transmission and not how to transport data: in fact, the DS1209 will toggle its TX pin according to the level read on its data line. The device is general purpose enough that it will operate regardless of what it is attached to or the transmission medium being used. You could use an infrared delivery system, but you are free to use any method as long as it can be driven by a single pin. For my purposes, imagine that a wire is pulled between the transponder and the base station. It could be a physical

| Number of Pulses |      | Pulses | Command word             |

|------------------|------|--------|--------------------------|

| Min.             | Тур. | Max.   | meaning                  |

| 5                | 20   | 29     | Write 0 or READ          |

| 30               | 40   | 49     | Write 1                  |

| 50               | 60   | 69     | Take RST\High            |

| 70               | 80   | 89     | Return to Inactive State |

| 90               | 100  | 109    | Initialize DS1209        |

Figure 2—DS1209 command words are coded as varying numbers of pulses. Note the "center" value in the allowable range.

Figure 1—A basic transponder system consists of a base station and receiver, a transponder, and an LF antenna.

wire, but you would lose the advantage of a transponder! I will refer to it as a VHF link because it is the most likely solution.

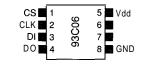

The transponder consists of a loop antenna tied to the 1209, which is linked to a 3-wire device whose output is read back by the 1209 in order to key a VHF transmitter back to the base station. Dallas also manufactures special-purpose devices such as the 1205 and 1204. These only need to be wired straight to the CLK, DQ, RST\, and BATref pins to operate. Intended as secure chips, they feature passwordprotected access and are very expensive, so you might not want to use these unless your security requirements are strict. Also, if you really do require secured access, any 93C06 EEPROM can be used with a bit of effort instead, leading to substantial cost savings.

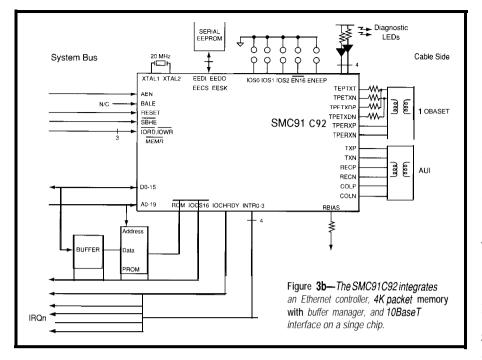

Motorola jargon better, SPI) compatible. Stated another way, this interface gives the user the ability to drive a chip select pin and write to, or read from, a data line with a synchronous clock. It listens for incoming data continuously by monitoring for signal level changes at its A- and A+ inputs, and can receive frequencies up to 250 kHz. Typically, it receives a pulse train from a small loop antenna

tuned to a designated frequency. The antenna outputs are tied to the A+ and A- pins of the device. The 1209 counts the number of pulses it receives via zero-crossing detection, interprets the message, and acts on the 3-wire bus. The LF inputs will wake up with a signal as small as 25 mV peak-to-peak, and the device can be addressed with any unique code out of 65,536. This "radio address" can be stored in internal RAM and can be changed at will or be permanently written.

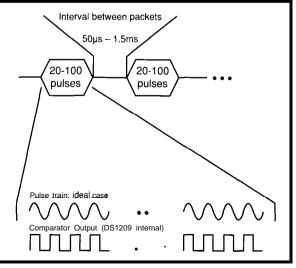

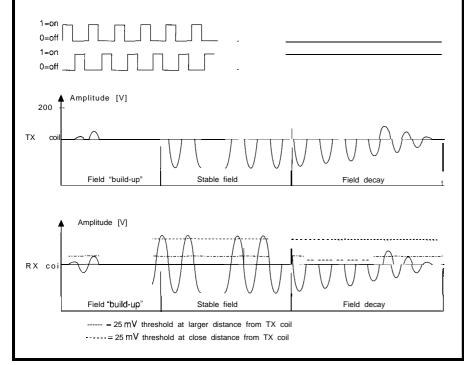

The device recognizes pulse packets at a frequency up to 250 kHz with the protocol described in Figure 2. You can see that every command word has a "center" number and an allowable range. In fact, the pulses are transmitted by a transmit base coil and driven by a square wave that may be generated by a microcontroller. Obviously, the magnetic field will exhibit both a

#### THE DS1209S-B1

Unfortunately, the data sheet will not tell you some facts that turn out to be vital in coaxing the best performance out of the part. I have uncovered some of them in my experiments and will pass them on to you here.

The device converts a wireless protocol into a 3-wire serial link. The circuits in this interface are clock, data, and select. It is also Microwire (or, if you like

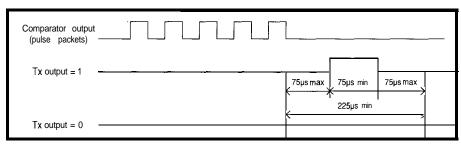

Figure 3-Each 20–100-pulse packet represents a command word. I he interval allows for discriminating between packets.

680x0, 683xx 80x86/88 real mode 80386 protected mode i960<sup>®</sup> family R3000, LR330x0 Z80, HD64180

#### **Features**

- Full-featured, compact ROMable kernel with fast interrupt response

- Preemptive, priority based task scheduler with optional time slicing

- Mailbox, semaphore, resource, event, list, buffer and memory managers

- Configuration Builder utility eases system construction

- InSight<sup>™</sup> Debug Tool is available to view system internals and gather task execution statistics

- Supports inexpensive PC-hosted development tools

- Comprehensive, crystal clear documentation

- No-hidden-charges site license

- Source code included

- Reliability field-proven since 1980

### Count on KADAK.

Setting real-time standards since 1978.

For a **free** Demo Disk and your copy of our excellent AMX product description, contact us today. Phone: (604) 734-2 796 Fax: (604) 734-8114

AMX is a trademark of KADAK Products Ltd. All trademarked names are the property of their respective owners.

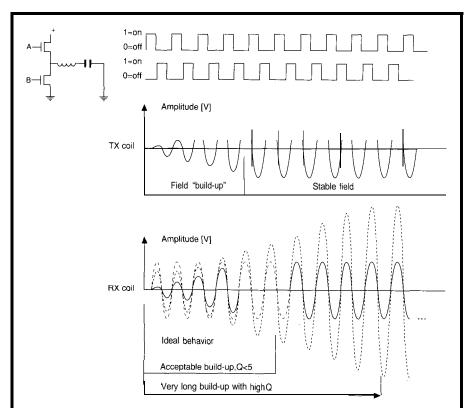

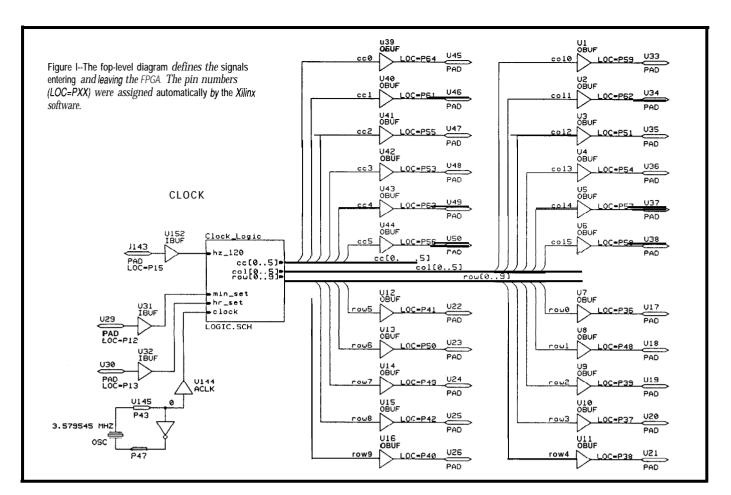

Figure4— The effects of Me cont's Q on the field amplitude growth: ideally, it should be in a stable state from the first p&e (i.e., no build-up time).

build-up time before reaching stable state and a decay at the end of transmission. The behavior of the field's expansion or decay is influenced by various factors, the most important being the way the wave is stopped on the transmitting antenna and the Q of both the receive and transmit coil. The device's effective range is also deeply related to these parameters.

The first notable design issue is that, at a close distance, the receive and transmit coils are strongly coupled. As the transmit field decays, energy is coupled to the receive antenna. This raises the energy level at the A+ and A- pins of the device above the 25-mV threshold. This creates the situation where the decay can be interpreted as valid pulses and leads to two different anomalies:

\*Insufficient dead time (less than  $50 \ \mu$ s, see Figure 3) between commands. This condition creates pulse trains that "merge" in a continuous stream. Remember that the device's receiver wakes up at 25 mV, and it triggers by recognizing a zero crossing rather than relative amplitude. In con-

trast with the 1991 data sheet, the 1209 does not have an internal Automatic Gain Control and its input gates are zero-cross triggered. In fact, the latest specs (1992/1993) do not even mention the AGC.

\*Misunderstanding of command words. This occurs when the number of received pulses becomes greater than the ones generated by the microcontroller, thus crossing the limits in Figure 2.

These effects can be overcome by three combined actions:

• Keep the Q low to minimize build-up time and decay. This has the side effect of decreasing sensitivity (i.e., range), but will make the system much more reliable. In my experience, the small receive coil should have a Q that is less than five. See Figure 4.

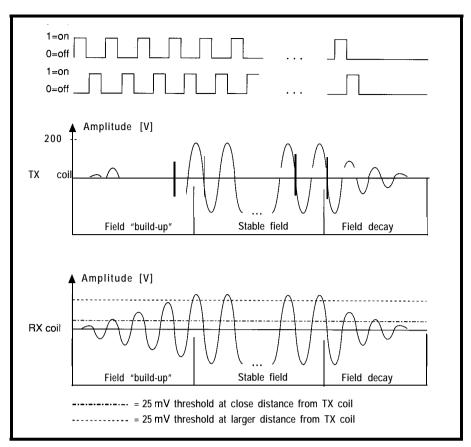

\*Design the driving bridge with logic-level MOSFETs and turn them both off when the packet is sent. This dumps the transmit coil in the shortest time, as shown Figure 5. Leaving one of the drivers on will keep the transmitting antenna oscillating for a

longer period, scrambling the protocol, as explained in Figure 6. (Keeping them both on will cause the magic smoke to come out of the circuit. And as every engineer knows, when the blue puff has escaped from its plastic case, somehow the device ceases to work. This is sure evidence that electronic circuits are based on magic smoke. QED)

\*Wait long enough between packets to give the receive coil enough time to settle down for 50  $\mu$ s between packets.

At longer, end-of-scale distances, the build-up time prevents valid pulses from being recognized, which serves to decrease the effective range. Somehow, this is generally a smaller problem than the previous one. Figure 5 shows a decent compromise based on minimizing the impacts of these two competing design problems.

At this point, we have tuned our antennas, timing circuits, and microcontrollers thinking we might be through with the transmission issues.

### Push the Limits of Real-time Design!

Figure 6-Leaving a driver on worstens field decay: ideally, if should drop to zero at once, instead.

Not yet, though! Two extra quirks must be addressed: power consumption and link directionality.

The DS1209-B1 data sheets state a standby current of 2 µA max. I've checked several devices from a batch of 900 and I've seen it drain from 1.5  $\mu$ A to 5  $\mu$ A with an average of 3  $\mu$ A. This is probably not a problem for most applications. However, there is a more important issue. Recall that the device has a wake-up threshold of 25 mV peak-to-peak. This means any magnetic fields up to 250300 kHz strong enough to wake up the device will keep its internal circuits switching at that field's frequency. This will cause the battery drain to go up to 50 µA for any incoming frequency of approximately 300 kHz. Also, the zerocrossing detection circuit, for the duration of this condition, will never be able to recognize any intelligence the base is attempting to send. Common sources of this kind of interference are computer monitors and televisions.

You will probably need to experiment to discover a "safe" distance. During my tests, I have seen the device stay awake when it is 30 cm from VGA screens. I have no experience with what would happen in the proximity of strong LF transmitters, like LORAN base stations, but I suspect there may be trouble.

#### DIRECTIONAL, LIKE INFRARED...

At this point, we have a radio device that is direction sensitive. This is because the magnetic coupling between the transmit and receive coils varies with the areas that they see of each other. This in turn is a function of  $\cos(\phi)$ , where  $\phi$  is the relative angle between the coils.

I think the laws of physics guarantee there are only two ways to cope with the problem. You can accept it or you can have extra coils with different orientations at different times linking to the receive coil.

However, if you're planning to write to the device as well as read from it, you must realize that moving it while writing may interrupt the communication, causing data loss. There is a critical angle depending on the system's characteristics and operating distance above which the device will not be able to listen to the transmitting antenna. The amplitude is varied by all the factors that affect the design.

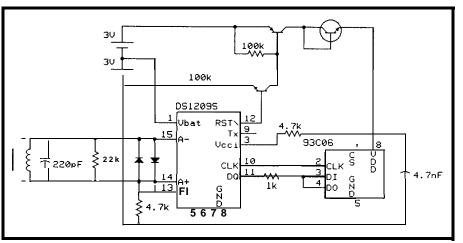

#### THE EEPROM INTERFACE

The communication issues up to this point will apply to any DS1209-

Figure 7—Some tricks in the power section of the circuit are necessary to mix the DS1209, which can operate on 3 volts, and the 93C06, which requires at least 5 volts.

based transponder, no matter what device you want to interface with it. Having overcome them, it's now possible to read and write a very cheap device like the 93C06 EEPROM.

Before we do that, we must take into account a very strict timing specification that the DS1209 imposes. The data sheets specify a 500-ns minimum time for the low state of the clock line. The DS 1204 and DS 1205 are designed to interface directly to the 1209, but as I said before, an EEPROM is much less costly and is perfectly satisfactory for most of the applications one may think of. We also want to design a portable device that will last as long as possible without requiring new batteries. At the time I developed the project, no EEPROMs were available that could satisfy all the ideal requirements, those being:

•Fast clock to comply with the 500-ns specification \*Zero power drain when not in use 02.5-V operation to meet the lowest

allowable  $V_{hat}$  of the DS 1209

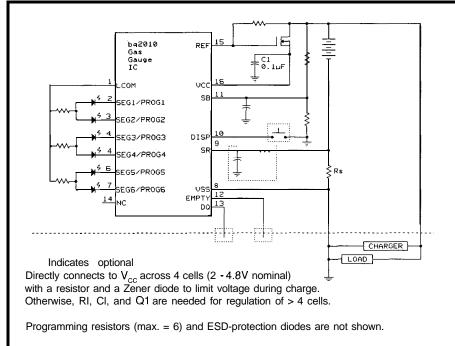

New-generation EEPROMs comply with the first two requirements, but the 93C06 has an  $I_{stdby}$  of 200  $\mu$ A, and its 3-V parts are not fast enough. The choice is to keep the DS1209 in standby at 3 V and the 93C06 off, then use the RST line to switch a second battery in to jump the supply up to 6 V (a diode drop was inserted to limit V<sub>dd</sub> to not more than 5.5 V) while turning the 93C06 on. As the RST line also drives the 93C06 chip select, an additional RC network must be inserted so the EEPROM sees its Chip Select go high after it wakes up (Figure 7).

The circuit works as follows: When you issue the RSTHIGH command to the DS1209, it will pull its RST line to 3 V. This will switch the auxiliary battery in through the transistors, raising the supply voltage on the DS 1209 to approximately 5.3 V. Now, the RST pin and the  $93C06V_{44}$ will reach the same level, and after the delay imposed by the RC network, the memory will see its Chip Select line go to logic one as well. This is the first step to establish communication with the remote device. Now we can issue all the command and data words that we need using the DS1209 Write and Read command words.

The simple Command Words shown in Figure 2 can be combined to obtain information from the 93C06. Next, we need to define a method that can be used as a design for writing the real code. As an example, a simple EEPROM readout of the data at a certain EEPROM location will be carried out through the following steps:

\*Initialize the DS1209 state machine (100 pulses).

\*Wake up the device while masking all the chip select bits (the code for this is 00011000). Alternatively, a DS1209 can be programmed to store a 16-bit value in its standby RAM. A wake-up message can be directed to a specific device using a full 16-bit address or a group of devices using a

| Vbat 1 16 BATref<br>vcco 2 2 5 15 A-<br>Vcci 3 0 14 A+<br>FO 4 6 13 Fi<br>TRI 5 7 12 RST/<br>DQTRI 6 0 11 DQ<br>1 IN/OUT 7 10 CLK<br>GND 8 9 TX |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------|

Vbat: Battery input, 2.5V < Vbat < 4V. NEVER ground it. If Vcci is grounded, this is the power input as well as the backup one. The device will automatically switch its power source to Vcci when it detects it to be >4.5V

Vcco: Will always output the greater of Vbat or Vcci Vcci: Power supply input, 4.5V < Vcci < 5.5V. Ground it when not in use. FO: This output shows the state (on/off) of the

internal comparator

| no n outpuis                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------|

| DQTRI: When pulled to a logic 1, tristates the DQ                                                                          |

| output                                                                                                                     |

| 1 IN/OUT: 1 -wire alternative input/output. Overrides                                                                      |

| the A+, A- comparator inputs                                                                                               |

| GND: Ground                                                                                                                |

| TX: This output shows the value on the DQ line of the<br>d-wire interface. Typically, it will drive the<br>VHF transmitter |

| CLK, DQ, <b>RST</b> : Serial clock output, bidirectional data link, and chip select line to the d-wire                     |

| decvice                                                                                                                    |

| FI: Driving FI will turn the comparator on/off                                                                             |

| At, A-: Coil inputs                                                                                                        |

| <b>BATref:</b> Specifically designed to provide power to a Dallas d-wire device such as the 1204 or 1205                   |

| CS: Chip Select<br>CLK: Serial Clock<br>Di-Serial Data In                                                                  |

|                                                                                                                            |

TRI: When pulled to a logic 1, tristates the DQ, CLK,

DCT output

Figure 8—The DS1209 wireless-to-3-wire chip and the 93C06 serial EEPROM can be combined to make an inexpensive **RF** transponder with security.

DO: Serial Data Out

Vdd. GND: Power Lines

subset address. Obviously, the DS1209-specific address must be programmed into the device before using this feature. There is a specific procedure in the data sheet for this operation. I suggest you master the basics by writing the code for the standard wake-up mode first. Before long, 16-bit addressing will become a straightforward matter as your experience grows.

\*Transmit a dummy address or transmit a real address for selective wake-up.

\*Check for the existence of a DS1209 in the proximity using the "beacon" feature. To do this, send 80 pulses, followed by 20, then by 40. If there is any device within range, it will start modulating its transmit pin with a 1.6-kHz square wave.

\*Stop the beacon by issuing 60 pulses.

•The EEPROM readout can now begin. The 93C06 protocol needs a trailing 01, so the first two commands should be constructed to provide that sequence.

•Next, you need to transmit the EEPROM address to be read (MSB first). In other words, to specify the address of interest, you need to output a sequence of bits that represents the address. The first bit sent is the MSB of the address followed by the LSB.

• The DS1209 will now reply at every read command by raising its transmit pin if the value read from the 93C06 is a one.

•To complete the read of this address, your code will need to test the

Figure 9—To complete the read of an address in the 93C06, the code needs to test the receiver in the interval between the read commands to determine if the DS1209 has read a one or a zero.

receiver in the interval between the read commands to determine if the DS1209 has read a one or a zero. The output timing is described in Figure 9.

#### CONCLUSIONS

I have shown you one way to apply the DS1209 in some of your designs through this illustration of a simple transponder circuit. As I have pointed out, this project is a matter of compromise. If you want to use the longest possible range, you must be ready to sacrifice shortest distance recognition, and vice versa.

Power consumption is low enough to guarantee it will work for two years when powered by a 2032 cell as long as you are not in the habit of leaving your device close to televisions or computer monitors. Its internal RAM code can be used to a good advantage to carry identification codes of all types.

Another possible application for this device is to interface it with a microcontroller through a synchronous serial port. This would allow cheap radio transmission of data, albeit at very slow rates, for certain kinds of niche products. Adding a 1204 or 1205 to the 1209 enables you to build a secure transponder for access control and limited data carriage. It's a matter of taste. The device is a bit quirky, but flexible enough to be used in a wide variety of situations.

Maurizio Fettari graduated with an M.S. in Electrical Engineering from Bologna University (Alma Mater Studiorum, oldest University in the world) in Italy. He is a software engineer for Magneti Marelli.

#### CONTACT

Dallas Semiconductor Corp. 4401 S. Beltwood Pkwy. Dallas, TX 75244-3292 (214) 450-0448 Fax: (214) 450-0470

401 Very Useful 402 Moderately Useful 403 Not Useful

# The Covert Chordic Keyboard

How long would it

And how many

take you to type this?

fingers do you use to

type? One finger or

not, you don't have

to be a musician to

keyboard that fits in

appreciate the

benefits of a

your palm.

FEATURE ARTICLE

Scot Colburn

he covert chordic keyboard is a small, one-handed, 2-line by 40-character, LCD-based text editor. Why is it covert? The entire machine can be hidden inside a jacket. The idea to have a small, discrete text entry device came to me while using an NEC PC-8201 (the Japanese cousin of the TRS-80 Model 100) to take notes in a FORTRAN class. I was getting stared at, and the "tap tap" sound of the keys was decibels above the soft "scritch scritch" of people writing notes. Also, I took the bus a lot in those days and often wanted to use the time to write. but bus-written notes are barely legible, and they need to be transcribed to the computer later anyway, so what's the point? But a small onehanded terminal could be used to write if I were on the bus, in class, or even while walking home.

The device uses a five-button keyboard that is held in the palm of one hand-each finger poised over its own button. Characters are formed by *chording,* which is defined as pushing several buttons at once. Text is displayed on a 40-character by 2-line LCD display. Lines longer than 240 characters can be edited by inserting, overwriting, moving backward or forward, and scrolling the tiny screen horizontally. Only 31 different chords are available, so escape sequences and chord multiples are used to give commands, enter less-common characters, move to different lines, or toggle between upper and lower case.

My original plan was to use some sort of tactile feedback to "read" the text. But when a friend offered me this tiny 80-character LCD, I just knew that was the way to go. This small stick of a display can be attached to the forearm with elastic, mounted to the hand-held portion of the terminal, or just laid on a desktop. With a backlight, this display can be read nearly anywhere, just like a watch.

#### THE ALPHABET

The chordic alphabet is designed to be as ergonomic, efficient, and easy to use as possible. Like Morse code, the most frequent letters are the easiest to chord. The four most common letters, "E," "T," "A," and "0," use one-finger chords (see Figure 1). The space character is more common than any of these, so it uses the fifth one-finger chord. I consider chords using groups of adjacent fingers to be easier to form than separated finger chords, so the letters "N," "H," "S," and "I" (which are members of the group consisting of the next most common letters) are formed using adjacent fingers.

Things get trickier when deciding precisely which chords go with which letters. "E" is most often followed by a space, for example, so the buttons in their chords are placed next to each other. "THE" is one of the most common triplets in English, so the chords for those three letters are designed to naturally and easily follow each other. "RE," "ER," "ON," "TO," and "IS" are other common doublets that are easy to chord. Of course, many other doublets occur that aren't so easily resolved. "IN," "AN," or "AT," for example, aren't adjacent in the current chording scheme. After several days of juggling letter, doublet, and triplet frequencies, I arrived at what you see here. Perhaps a computer could balance all these factors nicely. I'm sure Samuel Morse would have done a better job.

Some letters are so uncommon that two of them share one chord. As any Scrabble player will tell you, Q, J, X, and Z are the highest scoring letters because they are so difficult to use (each one is a lo-point letter). On the chordic keyboard, the letters "Q" and "X" share the same chord. If the chord for "Q" is made twice, then the first "Q" is erased and an "X" pops up. The same goes for "J." Two "J" chords make one "Z." The only way to chord a "QQ" sequence is to chord one "Q," then any character besides "Q," then backup to erase that letter, and then form the second "Q." I couldn't find "QQ" in Funk & Wagnalls and I believe J.J. Mcabe's has periods in it, so neither "JJ" nor "QQ" should pose a problem. The comma and the period each have their own chord, since they share frequencies with B and W. But all other punctuation is bundled under one punctuation chord. After the comma and the period, the most common punctuation mark is the apostrophe ('). Repeating the punctuation chord erases the last punctuation mark and replaces it with the next most frequent punctuation mark. Fourteen punctuation marks are revealed by successive repeats of the punctuation chord.

| Cha:<br> <br> | racter<br>Thumb<br>Forefinger<br>Middle finger<br>Ring finger<br>Pinky finger<br>I        <br>1 0 0 0 0<br>1 1 1 0 1<br>0 0 1 1 1 1001 t                                                                                                                                                                                            | Chai<br> <br> <br> <br> <br> <br> <br>r<br>s                | racter<br>Thumb<br>Forefinger<br>Middle finger<br>Ring finger<br>Pinky finger<br>       <br>1 0 1 1 1<br>0 1 1 1 0<br>00010 01100                                                                               |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e<br>f<br>g                                                                                        | 00100<br>010 01                                                                                                                                                                                                                                                                                                                     | u<br>v                                                      | 0 1 1 1 1<br>1 0 1 0 1                                                                                                                                                                                          |

| h<br>i<br>k<br>1<br>m<br>n<br>o<br>P                                                               | 0 0 1 1 0 0 1 0 1 1 w<br>110 0 0<br>10110 z<br>0 0 1 0 1 punctuation<br>11100 ex<br>0 1 0 1 space<br>0 0 0 1 1<br>00001 CR-L;<br>11010                                                                                                                                                                                              | o n<br>SC                                                   | $\begin{array}{c} (2*q) (2*1 \ 0 \ 1 \ 1 \ 1 \ 1) \\ 1 \ 0 \ 1 \ 0 \ 0 \\ (2*j) (2*1 \ 0 \ 1 \ 1 \ 0) \\ 1 \ 0 \ 0 \ 1 \ 1 \\ 1 \ 1 \ 1 \ 0 \ 0 \\ 0 \ 1 \ 0 \ 0 \ 1 \\ 0 \ 1 \ 0 \\ 1 \ 0 \ 0 \ 1 \end{array}$ |

|                                                                                                    | Numbers Mode (tog                                                                                                                                                                                                                                                                                                                   | gl ed                                                       | with Esc/n)                                                                                                                                                                                                     |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>2<br>8<br>9                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                | a<br>b<br>c<br>d<br>f                                       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                            |

|                                                                                                    | Escape Codes                                                                                                                                                                                                                                                                                                                        |                                                             |                                                                                                                                                                                                                 |

| Esc.<br>Esc<br>Esc<br>Esc<br>Esc<br>Esc<br>Esc<br>Esc<br>Esc                                       | /b Backspace destructive<br>/i Initialize (clear) c<br>/j Jump to MONITOR-51<br>/l# move Line # to curren<br>/n Numbers mode toggle<br>/0 Overwrite/push-right<br>/s Shift toggle upper/<br>/t Toggle serial port on<br>/u Upload current line t<br>/w toggle Windows (leave<br>ly move cursor to beginm<br>/. move cursor to end o | urrer<br>nt wi<br>togg<br>lower<br>or<br>o se<br>cur<br>ing | nt page<br>ndow<br>gle<br>c case<br>off (to save 10 mA!)<br>rial port<br>rent line displayed)<br>of current line                                                                                                |

Figure 1-A characteristic of the chordic alphabet is ifs premise of accessing the most common letters of the alphabet. The table above is a summary of the finger chord combinations for the alphabet as well as numbers and frequently used punctuation marks. The numbers are easier yet, at least for a computer nerd. Once "Numbers Mode" is toggled with an Esc/N, the numbers themselves are binary, except for zero, which is just a thumb-press. Cursor moves found here are identical to an IBM PC keyboard.

Learning the chordic alphabet is easier than one would think. Once a few sequences are committed to memory, remembering the rest of the alphabet is simple. Learn the words "IS" and "THE," for example, and you're a fifth of the way there. Remembering 3 1 different character chords is much easier than remembering, say, 31 flavors of ice cream.

#### MUSIC LESSONS: THE CHORDS

Entering a chord is a bit different than typing. A typewriter is sensitive to key presses, whereas the chordic keyboard is sensitive to key releases. A chord is entered when a button in that chord is released. If the chordic keyboard listened to button pushes, then a "W" might become "TNGW" which is a 4-character string of three decreasingly common characters with a "W" tagged on at the end.

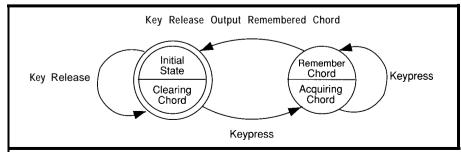

The chordic keyboard enters a character by watching the buttons being pushed and waiting for a button release. When a release occurs, it knows that the user is moving to a different chord, so it records the last combination of pressed keys as the previously impressed chord. Now the keyboard is watched for another key press; subsequent key releases are all ignored until a key press signals that the user is beginning to chord another character. The state diagram in Figure 2 describing this algorithm is perhaps easier to understand.

Moving from one chord to another doesn't necessitate releasing all the buttons and then pressing a new chord onto the keyboard. For example, The word "IS" can be spelled by making an "I" chord, releasing only the thumb to enter the "I," then pressing with the middle finger to form an "S," then releasing either finger to enter the "S."

#### THE LINE EDITOR

The chordic keyboard can store and edit 31 "lines" of text. Each line

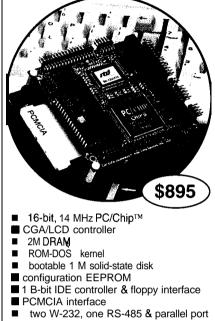

*cpuModule*<sup>™</sup> *is the first <u>complete</u>* 100% PC-compatible **PC/104 single board computer** measuring only 3.6" by 3.8"!

- XT keyboard & speaker port

- watchdog timer

- ■+5 volts only operation

Designed for low power applications, the CMF8680 draws <u>one watt</u> of power, which drops to <u>350 milliwatts</u> in sleep mode, <u>125 milliwatts</u> in suspend mode. Free utility software lets your application boot from ROM!

RTD also offers a complete line of *PC/l* 04 peripherals for expansion:

1.8" hard drive & PCMCIA carriers

12-& 14-bit data acquisition modules

opto-22 & digital I/O modules

VGA CRT/LCD interface

For more information: call, write or fax us today!

Place your order now and receive a CM102 PCMCIA carrier module FREE!

Real Time Devices, Inc.

P.O. Box 906

State College, PA 16804

(814)

234-8087

Fax:

(814)

234-5218

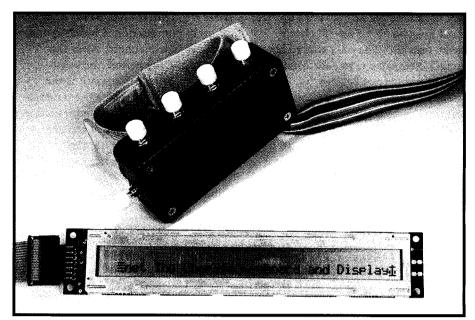

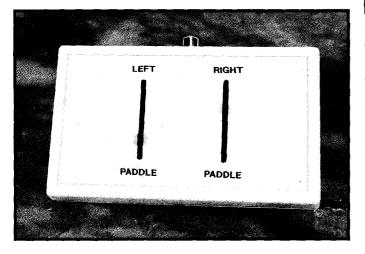

Photo I--The Chordic Keyboard is made up of an off-the-shelf box, five buttons, and a ribbon cable that goes to the controller. A Velcro strap holds the keyboard in your palm. A P-line by 40-character LCD display offers a compact window onto already-typed text to allow reviewing and editing.

can contain up to 240 characters. Lines are displayed on one of the LCD display lines, so two lines may be viewed at once. The Window command (Esc/W) will pop the cursor between the two lines displayed on the LCD. Chorded characters appear at the cursor, just like on a word processor. The Overwrite (Esc/O) toggle changes between an insert-by-pushing-right cursor (an underline cursor) and a write-over cursor (blinking block). If the Insert cursor is active when a line becomes full, the Overwrite cursor automatically appears. The backspace chord (all five buttons held down) can be toggled between destructive and nondestructive modes using the Backspace toggle command (Esc/B). Two escape codes, Esc/Y and Esc/. (escape period), move the cursor to the beginning or the end of the next line, respectively.

The 3 1 lines are instantly accessible with the Line command (Esc/L). Following the line command with any of the 3 1 available chords makes that line instantly pop up on the current window (top or bottom) of the display. These lines cannot be deleted, but they can be erased via the Init command.

#### THE MACHINE

The machine is based on Iota Systems' EC-32 80C32 board. Up to 92K of memory can be placed on the board. The upper 32K is mapped to both program and data space, while the lower 32K is mapped in the standard 805 1 Harvard configuration, doubled so that data accesses come from RAM and code accesses from EPROM. All the RAM is battery backed with an onboard lithium battery. I/O devices live in the top 4K, so the top half of the memory is limited to 28K. It should be

gure 2—I he primary action of the Chord/c Keyboard can be described with a two-node state diagram. Characters are entered upon the first key release rather than a key press as with traditional keyboards

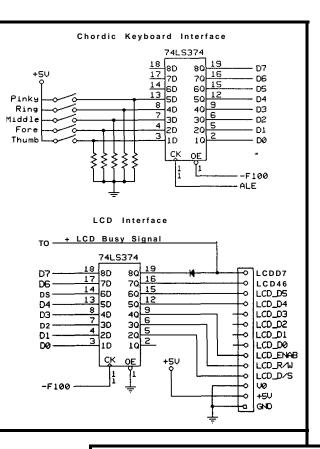

Figure **3**—The keyboard consists of nothing more than some push **buttons**, pull-down resistors, and a **latch**. The LCD interface is just another latch.

noted that this processor platform was my choice for the project. Any other processor platform could be used, however, as long as it has the proper number of I/O lines available and can support the same level of I/O and bit-level operations that I used.

The hardware side of this project is simple (refer to Figure 3). Only two latches and a diode are needed on the board. One

latch gets the keyboard data, and the other latch, in conjunction with the diode, handles output to the LCD. The chordic keyboard is housed in one of those ubiquitous blue boxes from Radio Shack, which I chose because it fit well in my hand. Five tactile feedback push buttons are arrayed around the outside of the box. Inside, five 10k resistors pull down the data lines and a ribbon cable carries all the signals to the latch on the board.

The software side is a bit more involved. When I bought this board I bet the same friend who lent me the LCD that an 8051 stacked up easily in processing power to, perhaps, a 6502. He nodded his head wisely and said, "You'll see..." Believe me, I have seen. The 8051 is a bit of a pain to program, but the bit-level operations are a pleasure, and easy access to the internal RAM makes up for the sometimes difficult to access registers.

The low-level interface code for the LCD (as well as the latch-anddiode interface) come nearly directly from Iota Systems' Application Note #1. This code initializes the LCD to the nybble-wide protocol and provides routines for getting data into the LCD.

ر در د اردان<del>ه در</del> در د

The chordic and serial input routines are interrupt driven, which means the processor can enter a lowpower idle between keyscans and characters. The serial interrupt routines can be ring-buffered in internal RAM, but I haven't found buffering to be necessary; I can't type more than 20 WPM on the chordic keyboard yet. In fact, the monitor program I'm using is incompatible with interrupt-driven serial output, so to make debugging easier I have removed the buffering code until it appears necessary.

Each line of text is stored in a page of memory so accesses to the external RAM can be addressed using the RO or R1 registers rather than DPTR. Each line is separate and no method of transferring text from one line to another is implemented, although it could be. When a line is exited, its cursor position is stored, so text entry can be started again exactly where it left off. If the buffer fills up

Listing 1—Key scanning is based on a timer interrupt, which also serves to debounce the button presses. The main process simply waits for a semaphore from the interrupt service routine.

|              | sleeps until semaphore fro<br>systems wakes it. | m serial                                                        |

|--------------|-------------------------------------------------|-----------------------------------------------------------------|

| j bc         | KeyReady,MProcChar<br>RI,MDRecieve              | ; Does KeyScan have key ready?<br>; Does SBUF have a character? |

| setb         | -                                               | ; stop clock til next int                                       |

| 0000         | MainLoop                                        | ; Do it again                                                   |

| MProcChar    | 110 111 200 p                                   | , 20 It ugain                                                   |

| acall        | ProcessChar                                     |                                                                 |

| sj mp        | MainLoop                                        |                                                                 |

| MDRecieve    |                                                 |                                                                 |

|              | DumbRecieve                                     |                                                                 |

|              | MainLoop                                        | 2                                                               |