CIRCUIT CELLAR INK®

# THE COMPUTER APPLICATIONS JOURNAL September 1994 Issue #50

Meet the M68HC16 Add DRAM to an 8031 ISA, EISA, MCA, VL, and PCI Explained Motorcycle Sensor System Supercaps for Memory Backup

# **EDITOR'S** INK

### The Golden Issue?

elcome to our fiftieth issue! When we started this as a 40-page bimonthly with no ads back in 1988, I never would have dreamed I'd see the fiftieth issue go out the door as a 96-page monthly with a group of dedicated advertisers and tens of thousands of faithful readers. As a bonus, we've filled this issue with five feature articles plus our regular columns to make number 50 a bang-up issue. Thanks to our authors and readers, we can continue to bring you first-class material each month. Here's to another 50.

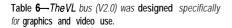

Continuing in the Circuit Cellar tradition of treading into new areas, I'm pleased to announce that starting with the January '95 issue, we will be putting out a quarterly special entitled Home *Automation and Building Control.*

HABC won't be just another glossy production that talks down to naive consumers nor will it cover \$50,000 installations in multimillion-dollar homes. What we will be covering is home automation technology that you can apply to your own home, whether it be off-the-shelf products, installation techniques, design ideas, or complete projects. We will also be looking at the commercial building control side to find out what is happening in that sector and how it might also be applied to the home. You've come to expect Circuit Cellar to get down to the nitty-gritty and tell it like it is, and HABC won't be an exception. There is no such thing as "too technical" when it comes to our readers, so we won't be holding anything back.

If you are already a regular reader of the *Computer Applications Journal, you* don't have to do anything special to receive *HABC*. It will be included in the center of the January, April, July, and October 1995 issues of *CAJ*.

In the meantime, I'm looking for authors to write about all aspects of the home automation industry. Whether it be your experiences with an **off**the-shelf product, your own design, or tricks of the trade, we want to hear from you. While we may use the Circuit Cellar HCS as the basis for some projects we write about here, we want to cover all systems currently on the market. Unlike some other industry magazines that only seem to recognize control systems advertised in their pages, we will be providing an equal, unbiased platform for all to use.

Home automation **is** always a popular topic among our readers (and I know it's popular among our staff). However, it still suffers from lack of consumer awareness and lack of decent user interfaces. It's all of our **job**—we the pioneers-to help set the stage for acceptance by the masses. A lot of work needs to be done before that can happen, though. We strive to be the medium to carry that work, but we still need your help to fill it. Feel free to contact me with your ideas by E-mail at **ken.davidson@circellar.com** or using any of the other methods listed on page 6.

This should be fun....

# CIRCUIT CELLAR I K

### THE COMPUTER APPLICATIONS JOURNAL

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

EDITOR-IN-CHIEF Ken Davidson

TECHNICAL EDITOR Janice Marinelli

ENGINEERING STAFF Jeff Bachiochi & Ed Nisley

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS John Dybowski & Russ Reiss

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR Lisa Ferry

GRAPHIC ARTIST Joseph Quinlan

CONTRIBUTORS: Jon Elson Tim McDonough Frank Kuechmann Pellervo Kaskinen PUBLISHER Daniel Rodrigues

PUBLISHER'S ASSISTANT Sue Hodge

CIRCULATION COORDINATOR Rose Mansella

> CIRCULATION ASSISTANT Barbara **Malesk**i

CIRCULATION CONSULTANT Gregory Spitzfaden

> BUSINESS MANAGER Jeannette Walters

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK, THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (203) 875-2751, Second class postage paid at Vernon, CT and additional offices One-year (12 issues) subscription rate U.S.A. and possessions \$21.95. Canada/Mexico \$31.95. all other countries \$49.95. All subscription orders payable in U.S funds only, via international postal money order or check drawn on U.S. bank. Direct subscription orders and subscription related questions to The Computer Applications Journal Subscriptions, P.O. Box 696. Holmes, PA 19043.9613 or call (600) 269-6301. POSTMASTER. Please send address changes to The Computer Applications Journal, Circulation Dept P.O. Box 696, Holmes, PA 19043-9613

Cover Illustration by Bob Schuchman PRINTED IN THE UNITED STATES

**HAJAR ASSOCIATES** NATIONAL ADVERTISING REPRESENTATIVES

NORTHEAST & MID-ATLANTIC Barbara Best (908) 741-7744 Fax: (908) 741-6823

SOUTHEAST **Christa Collins** (305) 966-3939 Fax: (305) 985-8457

> MIDWEST Nanette Traetow (708) 789-3080 Fax: (708) 789-3082

WEST COAST Barbara Jones & Shelley Rainey (714) 540-3554 Fax: (714) 540-7103

Circuit Cellar BBS—24 Hrs. 300/1200/2400/9600/14.4k bps,8bits,no parity, 1 stop bit,(203) 871-1988;2400/ 3600 bps Courier HST, (203) 671.0549

All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers

Circuit Celtar INK makes no warranties and assumes no responsibility or liability of anykind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans descriptions, or Information published in Circuit Cellar INK

Entire contents copyright© 1994 by Circuit Cellar Incorporated. All rights reserved. Reproduction of this sublicationin whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# **READER'S** INK

#### Sony Documents

In response to the request listed in "Reader's INK," CAJ 48, I think some readers (besides Mr. Khan) might be interested in how to get technical documents from Sony. Here are some phone numbers:

Customer Relations: (800) 282-2848 Camera Tech Info: (800) 222-7669 Document Ordering: (800) 488-7669

The sequence of calls is Customer Relations to get the phone number of the tech info line you need, Tech Info to get the name of the document you need, and then Document Ordering to actually get the document.

In Mr. Khan's case, one of the documents he wants is "Protocol of Control L/LF," Sony part number 9-972-453-11. This is a 26-page pamphlet, sold as a service manual.

Peter Lengsfeld, Addison, IL Bill Fuhrmann, bill.fuhrmann@tstation.mn.org

Mudassir Farhat Khan is asking for Sony camcorder control protocols in "Reader's INK," *CAJ* 48. There is a file on the Circuit Cellar BBS in area 17 called SONYCTL.ZIP. It is possible to read out the protocol (or part of the protocol) from the assembly listing.

#### Gyorgy Komarik

via the Circuit Cellar BBS

#### **Encrypted Program?**

Got the new issue of the magazine yesterday (CAJ 48). Murphy seems to have been present when page 38, Listing 3 was composed.

Line 55 is missing. You need to close the FOR loop begun in line 40 with: 5 5  $\,$  NE X T  $\,$  N.

Line 130 reads: 130 FOR I = J TO MLEN. When you execute line 130 the first time, J = 26. Thus line 130 should be: 130 FOR I = 1 TO MLEN.

Interesting article, but the use of **G0T0** to exit **F0R** loops several times in Listing 3 on page 38 shows why the structured programming crowd dislikes BASIC. While I realize that at least one reason Microsoft GW-type BASIC is used in programs accompanying articles is that everybody who has DOS through 3.3 has it, I find the limitations of that kind of BASIC overcome the virtues-if there are any.

The use of I N PUT \$ to get the encryption key letter [line 35) allows accidental input of more than one character, and the unterminated FOR loop is clumsy compared with Pascal even if the N E X T isn't omitted. In Pascal the use of a set makes the process easier to write and easier to comprehend when reading the source code.

```

procedure Test:

var

C: char;

N : short:

begi n

Read(C);

if not (C in ['a'..'z', 'A..Z']) then begin

ClrScr; {not alpha, so bomb1

writeln('You idiot! Follow instructions!')

end

else begin {char is alpha, so continue}

N := ord(C);

{convert alpha to num 0\mathchar`-251

case N of

ord('A')..ord('Z'): Dec(N, 65);

ord('a')..ord('z'): Dec(N, 97)

end; {case}

{rest of program)

end

end;

```

Call **Test** from a main program.

Frank Kuechmann via the Circuit Cellar BBS

#### **Contacting Circuit Cellar**

We at the Computer **Applications Journal** encourage communication between our readers and our staff, so have made every effort to make contacting us easy. We prefer electronic communications, but feel free to use any of the following:

- Mail: Letters to the Editor may be sent to: Editor, The Computer Applications Journal, 4 Park St., Vernon, CT 06066.

- Phone: Direct all subscription inquiries to (609) **786-0409**. Contact our editorial offices at (203) 8752199.

Fax: All faxes may be sent to (203) 872-2204.

- **BBS:** All of our editors and regular authors frequent the Circuit Cellar BBS and are available to answer questions. Call (203) 871-1988 with your modem (300-I 4.4k bps, 8N1).

- Internet: Electronic mail may also be sent to our editors and regular authors via the Internet. To determine a particular person's Internet address, use their name as it appears in the masthead or by-line, insert a period between their first and last names, and append "@circellar.com" to the end. For example, to send Internet E-mail to Jeff Bachiochi, address it to jeff.bachiochi@circellar.com. For more information, send E-mail to info@circellar.com.

#### "ZERO POWER" KEYBOARD ENCODER

USAR Systems has announced the first PS/2compatible keyboard encoder which consumes hardly any power. The GreenCoder IC extends system battery life, has a small form factor, and is easy to integrate.

The UR5HCFJL GreenCoder regulates power consumption based on the keyboard's activity. Active, the keyboard uses only 2 mA; inactive, it consumes less than 2  $\mu$ A. To further reduce keyboard power consumption, the encoder provides an innovative LED dimming feature-when the keyboard is not in use, the LEDs gradually fade.

The UR5HCFJL offers these low-power advantages without compromising functionality or adding to the complexity of the system. The IC, which requires no software drivers or BIOS modifications, comes equipped with a full range of technical features. These include a 16bit timer that can be used for overall system power management activities such as CPU wake-up and peripheral shutdown, a watchdog and oscillator monitor circuit for high-reliability applications, and a port for an additional input device.

Ready to connect to Fujitsu's FKB Series and other laptop or palmtop keyboards, the UR5HCFJL is available for 3-, 3.3-, and 5-V systems in DIP, PLCC, QFP, and wide-temperaturerange packages for \$3.45 in quantity. Evaluation kits, with the IC, sample keyboard, evaluation board, connectors, and cables, are also available for **\$140**.

USAR Systems, Inc. 568 Broadway, Ste. **#405** New York, NY 10012 (212) 226-2042 Fax: (212) 226-3215 **#500**

#### **ROBOT KIT**

Aclypse Corp. is shipping the ADR-1 Robot Kit for the hobbyist and educational markets. The ADR-1 is 27" tall with a 14" diameter and weighs approximately 16 lbs. The complete robot kit has an onboard computer system that features voice recognition, English speech output, power motor drive, and a battery with a monitoring and recharging system.

The robot has its own operating system and a builtin BASIC programming language for robot instruction. The system can be programmed by connecting to almost any computer or terminal through a serial cable. Program and data files can be sent back and forth between the robot and a personal computer at speeds up to 19,200 bps.

The onboard computer is powered by a 16-bit 8086compatible CPU operating at 10 MHz with 256 KB of RAM (expandable) and 128 KB of ROM. A lithium battery enables data to be retained if power is lost. Two I/O ports have a total of 12 digital inputs and outputs. Expansion cards can be connected to add memory, sensors, motors, and other new devices.

The robot is powered by a 12-V, 6-A battery pack and contains an onboard power and recharge module. The unit features 6" diameter wheels and can move forward or backward at a speed of up to 8 inches per second.

No electronics or advanced computer experience is required to assemble and use the ADR- 1. No special tools are required and assembly normally takes from 2 to 6 hours. The ease of

assembly makes the kit ideal for classroom and lab environments.

The ADR- 1 Robot Kit sells for \$499.

Aclypse **Corp.** Rt. 2 Box 213H Worthington, IN 47471 (812) 875-2852 BBS: (812) 875-2836

#### UNIVERSAL DEVELOPMENT BOARD

Intellix/Systronix has released a development board that supports all Dallas Semiconductor 805 1 -compatible microcontrollers. The **DPB2** is a complete, single-board computer with LCD and keypad interfaces, serial I/O, relay-driver outputs, analog-to-digital conversion, rugged voltage regulator, and a generous prototyping area.

The DPB2 is a 100 mm x 60 mm (4" x 6.4") card that contains 72-pin SIMM, 40-pin SIMM, and 40-pin DIP sockets for the Dallas microcontrollers. Crystal, serial I/O, and other ports are common to all processor sockets. Processor I/O pins are brought out to labeled headers. The board accepts unregulated 6-13 VDC or can be powered directly with regulated 5 VDC.

Serial loading and system reset are controlled by a TL7705 monitor chip and a 16V8 programmable logic device. Loading can be initiated by on-card push buttons or the DTR line of the RS-232 serial port. Serial loader software is included.

The DPB2 is assembled and tested in a variety of configurations, and is available starting at \$199. A bare board

A bidirectional RS-232 serial I/O and RS-232 unidirectional printer output are brought out to 2 x 5 headers, and a 2 x 5–to–DE-9 adapter is included. The pinout is consistent with a standard PC/AT 9-pin serial port. A 74C922 4 x 4 keypad encoder/debouncer conditions the keypad and interrupts the processor when a key with documentation is available for \$49. Software tools are also available.

is ready to be read. A patch area is provided to map the keypad. The LCD interface accepts most 4- or 8-bit

reference voltage is included. Four high-current, open-

drive relays, stepping motors, and alarms.

collector relay drivers with snubbing diodes can directly

An 8-bit A/D converter with an adjustable 2.5-5.0-V

#### Intellix/Systronix, Inc.

parallel LCD displays.

555 South 300 East, Ste. **#21** • Salt Lake City, UT 84111 (801) 534-I 017 • Fax: (801) 534-I 019

#502

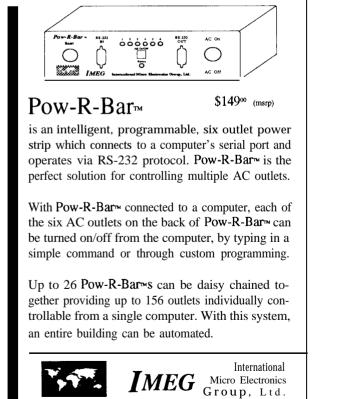

#### SOFTWARE CONTROLLER I/O CARD

Axxon has designed a new peripheral for IBM PC and compatible computers called **SOFT I/O.** This 16-bit product offers four high-speed serial ports (COM1–COM4 using the 16550 UART) plus two bidirectional parallel ports (LPT1 and LPT2).

The SOFT I/O has been engineered to be completely free of jumpers for configuring all of the hardware ports. With software, the user is able to change the address, disable any of the serial and parallel ports, and select from interrupts 3, 4, 5, 7, 9, 10, 11, 12, and 15 for any port. The hardware is completely compatible at the register level with high-speed, 16550-type UARTs with internal 16-byte buffer and IBM-PS/2 printer port specifications.

Also included is support for an onboard BIOS using softwareupdated flash memory for future expansion. The high-speed serial

ports are ideal for use with 9600-bps or faster external modems. The bidirectional ports support scanners and aid in fast data transfer for laser printers or external printer port-driven tape drives.

The SOFT I/O sells for \$299 (CDN dollars) and includes a five-year warranty.

Axxon Computer Corp. 3979 Tecumseh Rd. East • Windsor, Ontario • Canada N8W1J5 • (519) 974-0163 • Fax: (519) 974-0165

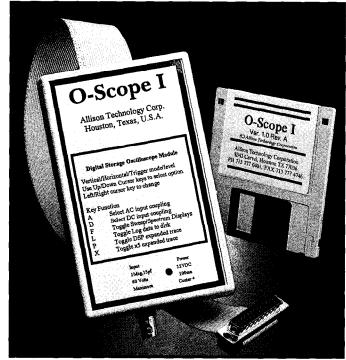

#### DIGITAL STORAGE SCOPE MODULE

A low-cost, digital storage oscilloscope module has been announced by Allison Technology. The O-Scope I connects to IBM-PC/AT-compatible computers via the PC's printer port and converts the computer into a digital storage oscilloscope capable of capturing and displaying DC, audio, and low-end ultrasonic frequency input signals. It can be used for power supplies, audio equipment, automotive, and general analog design and repair.

O-Scope I is small, light weight, and portable. It draws less than 40 mA of current from a 12-VDC source. It uses standard x1 and ×10 oscilloscope probes and works with both desktop and laptop computers. Trace sweeps can be frozen on screen, saved to disk to be used with other programs, or output to a printer via

the DOS print-screen function. Vertical ranges of 50 mV to 10 V per division are provided. Sweep rates of 500 us (xl mode) to 100 s per division are available from most AT compatibles. The analog frequency range is DC to 22 kHz for DCcoupled input and 1 Hz to 22 kHz (-3 dB) for the ACcoupled input option. A 128-point Fourier spectrum analyzer mode provides frequency spectrum information from DC to one-half of the current sample rate. There are 50 samples per division in the xl sweep mode. Two forms of sweep expansion are provided. Expansion modes of  $\times 2$  and x5 spread out the sweep by separating samples. Special DSP expansion modes are

available from x2 to x1 6 which will expand the sweep by adding calculated samples based on the frequency content of the captured sweep signal. In addition to the sweep, O-Scope I provides voltage, frequency, and period calculations. Voltage measurements include peak-to-peak, average, peak, minimum, and RMS. If more than one cycle exists in the sweep, a frequency and period are calculated. If less than one cycle exists, a pulse period is calculated instead.

O-Scope I sells for \$169.95 including an AC adapter and cable. A kit version, which is provided without the shielded case, is also available for **\$119.95**.

Allison Technology Corp. 8343 **Carvel** Houston, TX 77036 (713) 777-0401 Fax: (713) 777-4746

#504

#### **RADIO MODEM**

Monicor has announced a low-cost radio modem which eliminates the need for an RS-232 cable. The **IC-15 Radio Modems** contain a UHF radio transceiver that supports 2400 and 4800 bps. A sensitive receiver, powerful transmitter, and fast protocol support line-ofsight distances up to one mile. Greater distances are possible with optional gain antennas.

Each radio has an intelligent RS-232 communications port that can be completely configured for any terminal. Data rates are up to 19,200 bps. The point-to-point radios are ready to use and are completely self-contained in a Lexan housing. They come complete with an antenna, a rechargeable NiCd battery, and a battery charger. Each radio weighs only 22 oz. The dimensions are 9" x 3" x 1.7".

The IC- 15 Radio Modem sells for \$950 each (2400 bps) and \$1400 each (4800 bps).

Monicor Electronics Corp. 2964 NW 60th St. • Ft. Lauderdale, FL 33309 (305) 979-1907 • Fax: (305) 979-2611

#### **DATAMAN S4 PROGRAMMER**

Dataman has announced improvements to their popular S4 hand-held **EPROM Programmer/Emulator.** The S4 now comes standard with 5 12 KB (4 Mbit) of RAM.

Approximately 7" x 4" x 2" and weighing just over a pound, S4 is selfpowered and completely portable, making it useful for field service work. S4 can operate for several days on its internal NiCd battery or be used as a conventional desktop programmer, controlled remotely by any computer with an RS-232 port. Besides functioning as a programmer, S4 can also be a ROM emulator. Included with each unit is an emulation cable that plugs directly into the target system in place of any EPROM or ROM up to 5 12 KB x 8 bits.

Equipped with a 32-pin ZIF socket, the S4 supports EPROMs, EEPROMs, and flash memory up to 8 Mbits. It can also program PIC and

8751 microcontrollers, 8-pin serial EEPROMs, and 16-bit-wide devices using optional adapter modules. Additional socket converters are also available for a variety of surface-mount packages. The comprehensive device library is regularly updated to support new devices. Upgrades can be downloaded free of charge from Dataman's 24-hour bulletin board. Other features include a high-contrast, 80-character LCD with a wide viewing angle, 45 color-coded rubber keys (nonbreakable), and a high-impact, molded plastic case which fits comfortably in the palm of your hand. S4 is covered by a full 3-year warranty and costs \$795.

Dataman Programmers, Inc. 22 Lake Beauty Dr., Ste. 101 • Orlando, FL 32806 • (407) 649-3335 • Fax: (407) 649-3310

#506

155 W. Tiverton Lexington, Kentucky 40503 P.O. Box 25007 Lexington, Kentucky 40524 800-274-8699 606-271-0017 Fax: 606-245- 1798

PCMCIA SERIAL I/O CARD Smart Modular

I/O card for use in any subnotebook, PDA, palmtop Technologies Inc. has computer, or other host

developed a **PCMCIA** serial

system equipped with a Type II slot. The card offers asynchronous compatibility with all DOS- and Windows-based software and connects to all standard serial peripherals. It also features synchronous operation for high-speed data transfers with mainframes.

The serial I/O card includes an internally buffered 16550 UART and an 8530 USART, a combination that provides the flexibility of either asynchronous or synchronous communication. It also provides the flexibility of configuring the asynchronous port as COM1-COM4 while the synchronous port is fully programmable. Its software eliminates the need to set any jumpers.

The card's power-down mode conserves power and extends battery life. In the

standby mode, which is automatically entered when no activity has been detected for a period of time, power is removed from most of the card's internal circuitry. In the sleep mode, the host computer essentially turns off the card's power. This mode is entered and exited under the control of the host computer using the PCMCIA interface.

The Serial I/O card sells for \$145 in quantity.

Smart Modular Technologies 45531 Northport Loop West, Bldg. 3B Fremont, CA 94538 (510) 623-1 231 Fax: (510) 623-I 434

#507

#### CPU COOLING DEVICE

The Turbo Chip Cooler (TCC) from Discovery Data Systems keeps CPUs almost 60°F cooler at room temperature than typical fan/heatsink chip coolers. CPUs will last longer and operate with wider timing margins for all computers. The device is especially effective with higher speed CPUs.

The solid-state refrigerator used in the TCC literally extracts heat from chips without the need for the heatsink

gels, special clips, or clamps required by other types of chip coolers. In most cases, when combined with a typical fan and heatsink combination, it maintains the CPU at or below room temperature.

The TCC can be used with any CPU, including 286, 386,486, Pentium, 680x0, and other processors (even DIPs and socketed types). Special heat-conductive mounting pads, provided with the TCC, allow it to conveniently mount with any chip or heatsink combination. A single model fits all devices and can be installed without tools.

The Turbo Chip Cooler sells for \$34.95.

**Discovery Data Systems** 12572 Westmont Dr. • Moorpark, CA 93021 (805) 529-1325 • Fax: (805) 523-8153

## FEAT'URES

14

24

34

40

44

Big Brother:

M68HC16

Exploring the

## FEATURE ARTICLE

#### Dana Romero

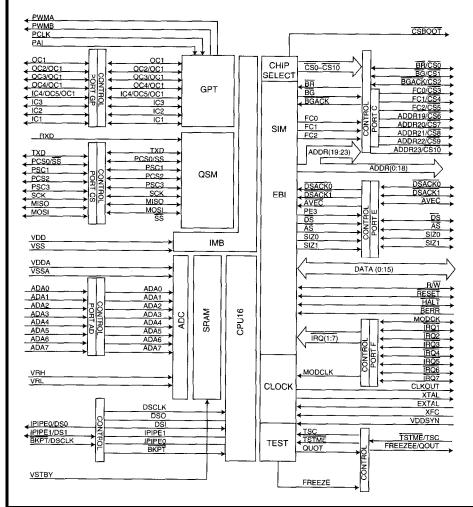

any articles have been written about applications of the 8031/8051 family of micros, a family long established in the field of embedded control. As an alternative, I would like to discuss Motorola's approach to microcontroller design with the M68HC16, their "next step" after the M68HC11. Having worked with the

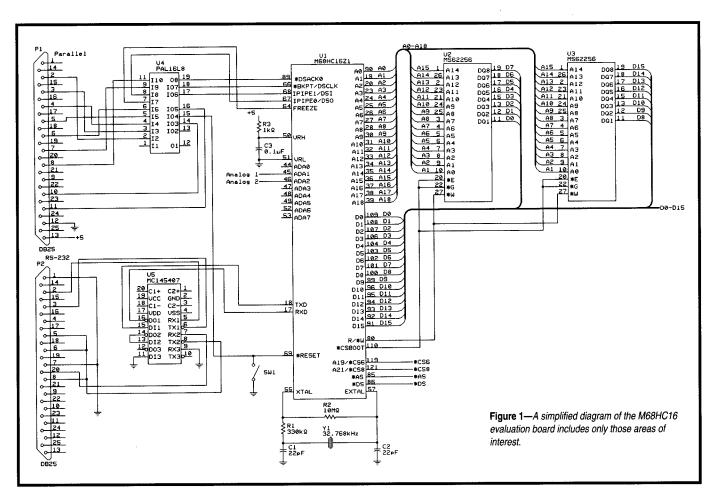

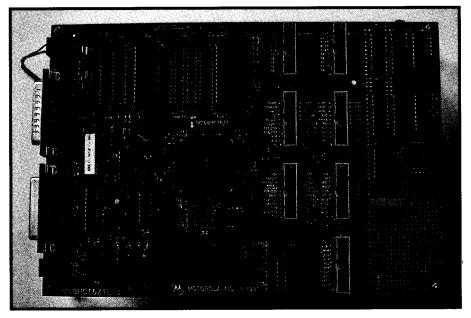

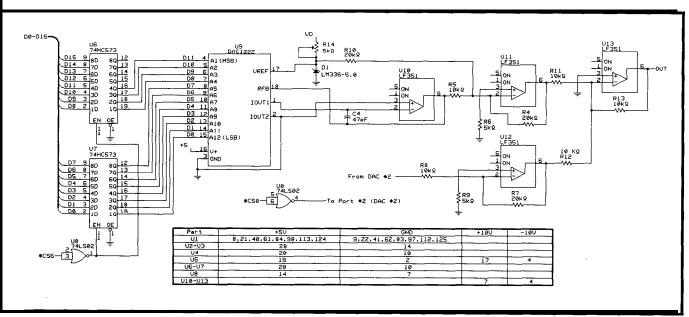

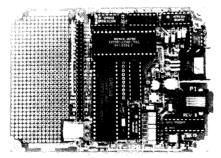

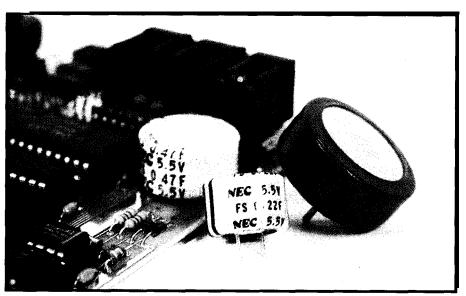

M68HC11 in the past and being familiar with its architecture and command set, when I read that Motorola was offering a development kit for the M68HC 16, I bought one immediately. The package turned out to be well worth the money-loads of software, programming examples, documentation, and even an introductory book on digital signal processing. In fact, the board and software are oriented toward prototyping A/D and D/A conversions for use in DSP. A much simplified diagram of the board is shown in Figure 1. Note that all the signals shown are also sent to 20-pin connectors, which have through holes for extending them to a wire-wrap area (Photo I). I've left out many signals that this new micro provides, but aren't used in this basic introduction.

Shown in the photo is a socket for a Burr-Brown serial D/A converter, which I didn't have access to and wouldn't have suited my purposes anyway. Both parallel and serial ports are provided. The parallel port, P1, is the primary communication path with a PC via its printer output; the serial port, P2, is secondary and is intended for a dumb terminal or another PC with communications software. Last, note that the components R3 and C3

Time to Meet Big Brother: Exploring the M68HC16

DRAM on an 8031: It's Not as Hard as You'd Think

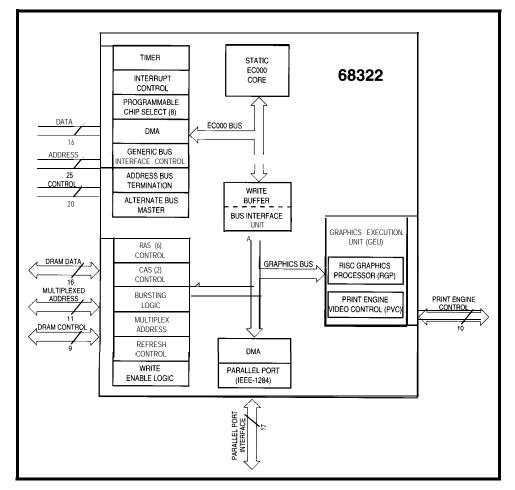

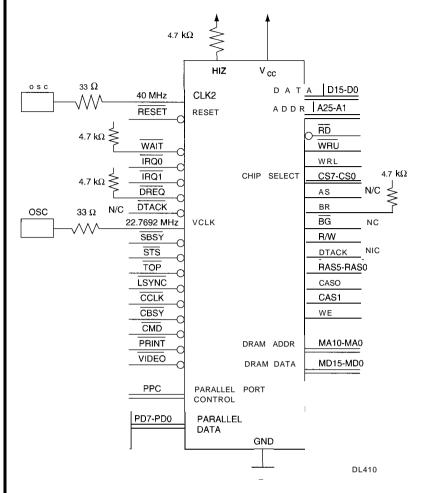

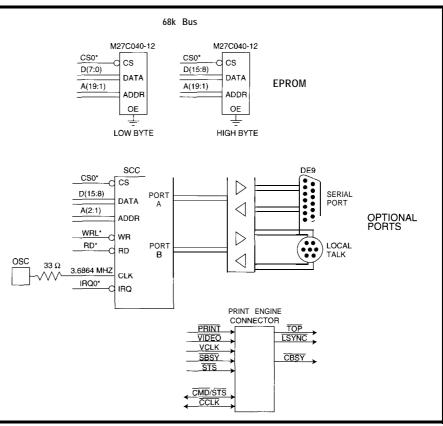

Motorola's 68322 Processor: Redefining the Low-end Laser Market

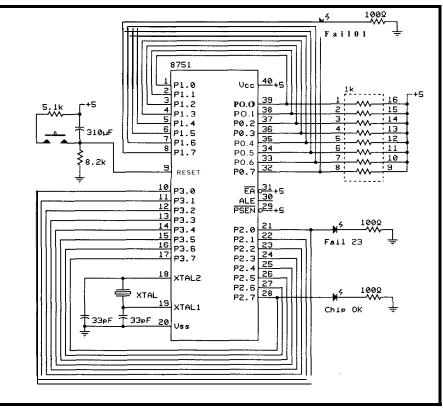

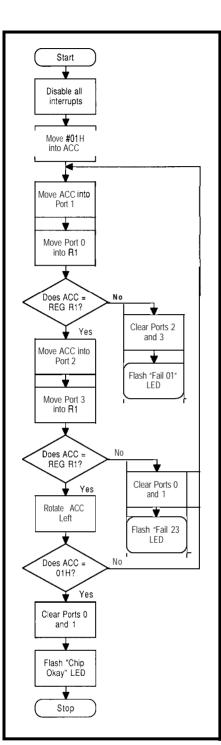

Preventing the Ultimate Blow: A Portable Checking Unit for 8751s

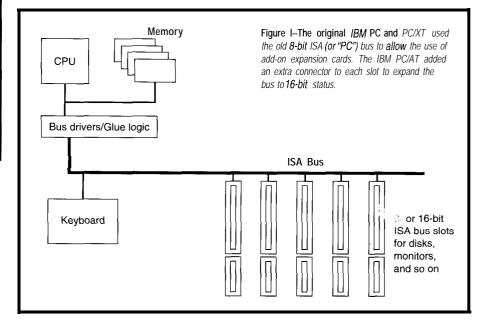

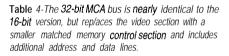

Understanding PC Buses

The M68HC11's big brother—the M68HC16—has been on the market for a short time now. Take a look at how the siblings compare and find out what the more powerful of the two has to offer for your next application.

are shown, but are not provided on the board. These are required to set a 5-V reference for the A/D converter section. I was stumped for quite a while because I assumed the ADC would get its reference from within the chip. Wrong. The reference voltage can be set to a value between 0 and 5 V, with the restriction that 0 < VRL < 2.5 V and 2.5 V < VRH < 5 V.

#### **ON LESS FIRM GROUND...**

Before discussing applications, I should cover some software and firmware that is essential to a discussion of the M68HC16. Lest I get in over my head (which I found wasn't hard with a device of this complexity), readers should check reference manuals for details. Also see the sidebar for a short comparison of the 'HC16 and 'HC11.

Motorola's background debug mode (BDM) introduced a new concept to me. It is an alternative operating mode in which debugging support is incorporated into the microcode of the CPU. It permits viewing and altering registers or memory, single-stepping, and so forth, with the processor in the circuit being tested. According to the *CPU16 Reference Manual*, BDM is enabled by the status of the /BKPT signal on the rising edge of /RESET and remains enabled until another system reset. Referring to the upper left corner of Figure 1, when BDM is activated, the FREEZE signal is activated by the CPU. IPIPE0 and IPIPE1 change mode from instruction status

Photo 1—The Motorola M68HC16 evaluation board includes a prototyping area where the DACs and support circuitry are built up.

| A 7F SF 103BE<br>B 00 FC 0023C<br>D 7F00 K F000                             | >START                                | LDZ #0                                          | DE F2                                                                                             | :point                    |

|-----------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------|

| E FFFF FK 0<br>IX 00008 SK 1<br>IY 06AF9 HR 0048<br>IZ 00000 IR 0000        | · · · · · · · · · · · · · · · · · · · | EMULS<br>ADCE #0<br>STE ARG<br>LDD ABG          |                                                                                                   | :signe<br>:round<br>:save |

| AM F5D73EFFF<br>SMHENZUC210S-PK-<br>1111100111100000                        |                                       | EMULS<br>ADCE #0<br>TED                         | -                                                                                                 | :cube                     |

| 0.0.0.0.0                                                                   | FE 00 00<br>B0 02 B0<br>B0 02 B0      | 002C0 0C F8 (<br>002C8 03 0D F<br>002D0 FF FF F | DATA (DMM) F3<br>C0 00 34 A3 91 51<br>FF FF FF 5F FF FE<br>FF FF FF F7 FD FF<br>FF F7 FF BF FF FF | 4Q                        |

| (hit any key to abo<br>Loading map file cos<br>Loading Loaded<br>>mdf3 02c0 | rt) Loading                           | √G F1<br>0002B2 loaded.                         |                                                                                                   |                           |

Photo 2—A typical PC display when using the EVB16 debugger includes memory, register, and program information.

signals to DSO and DSI, respectively. In conjunction with /BKPT—now interpreted as a clock signal—these two signals form a full-duplex synchronous serial interface. The PAL at U4 then magically completes the connection to the PC printer port.

From here, the development system provides a debug program for PCs called EVB16 which displays registers, memory, code, breakpoints, and a main command window (Photo 2). Both EVB16 and the PAL were developed by P&E Microsystems. I suppose

there are other tools for developing, uploading, and downloading programs for the M68HC16, but this system is hard to beat. If you're not an experienced programmer, it's nice to start writing and testing a small subroutine without worrying about everything crashing and leaving no hint about what went wrong.

#### MACMATH

To illustrate some of the 'HC16 commands, especially the MAC and EMULS commands, let's consider the Taylor series expansion:

$$cos(x) \cong 1 - \frac{x^2}{2!} + \frac{x^4}{4!} - \frac{x^6}{6!} + \frac{x^8}{8!}$$

This equation is derived from the expression for  $\exp(ix)$ , and the fact that  $\exp(ix) = \cos(x) + i^* \sin(x)$ . By itself, this isn't going to do much in the way of DSP; but, it is a start in that direction.

It would be nice to calculate cos(x)from  $x = -\pi$  to  $x = \pi$ , but the MAC command is a lot more tractable if we keep -1 < x < 1. Since a user is probably going to scale the final result anyway, let's translate cos(x) to:

$$\cos(\pi \mathbf{x}) \cong \pi^2 \times \left[ \frac{1}{\pi^2} - \frac{\mathbf{x}^2}{2} + \frac{\pi^2 \mathbf{x}^4}{24} - \frac{\pi^4 \mathbf{x}^6}{720} + \frac{\pi^6 \mathbf{x}^8}{40320} \right]$$

Now if -1 < x < 1, an entire cycle can be computed while, at the same time, keeping all of the terms between -1and 1. A program to calculate  $\cos(\pi x)/\pi^2$  for a given x is COSX.ASM (see Listing 1). I have precalculated the five coefficients and called them CFO-CF4.

At this point, we need to understand the formats for the MAC command and the EMULS (extended signed multiply) command. For MAC, the signed 16-bit numbers to be multiplied have their decimal points between bits 15 and 14 (bit 15 is the sign bit). The product in the 32-bit register, E:D, has its decimal point between bits 31 and 30 (bit 31 is the sign bit). Thus, a multiplicand of \$8000 is equal to -1, \$2000 to  $\frac{1}{4}$ , \$C000 to  $-\frac{1}{2}$ , and so on. More specifically, to translate  $\pi^{2/24}$  = 0.411234, multiply by the range 32768 to get 13475 or \$34A3, which is the coefficient CF2.

The EMUL command is similar, but the range is now 65536. \$000 represents  $-\frac{1}{2}$ , \$4000 is  $\frac{1}{4}$ , and \$1000 is  $\frac{1}{6}$ .

|                                                                                                                  |                                                                                        | K.ASM subroutine calculate the E register.                                               | es $\cos(\pi \times X)/(\pi^2)$ . Enter with the argument in loc                   | ation ARG   |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------|

| CF0<br>CF1<br>CF2<br>CF3<br><b>CF4</b><br><b>ARG</b><br><b>ARG2</b><br><b>ARG4</b><br><b>ARG6</b><br><b>ARG8</b> | E Q U<br>E Q U | \$02E0<br>CF0+2<br>CF0+4<br>CF0+6<br>CF0+8<br>\$02F0<br>ARG+2<br>ARG+4<br>ARG+6<br>ARG+8 |                                                                                    |             |

|                                                                                                                  | ORG                                                                                    | \$02E0                                                                                   |                                                                                    |             |

|                                                                                                                  | DC.W<br>DC.W<br>DC.W<br>DC.W<br>DC.W                                                   | \$0CF8<br>\$C000<br>\$34A3<br>\$9151<br>\$0300                                           | one over PI squared<br>-1/2<br>+PI^2 over 24<br>-PI^4 over 720<br>+PI^6 over 40320 |             |

|                                                                                                                  | ORG                                                                                    | \$0200                                                                                   |                                                                                    |             |

| *****                                                                                                            | Initializ                                                                              | ation Routines                                                                           | ****                                                                               |             |

|                                                                                                                  | I NCLUDE<br>I NCLUDE<br>I NCLUDE<br>I NCLUDE<br>I NCLUDE                               | 'ORG00000.ASM'<br>'ORG00008.ASM'                                                         | <pre>set EK=F, XK=0, YK=0, ZK=0 set sys clock at 16.78 MHz</pre>                   |             |

|                                                                                                                  | I NCLUDE                                                                               | 'INITRAM.ASM'                                                                            | disable COP<br>initialize and turn on SRAN<br>set stack (SK=#\$1, SP=#\$03{        |             |

| *****                                                                                                            | Set up Po                                                                              | ort F as an outp                                                                         | ut ****                                                                            |             |

|                                                                                                                  | LDAB<br>STAB<br>LDAA<br>STAA                                                           | #00<br><b>PFPAR</b><br>#\$FF<br><b>DDRF</b>                                              | ;configure <b>port</b> F <b>as general</b>                                         |             |

|                                                                                                                  | STAA<br>STAB                                                                           | PORTFO                                                                                   | ;now set port F as an output<br>;set initial value to zero                         | , por c     |

| ***** (                                                                                                          | Compute p                                                                              | owers of x                                                                               | ****                                                                               |             |

| CTADT.                                                                                                           | LDZ                                                                                    | #0                                                                                       | ;point to bank zero                                                                |             |

| START:                                                                                                           | LDD<br>STAB<br>TDE                                                                     | ARG,Z<br><b>Portfo</b>                                                                   | ;write odd value of ARG to p                                                       | port F      |

|                                                                                                                  | TDE<br>EMULS<br>ADCE<br>STE<br>LDD<br>EMULS<br>ADCE                                    | #0<br>ARG2,Z<br><b>ARG,Z</b><br>;cube <b>of x</b><br>#0                                  | ;signed multiply E*D>>E:D<br>;round E:D into E<br>;save square of x n ARG2         |             |

|                                                                                                                  | TED<br>EMULS<br>ADCE<br>STE<br>LDD<br>TDE<br>EMULS                                     | #O<br>ARG6.Z<br>ARG2.Z                                                                   | sixth power of x                                                                   |             |

|                                                                                                                  | ADCE<br>STE<br>TED                                                                     | #O<br>ARG4,Z                                                                             | fourth power of x                                                                  |             |

|                                                                                                                  | EMULS<br>ADCE<br>STE                                                                   | ∦O<br>ARG8,Z                                                                             | eighth power of x                                                                  | (continued) |

|                                                                                                                  |                                                                                        |                                                                                          |                                                                                    |             |

## PIC16C5x Real-time Emulator

Introducing RICE16-5x and RICE5x-Junior, real-time in-circuit emulators for the PIC16C5x family microcontrollers: affordable, feature-filled development systems from **¢Enn**\*

\* Suggested Retail for U.S. only

#### RICE16 Features:

Real-time Emulation to 20MHz

- PC-Hosted via Parallel Port

- Support all oscillator types

- 8K Program Memory

- 8K by 24-bit real-time Trace Buffer

- Source Level Debugging

- Unlimited Breakpoints

- External Trigger Break with either "AND/OR" with Breakpoints

- Trigger Outputs on any Address Range

- 12 External Logic Probes

- ■User-Selectable Internal Clock from 40 frequencies or External Clock

- Single Step, Multiple Step, To Cursor, Step over Call, Return to Caller, etc.

- . On-line Assembler for patching instruction

- Support 16C71, 16C84 and 16C64 with Optional Probe Cards

- Easy-to-use Windowed Software

- Comes Complete with TASM16 Macro Assembler, Emulation Software, Power Adapter, Parallel Adapter Cable and User's Guide

- 30-day Money Back Guarantee

- Made in the U.S.A.

RICE5x-Junior supports PIC16C5x family emulation up to 20 MHz. It offers the same real-time features of RICE16 without the real-time trace capture.

### **PIC** Gang Programmers

Advanced Transdata Corp. also offers PRODUCTION QUALITY gang programmers for the different PIC microcontrollers.

■ Stand-alone COPY mode from a master device ■ PC-hosted mode for single unit programming ■ High throughput ■ Checksum verification on master device ■ Code protection ■ Verify at 4.5V and 5.5V ■ Each program cycle includes blank check, program and verify eight devices

Price5 start at \$599

PGM16G: for 16C5x family

PGM47: for 16C7'

Throughput: 16C54: 4 seconds

16C71: 10 seconds

(0 devices) 16C57: 10 seconds

16C84seconds

iC71/84 ids

PGM17G:17C42 17C42: 13 seconde

**Call (214) 980-2960 today for our new catalog.** For RICE16.ZIP and other product demos, call our BBS at (214) 980-0067.

18

Advanced **Transdata** Corporation Tel **(214) 980-2960** 14330 Midway Road, Suite 120, Dallas, Texas 75244 Fax (214) 980-2937

See us at Embedded Systems West booth #749 #111 ISSUE #50 september 1994 The Computer Applications Journal For this reason the stored arguments, ARG2–ARG8, need to be divided by two to be in the proper format for the MAC command. The four LSRW instructions just before the MAC section handle this.

Before running this program from within EVB16, be sure to first set the data window (F3) with the command MD F302E0 to display the coefficients CFO-CF4 and the values ARG-ARG8. (You can watch the ARGs being changed if you trace through the program with the Tn command, where n is the number of steps to trace.) To watch the timing on a scope, preload ARG with an odd value using DMM W 0 2 F 0 from within the F1 (debug] window. The odd value sets Port F's bit zero to one for the duration of the loop. Since port F has been configured as an output port, the signal MODCLK is now redefined as FO. Your scope probe on this line will show the time that it remains positive.

I measured 100 µs for one loop. Although that seems slow, there are a lot of 16- and 32-bit calculations going on. Interestingly, eliminating the eighth-power term of the approximation only reduces the calculation time to 90 us. Timing would be a concern if one wanted to output a waveform.

#### **D/A EXPERIMENTS**

One of the first things that I wanted to do with the M68HC16 board was to experiment in generating audio waveforms that would be difficult or impossible to produce with analog circuitry alone. My ultimate goal was to produce unique tones. Using the prototyping area on the board, I added two 12-bit DACs whose outputs are then sent to a summing junction as shown in Figure 2.

I summed the two DAC outputs so that one could provide a fundamental or low-frequency tone while the other provided a harmonic or nonharmonic, high-frequency tone. Alternatively, one DAC might help generate an envelope of sorts for the other's tone, and so on. (Note that, just because the circuit uses DAC 1222 converters, you're not restricted to the slower response of 12-bit resolution. Instead, through software, a 16-bit

| #\$0010<br>CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b><br>\$02EA.Z<br><b>PORTFO</b><br>#08<br><b>DELAY</b><br><b>START</b> | ;set saturation mode in MAC reg<br>;first term is one over PI^2<br>last coefficient?<br>return with rounded result in E<br>remove this to measure timing<br>all bits set to zero<br>negative state for scope timing |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b><br>\$02EA.Z<br><b>PORTFO</b>                                                   | ;first term is one over PI^2<br>last coefficient?<br>return with rounded result in E<br>remove this to measure timing<br>all bits set to zero                                                                       |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b><br>\$02EA.Z<br><b>PORTFO</b>                                                   | ;first term is one over PI^2<br>last coefficient?<br>return with rounded result in E<br>remove this to measure timing                                                                                               |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b><br>\$02EA.Z                                                                    | ;first term is one over PI^2<br>last coefficient?<br>return with rounded result in E<br>remove this to measure timing                                                                                               |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b>                                                                                | ;first term is one over PI^2<br>last coefficient?<br>return with rounded result in E                                                                                                                                |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b>                                                                                | ;first term is one over PI^2<br>last coefficient?<br>return with rounded result in E                                                                                                                                |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA<br><b>LOOP</b>                                                                                | ;first term is one over PI^2<br>last coefficient?                                                                                                                                                                   |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2<br>#\$02EA                                                                                               | ;first term is one over PI^2                                                                                                                                                                                        |

| CF0.Z<br>#ARG2<br>#CF1<br>2,2                                                                                                          | ;first term is one over PI^2                                                                                                                                                                                        |

| CF0.Z<br>#ARG2<br>#CF1                                                                                                                 |                                                                                                                                                                                                                     |

| CFO.Z<br>#ARG2                                                                                                                         |                                                                                                                                                                                                                     |

| CFO.Z<br>#ARG2                                                                                                                         |                                                                                                                                                                                                                     |

|                                                                                                                                        |                                                                                                                                                                                                                     |

|                                                                                                                                        | ;set saturation mode in MAC reg                                                                                                                                                                                     |

| #\$0010                                                                                                                                | ;set saturation mode in MAC reg                                                                                                                                                                                     |

| #\$0010                                                                                                                                | ;set saturation mode in MAC reg                                                                                                                                                                                     |

|                                                                                                                                        |                                                                                                                                                                                                                     |

|                                                                                                                                        |                                                                                                                                                                                                                     |

| nd accumulate                                                                                                                          | ****                                                                                                                                                                                                                |

| ARG8,Z                                                                                                                                 |                                                                                                                                                                                                                     |

| ARG6,Z                                                                                                                                 |                                                                                                                                                                                                                     |

| ARGZ,Z<br>ARG4,Z                                                                                                                       | ;change format for MAC command                                                                                                                                                                                      |

| 1000 7                                                                                                                                 |                                                                                                                                                                                                                     |

|                                                                                                                                        | ARG2,Z                                                                                                                                                                                                              |

output port can be used for 12-,10-, or 8-bit conversions.)

I wired both DACs for bipolar, rather than unipolar, operation. I adapted the circuitry, not from National Semiconductor, the manufacturer, but from Analog Devices' specification for the AD7541A. (As far as I can tell, the chips are functionally the same.) The outputs for given input codes are listed in Table 1. Note that  $V_{\text{OUT}}$  as referred to in the table is the voltage that will appear at the output of either U11 or U12; op-amp U13 will produce the negative sum of these voltages at its output. Also, V<sub>IN</sub> is set by voltage reference D1 and potentiometer R14 and goes to V<sub>REF</sub> of both DACs.

With this hardware in place, the real complexity comes in the software. The fact that decoded chip selects come directly from the microcontroller means more work in software. A program that produces a basic audio waveform is S P I K E . A SM (see Listing 2). This program shows how to set up the chip selects, output to the

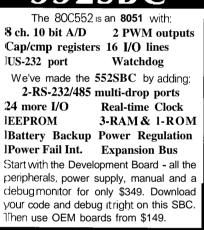

#### BCC52 BASIC -52 Computer/Controller Bar Code Sensor Battery Controllers The BCC52 controllercontinuesto be Clock/Calendars Micromint's best selling single-board com-**Digital Power Drivers** puter. Its cost-effective architecture needs **DTMF & Phone Interfaces** onlyapowersupplyandterminalto become Firmware Furnace Widgets a complete development system or single-HCS-II Hard-to-find Parts board solution in an end-use system. The I<sup>2</sup>C Bus ICs BCC52 is programmable in BASIC-52, (a IRLEDs & Photodiodes fast, full floating point interpreted BASIC), or IR Data Link Parts assembly language IR Remote Control The BCC52 contains five RAM/ROM Laser Diode Controllers sockets, an "intelligent" 2764/128 EPROM Linear Hall Effect Sensor programmer, three 8-bit parallel ports, an Multiplexers & Crosspoints auto-baud rate detectserial console port, a serial printer port, and much more. Power Op Amp PROCESSOR INDUT/OUTDUT Remote Temperature Sensor •80C528-bit CMOS processor w/BASIC-52 Console RS232 – autobaud detect Stepper Motor Drivers Lineprinter RS-232 Three 16-bit counter/timers Watchdogs & Power Monitors Six interrupts Three8-bit parallel ports 8051 Information Much more! EXPANDABLE1 and more! Compatible with 12 BCC expansion boards MEMORY Use a soldering iron? Get the parts! To Order Call 1-800-635-3355 • 48K RAM/ROM, expandable Five on-board memory sockets UPS: Ground/2nd day \$6 5019.00 to 48 US states, COD add \$4.50. PO Boxes and Canadian addresses. \$6 for USPS mail, Check, MO, or COD only; no credit cards, no open POs. NC residents add 6% sales tax. Quantity discounts start at five parts. Data sheets included with all parts. Tel: (203) 871-6170 Either 8K or 16K EPROM Fax: (203) 872-2204 BCC52 Controller board with BASIC-52 and SK RAM \$189.00 Single Qty. Call/write/FAX for seriously tempting catalog... BCC52C \$199.00 Low-power CMOS version of the BCC52 Pure Unobtainium BCC52I -40°C to+85°C industrial temperature version \$294.00 BCC52CX Low-power CMOS, expanded BCC52w/32K RAM \$259.00 CALL FOR OEM PRICING Your unusual part5 source 13109 Old Creedmoor Road Raleigh NC 27613-7421 MICROMINT, INC. 4 Park Street, Vernon, CT 06066 In Europe: (44) 0285-658122 • In Canada: (514) 336-9426 • In Australia: (3) 467-7194 FAX/voi ce (919) 676-4525 Distributor Inquires Welcome!

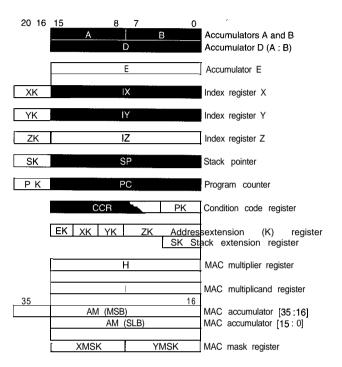

#### Meet the M68HC16

The M68HC16 is Motorola's 16-bit step after the M68HC11 line of microcontrollers. Additional features make it more suitable for digital signal processing. The

M68HC16 architecture is based on modules similar-but not identical-to those used in the M68HC11. These modules include a CPU core, RAM, 10-bit analog-to-

> digital converter (ADC), generalpurpose timer (GPT), queued serial module (QSM), system integration module (SIM), clock control, and port or chip selects. All these modules are running on one IC at 16.77 MHz.

Although the basic modules of the M68HC 16 are named differently than in the M68HC11, most of the features of the 'HC11 are present in the 'HC16. Of course, the data path is 16 bits wide, and it has 1 MB of data space and 1 MB of code space. Although the documentation implies that the address bus is 24 bits wide, ADDR20-ADDR23 follow the output of ADDR19. According to the Technical Summary, these are brought out to pins only for test purposes. This summary also claims that the 'HC16 is upwardly code compatible with the 'HC 11. However, the 'HC16 has no instructions to increment or decrement any of the 16-bit registers directly as the 'HC11 does with the INX and INY instructions. The only instructions that comes close are A I X and A I Y: add immediate to X or Y. The

Figure 2--Hiwo-cnainnel UAC and some tilters on the outputs can be used to generate tones under processor control.

processor would be more accurately said to be "upwardly register compatible."

The *CPU16 Reference Manual* devotes a whole appendix to the comparison of the two command sets. Looking at the registers found on the 'HC16, you'll see that the shaded registers in the diagram are also found in

the 'HC 11. but that the condition code register is only partially shaded. This partial shading is because the 'HC16 adds three new flags, devoted to the multiply-andaccumulate (MAC) register. and a field of three bits to mask eight interrupts. The "K" extension registers are four bits each and concat-

enate with their corresponding 16-bit registers to form 20-bit addresses, with the exception of the EK register. The EK register concatenates with a word following an opcode in the extended addressing mode.

A significant conceptual difference between the 'HC 16 and the 'HC 11 comes with the addition of the MAC section, which consists of a 36-bit accumulator (AM), multiplier registers (H and I), and 8-bit mask registers (XMSK and YMSK). This section was specifically designed for DSP calculations. XMSK and YMSK are used for modulo addressing. Readers should study these for their own applications; but for now, it is sufficient to say that setting both to zero disables modulo addressing.

With this in mind, a single MAC instruction of the form MAC x0, y0 performs the following sequence:

1. A 16-bit signed fraction in the H register is multiplied by the same in the register; the product is shifted left once to align the decimal and then placed in the 32-bit register, E:D. DO is set to zero.

2. The aligned product is added to the current contents of AM, and flags in the CCR are set accordingly.

3. The X and Y registers are incremented by x0 and y0, respectively.

4. Contents in H are saved in the Z index register.

5. The word pointed to by XK:IX is loaded into H and the word pointed to by YK:IY is loaded into I.

Before using the MAC command, place values into H and I with LDH I, which loads H with the word pointed to by XK:IX and I with that pointed to by YK:IY. See Listing 1 for an example.

## **188SBC**

Use Turbo or MS 'C Intel 80C188XL Two 1 meg Flash/ ROM sockets Four battery backed, 1 meg RAM 16 channel, 12 or 16 bit A/D 8 channel, 12 bit D/A 2 RS-232/485 serial, 1 parallel 24 bits of opto rack compatible I/O 20 bits of digital I/O Real-time clock Interrupt and DMA controller

8 bit, PC/104 expansion ISA bus Power on the quiet, 4 layer board is provided by a switcher with watchdog and power fail interrupt circuitry.

The 188SBC is available with Extended Interface Emulation of I/O - a Xilinx Field Programmable Gate Array and a breadboard area. Define and design nearly any extra Interface you need we'll help! 188SBC prices start at \$299. Call right now for a brochure!

#### True Low-cost In-circuit Emulation

The DryICE Plus is a low-cost alternative to conventional ICE products. Load, single step, Interrogate, disasm, execute to breakpoint. Only \$448 with a pod. For the 805 1 family, including Philips and Siemens derivatives. Call for brochure!

| Listing | <b>; 2</b> —The SPIKE                        | E.ASM sample program         | produces an audio waveform by shifting the D register.                                                  |

|---------|----------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------|

|         | I NCLUDE<br>I NCLUDE<br>I NCLUDE<br>I NCLUDE |                              | ; initialize reset vector                                                                               |

|         | ORG                                          | \$0200                       | ;start prog after interrupt vectors                                                                     |

| ****    | Initiali                                     | zation Routines              | s ****                                                                                                  |

|         | INCLUDE                                      | 'INITSYS.ASM                 | ;set <b>EK=F</b> , <b>XK=O</b> , YK=O, <b>ZK=O</b><br>;sys <b>clock at</b> 16.78MHz, <b>disable COP</b> |

|         | INCLUDE                                      | 'INITRAM.ASM                 |                                                                                                         |

| ****    | Start of                                     | main program                 | ****                                                                                                    |

|         | LDD<br>STD<br>LDD                            | #\$03FF<br>CSPAR1<br>#\$0200 | <pre>set CS6-CS10 as 16-bit chip selcts block size = 2k</pre>                                           |

|         | STD<br>LDD                                   | CSBAR6<br>#\$0300            | CS6 active when address = \$02XXXX<br>block size = 2k                                                   |

|         | STD<br>LDD                                   | <b>CSBAR8</b><br>#\$7430     | CS8 active when address = \$03XXXX<br>chip selects are asynchronous,                                    |

|         | STD<br>STD                                   | CSOR6<br>CSOR8               | write only with data strobe,<br>in user space                                                           |

| ****    | Set DAC #                                    | 2 for offset v               | voltage *****                                                                                           |

|         | LDX<br>LDAB<br>TBXK                          | #0000<br>#03                 | ;essential <b>for proper chip select</b><br>;CS8                                                        |

|         | LDAA<br>LDAB<br>STD                          | #0C<br>#00<br>\$0000,X       | ;8 gives zero volts<br>;\$0C gives DC offset<br>;(offset value: \$0-\$F or 0-15)                        |

| ****    | Increment                                    | and send word                | to DAC #1 *****                                                                                         |

| START:  | LDAA<br>LDAB<br>TBXK                         | #00<br>#02                   | :CS6                                                                                                    |

|         | LDAB                                         | #04                          | ;start with D= 0004                                                                                     |

| 0UT1:   | STD<br>ASLD                                  | \$0000,X                     | ;multiply <b>by two</b>                                                                                 |

|         | CMPA<br>BMI<br>CLRB                          | #\$09<br><b>0UT1</b>         | ;stop when A>8                                                                                          |

|         | LDAA                                         | #08                          | ;reset A & B                                                                                            |

| OUT2:   | STD<br>ASRD                                  | \$0000, X                    | ;divide <b>by two</b>                                                                                   |

|         | BCC<br>JMP                                   | OUT2<br>START                | -                                                                                                       |

| ****    | Exception                                    | ns/Interrupts                | ****                                                                                                    |

| BDM:    | BGND                                         |                              | ;exception vectors point here<br>; and put the user in bckgrnd mode                                     |

DACs, and use the D register for 16-bit shifts.

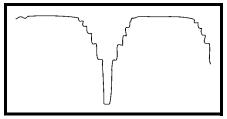

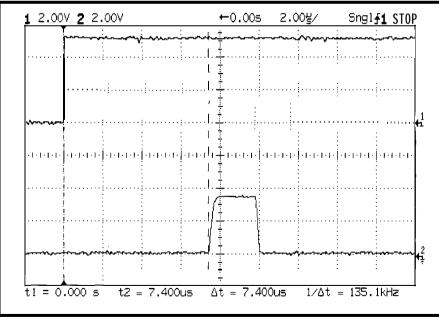

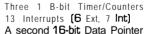

An oscilloscope on the output of U13 shows what first appears to be a rectified sine wave (Figure 3). But a close examination of the program and the waveform show that it is far removed from a sine wave-change a few parameters and the results look quite different. Specifically, DAC #2 has been held at a constant offset. At the next level, we can vary this according to external input such as the A/D section or an interrupt, for example.

| Binary             | into <b>DAC</b>          | Analog Output                           |

|--------------------|--------------------------|-----------------------------------------|

| <u>MSB</u><br>1111 | L <u>SB</u><br>1111 1111 | $+V_{IN}\left(\frac{2047}{2048}\right)$ |

| 1000               | 00000001                 | $+V_{IN}\left(\frac{1}{2048}\right)$    |

| 1000               | 00000000                 | 0 V                                     |

| 0111               | 1111 1111                | $-V_{IN}\left(\frac{1}{2048}\right)$    |

| 0000               | 00000000                 | $-V_{IN}\Big(\frac{2048}{2048}\Big)$    |

Table 1 - - The DAC1222 digital-to-analog converter

produces a bipolar output referenced to V,,

From here, it's up to your imagination. If you plan to work with the M68HC 16, you really should have the following: the *CPU16* Reference *Manual* (software descriptions), the M68HC16 *User's Manual* [for voltage

Figure 3—Looking at U13 pin 6 when running SPIKE . A SM produces something like a rectified sine wave.

and timing specifications), and the MASM16 assembler from Motorola. Also, the EVB16 debugger and PAL firmware from P&E Microsystems work quite well with MASM16 and greatly speed learning the ins and outs of this device.

Dana Romero holds a B.S. in Mathematics from the University of Utah.

#### CONTACT

P&E Microsystems P.O. Box 2044, Woburn, MA 01888 (617) 944-7585 Fax: (617) 353-9205

Motorola (602) 952-4103 Fax: (602) 952-4067

#### IRS

401 Very Useful 402 Moderately Useful 403 Not Useful

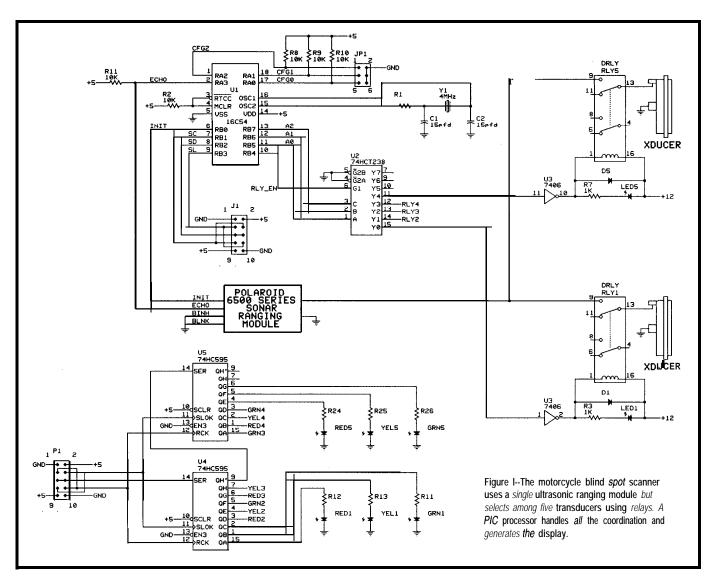

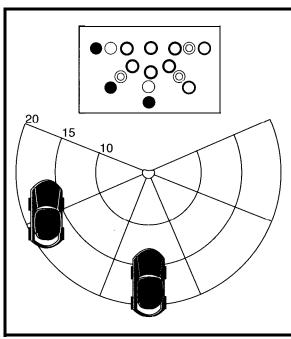

# DRAM on an 8031: It's Not as Hard as You'd Think

Although the 8051 family is not designed to use DRAM, it can be done. Hugo shows us how to connect the 8051 family CPU to 256 KB or more DRAM.

## FEATURE ARTICLE

**Hugo Cheung**

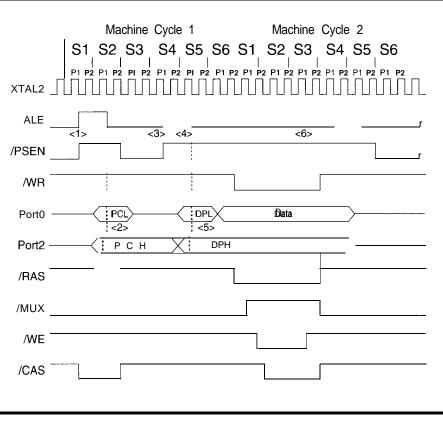

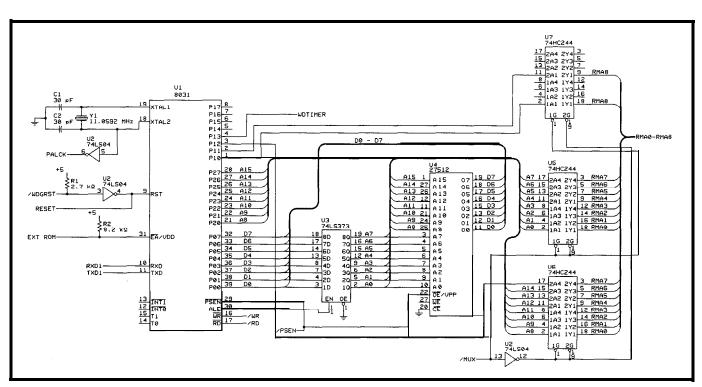

However, using DRAM is inconvenient because of its need to be refreshed with burst modes or cycle stealing. Burst refresh requires the CPU to stop accessing the refreshing DRAM. Cycle stealing, which I use in this application, refreshes the DRAM during the CPU instruction fetch cycle: Unlike the methods used for the IBM PC, XT, or AT, these refresh techniques have no software overhead and the CPU doesn't need to halt while DRAM refreshes.

After looking at the timing for DRAM, I'll investigate the timing for the 8051 (or any 8051 family device). Specifically, I'll look at how we can fit DRAM into an 805 1 application. Since understanding the detail timing of a system is critical to implementing DRAM in an application, I'll provide a lot of timing diagrams along with circuit diagrams.

#### **OVERVIEW OF THE 41256 DRAM**

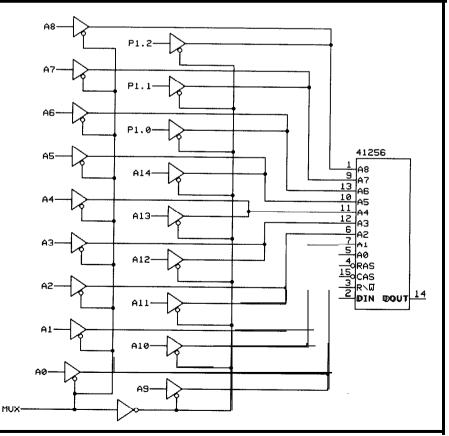

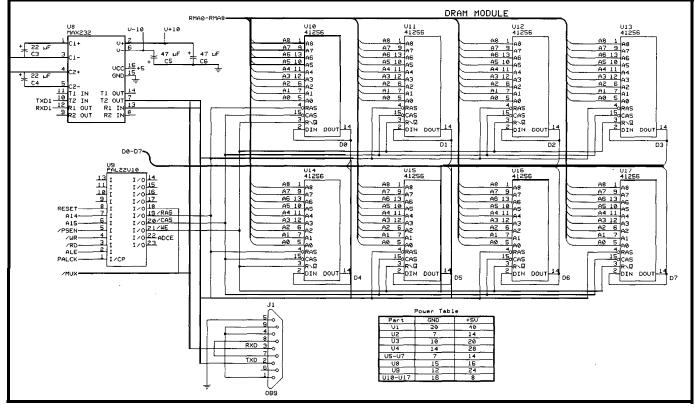

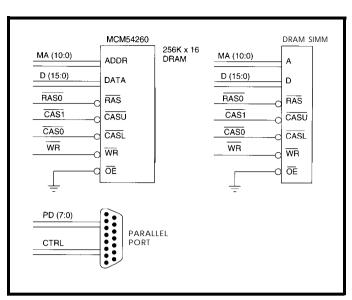

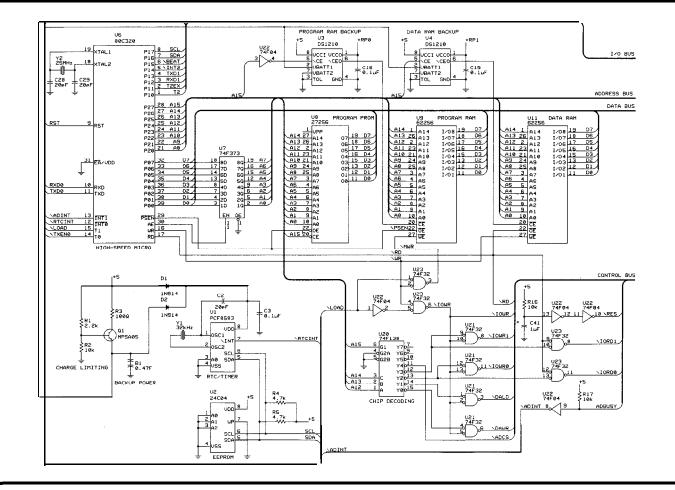

Figure 1— I he DRAM requires a multiplexer to switch the column or row address to the A0–A8 pins. The switching is controlled by the /MUX signal.

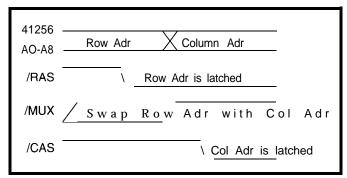

Figure 2—/RAS and /CAS latch the row and column addresses into the DRAM. The address multiplexing signal (/MUX) has to change between /RAS and /CAS.

**256** Kb of RAM and uses separate data input and output lines. It requires **18** address lines to give it a total of 256K address locations. The address lines are multiplexed to nine pins (AO-AS). The active-low multiplexing control signals are /CAS (column address strobe) and /RAS (row address strobe). All together, the 41256 has a total of 16 pins, including the /WE (active-low write-enable signal) and two power pins (+5 V and ground).

When /RAS is asserted, the information on the nine address lines is latched internally and is used as the lower 9 bits of the total 18-bit address. When /CAS is asserted, the informa-

tion on the nine address lines is used as the upper 9 bits of the complete 18-bit address.

#### ADDRESS MULTIPLEXING

The 8031 has 64 KB of address space for data memory and I/O. In my application, 32 KB from OOOOH to 7FFFH is allocated for the DRAM. The 256 KB DRAM requires 18 address lines. However, the CPU can only provide 15 address lines (AO-A14) from the address bus. To get the remaining lines, I used three bits of the CPU's Port 0 to make up a total of 18 address lines for the DRAM.

Figure 1 is a simplified circuit diagram of the address multiplexer. When /MUX the control line to the multiplexer-is low, the microprocessor's AO-A7 and P1.O are routed to the AO-A8 address input pins of the 41256. When /MUX is high, the microprocessor's A8–A14, **P1.1**, and **P1.2** are routed to the 41256's **AO-A8** pins.

Figure 2 shows the timing for /RAS, /MUX, and /CAS./RAS first goes active

when /MUX is low, indicating the low-order address bits are being presented to the DRAM. Next, /MUX goes low and /CAS is asserted to tell the DRAM that the high-order address bits are being presented. These three signals are generated by a PAL 22V10.I will describe the details of the PAL's contents later.

#### HOW TO READ AND WRITE DRAM

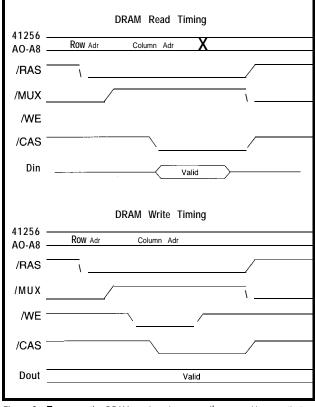

The 805 1 has /RD and /WR signals for data memory read and write timing control. /WE, which is the write-enable signal for the DRAM, has to be valid after /MUX and before /CAS become active. Figure 3 shows

Figure 3—To access the DRAM, we have to prepare the row address, activate /RAS, switch to the column address, set up /WE, and activate /CAS.

DRAM read and write timings. The DRAM read/write sequence of events is as follows:

- **1. Al5** is low (address = OOOOH to 7FFFH) and /MUX is low

- 2. /WR is low to write; /RD is low to read

- 3. /RAS goes low to latch the row address

- 4. /MUX goes high to switch the DRAM address bus from the column to row address

- 5. /WE goes low to write to DRAM or it goes high to read from DRAM

- 6. /CAS goes low to latch the column address

#### HOW TO REFRESH DRAM

The information contained in the internal storage cells of dynamic RAM must be accessed periodically to keep it valid. Typically, the information in a DRAM storage cell remains valid for only a few milliseconds. If the cell is not refreshed, the data is lost.

When data is read from the 41256, an entire row of the internal cell is refreshed in parallel. An entire RAM chip can be refreshed by accessing A0–

A7 during a 4-ms refresh period. To do this, we need to have a refresh counter, which can be implemented in software or hardware. However, to avoid the software or hardware overhead necessary to implement such a refresh counter, we can instead use the /*CAS before IRAS* refresh method.

Most DRAM currently available on the market has a built-in refresh counter and refresh-timing generator. The internal refresh clocks and refresh counters can be initiated by special timing in the /CAS and /RAS signals. From Figure 2, we know that read or write timing normally requires that /RAS be active before /CAS. If /CAS is active before /RAS, though, the DRAM internal decoding logic will trigger the internal refresh clock and counter. Consequently, a simple

| 1 |  |  |  |

|---|--|--|--|

|   |  |  |  |

|       | Machine Cycle 1 Machine Cycle 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|