## THE COMPUTER APPLICATIONS JOURN #56 MARCH 1995 FUZZY LOGIC

Fuzzy-Controlled Levitating Ball

Embedded Fuzzy Logic

Remote-Controlled Car Door Locks

Intel's 8xC251SB

# EDITOR'S INK

### Warm Fuzzies?

uzzy logic is an idea whose time has come. The Japanese and Europeans are far ahead of U.S. designers in embracing this novel programming approach. It's about time more engineers started to take notice. When sat down to choose themes for 1995, had one fuzzy logic article in hand, so decided to gamble and devote an issue to the topic. I'd been seeing it discussed elsewhere on a more regular basis, so thought it was time for us to take a look. I was pleasantly surprised when I ended up with three substantial articles and an extensive sidebar describing fuzzy logic and its applications, We even have a fuzzy-based home controller article waiting in the wings for a future issue of Home Automation & Building Control.

guess I shouldn't have been surprised. The methodology more closely approximates the way humans make decisions, so resulting control systems behave more "naturally." As more people become aware of its advantages, more writers will talk about it. I learned a lot working on this issue, and I hope you do, too.

Our first fuzzy article presents a good overview of what the technique is and how it can be applied to a simple temperature feedback system. Can fuzzy logic truly be called "the next generation of control"?

Next, we narrow the focus to see how fuzzy logic can be simplified enough to be effective on a small microcontroller with limited resources. It doesn't necessarily require lots of horsepower as was thought in the early days.

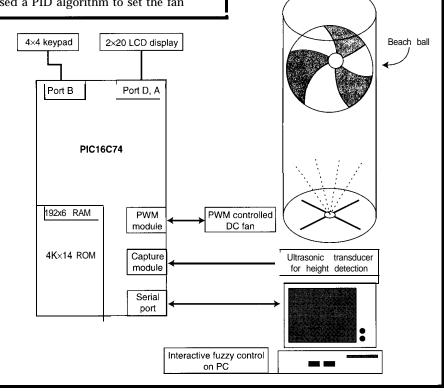

Our next article continues on the seemingly never-ending quest for the best way to levitate a ball on an air cushion. Tom Cantrell originally threw down the gauntlet and presented one approach based on PID algorithms. However, fuzzy turns out to be just as effective and requires less tweaking. The sidebar to this article presents yet another approach to the same problem.

Our final feature is a follow-up to another past article. In the February '94 issue, Do-While Jones cautioned against the indiscriminate use of interrupts. Mike Smith shows that under the right circumstances, software interrupts can be quite effective.

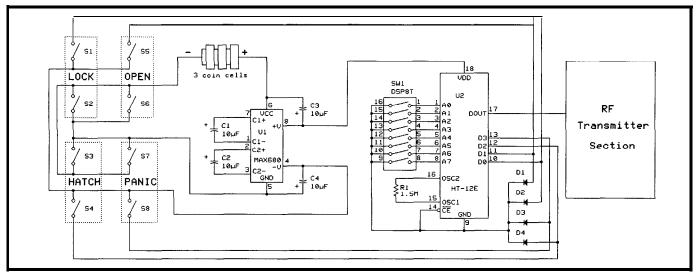

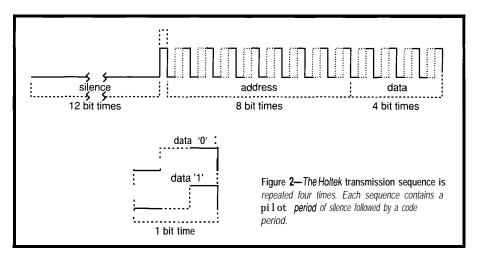

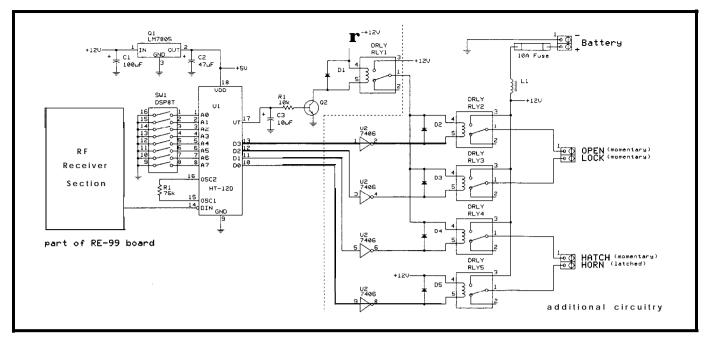

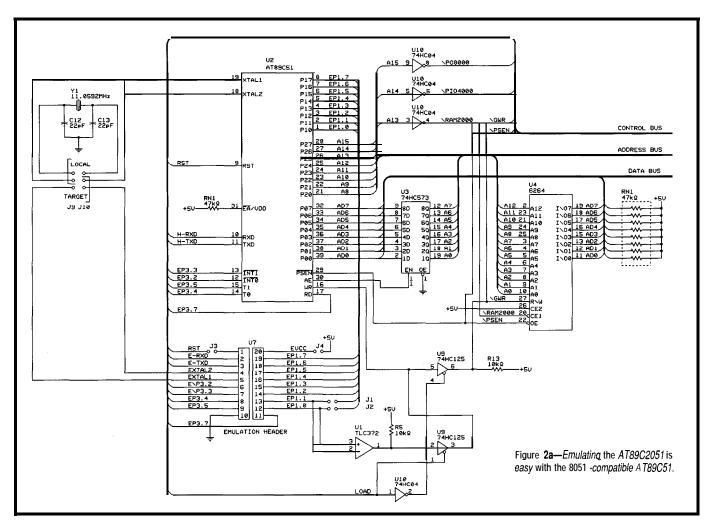

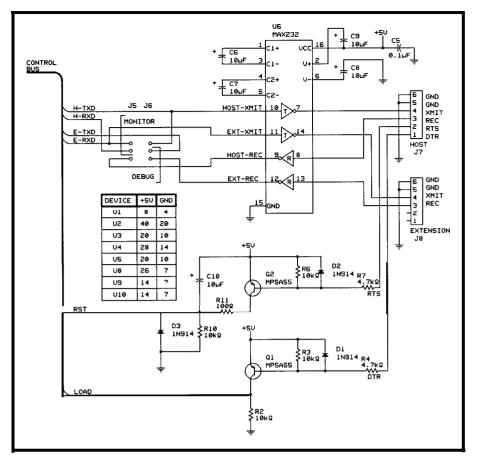

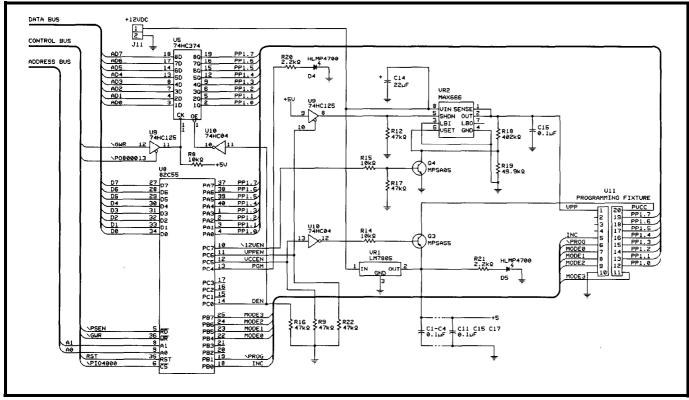

In our columns, Ed continues enhancing his multitasking kernel by providing a way for low-level tasks to access high-level routines. Jeff comes to Bev's rescue with an RF-based link to her car that enhances her safety in dark, lonely parking lots. Tom explores yet another 8051 derivative, but this one comes from the designers of the original 8051-Intel. Finally, John explains how to put together a low cost but highly effective development system for the Atmel AT89C2051.

llon

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

EDITOR-IN-CHIEF Ken Davidson

TECHNICAL EDITOR Janice Marinelli

ENGINEERING STAFF Jeff Bachiochi & Ed Nisley

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITOR John Dybowski

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR Lisa Ferry

**PRODUCTION STAFF** John Gorsky James Soussounis

CONTRIBUTORS: Jon Elson Tim McDonough Frank Kuechmann Pellervo Kaskinen

PUBLISHER Daniel Rodrigues

PUBLISHER'S ASSISTANT Sue Hodae

CIRCULATION COORDINATOR Mansella

CIRCULATION ASSISTANT Barbara Maleski

CIRCULATION CONSULTANT Gregory Spitzfaden

> **BUSINESS MANAGER** Jeannette Walters

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK, THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated. 4 Park Street. Suite 20, Vernon, CT 06066 (203) 875-2751 Second class postagepaid at Vernon, CT and additional offices. One-year (12 issues) subscription rate U S A and possessions \$21 95. Canada/Mexico \$31.95. all other countries \$49.95. All subscription orders payable in U.S. funds only. viainternational postal money order or check drawn on U S bank. Direct subscription orders and subscription related questions10 Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (600) 269.6301

POSTMASTER: Please send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Cover photography by Barbara Swenson PRINTED IN THE UNITED STATES

HAJAR ASSOCIATES NATIONAL ADVERTISING REPRESENTATIVES

NORTHEAST & MID-ATLANTIC Barbara Best (908) 741-7744

Fax: (908) 741-6823

SOUTHEAST Christa Collins (305) 966-3939 Fax: (305) 985-8457

WEST COAST Barbara Jones & Shelley Rainey (714) 540-3554 Fax: (714) 540-7103

MIDWEST Nanette Traetow (708) 789-3080 Fax: (708) 789-3082

Circuit Cellar BBS-24 Hrs 300112001240019600114 4k bps,8 bits, no parity, 1 stop bit, (203) 871-1988; 24001 9600 bps Courier HST, (203) 871-0549

All programs and schematics in Circuit Cellar INK have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects. Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK.

Entire contents copyright@ 1995 by Circuit Cellar Incorporated All rights reserved Reproduction of this publication in whole or inpart without written consent from Circuit Cellar Inc is prohibited

|    | 1                                                     | 4                                  |              | ry Logic: The Next Generation of Control<br>Bud Moss                                                            |

|----|-------------------------------------------------------|------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------|

|    | 3                                                     | 0                                  |              | ry Logic for Embedded Microcontrollers<br>im Sib&troth                                                          |

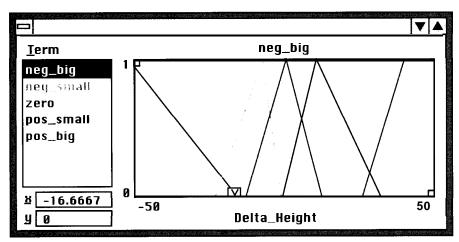

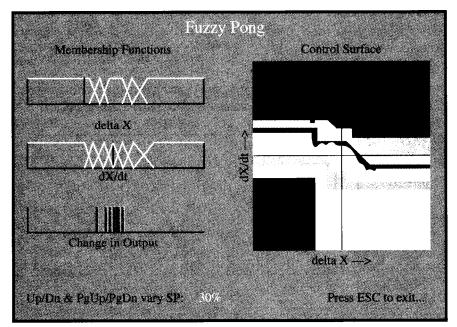

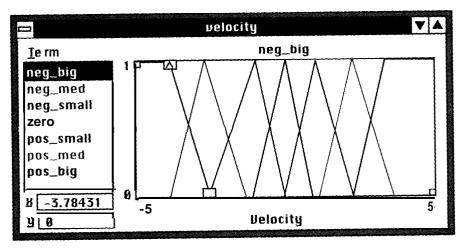

|    | 3                                                     | 8                                  | by i<br>Fuzz | tating a Beach Ball Using Fuzzy Logic<br>Robert Schreiber<br>zPong<br>David Rees-Thomas                         |

|    | 5                                                     | 0                                  | The          | ng ASSERTive with Your Processor<br>Advantage of Software Interrupts<br>Mike Smith & Kathy Kim                  |

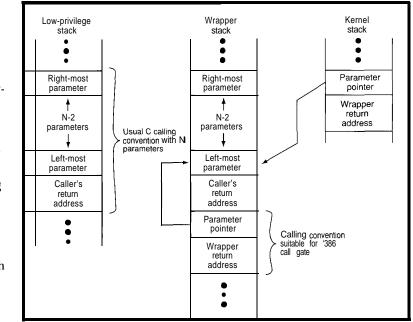

|    | 5                                                     | 8                                  |              | Firmware Furnace<br>Journey to the Protected Land: Smashed Gates & Conforming Code<br>Ed Nisley                 |

|    | 6                                                     | 8                                  | <u>الم</u>   | <b>From the Bench</b><br><b>RF</b> Panic Button Commands Multiple Automotive Functions<br><i>Jeff</i> Bachiochi |

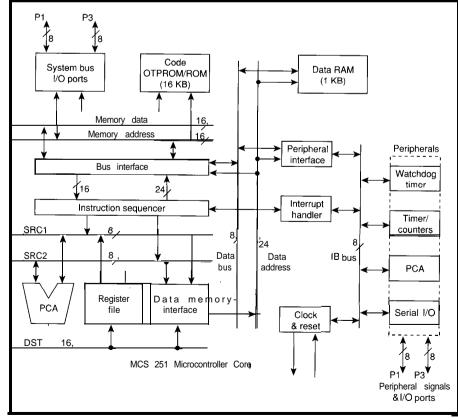

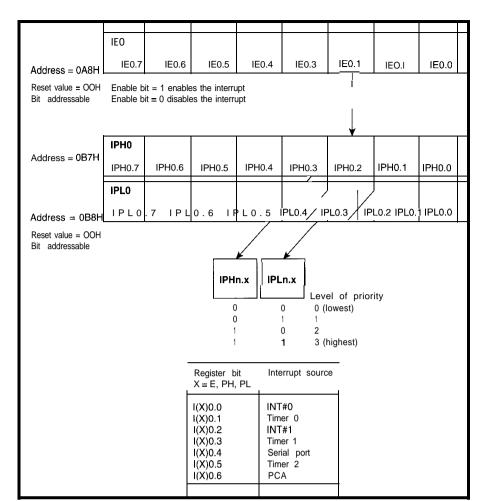

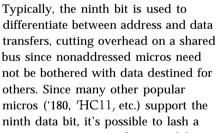

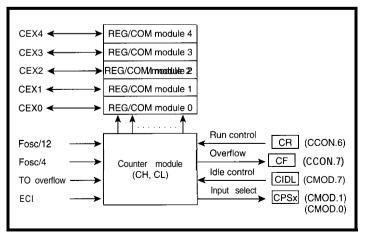

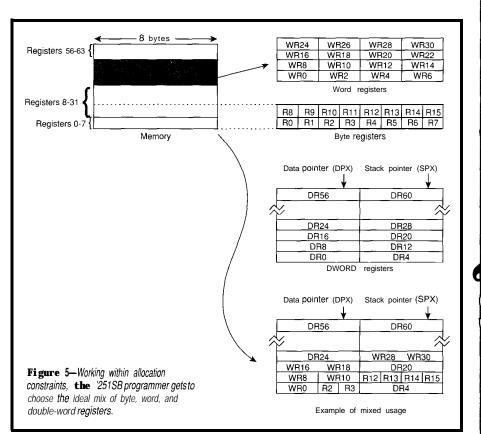

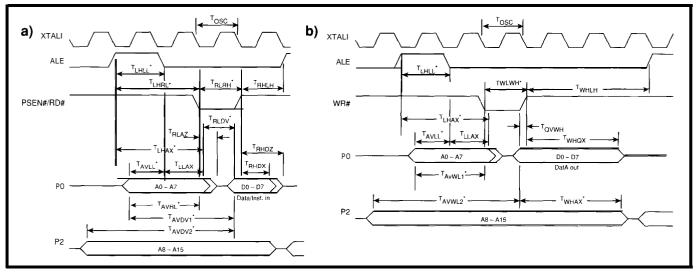

|    | 7                                                     | 2                                  |              | Silicon Update<br>Plan '251 from Outer Space<br>Intel's 8xC251 SB<br>Tom Can trell                              |

|    | 7                                                     | 8                                  |              | <b>Embedded Techniques</b><br>Embedded Development<br>John <b>Dybowski</b>                                      |

|    |                                                       |                                    |              |                                                                                                                 |

| 2  | <b>Editor's</b><br>Ken Da<br><b>Warm</b> I            |                                    | ,            | Steve's Own INK<br>Steve Ciarcia<br>Necessity: the Mother                                                       |

| 6  | New Pro                                               |                                    |              | Advertiser's Index 81                                                                                           |

| 85 | Connec<br>Excerpts<br>the Circu<br>conducte<br>Ken Da | <b>from</b><br>uit Cellar<br>ed by | BBS          | 56                                                                                                              |

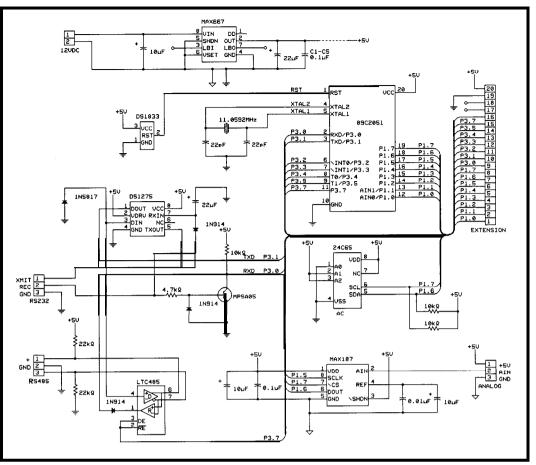

#### MULTIPURPOSE EMBEDDED CONTROLLER

Remote Processing has released a multipurpose embedded controller with an operating system, operator interface, and I/O on a single card. The RPC-320 uses the Dallas Semiconductor 80C320 CPU with a unique addressing scheme to access 1 MB of memory. Normally, the 80C320 (a variation of the Intel 8032) can only access 64 KB of RAM.

The RPC-320 features industrial I/O. It has 8 ADC input lines with 12-bit resolution, 20-MHz quadrature encoder and counter input, 34 digital lines, and 2 RS-232 or RS-485 serial ports. A keypad and LCD character and graphics port for operator interface are also included. Over 12.000 lines of code can be stored and executed to a flash EPROM by the oncard RPBASIC.

RPBASIC is an improved version of Intel BASIC-52 which directly supports the hardware using single commands. The included RPBASIC operating system accesses up to 1 MB of RAM and flash memory for data logging and program storage. Over 500 KB of programs can be autorun on powerup.

A built-in temperature transducer monitors ambient temperatures. Two operational amplifiers buffer, amplify, and filter inputs from sensors. The temperature transducer and amplifier can be connected directly to an ADC input, which accommodates eight single-ended or four differential inputs with ranges of O-5 or f2.5 V. Inputs are overload protected to  $\pm 25$  V.

The 20-MHz multimode counter interfaces to quadrature encoders or other high-frequency devices. Up and down counters interrupt the program when a preset count is reached. RPBASIC loads or reads a 24-bit number to the counter. Frequency measurements are possible with RPBASIC's multitasking feature. Many LCD displays interface to the display port. RPBASIC positions the cursor and writes to the display in a single command. Graphics commands draw lines and control pixels to show level or position. BASIC also scans and buffers entries from a 16-key keypad port.

The RPC-320 sells for \$365 and includes a hardware manual and RPBASIC. Remote Processing 6510 W. **91st** Ave. Westminister, CO 80030 (303) 690-I 588 Fax: (303) 690-I 875

#500

#### FAULT-TOLERANT POWER SUPPLY

A line of active fault-tolerant power supplies which provide mission-critical PC users with automatic backup power has been introduced by Antec. Available as a tower enclosure (KS022), file server tower (KS033), and disk array tower (KS044), the Reliant products are the first power supplies which cause absolutely no power interference to computer components.

Antec is also introducing the RPT-600, a unique AT-size, fault-tolerant power supply

designed with two built-in, 300-W power units. The RPT600 works as a highly efficient 600-W supply or as a loadsharing, fault-tolerant unit with two individual 300-W supplies. The Reliant immediately takes over when a master power supply fails to prevent damage due to overvoltage, overcurrent, and other power problems. If a master power supply fails, sophisticated diagnostics sound an alarm, alerting the user to hot-swap the failed power supply.

The RPT-600 sells for \$199, the KS022 for \$799, KS033 for \$1699, and the KS044 for \$1799.

Antec, Inc. 2859 **Bayview** Dr. • Fremont, CA 94538 (510) 770-1200 • Fax: (510) 770-1288 **#501**

#### DATA ACQUISITION AND CONTROL SYSTEM

Prairie Digital has introduced a low-cost dataacquisition and control system for all ISA bus computers. The Model 100 provides the most commonly used features of analog and digital I/O boards. Typical measurements include temperature, pressure, humidity, light levels, force, and acceleration.

Through software, users can select eight singleended channels or four differential channels. Conversions are performed in  $10 \ \mu s$  with 12 bits of resolution. Users set an input range of O-5 V or ±2.5 V. Four chan-

nels of 8-bit analog output (O-5 V) can also be selected.

Twenty-four lines of digital input and/or output are provided (eight lines are semidedicated) for controlling relays, lights, motors, switches, thermostats, and liquid levels. Also

provided are three 16-bit timer/counters for timing events, counting pulses, and generating interrupts with accurate timing.

Atlantis software enables the Model 100 to emulate strip-chart recorders, oscilloscopes, and digital voltmeters simultaneously. Up to ten instruments can be displayed at one time, including bar graphs and a real-time clock. Foreground or background sampling, software triggers, and user-definable macros are also featured.

Model 100 sells for \$279. Optional Atlantis software sells for \$79.

Prairie Digital, Inc. 846 17th St. Prairie du Sac, WI 53578 (608) 643-8599 Fax: (608) 643-6754

#502

#### UNIVERSAL **FRONT-**PANEL CONTROLLER

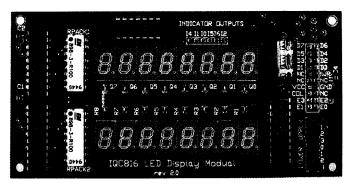

The IQC816 Universal Front-Panel Controller chip from IQ Systems is the first in a series of chips which greatly simplifies incorporating encoders, displays, keyboards, switches, sound, and speech in electronic products. The product family is founded on a new command set which provides a standardized user interface regardless of the host processor type.

IQC8 16 can support 32 digits of LED display addressed as 4 displays of 8 digits. Displays can be concatenated for more than 8 digits or reduced in width for increased brightness. An intelligent display offers features such as left and right formatting, choice of cursors, alpha decode, programmable display width, and so on. Thirtytwo segments of LCD display plus 4 x 40 lines of alphanumeric smart LCD display are also supported.

Sixteen nonmultiplexed outputs drive actuators, relays, or incandescent bulbs. Eight rotary encoders with full quadrature decoding are supported, and each encoder is supported by an 8-bit up/down counter. Forty-eight standard switches (176 with shift, control, and alternate key modifiers) can be supported. The output buffer is 8 bytes deep and records switch scan codes and the address of encoders which have changed state. A sound generator with programmable frequency and duration and an UART are also on the chip.

The software interface is flexible and easy to use. The goal is to standardize the user interface command set in much the same way as the interface to modems was standardized with the Hayes AT command set.

The IQC8 16 is available in a 40-pin DIP package and sells for \$19.95 in single quantity and \$9.95 in 1000s. An evaluation kit is available for \$95. The kit, which contains C drivers for the IBM PC and numerous application examples, enables a designer to plug on displays, encoders, speakers, and so on, then couple them to any host with a UART.

IQ Systems, Inc. 20 Church Hill Rd. Newtown, CT 06470 (203) 270-8667 Fax: (203) 270-9064 Internet: 76636.3267@ compuserve.com

#503

#### **PENTIUM** COOLING SOLUTION

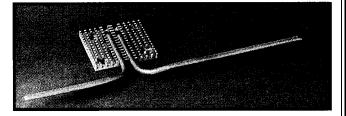

Thermacore Inc. has announced a new series of standard and customizable products designed to cool Pentium or other high-performance processors in notebook computers. The Processor Thermal **Manage**ment Systems offer high-efficiency cooling without noise, moving parts, or electrical power requirements. The performance of these compact solutions helps chips such as the Pentium to maintain case temperatures at less than 40°C over the ambient temperature, thereby ensuring the chip's intended life and performance characteristics.

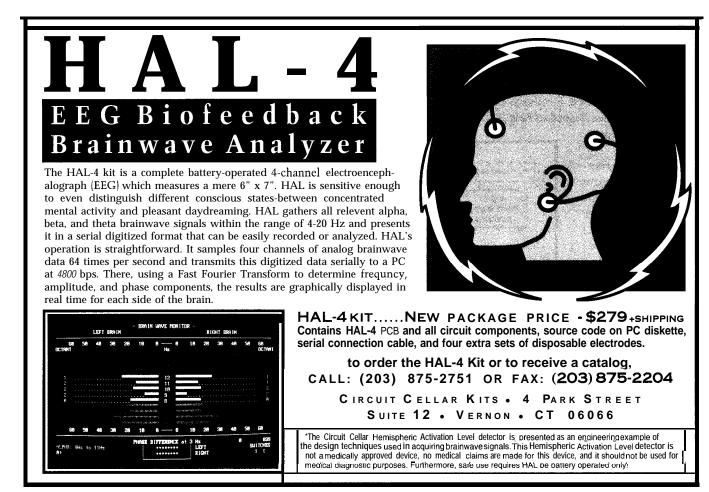

This new line of products uses Thermacore's exclusive heat-pipe technology. Through this passive technology, heat is moved from the chip's surface via a two-phase heat-transfer process which requires no moving parts or power from a notebook's battery. Depending on design and space considerations, heat can then be dissipated by natural convection using fins attached to the heat pipe or through existing components such as the keyboard's aluminum back plane, which can act as a heat sink.

Unlike other heat-transfer solutions, Thermacore's products have been designed from the ground up for the notebook computer. For example, they operate in any position the user places the notebook, including upside down. Its light-weight (less than 65 g for the full heat sink) and snap-on chip design optimize manufacturing while its mean time to failure is over 100,00 hours.

Thermacore's new products are available immediately. Designs can be modified to fit any style case or board configuration.

Thermacore, Inc. 780 Eden Rd. Lancaster, PA 17601 (717) 569-6551 Fax: (717) 569-4797

#504

#### PASSIVE BACKPLANE SBC

The PCI-930 from Teknor Microsystems is a '486DX-based, passive backplane CPU card, operating at processing speeds of up to 100 MHz with Intel's DX4 microprocessor chip. The ICI-930 is designed to the new PICMG Rev 2.0 industrial PCI

specification and offers full PCI and ISA passive backplane compatibility. This standard enables compatible cards to run on a shared PCI and ISA passive backplane.

Full onboard I/O, such as hard and floppy disk controllers, serial, parallel, and keyboard ports, and bootable flash memory, is standard on the card. SVGA resolutions to 1024 x 768 x 256 colors are included. OEM designers gain fast video access through a 32-bit PCI local-bus interface to Cirrus Logic's CL-GD5430 videoprocessor chip. High PCI transfer rates (up to 132 MBps) provide maximum throughput and help alleviate system bottlenecks. The card also includes a 256-KB write-back cache, a real-time clock with battery backup, AM1 BIOS, watchdog timer, SVGA output, and mouse port.

Configurable with up to 128-MB DRAM and up to 4-MB flash memory, the ICI-930 is wellsuited for highspeed, performance-

dependent applications such as medical imaging, telecommunications, and industrial automation.

PCI-930 microprocessor configuration options include an Intel '486DX @50 MHz, '486DX2@66 MHz, and '486DX4@100 MHz. The '486DX-50 entry-level version is priced at \$1595.

Teknor Microsystems, Inc.

616 **Curé** Boivin • Boisbriand, Quebec • Canada **J7G 2A7** (514) 437-5682 • Fax: (514) 437-8053

#505

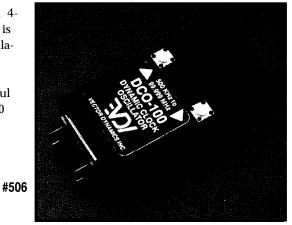

#### DYNAMIC CLOCK OSCILLATOR

Vector Dynamics has introduced the **DCO-100 Dynamic Clock Oscillator**, a self-contained test instrument for development engineers. This product emulates an oscillator toolbox, eliminating the need to stock multiple oscillator frequencies to meet the demands of new product design.

The DCO-100 provides user-selectable clock frequencies from 500 kHz to 99.999 MHz in 1-kHz steps. Changes in frequency are glitch-free, allowing on-the-fly frequency selection without removing it from the circuit under test. Frequency is selected by using two push buttons and is displayed on a 5-digit decimal display located at the top of the module. The module can be easily reprogrammed to any frequency within its range, making it a versatile development tool which can be reused on other projects.

The DCO-100 module has an identical footprint to a standard 4pin (14-pin configuration) full-size, fixed-frequency oscillator and is powered by the 5 V normally provided to pin 14 of the clock oscillator in the circuit. The unit's dimensions are 1.27" x 2.75" x 0.5".

The DCO-100 includes a built-in display and programming buttons, so no accessories are needed. A user handbook with useful application notes and storage box are also included. The DCO-100 sells for \$200.

Vector Dynamics, Inc. 1880 Tanglewood Dr. NE • **St.** Petersburg, FL 33702 (813) 526-7038 • Fax: (813) 527-6534

#### MULTIPLE METER SOFTWARE

AGX has introduced a new, multiple-meter software product with drivers for most serial interface meters. Metersoft offers real-time display, meter monitor and logging, controllers, counters, bar graphs, sensors, and transmitters with an RS-232 or RS-485 serial interface. Metersoft displays 1, 4, 9, or 16 meters per PC screen with alarms, channel ID, engineering units, and trending information.

Metersoft provides such as uniform meter setup and configuration, data logging, multiple-meter display, test and measurement, quality control, and the creation of virtual meters (for example, you could determine the

sum or difference of two real meters).

Priced from \$99, Metersoft provides the user with a low-cost data acquisition and monitoring system for existing and newly purchased meters.

AGX Corp. Metersoft Division 5761 **Uplander** Way Culver City, CA 90230 (310) 642-6663 Fax: (310) 642-6661 **#507**

#### MICROCONTROLLER BOOK

Lakeview Research has announced a handson guide of circuits, programs, and applications featuring the 8052-BASIC single-chip

computer. Jan Axelson's *The Microcontroller Idea* Book presents practical designs for use in data loggers, controllers, and other embedded computer applications. In addition to the basic circuits needed for

any project, the book shows how to add keypads, switches, relays, displays, sensors, clock/calendars, motor controls, wireless links, and other I/O interfaces.

This 277-page book includes complete circuit schematics, parts lists, design theory, construction and debugging tips, and program listings. Circuit and program

#### DATAACCESS ARRANGEMENT

The first all-silicon, full-function Data Access Arrangement (DAA) has been developed by Krypton Isolation. The **K**<sup>2</sup> DAA chip set provides isolation from 1.5 and 2 kVDC (3.5 kVDC for European standards) in stand-alone, card-level, and PCMCIA fax modems for computers ranging in size from

portable and hand-held systems to desktop workstations.

As a total solution to the problem of isolating modem chip sets from the telephone line, the devices are easy to use, lower in cost than other forms of DAA, and function at all speeds up to V.32, V.32bis, and V.34. It is designed to mount inside any kind of fax-modem card housing without any modifications to the motherboard. The chip set connects directly to the telephone line.

Other features of the  $K^2$  chip set include off-hook relay control, ring-indication control, internal 2-to-4 wire conversion, and caller ID.  $K^2$  offers a power-down mode, operation from a single 5-v source, and low power consumption. The chip set includes one device in an 8pin SOIC package, one in a 16-pinQSOP package, and one in a 20-pin QSOP package. The chip set meets all appropriate standards.

The K<sup>2</sup> Chip Set sells for \$8.50 in quantity.

Krypton Isolation, Inc. 39111 Paseo Padre Parkway, **Ste.** 202 Fremont, CA 94538 (510) 713-9100 Fax: (510) 713-9188

#508

examples are based on the popular 8052-BASIC microcontroller, whose onchip BASIC interpreter includes over 100 commands, statements, and operators for convenient writing, running, and debugging of programs. Special commands store user programs in EPROM or other nonvolatile memory. As a member of the 8051 microcontroller family, the chip uses a standard, popular architecture.

**The Microcontroller Idea Book** sells for \$31.95 plus \$3.00 shipping.

Lakeview Research 2209 Winnebago St. Madison, WI 53704 (608) 241-5824 **#509**

### FEATURES

14

30

38

42

Fuzzy Logic: The Next Generation of Control

Fuzzy Logic for Embedded Microcontrollers

Levitating a Beach Ball Using Fuzzy Logic

PC FuzzPong

50

Being ASSERTive with Your Processor

As Bud points out, fuzzy logic balances many factors in measurable and mathematically precise ways. A myriad of graphs help visualize the fuzzy-logic decisionmaking process.

Fuzzy Logic:

The Next

Generation

of Control

## FEATURE ARTICLE

Bud Moss

uzzy logic is another step toward eliminating the need tooreclure our thoughts to

the point they become unrecognizable. It lets us design the core software of a control system or similar task using a method which simulates how we think. It's no longer necessary to break down our ideas into line after line of code or long, complex equations. Instead, we can use graphs and shapes, and a few IF... THEN rules complete the system.

Fuzzy logic is not for everyone just most of us. If you enjoy generating and optimizing equations more than implementing and debugging the system, fuzzy logic may not be for you.

For the rest of us, it's well worth the effort.

#### ABSOLUTESVERSUS GENERALIZATION

Have you ever been hiking and had to cross a stream, but there wasn't a bridge?

My first reaction is to look for another way. Scanning the water, I search for rocks that can be used as stepping stones. To pick the right rocks, 1jump into the water and document every characteristic of every rock using the tools-a protractor and ruler-I just happened to pack. Next, I generate a formula, plug the data into a calculator, and hope. Two or three days later, the stream is conquered and I'm on my way.

Not very likely.

Instead, I base my decision on approximations. First, I decide which characteristics should be considered and how important they are compared

to the others. I know that rocks with a large flat top are easier to stand on and the closer together they are the better. I also know that the distance between them is more important than the shape of the top. After finding how well each rock fits the categories, I choose the right one.

Fuzzy logic follows a similar process. It allows us to be imprecise and still arrive at the correct answer. By setting up graphs (size, top, and distance), adding shapes (large, flat, and close), and specifying the rules (IF the rock is small AND pointed OR is too far away, THEN eliminate it), I come up with the best rocks.

Unlike a system that uses absolutes, this system, once it is proven, enables me to find the correct rock in any stream, not just this one.

#### **ITS BEGINNINGS**

In 1965, Lotfi Zadeh found that, due to the contradictory nature of control systems, they were not easily represented using the traditional method of mathematical modeling. He theorized that adding imprecision to the system would allow it to react more precisely when presented with conflicting input data. His article "Fuzzy Sets" launched the field of fuzzy logic.

Western countries didn't exactly jump when fuzzy logic was born. In fact, it took almost 30 years for it to hit mainstream media. There's

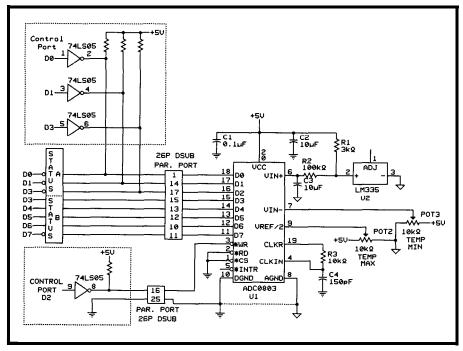

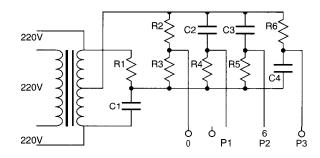

Figure 2—AnLM335 converts temperature to a voltage which is digitized by the ADC0803. The digital value is transferred to the PC via one of the parallel ports.

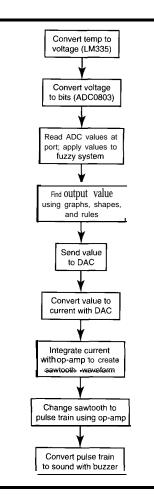

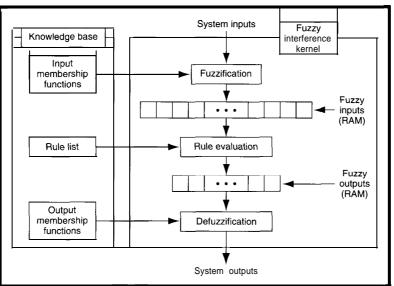

Figure I--The sample fuzzy logic system described starts with temperature and ends with sound. However, if doesn't simply pass the ADC output value to the input of a DAC.

probably a multitude of reasons, but most are related to the fact that the system could not be proven mathematically. Some believed that an unprovable system was the same as no system. Others were uncomfortable with the word fuzzy-an excellent word for what it describes, but to those accustomed to precision, it may not have been the best choice.

Unlike the West, the Japanese were interested. The word fuzzy was not translated, but transferred phonetically, thereby facilitating the acceptance of the concept at face value. With an easy acceptance, the Japanese went straight to the next step experimentation, which quickly demonstrated that traditional methods of proof were unnecessary. For years, the Japanese have marketed fuzzybased products.

But, the West is catching up. In the last few years, many companies have been developing products based on fuzzy logic concepts. Most large IC manufactures are marketing microcontrollers and coprocessors optimized to perform in a fuzzy-logic environment.

For example, did you know that fuzzy logic controls the Saturn automobile's transmission? The designers found that they achieved better performance and smoother operation with fuzzy logic than they did using a traditional approach. This trend should continue as more designers see the benefits of this type of control.

#### THE HARDWARE

To gain an understanding of fuzzy logic, we'll use the simplest control problem: one input and one output. Figure 1 shows the flow of an entire system. We'll vary the frequency of a speaker as the room temperature varies.

The hardware was designed to show the ease of setting up a control system based on fuzzy logic. Most of

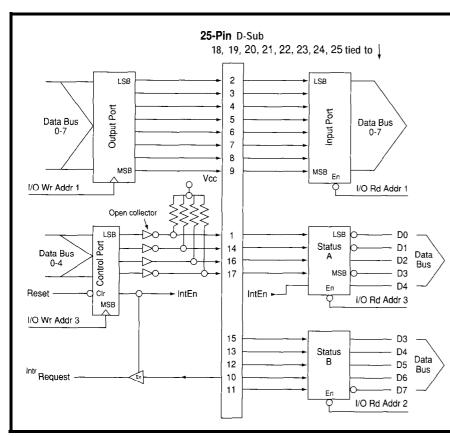

Figure 3—Instead of using a board, the interface to ADC and DAC is done through a 25-pin D-sub printer port connector.

us have an unused parallel port or an A/B box. Instead of using another slot in the PC, the hardware interface will be done via the PC's printer port.

#### **TEMPERATURE TO VOLTAGE**

The LM335 converts the room temperature into a voltage that's used to feed the ADC. Basically, it's a zener diode whose breakdown voltage varies proportionally with temperature. For each Kelvin degree, the junction voltage changes 10 mV. (Remember Kelvin begins at absolute zero, which is  $-459.67^{\circ}$ F. To convert Kelvin to Fahrenheit, use the following formula:  $F^{\circ} = 1.8 \times Kelvin - 459.67^{\circ}$ .) To hold the input stable, R2 and C2 are configured as a low-pass filter with a one-second time constant.

8analog-640-kHz

Frequency=

$$\frac{1}{1.1 \times R3 \times R4}$$

with R3  $\approx 10~k\Omega.$  The range of input voltages is set using the  $V_{\rm IN-}$  and  $V_{\rm REF/2}$  pins and the potentiometers connected to them.

For example, if the minimum input voltage is 0.5 V and the maximum is 3.5 V, the reference voltage is (3.5 - 0.5)/2

$\begin{array}{c} V_{IN_{*}}I \text{ with both } \\ V_{IN_{*}}at \quad 0 \quad . \quad 5 \quad V \quad V_{IN_{*}}I \quad d \\ 1 \end{array}$

of the printer port's hardware. Table

| <u>Addr</u> | Port 1 | Port 2 | Port 3 |  |

|-------------|--------|--------|--------|--|

| 1           | 3BC    | 378    | 278    |  |

| 2           | 3BD    | 379    | 279    |  |

| 3           | 3BE    | 37A    | 27A    |  |

|             |        |        |        |  |

Table I--The actual I/O port addresses used in your code depend on which physical parallel port you're using. The Addr numbers correspond to the Addr labels in Figure 3.

ports. Don't confuse the address of LPT1 with that of port 1. They may not be the same. The operating system sets the address of LPT1 equal to the first parallel port found, which may or may not be port 1.

Each parallel port can be broken into four sections: status, control, input, and output. The circuitry uses every free line of the port, except the interrupt to the processor, which must remain off (control port D4 = 0). Depending on how your system is configured, you may end up with unexpected results or a system crash if you forget this.

The software used to read the ADC is shown in Listing 1. To start the conversion, we drive D2 of the control port low then high pulse the WR pin. After giving the ADC time to digitize the voltage, the data can be read.

The port's hardware wasn't designed for this, so to get the data, we have to do a little manipulation. First, bits O-2 are read from Status A via data bits 0, 1, and 3. There is a reason

Listing I--This procedure reads the ADC and returns the value read in the AX register. The equates are used in all three listings.

| Port           | equ  | 0378h          | base address of port to use<br>change this if different                                                                                                              |

|----------------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| StatusPort     | equ  | Port+1         | addr of status port for rd                                                                                                                                           |

| ControlPort    | equ  | Port+2         | addr of ctrl port                                                                                                                                                    |

| Dos            | equ  | 021h           | DOS interrupt                                                                                                                                                        |

| Screen         | equ  | 010h           | BIOS int for screen access                                                                                                                                           |

| GetDisplay     | equ  | 0fh            | get video mode                                                                                                                                                       |

| Cls            | equ  | 00             | set video mode                                                                                                                                                       |

| Di spl ay      | equ  | 02             | DOS display char function                                                                                                                                            |

| PositionCursor | equ  | 02             | BIOS set curser function                                                                                                                                             |

| Exi t          | equ  | 020h           | program exit                                                                                                                                                         |

| GetKey         | equ  | 08             | func to get char from keybd                                                                                                                                          |

| KeyPressed     | equ  | 0ffh           | key was pressed                                                                                                                                                      |

| CheckKey       | equ  | 0bh            | function to check key pressed                                                                                                                                        |

| LoopsToWait    | equ  | 0              | each loop takes 17 clocks. To<br>find number required for your<br>system, Loops = $115 \ \mu s/time$<br>period of PC clock/17 (e.g.,<br>a 33-MHz PC needs 224 loops) |

| GetADValue     | proc | near           |                                                                                                                                                                      |

|                | mov  | dx, Control Po | ort                                                                                                                                                                  |

|                | mov  | ax, 04         |                                                                                                                                                                      |

|                | out  | dx,al          | ;set start to 1 just in case                                                                                                                                         |

|                | xchg | ah,al          |                                                                                                                                                                      |

|                | out  | dx,a]          | ;start to O                                                                                                                                                          |

|                | xchg |                |                                                                                                                                                                      |

| _              | out  | dx,al          | ;then <b>back to</b> 1 (continued)                                                                                                                                   |

#### Listing 1-continued

| WaitOnAd:  | mov   | cx, LoopsTo | Wait ;number of loops for 115 $\mu s$ |

|------------|-------|-------------|---------------------------------------|

| war conau. | l oop | Wai t0nAd   |                                       |

|            | in    | al,dx       | ;get the first 3 bits                 |

|            | not   | al          | ;complement all the bits              |

|            | mov   | ah,al       | 1                                     |

|            | and   | ah, 07      | :unused <b>bits to</b> O              |

|            | shr   | al.1        | ;D3-D2 position                       |

|            | and   | al, 04      | ;mask all but D2                      |

|            | or    | ah,al       | ;DO-D2 in ah                          |

|            | mov   | dx,StatusP  | ort                                   |

|            | i n   | al, dx      | ;get D3-D7                            |

|            | and   | al,Of8h     | ;dump DO-D2                           |

|            | or    | al,ah       | ;OR <b>in</b> DO-D2                   |

|            | test  | al,080h     | ;top bit a one?                       |

|            | jnz   | AndAZero    | ;no                                   |

|            | or    | al,080h     | ;invert top bit                       |

|            | ret   |             | -                                     |

| AndAZero:  |       |             |                                       |

|            | and   | al,07fh     | ;invert top bit                       |

|            | ret   |             | -                                     |

| GetADValue | endp  |             |                                       |

|            |       |             |                                       |

behind using D3 instead of D2. Notice that the clear input of the control port is tied to the PC's reset line. On powerup, pins 1, 14, and **17** are pulled high, pin 16 is driven low. The outputs are open collector. Thus, by using pin 17, we eliminate the possibility of bus contention with data bit 2 of the ADC.

The other five bits, D3–D7, are read at Status B. Notice bits DO-D2 and D7 are inverted by the port's hardware and must be reinverted to be used. A couple of lines of code later, we're back to the original byte.

#### **BITS TO VOLTAGE**

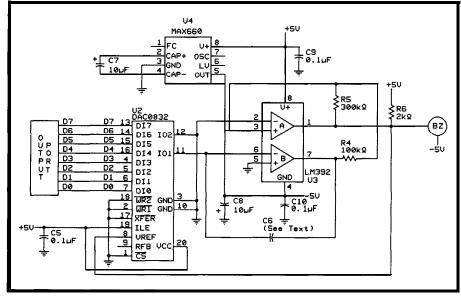

After the value from the ADC is processed by the fuzzy system, the DAC in Figure 4 converts it back to a value we can use. The DAC0832 is a double-buffered, multiplying DAC with complementary current outputs that is easily interfaced to many microprocessors.

The 8-bit value to be converted is simply sent to the DAC's data lines. The resulting current is presented on the  $I_{OUTI}$  pin. External conditioning circuitry then converts the current to a

Figure 4—After the ADC's value is processed by the fuzzy system, a DAC0832 and associated circuitry drive a piezoelectric buzzer. The buzzer's tone varies with the room temperature.

#### A Complete Family of Data Acquisition Products from

## American Eagle **Technolog**

- Data acquisition rates from 100kHz to 1 MHz.

- Newest designs incorporate the latest technology: FIFO buffers, dual-DMA, REP INSW data transfers, programmable gains, etc.

- Simultaneous sampling option for all boards.

- Lowest prices on the market for comparable performance.

- Digital I/O w/ on-board relays.

- 16-bit analog output (D/A).

- Large inventory of popular items for next day delivery.

- Also available: signal conditioning, multi-port serial boards, device programmers, logic analyzers, & much more.

#### Only American Eagle Technology Gives You All This Free Software:

- WaveView menu-driven software

- *Discstream* high-speed streaming software

- Complete software developers' kits for both DOS and Windows

- Drivers for all popular application programs such as LabView, LabWindows, Notebook, SnapMaster and DASyLab

voltage if necessary. The current at the output can also be affected by using the V<sub>RFF</sub> input for feedback.

Software to set the DAC is shown in Listing 2. The byte is written to the output port and immediately converted to a DC current.

#### CURRENT TO SOUND

The remainder of the circuitry in Figure 4 converts the current from the DAC to a pulse train that drives a buzzer. To stay with one supply, an ICL7660 (U4) is used to generate the -5 V. Internally, an onboard oscillator controls the on time of four MOS switches.

The first half of the cycle is used to charge C7 to Vc,. During the next half, the positive side of C7 is tied to ground and the negative, to pin 5. The charge is transferred in the opposite polarity. U4 can deliver 100 mA without significant change in the output voltage.

First, we integrate the current, creating a sawtooth waveform (U3a). The frequency of the signal is dependent on the amount of current flowing through pin 11. With an input of 0, essentially no current flows through  $I_{\rm OUT1}.$  Thus, the frequency is 0. As the input value increases, the current also increases, varying the charge and discharge rate of C6.

The signal is passed to an opencollector comparator (U3b) to generate the square wave. Notice its output is tied to  $V_{REF}$ . With each cycle, the charge across C6 must be reversed. To do this, we drive U2/8 to +5 V and then to -5 V.

For example, assume the comparator's output just switched to +5 V. C6 was charged to +1.667 V during the previous half cycle. C6 discharges into I,,,, (electron flow) through the resistor ladder to  $V_{RFF}$ . U3b's output switches to -5 V when the voltage of C6 exceeds one-third of the positive supply. At this point, all of the available supply voltage is dropped across R5. When U3b/3 is driven below U3b/2, the output switches, reversing the direction C6 charges.

To find component values, use the following formula:

Listing 2-All that's required to send a value to the DAC is a couple of lines of code. WriteDac proc near mov dx, Port ;Assumes value is passed in AL dx, al out

WriteDac endp

| cal    | cogmont           |                             |                                       |

|--------|-------------------|-----------------------------|---------------------------------------|

| nai n  | segment<br>proc   | far                         |                                       |

|        | assume            | cs: cal                     |                                       |

|        | org               | 0100h                       |                                       |

| stort. | -                 |                             |                                       |

| start: | mov               | dx, Control Port            |                                       |

|        | xor               | ax,ax                       |                                       |

|        | out               | dx,al                       | ;setIREQ to off                       |

|        | cal l             | Clear-Screen                |                                       |

|        | mov               | dl,'1'                      | ;indicate <b>step 1</b>               |

|        | mov               | ah, Di spl ay               |                                       |

|        | i nt              | DOS                         | ;send 1 to display                    |

|        | mov               | ah, GetKey                  |                                       |

|        | int               | DOS                         | ;apply power then press return        |

|        | call              | Cleat-Screen                | indicate stan two                     |

|        | mov               | dl,'2'<br>ah Display        | ;indicate <b>step two</b>             |

|        | mov<br>int        | ah,Display<br><b>DOS</b>    | ;send <b>2 to the display</b>         |

|        | call              | ReadAD                      | , send 2 to the display               |

|        | call              | Cleat-Screen                |                                       |

|        | mov               | dl,'3'                      | ;indicate step three                  |

|        | mov               | ah, Di spl ay               | , marcare scop chiec                  |

|        | int               | DOS                         | ;send 3 to the display                |

|        | cal l             | LoopWriteDac                | · · · · · · · · · · · · · · · · · · · |

|        | call              | ClearScreen                 |                                       |

|        | mov               | dl,'4'                      | ;indicate <b>step four</b>            |

|        | mov               | ah, Di spl ay               |                                       |

|        | i nt              | DOS                         | ;send <b>4 to the display</b>         |

|        | mov               | dx,Port                     |                                       |

|        | mov               | al,Offh                     |                                       |

|        | out               | dx, al                      | ;send an ffh to DAC                   |

|        | mov               | ah, GetKey                  | raot a here                           |

|        | int               | DOS                         | ;get a key                            |

|        | call<br>int       | ClearScreen<br><b>Exit</b>  | :all done                             |

| mair   | endp              | LAIU                        | , att done                            |

| inci i | enup              |                             |                                       |

| ReadAD | proc              | near                        |                                       |

|        | mov<br>int        | an, Get Di spi ay<br>Screen | ;read <b>display mode</b>             |

|        | mov               |                             | sor;going to set cursor to start      |

|        | mov               | dh, l                       | ;line number                          |

|        | mov               | d1,0                        | ;column number                        |

|        | int               | Screen                      | ; bh has display page                 |

|        | call              | GetADValue                  | rets al with value                    |

|        | mov               | ah, al                      |                                       |

|        | mov               | сх,4                        | ;set up for rotates below             |

|        | ror               | ah, cl                      | ;high nybble to low                   |

|        | xchg              | al,ah                       | ;digits <b>right to display</b>       |

|        | push              | ax                          | ;save for second digit                |

|        | call              | ToAscii                     |                                       |

|        | mov               | dl,a]                       |                                       |

|        | mov               | ah,Display                  |                                       |

|        | • •               |                             |                                       |

|        | <b>int</b><br>pop | DOS<br>ax                   | ;char in dl to screen                 |

|                                  | int<br>cmp<br>jne<br>mov<br>int          | ah,CheckKey<br>DOS<br>al,KeyPressed<br>ReadAD<br>ah,GetKey<br>DOS | check for key<br>clear keybd                |             |

|----------------------------------|------------------------------------------|-------------------------------------------------------------------|---------------------------------------------|-------------|

| ReadAD                           | ret<br>endp                              | 200                                                               |                                             |             |

| LoopWri <sup>.</sup><br>WaitABit | inc<br>mov<br>out<br>mov                 | oc <b>near</b><br>al<br>dx,Port<br>dx,al<br>cx,08000h             | next value                                  |             |

| wai tabi (                       | loop<br>push<br>mov<br>int<br>cmp<br>pop | WaitABit<br>ax<br>ah, CheckKey<br>DOS<br>al, KeyPressed<br>ax     | wait so change can be seen<br>check for key |             |

|                                  | j ne<br>nlov<br>i nt                     | LoopWriteDac<br>ah,GetKey<br>DOS                                  | ;c]ear <b>keybd</b>                         | (continued) |

Frequency=  $\frac{\text{Digital Input}}{256 \text{ x } 15 \text{ k}\Omega \text{ (typical) x C6}}$

where  $R5 = 3 \times R4$ . For the circuit shown, the component values are:

Frequency max =  $\frac{255}{256 \times 15 \text{ k}\Omega \times 5 \text{ nF}} \approx 13 \text{ kHz}$

#### **BUILDING AND CALIBRATION**

Due to the simplicity and purpose of the circuitry, several ADC and DAC characteristics were not mentioned. All converters have a list of pitfalls. If your application requires increased accuracy, look into the converter's specifications before beginning.

When building the board, keep the converters' components as close as possible to the ICs. Keep the digital and analog grounds separated, except at the point of connection where they enter the board. To overlook the problems associated with driving cables, the board uses an onboard connector. If you use a cable, add the necessary components. To avoid the possibility of setting up a ground loop,

#### 8051 EMBEDDED CONTROLLERS

RIGEL Corporation builds and supports professional development tools for embedded controller systems, with hardware and software for industrial applications, and books and kits for educational and training purposes.

float the supply's ground (i.e., disconnect the jumper between the supply and earth ground).

The software in Listing 3 checks your setup and gives the step number and data.

- Step l-The port's interrupt request is disabled. Apply power. Verify U4/5 is approximately -5 V.

- Step 2-The ADC is read and the value displayed. Change the sensor's temperature to the lowest that will be encountered. Measure the voltage on pin 6. Adjust TempMin (pin 7) for the same value. Change the sensor's temperature to maximum. Again, measure the voltage on pin 6. Set the voltage on pin 9 to one-half that of pin 6. Verify the data displayed is FF hex. Put the sensor in minimum temperature. Ensure the displayed value is 0.

- Step 3—0–FF is written to the DAC in a continuous loop. Verify all data pins of the DAC are pulsing.

- Step 4—FF is sent to the DAC. Check that the sawtooth waveform and the pulse train are present.

#### **ON TO FUZZY LOGIC**

Now that the hardware is in place, there are several ways the control system could be generated without using fuzzy logic. One way might be to equate the temperature of the room with the different frequencies produced by the speaker.

That's not too hard. All we need to do is specify in absolute terms the difference between warm and cold. We'll say that the room is warm when the value read at the ADC is between

2.5 and 75. So, if the value is below 25, the room is considered cold.

But, is that correct? Does the room suddenly change from warm to cold at one specific temperature? What's needed is another set, which we can call KindaWarm. This set is defined as the span of inputs somewhere between Warm and Cold.

```

Listing 3-continued

ret

LoopWriteDac endp

ToAsci i

proc

near

and

al.Ofh

;only low nybble

add

a1.030h

al,03ah

:> 9

cmp

ToAsciiEnds

j]

add

al.07h

:get to A

ToAsci i Ends:

ret

ToAscii endp

ClearScreen proc near

ah, GetDi spl ay

mov

:get display mode

i nt

Screen

ah.Cls

mov

Screen

;clear screen

i nt

ret

Clear-Screen

endp

cal

ends

end

start

```

The difficulty of the task quickly escalates into a full-blown project. What's needed is a way to tell a computer that Warm, KindaWarm, and Cold are not separate entities, but a combination of all three.

Let's see how fuzzy does it.

#### START AT THE BEGINNING

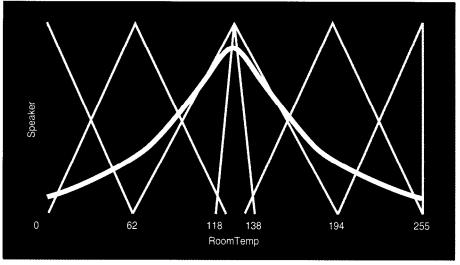

The first thing to do is to decide what the input versus the output graph should look like. You could specify that as the room temperature increases, the frequency of the speaker also increases. In other words, the control system is the equivalent of reading the ADC and sending the value to the DAC, which is no fun at all. Instead, specify the frequency of the speaker as maximum when the room temperature is perfect and minimum at either extreme. You should further stipulate that the graph resembles a bell curve.

#### SET UP THE GRAPHS

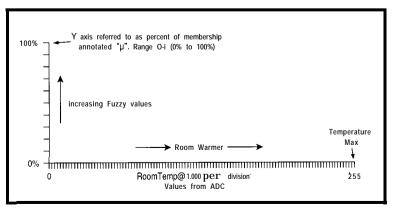

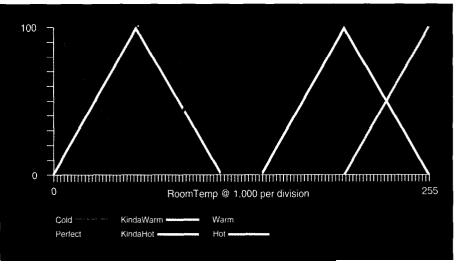

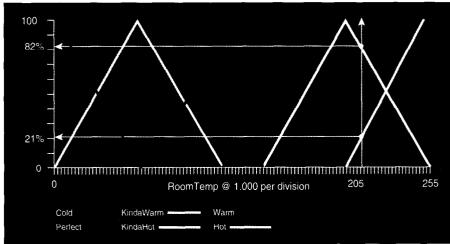

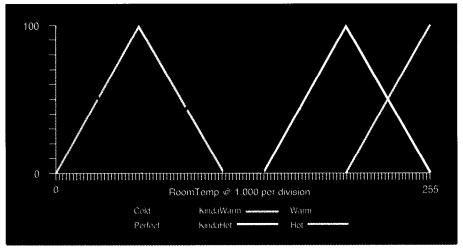

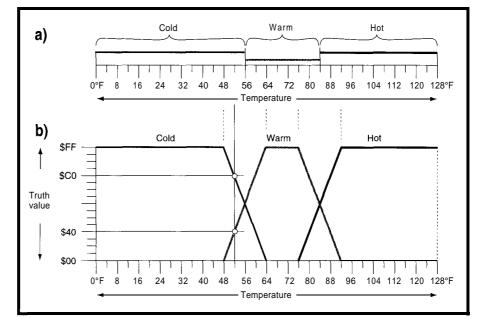

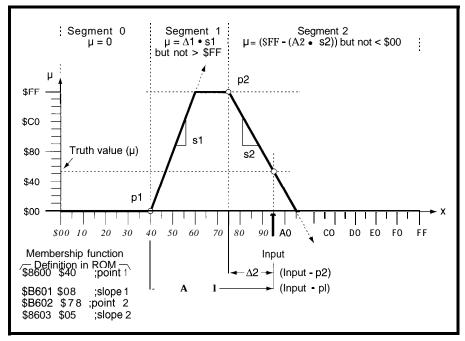

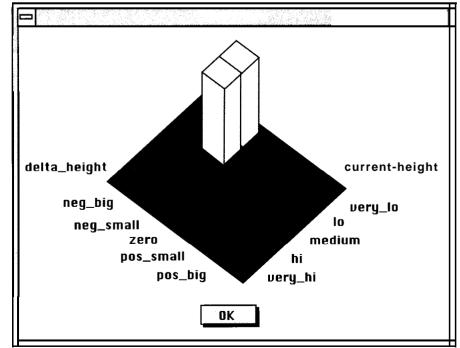

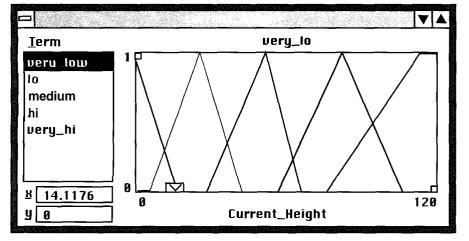

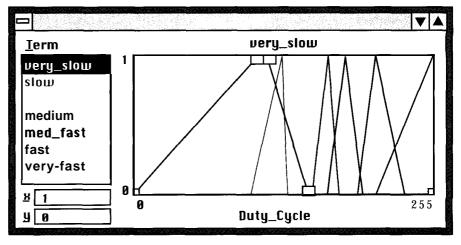

Both the input and output require a separate graph. Figure 5 shows the graph for the input. The values for the x-axis are the input values from the ADC. The values start at 0 (room coldest) and end at 255 (room warmest].

The y-axis is called the *degree of membership* (fuzzy value). Most documentation specifies its range as 0.0 to 1 .O and annotates it as  $\mu$ . Instead

of adding to the complexity of this, I'll refer to this axis as the *percentage of membership.*

The range starts at 0 (i.e., no membership) and ends at 100% (complete membership). If we were using Boolean logic, there would only be two values on this axis: 0 (false) and 100 (true). Fuzzy logic includes

Figure 5—After deciding what output shape is needed, input and output graphs are set up. The values on the y-axis are fuzzy values. The x-axis inputs from the ADC.

Boolean values as well as all the other values in between the Boolean poles. One could view Boolean as a pulse train (True or False) and fuzzy as a sine wave with varying degrees of truth.

#### ADD THE SHAPES

Shapes replace all the drudgery of defining and redefining values. The values contained in each set are still defined, but they conform to a shape rather than matching specific numbers, Each shape defines what values are contained in the fuzzy set and the weight (i.e., percentage of membership) of each.

As an analogy, say you're in a boat and the dock is one mile away. The input shape (set) contains the distance between you and the dock. The output shape equals the range of the gas lever. When the dock is a mile away, the distance has little membership in the input set, so the lever remains unchanged. The closer you get to the dock, however, the higher the dock's membership within the shape. This membership is transferred to the output's shape, thereby decreasing the lever's position.

The shapes available are trapezoids and triangles. And, it is not readily apparent how to achieve a bell curve using these shapes. However, when rules are added, any output shape can be represented.

To select input shapes, first establish what values belong in each set. This defines the base of the shape.

Figure I-Trapezoids, triangles, and rectangles are used to define which ADC values are contained in each set and to what degree (i.e., the percentage of membership) each belongs.

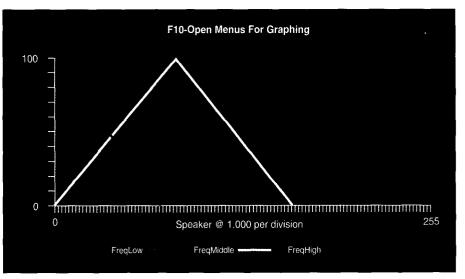

Figure 7—Three shapes on the output graph generate the be// curve. FreqLow controls fhe leading and falling edges, FreqMiddle, the transition to the peak, and FreqHigh, the peak.

The left bottom is the minimum and the right, the maximum. Next, you

Figure 8-The input from the ADC is converted to a fuzzy value by first drawing a vertical line from the x-axis Horizontal lines to the y-axis determine fhe value.

need to decide when the fuzzy set becomes 100% true.

For example, refer to the Warm shape in Figure 6. Here, the room is completely warm (i.e., membership = 100%) at only one point, the shape's peak. If necessary, we could replace the triangle with a trapezoid, allowing the set to be completely true for more than one input or, for that matter, it could be true for all inputs as in rectangles. Now that the points are defined, all that's left is to connect the dots.

Unlike criteria in an absolute system, fuzzy logic lets you overlap shapes anytime values belong to more than one set. When the input value for the RoomTemp graph (Figure 6) is within the KindaWarm shape three

components-Cold, KindaWarm, and Warm-interact. KindaWarm is *not* a singular set of values, but a varying degree of three.

Output shapes are a little different. Instead of working directly with the edges, centroids are used. To use an analogy again, you could consider this the center of gravity or the fulcrum on which the pivot balances. Each centroid has an x and y coordinate of which only the x value is actually used.

Shape selection is easier than inputs. You start out by finding the number of shapes required, a decision dictated by the number of dissimilar areas you're attempting to control. In this system, there are three areas and thus three shapes. FreqLow (Figure 7) controls the leading and falling edges, FreqMiddle depicts the area between FreqLow and the peak, and FreqHigh represents the peak.

Next, you determine what the output should do as fuzzy values vary. For example, the FreqLow shape is drawn so that as fuzzy values decrease, the output increases. FreqHigh is the opposite—decreasing the fuzzy values decreases the output. An equilateral triangle is used for FreqMiddle, so the output for all fuzzy values is the same, thereby creating a line. You should position the shape by visualizing the centroid with a fuzzy value of 100%. You then place it on the graph so the point is at the desired output if it were the only shape used.

With output shapes, you should always remember:

- overlapping shapes has no effect. As long as the centroid is in the same place, the base of the FreqMiddle shape can be reduced without affecting the output shape.

- unlike inputs, gaps between shapes have no effect.

- as long as their bases are identical, a centroid's x coordinate is the same for equilateral triangles, trapezoids with equal slopes, and rectangles, and it is always in the middle of the shape.

- when using trapezoids, the length of the top determines how close each centroid is to the previous. With a

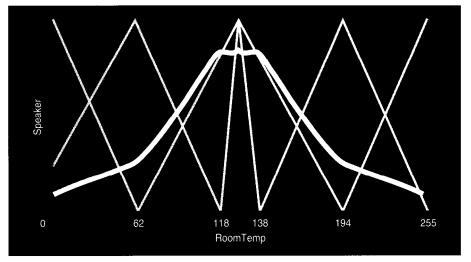

Figure 9-Very seldom is the output-versus-input graph correct the first time. Three transitions need to be corrected: 62, 118-138, and 194.

Figure 10—After finding the fuzzy values, fhey are processed by the rules and transferred to the output graph. Cenfroids are used to find the X-axis values.

Figure 1 1—Small modifications to the Kinda Warm and KindaHot shapes are all that's required to smooth the transition at the top of the bel/ curve.

longer top, there is less change in the x coordinate of the centroids.

• of all the components, output shapes have the least affect.

#### INPUT TO FUZZY VALUE

Figure 8 shows the completed graph for RoomTemp. To see how the fuzzy value for a given input is derived, I use a sample input value of 205.

I first draw a vertical line from 205 to the top of the graph. This line intersects two shapes. Thus, the value has membership in both of the fuzzy sets Hot and KindaHot. To find the fuzzy value, I draw a horizontal line from the point of intersection to the vaxis. This tells me that 205 has an 82% membership in the KindaHot set and 21% membership in the Hot set.

Once I have the fuzzy value, I can apply it to the output. Before doing that, I need to specify how the conversion takes place.

#### FORMULATING RULES

Rules define the relationship between input and output shapes. They are formulated much like the BASIC statement IF...THEN with a few modifications. Valid operators are AND (intersection], OR (union), and NOT (complement).

As stated, rules tell the system how the inputs and outputs are linked together. For instance, take the propeller of a boat. If there's no propeller (rules], the motor (input) can run all day, but we ain't goin' nowhere (output). If we install a small propeller, the rule becomes: IF motor = fast THEN output = slow. However, with a larger propeller, the rule becomes: IF motor = slow THEN output = fast.

Fuzzy rules differ from their conventional counterparts. Instead of a rule evaluating to one of two values, which are true or false, they can have varying degrees of each. For example, the statement, IF p AND q THEN  $r_{r}$ evaluates to true (the rule fires) as long as both *p* and *q* have values greater than 0. Each rule specifies what input conditions must be met for the rule to evaluate to true, and once it's true, which output shapes to use.

Once the operators are understood, rule development is straightforward. Write the rules as if you're explaining how the system works. Visualize the input graph superimposed over the final output graph (Figure 9), and for each input shape, define what the output should do when the input is within the set.

## PIC16C5x/16Cxx Real-time Emulators

Introducing RICE16 and RICExx-Juniors, real-time in-circuit emulators for the PIC16C5x and PIC16Cxx family microcontrollers: affordable. feature-filled development systems from \* Suggested Retail for U.S. only

**RICE16** Features:

- Real-time Emulation to 20MHz for 16C5x and 10MHz for 16Cxx

- PC-Hosted via Parallel Port

- Support all oscillator type5

- 8K Program Memory

- 8K by 24-bit real-time Trace Buffer

- Source Level Debugging

- Unlimited Breakpoints

- External Trigger Break with either "AND/OR" with Breakpointe

- Trigger Outputs on any Address Range

- 12 External Logic Probes

- User-Selectable Internal Clock from 40 frequencies or External Clock

- Single Step, Multiple Step, To Cursor, Step over Call, Return to Caller, etc.

- On-line Assembler for patch instruction = 30-day Money Back Guarantee

- Easy-to-use windowed software

### **RICE-xx** Junior series

RICE-xx "Junior" series emulators support PIC16C5x family, PIC16C71, PIC16C84 or PICI6C64. They offer the same real-time features of RICE16 with the respective probe cards less real-time trace capture. Price starts at \$599.

### PIC Gang Programmers

Advanced Transdata Corp. also offers PRODUCTION QUALITY gang programmers for the different PIC microcontrollers.

Stand-alone COPY mode from a master device PC-hosted mode for single unit programming • High throughput • Checksum verification on master device ■ Code protection ■Verify at 4.5V and 5.5V ■ Each program cycle includes blank check, program and verify eight devices Price5 start at \$599

PGM16G; for 16C5x family

PGM47: for 16C71/84

PGM17G: for 17C42

Call (214) 980-2960 today for our new catalog.

For RICE16.ZIP and other product demos, call our BBS at (214) 980-0067.

Advanced **Transdata** Corporation Tel (214) 980-2960 14330 Midway Road, Suite 1'28. Dallas, Texas 75244 Fax (214) 980-2937

25

Emulators for 16C71/84/64 available now!

- Support 16C71, 16C84 and 16C64 with **Optional Probe Cards**

- Comes Complete with TASM16 Macro Assembler, Emulation Software, Power Adapter, Parallel Adapter Cable and User's Guide

- Made in the U.S.A.

Figure 1 2—After a couple of simple modifications to the rules and shapes, the output is much closer, buf still unsatisfactory. A little more work on the raising and falling edges, and we'll achieve our goal.

For example, rule B in Table 2a declares that if the input falls in either the Cold or Hot shape, the frequency is set low. This rule controls the outside edges of the bell curve.

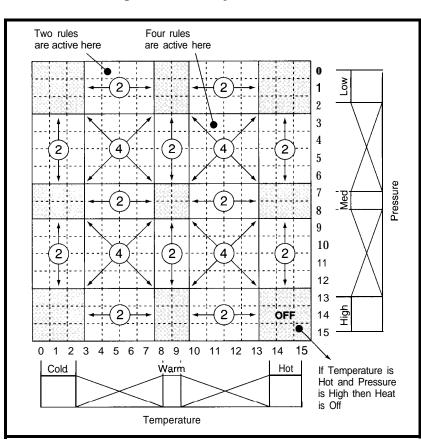

How many rules are required? It depends on the number of inputs. This system has one input with six shapes. To cover all possible input conditions, a minimum of six rules is required. If the system had two inputs, each with eight shapes, then you need 8 x 8 or 64 rules to cover all input combinations.

In addition, you might add rules to optimize the output shape. For example, this system uses ten rules instead of the minimum of six (the OR operator is used as a connector). As you can imagine, there's a point when the number becomes unmanageable. Typically, for systems with more than one input, not all combinations are possible. Thus, not all rules are required. Also, the number of shapes can often be reduced without compromising the output.

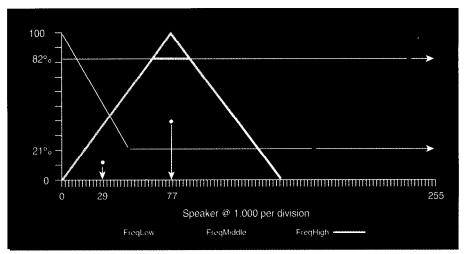

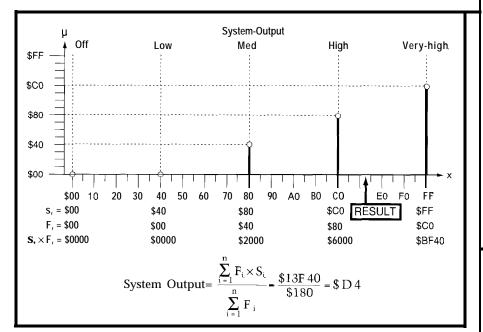

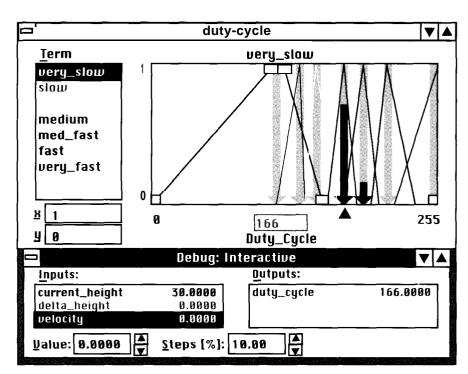

#### TRANSLATING FUZZY VALUES TO USABLE OUTPUTS

Now that we have the rules (recall Table 2a), let's figure out which rules are acted on. As stated, an input of 205 has membership in both KindaHot and Hot. Both rules B and C use the shapes and the OR operator, so they evaluate to true even though there is no value for Cold or KindaWarm.

Next, we have to apply the fuzzy values to the output. In fuzzy terms,

this is considered defuzzifying. To take the values from input to final output, we read the crisp input, make it fuzzy by determining its membership percentage, apply rules, defuzzify, and finally convert to a crisp output.

With an input of 205, the percentage membership for rule B is Hot at 2 1%. This value needs to be defuzzified and applied to the output. Notably, the process is more complex than converting to fuzzy values.

Refer to Figure 10. Draw a horizontal line from the 2 *1%* mark on the y-axis. The shape is specified in the rule as FreqLow. That's how the percentage membership is transferred. The fuzzy value defines the top of the area (dark outline) that's used to calculate the centroid. After finding the centroid, draw a vertical line to the x-axis. This value of 29 is the output for rule B.

If this were the only rule that fired, the speaker's frequency would be close to minimum, which is not exactly what we want. With an input of 205, the room is hot but has not reached maximum. This is where fuzzy starts to work.

Due to the overlapping of the Hot and KindaHot shapes, rule C also fires, increasing the speaker's frequency. Any time more than one rule fires, the final output is modified according to the weight of each that fires. This modification corresponds to driving a car with pressure on both the brake and the gas. The final output (i.e., the speed of the car) is dependent on the amount of pressure applied to each.

Before finding the crisp output, it is necessary to calculate the centroid for the second rule (C). Once again, start with transferring the 82% membership to the FreqMiddle shape (the shape is an equilateral triangle, so the centroid is in the middle of the base regardless of what the fuzzy value is). If you refer again to Figure 10, you can see that the centroid is 77. No other rules fired. The final output is calculated by:

```

CrispOutput = \frac{Crisp 1 \times Weight 1 + Crisp2 \times Weight 2}{Weight 1 + Weight 2}= \frac{29 \times 0.21 + 77 \times 0.82}{0.21 + 0.82}= 67

```

The final output is sent to the DAC.

Figure 13—The AND operator is used to zero in on specific areas where shapes overlap. The system is complete. Although if took several tries, it's much easier than modifying code or manipulating equations.

- a) A-IF (RoomTemp Perfect) THEN (Speaker FreqHigh)

B-IF (RoomTemp Hot) OR (RoomTemp Cold) THEN (Speaker FreqLow)

C-IF (RoomTemp KindaWarm) OR (RoomTemp KindaHot)

THEN (Speaker FreqMiddle)

D-IF (RoomTemp Warm) THEN (Speaker FreqHigh)

- b) E-IF (RoomTemp Hot) OR (RoomTemp Cold) THEN (Speaker FreqLow)

F-IF (RoomTemp KindaHot) AND (RoomTemp Hot) OR (RoomTemp KindaWarm) AND (RoomTemp Cold) THEN (Speaker FreqLow)

Table z-a) Hules define the relationship between input and output graphs and are formulated much like the BASIC IF.. THEN statement. b) Additional rules are often required to optimize the input versus output shape.

Notice the fuzzy value is used first in the calculation of the centroid and then again to find the final output. There are a few reasons for this. First, whatever the type of shape, centroids move very little. Using the value to define the usable area allows fine adjustments to be made on the final output shape.

Next, it must be used in the final calculation so that the relative truth of each rule is considered. For example, the weights [relative truth) of rules B and C are 21% and 82%, respectively. If we want rule C to affect the output more than rule B, we first see how true

the rule is relative to itself and then how true it is relative to total truth. And, that's the basis of fuzzy logic. It doesn't deal with absolute truth, but relative truth.

Still fuzzy? Let's try it another way. Break the equation into two parts and use the first:

| Crisp | 1 | x | Truth | 1 |

|-------|---|---|-------|---|

| Truth | 1 | + | Truth | 2 |

Essentially, this relates the output for the rule to its truth and puts that in relation to total truth.

Why is total truth used? Because up front, there's no way to know what

completely true is. In the equation above, 103% (i.e., 21% + 82%) represents complete truth and not 100%. If ten rules fire, each with the weight of 100%, complete truth becomes 1000. In essence, regardless of what the value for total truth is, it equals 100% true.

#### MAKING IT WORK

The output versus the input graph for the system is shown in Figure 9. Unfortunately, as you can see, I didn't

| RoomTemp               | Rules Fired |  |

|------------------------|-------------|--|

| IN = 0                 | B,E         |  |

| 0 < IN < 62            | B,C,E,F     |  |

| IN = 62<br>62 < IN 118 | C<br>C,D    |  |

| 118 < IN < 124         | A,C,D       |  |

| 124 IN 132             | Á,D         |  |

| 132 > IN < 138         | A,C,D       |  |

| 138 IN<194<br>IN = 194 | C,D<br>C    |  |

| 194 < IN < 255         | B,C,E,F     |  |

| IN = 255               | B,E         |  |

Table 3—Multiple rules can evaluate to true (fire) for the same value. This prevents the absolutes common in conventional logic.

28 Issue #56 March 1995 Circuit Cellar INK

problems: the top shouldn't be flat, nor should the corners be abrupt. I need to modify the system to achieve the desired output. Let's break the problem into three parts: the areas in the ranges of O-62, 118-138, and 194-255.

meet the objective. There are two

In the first area, the Cold shape begins at 0 and ends at 62. We need to add another rule that "pulls" the output toward 0 when the input is within this shape. Also, notice that the Hot shape controls the same portion, but on the opposite end. Both ends get fixed with this one rule.

The final output can be derived by two methods: the max method and the average. Using the max method, only one centroid per output shape is used in the final calculation. The average averages all centroids.

For example, to fix the problem with the abrupt corners, you can specify rule B twice. With an input of 205, three centroids would be produced: one for rule C and two for B. Using the max method, the final crisp output becomes:

68HC08

68HC16

6809

68HC

7

-----0

Ô

5\_0

5

Ň

-----10

A

-0

utilities

SPECIAL!!

6801/6803, and 6502.

C COMPILERS

DEBUGGERS

8051/52

8080/8085

8086/1 86

8096/1 96

7

-0-

(

5-0

Å

- 10

Ä

7

Ĩ

#113

**CROSS ASSEMBLERS**

Low Cost!! PC based cross development packages which include EVERYTHING you need to develop C and assembly

Hand coded (efficient ASM) standard library (source included).

\* 68HC08 and 68HC16 kits do not include monitor/debugger.

Super Developer's Kit

(Ask for SDK Special)

Reg. \$400.00 NOW \$300.00

Dunfield Development Systems P.O. Box 31044 Nepean, Ont. K2B8S8

CANADA

Tel/BBS: 613-256-5820 Fax: 613-256-5821

~~~ h ~~ h

7L 🖁

Includes all 8 kits above, plus additional assemblers for 6800,

Includes text editor, telecomm software and many other

· MICRO-C compiler, optimizer, and related utilities.

Resident monitor/debugger ( source included)\*

Each Kit: \$99.95. + s&h (please specify CPU)

language software for your choice of CPU.

Cross Assembler and related utilities

| $Centroid C \times Fuzzy C + Largest Centroid B \times Fuzzy B$ |

|-----------------------------------------------------------------|

| Fuzzy C + Fuzzy B                                               |

Using the average method, the final crisp output becomes:

#### CentroidC× Fuzzy C + 2 × CentroidB× Fuzzy B Fuzzy C + 2 $\times$ Fuzzy B

At first glance, it may appear that specifying a rule twice doubles its effect. Unfortunately, it's not that easy. Due to the interaction between all centroid and fuzzy pairs (it's that relative truth thing), it may fix the problem, create another, or have no effect. It works here, so we use it.

How should the area between 118 and 138 be adjusted? Should we modify the rules or the shapes?

To be honest, it's a toss up. It's kinda like your toast. If you toast some bread and it's too light, you have to decide how to make it darker. You could toast it again (input), change the toaster's setting (rules), or manually hold the lever down (output). All of these activities achieve the same thing.

However, since modifying shapes is the easiest, let's start there. If you superimpose the input graph over the output, the area in question falls within the perfect shape. In fact, the top goes flat as soon as the shape comes into existence.

When the input is within this shape, two rules (A and D) fire. There's our problem. Both rules tell the system to increase the frequency. To fix it, vou need to add interaction, holding the output low longer. Since rule C uses the FreqMiddle shape, it could provide the fuzziness needed if we make it fire. After modifying both the KindaWarm and KindaHot shapes as shown in Figure 11, the problem is solved. At the points of overlap, the rules "fight" each other, smoothing the transition.

The modified output is shown in Figure 12. Although it's better, it still isn't right. The transition with an input of 62 is still too abrupt. To smooth it further, add another rule that fires only when input is within the area where the Cold and Kinda-

Ĩ┈╽┈╽┈╽┈╽┈╽┈╽┈╽ 8051 80C32 2**........................** Ô -----0 Ň

87C751

87C752

Use one of our embedded controllers to save time and money. They are ideal for developing products, test fixtures and prototypes.

We offer a complete line of controller boards and software tools for the 8051 and 87C751 families of microcontrollers. Complete packages are availab le to help you develop your projects.

#### Features:

- Breadboard area

- Flexible I/O arrangement

- Powerful controller BASIC for the 87C752 or 80C32

Ph: (702) 83 1-6302 Fax: (702) 831-4629

lota Systems, Inc. POB 8987 • Incline Village, NV 89452-8987

IF (RoomTemp Cold) AND (RoomTemp KindaWarm) THEN (Speaker FreqLow)

The AND operator allows us to zero in on specific areas of shape overlap. At any other time, one or more of the fuzzy values is 0, preventing the rule from firing.

The same problem exists on the falling edge of the output. Instead of writing a separate rule, we can combine both using the OR operator as shown in Table 2b, rule F.

The final output is shown in Figure 13. Table 3 shows which rules fire as the input varies. Although it took several tries to get the optimum shape and rule mix, it's much easier than modifying code or manipulating equations.

#### SOME USES

The applications are endless. Some of them include:

- robotics

- home and office burglar alarm and climate control

- AC/DC motor control

- weather prediction through humidity, temperature, pressure, and so on

- analyzing data for patterns and trends.

- controlling product flow in production (anything requiring control or generalization is a possible application)

#### WHERE TO GO FROM HERE

I hope this gives you a basic understanding of fuzzy logic. The next step is to apply the principles outlined in the article to your own designs. All you need is a lot of time, a ream or two of graph paper, and a calculator. If that is not appealing, there is a better way.

I have development systems for both the novice and advanced user. Please call or write for details.  $\Box$

Bud Moss has worked in the electronic and electrical fields for more years than he cares to remember. After researching and using several unconventional technologies, he founded Xcentrics to provide affordable fuzzy logic development tools. He may be reached at 75313.2353@compuserve.com.

#### SOFTWARE

Software for this article is available from the Circuit Cellar BBS and on Software On Disk for this issue. Please see the end of "ConnecTime" in this issue for downloading and ordering information.

#### SOURCE

Xcentrics, Inc. P.O. Box 1268 McMinnville, OR 97 128 (503) 434-5729

#### IRS

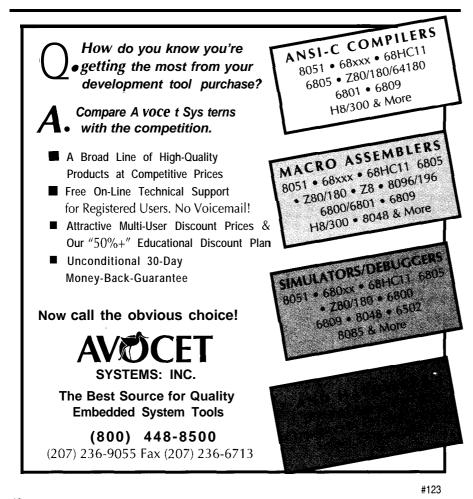

401 Very Useful 402 Moderately Useful 403 Not Useful