# E COMPUTER APPLICATIONS JOURNAL

## THE COMPUTER APPLICATIONS JOURNAL #60 JULY 1995 GRAPHICS & VIDEO

Using Color in Scientific Visualization

**Digital Video Resizing**

**MIPS for the Masses**

Transient Circuit Protection Explored

## EDITOR'S INK

### Habitech95

magine walking onto a show floor and finding over 80 exhibitors showing their home automation wares. Turn around, walk down the hall, and you find dozens of home automation classes and seminars dealing with topics such as equipment selection, installation, customer service, and marketing. Such was the recent scene in Atlanta, the site of Habitech95.

Habitech is the home automation industry's only trade show. It hosts virtually every key player in the HA arena and is Mecca to HA dealers, installers, enthusiasts, and those just thinking of getting their feet wet. It's also the place to size up the state of the **industry** and see what's new.

The majority of exhibitors displayed independent subsystems that control a specific aspect of the home. Lighting systems, drapery controllers, audio/video distribution, HVAC controllers, security systems, and even central vacuum setups were represented. However, as Greyson Evans points out in his article in the HABC insert, for the **industry** to truly grow, we need a unified method of communication between these subsystems to enable them to interoperate.

There are a number of contenders wanting to facilitate that communication, and the question in everyone's mind continues to be, "Will it be X-10, CEBus, or **LonWorks?**"

X-10 continues to hold the lead in terms of price. There were even new X-10 products that address some of the shortcomings people have complained about for years. Powerline Control Systems (PCS) has a number of X-10 offerings that gradually brighten from off (rather than going to full on first, then dim), preset dim, and microdimming. While pricey, I think they'll be popular among X-10 diehards. They are also shipping now.

As for CEBus versus **LonWorks**, the juty is still out. Both camps had pavilions showing products with support for each built in. Greyfox presented a CEBus box that provides Node 0 functionality for coax and twisted pair in addition to routing services between power line, coax, twisted pair, and RF. Such a box serves as the core of any complete CEBus installation. I hadn't expected to see one produced for at least another year or two.

I certainly don't have room here to get into all of what was shown, but there is a Web page that offers extensive home automation information, including how to contact the companies I've mentioned here. Point your browser at http://www.hometeam.com/ and be prepared to spend some time reading. It's good stuff.

Next year's show cohabits with CES Orlando: The Digital Destination and takes place May 23-25. Mark your calendar now.

Ken

# CIRCUIT CELLAR® THE COMPUTER APPLICATIONS JOURNAL

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

EDITOR-IN-CHIEF Ken Davidson

TECHNICAL EDITOR Janice Marinelli

ENGINEERING STAFF Jeff Bachiochi & Ed Nisley

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITOR John Dybowski

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR Lisa Ferry

PRODUCTION STAFF John Gorsky James Soussounis

CONTRIBUTORS: Jon Elson Tim McDonough Frank Kuechmann Pellervo Kaskinen PUBLISHER Daniel Rodrigues

PUBLISHER'S ASSISTANT Sue Hodge

CIRCULATION MANAGER Rose Mansella

CIRCULATION ASSISTANT Barbara Maieski

CIRCULATION CONSULTANT Gregory Spitzfaden

> BUSINESS MANAGER Jeannette Walters

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK, THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0696-6965) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (203) 675.2751. Second class postage paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate U.S A and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. All subscription orders payable in U.S. funds only, via international postal money order of check drawn on US. bank. Direct subscription orders and subscription, related questions to Circuit Cellar INK Subscriptions, P.O. Box 696, Holmes, PA 19043.9613 or call (600) 269-6301.

POSTMASTER: Please send address changes to Circuit Cellar INK, Circulation Dept., P 0 Box 698, Holmes, PA 19043.9613.

Cover photography by Barbara Swenson PRINTED IN THE UNITED STATES

SOUTHEAST

Christa Collins

#### HAJAR ASSOCIATES NATIONAL ADVERTISING REPRESENTATIVES

NORTHEAST & MID-ATLANTIC Barbara Best (908) 741-7744

Fax: (908) 741-6823

(**305) 966-3939** Fax: (305) 985-8457 MIDWEST Nanette, Traetow WEST COAST Barbara Jones & Shelley Rainey (714) 540-3554 Fax: (714) 540-7103

Nanette Traetow (708) 357-0010 Fax: **(708)** 357-0452

Circuit Cellar BBS—24 Hrs. 300/1200/2400/9600/14.4k bps, 8bits, no parity, 1 stop bit, (203)871-1988; 2400/ 9600 bps Courier HST. (203) 671.0549

All programs and schematics if *Circuit Cellar INK* have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in *Circuit* Cellar INK

Entire contents copyright © 1995 by Circuit Cellar Incorporated. All rights reserved Reproduction of this publication," whole or " part without written consent from Circuit Cellar Inc. is prohibited.

|               | Use of Color in Scientific Visualization<br>Mike Bailey                                                                |     |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|

|               | ual Reality Position Tracking<br>Herschell Murry & Mark Schneider                                                      |     |

|               | ital Video Resizing and Compression                                                                                    |     |

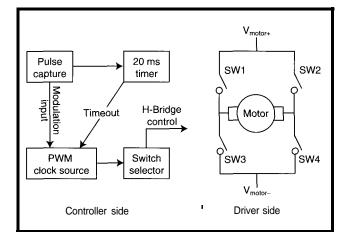

|               | IC-based Motor Speed Controller<br>Chuck McManis                                                                       |     |

|               | R BONUS SECTION: <i>HOME AUTOMATION &amp; BUILDING CONTROL</i><br>GINS ON PAGE 47                                      |     |

|               | <b>Firmware Furnace</b><br>journey to the Protected Land: The Mystery of Scan Code Set 3<br><i>Ed Nisley</i>           |     |

|               | <b>From the Bench</b><br>Sacrifice for the Good of the Circuit<br>Strengthening the Weak Link<br><i>Jeff Bachiochi</i> |     |

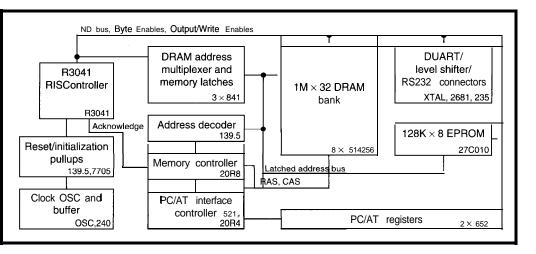

| <b></b>       | Silicon Update<br>MIPS for the Masses<br>Tom Can trell                                                                 |     |

|               | <b>Embedded Techniques</b><br>Circuit Protection<br>John <b>Dybowski</b>                                               |     |

|               | <b>ConnecTime</b><br>Excerpts from                                                                                     | 100 |

| itor          | the Circuit Cellar BBS<br>conducted<br>by Ken Davidson                                                                 |     |

| ews<br>/einer | Your Computerized                                                                                                      | 112 |

4

4

0

6

2

6

1

2

3

3

8

8

g

2

6

8

Editor's INK Ken Davidson Habitech95

Reader's INK Letters to the Editor

New Product News edited by Harv Weiner

> 81 Advertiser's Index

# **READER'S INK**

#### **PNEUMONICS HELP MEMORY?**

I think you folks need to take better care of Steve. All that overdosing on Papa Gino's pizza has affected his vocabulary.

Steve said he was writing pneumonics. My dictionary defines "pneumonic" as an adjective which refers to the pulmonary system or affected with pneumonia.

It seems Steve could use a mnemonic, as in ni-**mon**ik, to keep his lungs clear. I hope so! Somewhat later he did write that he was "rationalizing these few pneumonics." Did that help him feel better? I sure hope so, because you produce a great magazine!

Joe Craig Ellicott City, MD

While Steve readily admits that his spelling is about as good as any other engineer, this is certainly one we should have caught on the very first reading. His favorite programming language may be solder, but he really does know what a mnemonic is. Honest.-Editor

#### **Contacting Circuit Cellar**

We at Circuit Cellar *INK* encourage communication between our readers and our staff, so have made every effort to make contacting us easy. We prefer electronic communications, but feel free to use any of the following:

Mail: Letters to the Editor may be sent to: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066.

Phone: Direct all subscription inquiries to (800) **269-6301**. Contact our editorial offices at (203) 875-2199.

Fax: All faxes may be sent to (203) 872-2204.

BBS: All of our editors and regular authors frequent the Circuit Cellar BBS and are available to answer questions. Call (203) 871-1988 with your modem (**300–14.4k** bps, **8N1**).

Internet: Electronic mail may also be sent to our editors and regular authors via the Internet. To determine a particular person's Internet address, use their name as it appears in the masthead or by-line, insert a period between their first and last names, and append "@circellar.com" to the end. For example, to send Internet E-mail to Jeff Bachiochi, address it to jeff.bachiochi@circellar.com. For more information, send E-mail to info@circellar.com.

#### BASIC LANGUAGE PROGRAMMABLE CONTROLLER

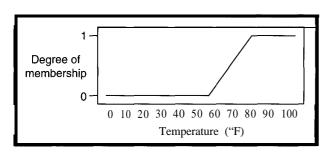

Sylva Energy Systems introduces a low-cost, full-featured BASIC-programmable controller board suited for data logging, home automation, and industrial-control applications. The **BAC552** controller uses a Philips 80C552 microcontroller with a 14.7-MHz clock and is packaged on a 9" x 6" fully socketed board. The controller is application ready with onboard I/O and screw-terminal plug-on connectors.

The controller provides ten 5-A relay outputs, three LED outputs, sixteen optoisolated DC inputs, eight 10-bit analog inputs (4-20 mA or high impedance), two 8-bit analog outputs (O-5 V), and an RS-232 or RS-485 communications port. As an option, the board may be ordered with an X-10 interface controller, which provides full two-way

power-line communications ability.

System expansion via the I<sup>2</sup>C bus offers up to 224 additional I/O points. An I<sup>2</sup>C operating system provides full master/slave communications between multiple BAC controllers interconnected with I<sup>2</sup>C bus extenders.

The user BASIC program resides in approximately 29.4 KB of SRAM, backed by a lithium battery and a MAX691. A 32-KB EPROM socket is available for permanent application program storage. A BASIC command generates an Intel hex file of the program in SRAM for EPROM programming. Full floating-point BASIC is expanded with statements supporting discrete-I/O-control-based applications. Interrupt sources include 8 of the **16** inputs, timer interrupt (1– 65,535 s) and a communications interrupt.

Enhanced embedded controller functions include a system watchdog timer, real-time clock/calendar module, power-loss-duration calculation, warm-or-cold-boot determination, auto-program load on powerup or reset, error trapping, and a queued **P R I NT** statement for improved BASIC execution speed.

The BAC552 controller sells for \$299.95 U.S. with a comprehensive user's manual and the X-10 controller option.

#### Sylva Energy Systems 519 Richard St. Thunder Bay, ON • Canada **P7A1R2** • (807) 683-6795 • Fax: (807) 683-6485

#500

#### IDE/PARALLEL PORT INTERFACE

Palmtech announces two new interface chips that connect IDE (hard disk) drives to 8-bit processors using a minimum of space while providing additional I/O and interrupts. Originally developed for a Z180powered single-board computer, the chips have a multitude of applications. The **PT IDE802/803** are single-chip IDE interfaces for 8-bit CPUs. The chips incorporate an additional 8bit unidirectional or bidirectional parallel port plus 10 **(11** for the IDE803) handshake or extra I/O lines suitable for a printer port. The chips also include a controller for three interrupts (two for the '803). The 8-to-16-bit data conversion is fully transparent with an IDE sector accessed as 512 8-bit bytes rather than 256 16-bit words. The PT IDE80x accepts any IDE drive conforming to the CAM ATA standard and does not require external buffering to the drive or printer. It can be coupled to most 8-bit CPUs with little or no extra glue logic. The chip is available in a 68-pin PLCC package, requires 100 mA at 5 V, and adds only 75 ns to the IDE drive access time. Also included on the

chip is a speaker or general-purpose output. The PT IDE80x sells for approximately \$41 in single quantities.

Palmtech

Moonah & Will St. Boulia, QLD 4829 Australia +6177 463-I 09 Fax: t6177 463-I 98

#501

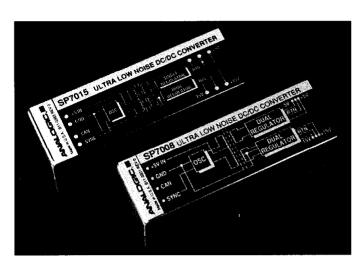

#### LOW-NOISE DC/DC CONVERTER

Analogic announces a family of state-of-theart exceptionally lownoise DC/DC converters designed specifically for high-performance dataacquisition applications. The family, models SP7005, SP7008, and SP7015, provides isolated ±15-V and +5-V analog supplies from a +5-V input and has excellent line-and-load regulation. In addition to data acquisition, these converters can be used in mixed signal circuits and in telecommunications.

This family of DC/DC converters features low noise and ripple of  $5 \cdot mV$  peak-to-peak under a full load with a line-and-load regulation of  $\pm 0.2\%$ . Models

SP7005 and SP7008 offer additional -6-V and -5-V supplies, respectively, and provide 6 W of power. Model SP7015 supplies up to 6.75 W of power. Each product is packaged in a 1" x 3" x 0.5" fully shielded module with input-to-output isolation of 10 M $\Omega$  and 500 VRMS. An optional sync input is available to blank switching during analogto-digital conversion. Models SP7005, SP7008, and SP7015 are priced at \$148.50 each in

Analogic Corp. 8 Centennial Dr. Peabody, MA 01960 (508) 977-3000 Ext. 2170 Fax: (617) 245-1274

100-piece quantities.

#502

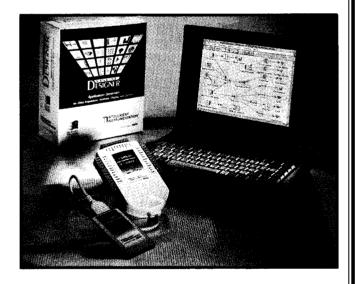

#### PORTABLE DATA ACQUISITION SYSTEM

**I/Ocard**, a portable data acquisition system for the PCMCIA bus, has been launched by Intelligent Instrumentation. Designed for notebook PCs, the system requires only 1 W of power, making it ideal for remote applications. I/Ocard connects to a PCMCIA type II slot and consists of a PC card and a termination pad.

The card features 8 differential analog inputs with 12-bit resolution, 30-kHz throughput, and external triggering. Gains and input ranges are software selectable. Both unipolar and bipolar input ranges are available.

Two models of I/Ocard are available. Model PCI-460P-1 provides gains of 1, 10, 100, and 1000 for extremely low-level signal measurement. PCI-460P-2 provides gains of 1, 2, 4, and 8. The system also features four TTL inputs, four TTL outputs, cold-junction

compensation for direct thermocouple connection, and a voltage-reference output for powering sensors

I/Ocard is fully supported by Visual Designer, Intelligent Instrumentation's Windows-based application-genera. tor software. Users can easily develop their own applications by drawing block diagrams (flowgrams) rather than coding the applications with a language such as C, Pascal, or BASIC. Sliders, switches, numeric inputs, and user prompts control the execution of the application. Displays include fully customizable plots, instrument panels, and control panels.

The I/Ocard portable data acquisition system sells for \$595. Additional termination pads art available for \$225.

Intelligent Instrumentation, Inc. 6550 S. Bay Colony Dr., MS130 • Tucson, AZ 85706 • (520) 573-3504 • Fax: (520) 573-0522

#503

#### DIGITAL VIDEO ENCODER

Philips introduces a digital MPEGcompatible video encoder. The **SAA7185** encodes digital YUV data to an NTSC or PAL CVBS and S-video analog signal to be displayed on a TV or recorded on a VCR. The SAA7185 is designed

for use in video-processing equipment such as computers, video servers, and video CD players. Because it accepts 16-bit YUV data or 8-bit CCIR 656-compatible YUV data in MPEG format, it is ideal for CD playback in PCS.

The SAA7 185 is a highly flexible and easily programmable 5-V CMOS device. It is controlled via an I<sup>2</sup>C serial interface or an 8-bit microprocessor port and can be synchronized as master or slave to external devices. The chip produces European PAL and either the U.S. or Japanese version of the NTSC signal. NTSC-M and PAL B/G standards and substandards are supported. The SAA 7185 also provides 8color onscreen display and provides closedcaption encoding. The chip contains cross-

color-reduction circuitry and IO-bit oversampled DACs to improve image quality.

The SAA7185, in 68-pin PLCC packages, sells for less than \$7 in volume.

Philips Semiconductors 811 E. Arques Ave. • Sunnyvale, CA 94088-3409 (408) 991-3737 • Fax: (708) 635-8493

#504

## A Serious Imaging Solution

"IMPACT Professional is a complete image analysis system that includes a broad range of crossdiscipline tools grouped into eight separate processing environments. These modules include

#### PLUG-AND-PLAY MICROCONTROLLER

Silicon Systems introduces the 73M2918, an 8052-compatible microcontroller with virtual 550 UART and built-in hardware which supports the emerging Plug-and-Play ISA standard. This highperformance microcontroller has all the attributes of an 8052 8bit microprocessor, including instruction cycle time, UART, timers, interrupts, 256 bytes of RAM, and programmable I/O. The 73M2918 also includes an HDLC

packet-generation unit

along with the registers and hardware required to facilitate Plug and Play. The

device features 32 pins of additional user programmable I/O. Programmable bank- and chip-select logic reduces the need for boardlevel glue logic. The unit has two buffered clock outputs to support peripheral devices such as UARTs and modems and two general-purpose input pins with programmable wakeup capability.

The device operates at a speed of 33 MHz at 5 V. An optional version, the **73M2918A**, operates at 44 MHz for high-speed applications. The device is offered in a small-form-factor 100-

lead QFP package. In quantities of 1000, the 73M2918 is priced at \$10.24 and the high-speed 73M2918A at \$14.92. Silicon Systems 14351 **Myford** Rd. Tustin, CA 92680 (714) 573-6200 Fax: (714) 573-6914

I'M OU

Don't bang your head and bust your development tool budget with inferior tools. Think smart and use **Paradigm LOCATE**. With today's compressed development cycles, you can't afford not to have the most powerful, full-featured locate utility speeding your '186 or V-series design to market.

Faster, more capable and supporting all Borland and Microsoft C/C++ compilers, only **Paradigm LOCATE** can jump the embedded system debugging chasm with access to **Paradigm DEBUG**.

Don't be caught flat-footed when you can be fast and nimble. Get Paradigm for all the tools and development support you need.

#### Paradigm Systems 3301 Country Club Road, Suite 2214, Endwell, NY 13760 (607) 748-5966 / FAX: (607) 748-5968 Internet: 73047.3031@ compuserve.com

CONTINUED.

©1995 Paradigm Systems, Inc. All rights reserved.

#### VIDEO/IMAGE DSP CHIPS

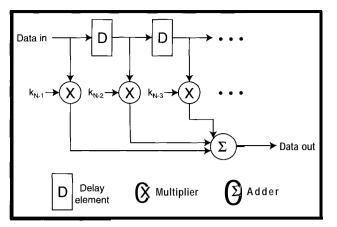

Genesis Microchip announces full-volume production of three video/image DSP chips: the gm865x1 and gm833x2 video/image resizing engines and the gm2242B half-band filter. The gm865x1 and gm833x2 provide a revolutionary break-

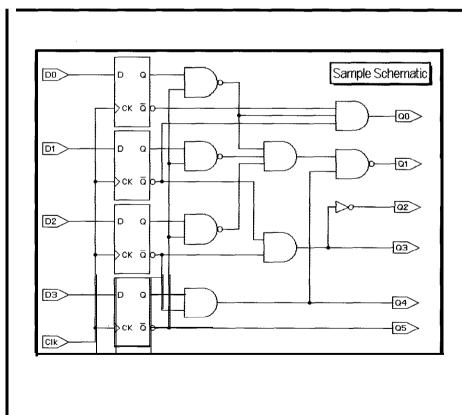

through in image-resizing technology and are part of the Acuity Resizing series of real-time, 2D filtering engines. Acuity Resizing devices produce the high-quality scaled images while minimizing the undesirable aliasing, artifacts, and distortion often created during digital-video scaling. Both chips use patented algorithms and architectures and implement advanced interpolation and finiteimpulse-response (FIR) filtering. In reduction mode, all memory required for FIR filtering is provided on-chip.

The gm865x1 offers up to 65-tap vertical and horizontal filtering independently in both directions. As a top-of-the-line part, it produces the highest quality resized images possible. Applications benefiting from the chip's performance include medical imaging, LCD projection systems, and high-end broadcast equipment which can take advantage of the chip's dynamic horizontal resizing for special effects.

For more cost-sensitive systems, the gm833x2 (an up to 33-tap device) is designed for many applications including videographic workstations, multimedia

systems, and projection and scan-conversion equipment. Both chips perform shrink-and-zoom operations.

The gm2242B half-band filter is fully compatible with the industry-standard TMC2242B part and offers more features at significantly less power and substantially less cost. Its unique features include a user-selectable sin x/x compensating filter and a handy pass-through mode. Constant data latency, available in all operating modes, is also available. Half-band filters double or halve digital-signal sampling rates and simplify ADC and DAC subsystem design. Applications ranging from broadcast and teleconferencing systems to digital compression and encoder equipment often use half-band filters.

Genesis Microchip, Inc. 200 Town Centre Blvd., Ste. 400 Markham, ON Canada L3R8G5 (905) 470-2742 • Fax: (905) 470-2447

#506

## STEPPER MOTOR CONTROLLER

The **ServoStep** from MicroKinetics controls the speed and direction of a stepper motor from any  $\pm 10$ -VDC signal source or from a single slide or rotary potentiometer. The step output is a frequency that is proportional to the magnitude of the input. The direction output is dependent on the polarity of the input signal. These signals run the stepper driver and motor. Onboard adjustments include maximum speed, acceleration, deceleration, and a zero deadband adjustment.

The outputs are open collector, making them directly compatible with industry-standard drivers. The power supply requirement is +12 VDC at 100 mA and -12 VDC at 50 mA. The ServoStep sells for \$199. MicroKinetics Corp. 1220-J Kennestone Cir. Marietta, GA 30066 (404) 422-7845 Fax: (404) 422-7854

#507

## **FEATURES**

14 The Use of Color in Scientific Visualization 24 Virtual Reality **Position Tracking** 30 Digital Video Resizing and Compression 36 Motor Speed Controller

A PIC-based

Getting color right is no easy task! After reviewing a little physiology, Mike looks at how we define colors in computers. Final tips ensure information does not get construed by color choice.

o some. a discussion of color in scientific visualization seems unnecessary. But, experience shows that some ways of using color communicate information more effectively than others. Used incorrectly, color detracts, providing less information than if it had not been used at all.

This article does not explain everything there is to know about color physics and human vision. Instead, after an overview of some these aspects, I go right to the qualitative issues of what color is and how it should be handled.

#### COLOR FREQUENCIES AND WAVELENGTHS

The electromagnetic spectrum is infinitely large. At the low frequency

**Mike Bailey**

# The Use of Color in Scientific Visualization

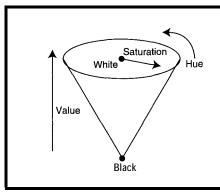

Figure 2—The Hue-Saturation-Value color cone is easier for humans to understand and work with.

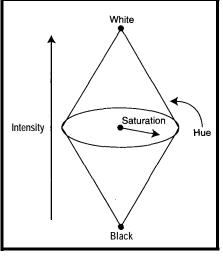

Figure 3-/n the Hue-Saturation-Intensity cone, color intensity is also accounted for.

end, it contains radio waves and microwaves. At the high end, it contains x-rays and gamma rays. Rather than speak of frequency, electromagnetic waves are usually discussed in terms of wavelength,  $\lambda$ , which is inversely proportional to the frequency, *f*:

$$\lambda = \frac{C}{f}$$

where c equals the speed of light (i.e.,  $3 \times 10^8$  m/s). Our eyes happen to be sensitive to the range of wavelengths within 380-780 nm. We see the long wavelengths around 780 nm as red and the short wavelengths around 380 nm as deep blue-purple.

#### THE EYE

The human eye is a marvelous input device, designed to meet a certain set of everyday demands. Like many parts of the human body, the eye is not a single component. Rather, it has several parts, each with its own area of specialization.

Rods are retinal sensors that detect grayscale and low levels of light. A typical human retina has approximately 115 million rods, mostly sensitive in the 500 nm (-green) range. Because there are so many, rods are much better at detecting high spatial frequencies than CORES.

Interestingly, rods are concen-

trated near the retina's periphery. Peripheral vision is therefore much more sensitive to small light changes than straight-on vision. As a result, some people detect CRT flicker only out of the corner of their eye. Straight-on, the flicker is no longer there.

Cones enable us to see color. Approximately 8 million cones concentrate near the center of the retina (the fovea), where their density is about 150,000 per square millimeter. Thus, color vision is far more sensitive to objects directly in front of us.

Cones are categorized by the wavelengths they are sensitive to. Low, medium, and high frequencies are viewed by L, M, and H cones, which achieve maximum sensitivity at 570, 550, and 440 nm, respectively. These wavelengths loosely correspond to the red, green, and blue portions of the spectrum.

It would be nice if the brain approximated red, green, and blue signals in a 24-bit (or more) frame buffer. Un-

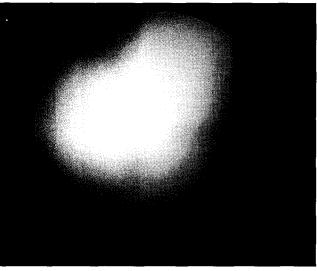

Photo I--Here's the fop circle of the Hue-Saturation-Value color cone.

fortunately, it is more complicated than that.

Three signals do go to the brain but as combinations of the L, M, and H cone signals. Specifically, they are:

If we permit ourselves the luxury of relating L, M, and H to R, G, and B (even though this is not exactly right), the three signals become:

| _ |                                                           |                                                           |                                                           |                                                    |                                                                  |  |

|---|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------|--|

|   | Black<br>White<br>Red<br>Green<br>Blue<br>Cyan<br>Magenta | <b>E</b><br>0.0<br>1.0<br>1.0<br>0.0<br>0.0<br>0.0<br>1.0 | <u>G</u><br>0.0<br>1.0<br>0.0<br>1.0<br>0.0<br>1.0<br>0.0 | <u>B</u><br>0.0<br>1.0<br>0.0<br>1.0<br>1.0<br>1.0 | <u>Y</u><br>0.00<br>1.00<br>0.30<br>0.59<br>0.11<br>0.70<br>0.41 |  |

|   | ,                                                         |                                                           |                                                           |                                                    |                                                                  |  |

|   | Orange                                                    | 1.0                                                       | 0.5                                                       | 0.0                                                | 0.60                                                             |  |

|   | Yellow                                                    | 1.0                                                       | 1.0                                                       | 0.0                                                | 0.89                                                             |  |

Table I-Using the luminance equation, it is relatively easy to defermine the luminances of standard colors.

|         | Black | Whit | e <u>Red</u> | Green I | Blue Cy | an Maa | <u>enta O</u> | r <u>anae N</u> | /ellow |

|---------|-------|------|--------------|---------|---------|--------|---------------|-----------------|--------|

| Black   | 0.00  | 1.00 | 0.30         | 0.59    | 0.11    | 0.70   | 0.41          | 0.60            | 0.89   |

| White   | 1 .00 | 0.00 | 0.70         | 0.41    | 0.89    | 0.30   | 0.59          | 0.41            | 0.11   |

| Red     | 0.30  | 0.70 | 0.00         | 0.29    | 0.19    | 0.40   | 0.11          | 0.30            | 0.59   |

| Green   | 0.59  | 0.41 | 0.29         | 0.00    | 0.48    | 0.11   | 0.18          | 0.01            | 0.30   |

| Blue    | 0.11  | 0.89 | 0.19         | 0.48    | 0.00    | 0.59   | 0.30          | 0.49            | 0.78   |

| Cyan    | 0.70  | 0.30 | 0.40         | 0.11    | 0.59    | 0.00   | 0.29          | 0.11            | 0.19   |

| Magenta | 0.41  | 0.59 | 0.11         | 0.18    | 0.30    | 0.29   | 0.00          | 0.19            | 0.48   |

| Orange  | 0.60  | 0.41 | 0.30         | 0.01    | 0.49    | 0.11   | 0.19          | 0.00            | 0.30   |

| Yellow  | 0.89  | 0.11 | 0.59         | 0.30    | 0.78    | 0.19   | 0.48          | 0.30            | 0.00   |

Table 2—Luminance differences offer a scientific measurement of contrast. The greater the luminance difference, the greater the contrast. A good contrast is 0.40 luminance difference.

red-green

blue-(red+green)

red+green

If yellow is substituted for red+green, the second signal becomes blue-yellow. Thus, the eye-brain system distinguishes chromaticity by the red/green and blue/yellow difference.

Knowing that blue only contributes about 11% to the overall appearance of brightness of a color, color scientists treat the third quantity red+green as lumi-

nance. So, the third signal becomes overall luminance.

The red-green signal is where most color deficiency occurs. For example, people with red/green color blindness do not correctly produce the red-green signal. Although blue, yellow, and overall luminance is understood, the person cannot determine if something is more red than green or vice versa.

#### DEFINING COLOR DIGITALLY

Too often, we ask computers for color in a way suitable to them: red, green, blue (RGB). Integers are fed to the digital-to-analog converters of the color guns.

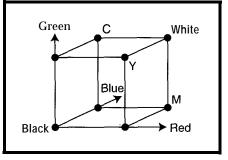

This method uses a rectilinear color space where red, green, and blue are the principal axes. Black is at the origin and white is at the other end of the major diagonal. As Figure 1 illustrates, the complementary colors of

Photo 2—Luminance differences shown in Table 2 fake on a clearer meaning when shown graphically.

cyan, magenta, and yellow are at the remaining corners.

Although this is convenient for

computers, humans don't think this way. It's easier to specify color with the Hue-Saturation-Value (HSV) system, an inverted cone shown in Figure 2. Black is at the bottom tip and white forms the base's center. The circumference includes colors with at

most two components. Colors with three components are found within the cone's volume.

If you start on the base circumference and increase the missing color

Photo 4-Accidental meaning is added by quantizing the colors in a visualization display.

component, the color moves closer to white and saturation decreases. Decreasing one or two components decreases the value or brightness. Traveling around the circumference changes the hue. Photo 1 shows the top circle of the HSV color cone.

The *Hue-Saturation*-*Intensity* system is another fairly easy way to specify color (see Figure 3). The two cones join at their bases with black being at the bottom tip and white at the

top. Equatorial colors have at most two components (e.g., red or red + green = yellow). Colors with three

Photo 3-A gallery of color interpolation functions. Grayscale, intensify, saturation, two-color, rainbow, rainbow with luminance modifications, heated object, and optimal are represented starting in the upper left and moving left to right and fop to bottom.

components are found in the volume of the double cone.

Doing a conversion from HSV or HSI to RGB is reasonably straightforward [1].

#### THE LUMINANCE EQUATION

When displaying information on top of other information or a background (e.g., with text and graphs], it is important to get good intensity contrast. The luminance equation determines good contrasts:

Table 1 shows standard colors and their luminances. Individual color component intensities have been normalized from 0.0 to 1 .O, instead of the more familiar O-255.

Y = 0.30 x red + 0.59 x green + 0.11 x blue

Table 2 offers a first-order approximation of contrast by taking the difference between the luminances of a foreground and background color. The greater the Aluminance, the greater the apparent contrast. A good threshold value for contrast is a Aluminance of about 0.40. This number, of course, varies between people and lighting conditions. Photo 2 depicts a color version of Table 2.

As the luminance equation implies, RGB color space is not perceptually uniform. A green of (0,1,0) looks brighter than a blue of (0,0,1).

Neither the HSV nor the HSI color space is perceptually uniform either.

Figure 4-In this simultaneous contrast illusion, the white square on the left looks lighter than the white square on the right In fact, fhey are both the same. Only the surrounding colors differ.

On the circumference of the color cone, green looks brighter than blue. If perceptual uniformity is important, it is better to ask for color in the CIELAB or CIELUV color space. [2]

#### COLOR ATTRIBUTES

In choosing color, be aware of established cultural or professional meanings for certain colors. Any visualization portraying set qualities is less effective if it fights the colors most viewers associate with these qualities.

For example, red indicates stop, on, off, hot, dangerous, high stress, oxygen, shallow, and money loss, depending on the application.

#### COLOR INTERPOLATION

Just as color represents ranges of scalar values such as temperature or stress, good ways must be chosen to interpolate colors in an intuitive and

\*EXPANDABLE...expand your interface to control and monitor up to 512 relays, up to 576 digital inputs, up to 128 analog inputs or up to 128 temperature inputs using the PS-4, Ex-16, ST-32 & AD-16 expansion cards.

FULL TECHNICAL **SUPPORT...provided** over the telephone by our staff. Technical reference & disk including test software & programming examples in Basic, C and assembly are provided with each order

HIGH RELIABILITY...engineered for continuous 24 hour industrial applications with 10 years of proven performance in the energy management field.

CONNECTS TO RS-232, RS-422 or **RS-485...**use with IBM and compatibles, Mac and most computers. All standard baud rates and protocols (50 to 19,200 baud) **Use our 900 number to order FREE INFORMATION PACKET.** Technical information (614) 464-4470.

24 HOUR ORDER LINE (800) 842-7714 Visa-Mastercard-American Express-COD

International & Domestic FAX (614) 464-9656 Use for information, technical support & orders. ELECTRONIC ENERGY CONTROL, INC. 380 South Fifth Street, Suite 604 Columbus, Ohio 43215.5436

Photo 6—In this simultaneous contrast illusion, you can see how red, green, and blue change as background luminance changes.

unambiguous way. There are many ways to do this.

• grayscale interpolation

The simplest way to interpolate color is through grayscale, which is easy to produce-mix equal amounts of red, green, and blue. However, many resist grayscale interpolation because it is not sufficiently flashy.

But, grayscale interpolation has a major advantage. It faithfully reproduces a range of scalar values without assigning any preconceived ideas about the order. Physicians using computer graphics dislike color interpolation for x-ray photographs since color can imply meaning where there is none. For example, a bright red area draws attention even though it is no more significant than any other color.

Grayscale's major disadvantage is that the eye only sees a limited number of shades per hue. Multiple hues offer more scalar values.

• HSV and HSI (rainbow) interpolation

To get a reasonable color range for displaying scalar values, interpolate hues in the HSV or HSI color spaces. You can hold the saturation and value or intensity constant and linearly interpolate the hue.

Typically, this interpolation begins at blue, passes through green, and ends at red. The blue-green-red path is popular because it approximates the color order of the electromagnetic spectrum that everyone sees in a rainbow. The direction blue-green-red or red-green-blue is determined by the inherent meaning of those colors in that particular application.

However, this method has problems. The best-looking colors on the monitor are fully saturated, but saturated colors cause problems with hardcopy and video devices. Typically, saturation should be held at 0.80 or less during the interpolation.

As well, different hues are perceived to have different intensities. Yellow is seen as the brightest, most important color (not red). If this distortion is a problem, use the luminance equation with the HSV or HSI equations to achieve a constant luminance instead of constant value or intensity.

This interpolation method also leaves large ranges of scalar values mapped to similarly perceived colors. You can make this clearer by having every nth scalar value map to black or white, creating contour lines to distinguish scalar values. This technique is especially effective in dynamic displays, but double check that you don't accidentally add meaning through color discontinuities.

• saturation interpolation

This method gives a color scale from unsaturated gray to a fully saturated color and is convenient when the hue carries other informational meaning and cannot be modulated.

Fully saturated areas are most colorful and draw most of our attention. Map the most important scalar

Photo 7—Because of simultaneous contrast, identical colon which are further apart spatially are more likely to appear different. Although if is fairly easy to identify the colored square's match on the right in the first photo, if is next to impossible in the second.

values here. For example, information on forest fires could overlay an existing colored map. If saturation is inversely proportional to the amount of burn, severely burned areas are gray or nearly gray and untouched areas retain their full map color.

#### intensity interpolation

You can also hold the hue and saturation constant to interpolate the intensity, which produces a color scale running from a dark version of a color to a light version of the same color (e.g., black to white).

This method is seldom used in scientific visualization because too often the difference in intensity is mistaken for 3D light-source shading (2D images with significant intensity variations tend to look 3D).

Use this interpolation method carefully and only with good reason!

#### • two-color interpolation

Sometimes, it's an advantage to show the variation of a scalar variable by interpolating between two colors. For example, with a terrain map, a forest (green) and a desert (brown) uses natural colors to correspond to scalar values. Interpolating the brown and green indicates forested land.

• heated-object color scale

When an object is heated, its color passes through a range of frequencies from red to yellow to white otherwise known as the *heated-object color curve*. It is used, among other things, to determine the temperature and motion of stars. That range of colors quite effectively encodes scalar information [3].

• optimal color scales

Levkowitz and Herman [3] also use a color scale passing through red, yellow, and light blue while moving from black to white. This color scale optimizes the maximum number of perceptually equal changes from black to white and distinguishes the maximum number of scalar values in a many-valued image such as a CAT scan or satellite image.

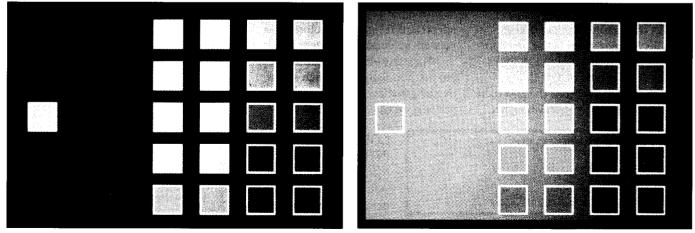

Photo 3 shows a gallery of color interpolation functions. However, it is

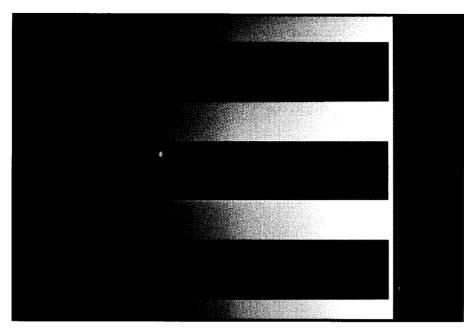

Figure 5—With the mach banding illusion, the eye sharpens each edge by making each band appear brighter on the left and dimmer on the right. In fact, the intensity is constant within each band.

sometimes necessary to interrupt the continuity of color interpolation because your system has only 256 colors or you need to add black or white colors to create contour lines. In either case, a less-than-continuous change of colors might be interpreted as a dramatic change in the scalar values. Photo 4 shows what can happen when 16.7 million colors are quantized to 256. Note that the boundary between scalar values in the quantized image appears much sharper than it really is.

#### REINFORCING INFORMATION

Color has an enormous impact on the way people perceive information. Here are some principles that you need to bear in mind while using color.

• color indicates patterns

Because color can be perceived as a global pattern, using color to reinforce smaller details often reveals new patterns in the data.

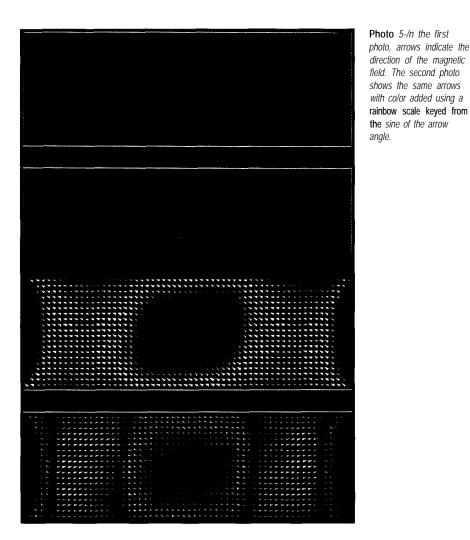

For example, a large vector field could be displayed as a collection of arrows where each arrow's size and direction shows the value of the vector field at that point. It is difficult to look at such a display and understand the overall pattern of vector magnitudes. Color coding the vectors (e.g., low velocity marks one end of the color

spectrum and high velocity the other) reveals more of the overall pattern.

Photo 5 enables viewers to better understand the distribution and direction of a magnetic field.

• limit the number of colors

If viewers need to discern information quickly or for absolute color discrimination, limit the total number of colors. Too many colors cause a viewer to overanalyze the information (at best) or get it wrong (at worst). Studies show that approximately seven colors is the optimal number for easy memorization and discernment.

• surrounding change colors

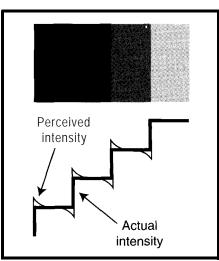

Simultaneous contrast is a wellknown effect which states that our perception of a color is tainted by surrounding colors.

In Figure 4, the white square on the left looks lighter than the white square on the right. Photo 6 shows another example of the simultaneous contrast illusion. Here, you can see how red, green, and blue change as background luminance changes. These examples reinforce the argument for using fewer colors when quickly discrimination is needed.

• compare adjacent colors

Because of simultaneous contrast, the farther apart two colors are spatially, the more likely it is that intervening colors cause them to appear different, even if they are identical.

Photo 7 shows a pathological example of this. A colored square is meant to be matched to one of the squares on the right. With a solid background, it is not hard to do. In the second photo, the background has been replaced with one of changing color. The differences in background, combined with the distance between the colors to be matched, make comparison more difficult.

• colors change with area size

Perception of a color depends on its area. In particular, our ability to discriminate colors diminishes with size. This is especially true with saturated blues, which should be avoided for small objects. Color standards know about this effect and thus fix the size of the color area presented to test subjects. Typically, this is around 2" of subtended arc (2" is about how large your thumb appears at the end of your outstretched arm. A full moon subtends an arc of about 0.5").

If you don't believe that perception of color changes with the size of the colored area, remember the paint swatch you liked and the painted wall you didn't.

. color changes with ambient light

High ambient light tends to desaturate the appearance of colors, particularly yellows.

• the ability to discriminate colors changes with age

You're not going to change this much-just use fewer colors.

• beware of afterimage anomaly

With all-green calligraphic CRTs, there was a phenomenon known as *pink eye*. After staring at a green screen for a while, the victim would rise, look around, and see nothing but pink. This afterimage of a particular color is determined by its complement in either the Red-Green or Blue-Yellow pair.

While this is fun to experiment with, it can seriously jeopardize conclusions in scientific visualization and reinforces the need for fewer colors. The more difference between display colors, the less likely an afterimage will cause one color to be mistaken for another.

beware the anomaly of mach banding

The human visual system tries to automatically increase edge sharpness. Nowhere is this more obvious than in a series of intensity bands shown in Figure 5.

Even though a spectracolorimeter shows that the intensity is constant within each band, the eye sharpens each edge by making each band appear brighter on the left and dimmer on the right. We perceive a cusping effect as would be seen in a Greek column.

Mach banding also shows up when smooth-shading polygons. Even though the intensity is interpolated within each polygon, at the polygon borders there is a first-derivative discontinuity in intensity so that bright or dark lines appear along polygon boundaries.

Since mach banding interferes with the eye's ability to discriminate intensity differences, don't expect crucial decisions to be made based on

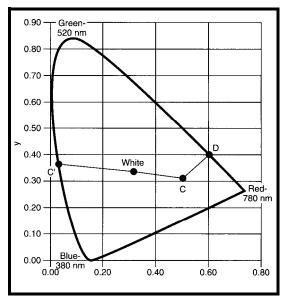

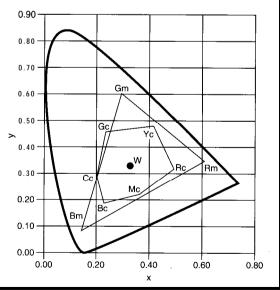

Figure 6-The interior of the CIE chromaticity diagram represents the total color set that humans perceive.

displays where there is abrupt intensity or intensity-slope changes.

• be aware of color-recognition deficiencies

The phrase "color blindness" is a misnomer, better described as a color-recognition deficiency. Many people (-10% Caucasian men, -4% non-Caucasian men, and -0.5% women) have some form of color-recognition deficiency.

The most common deficiency is the inability to discern red versus green. It is a good rule of thumb to redundantly display important information (e.g., colored and outlined).

Because many have problems recognizing colors quickly, don't have color recognition as the single point of failure in crucial operations of interac-

tive systems. Also, because hardcopies get photocopied, color information is eliminated. Duplicate information through shape, fill pattern, outline pattern, outline thickness, character strings, fonts (including bold and italics), and symbols.

#### outline boundaries

Two colored areas adjacent to each other is common in scientific visualization (e.g., when two countries abut on a map or areas of stress concentration are depicted contiguously).

Usually, the shape of the border is important since cones, which detect color, are not good at detecting boundaries. Rods detect boundaries well, especially if the line between adjacent colors is black or white.

avoid saturated blues for fast-moving items or fine detail

Only about 10% of your cones are the S-type, which means that your

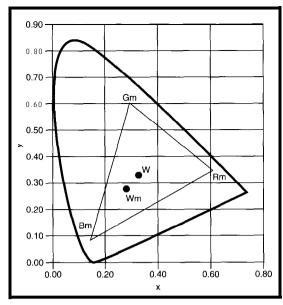

Figure 7—In the color gamut for a Silicon Graphics monitor, the white of the monitor (Wm) is more blue than the overall white point (W).

sensitivity to blues is reduced. In other words, the visual system processes blues less effectively than other colors. From the luminance equation, we know that only about 11% of overall luminance come from blue. Less-saturated blues work much better because other wavelengths are mixed in, thus stimulating the more effective M- and L-type cones.

• avoid mixing saturated reds and blues together

Do not place saturated reds and blues next to each other. In the eye, low color frequencies (reds) focus in front of high frequencies (blues). The difference in focal locations, known as *chromostereopsis*, appears to the eye as a change in depth. The red portion appears closer to the viewer than does the blue portion.

In advertising, this effect is often used to draw attention. In scientific visualization, however,

it can be disconcerting. Although the viewer knows that the entire display is at a single depth, chromostereopsis fights this knowledge.

If reds and blues must be adjacent, desaturate them so that other color

## HAL-4

EEG Biofeedback Brainwave Analyzer

The HAL-4 kit is a complete battery-operated 4-channel electroencephalograph (EEG) which measures a mere 6"x7". HAL is sensitive enough to even distinguish different conscious states between concentrated mental activity and pleasant daydreaming. HAL gathers all relevent alpha,

beta, and theta brainwave signals within the range of 4-20 Hz and presents it in a serial digitized format that can be easily recorded or analyzed.

HAL's operation is

straightforward. It samples four channels of analog brainwave data 64 times per second and transmits this digitized data serially to a PC at 4800 bps. There, using a Fast Fourier Transform to determine frequency, amplitude, and phase components, the results are graphically displayed in real time for each side of the brain.

HAL-4 kit.....\$179.00 plus shipping

The Circuit Cellar Hemispheric Activation Level detector Is presented as an engineering example of the design techniques used inacquiringbrainwavesignals. ThisHemispheric Activation Level detector Isnot a medically approved device, no medicalclaims are made for this device, and it should not be used for medical diagnostic purposes. Furthermore, safe use requires that HAL be battery operated only Sonar Ranging Experimenter's Kit Targeting ♦ Ranging ♦ Machine Vision

The Circuit Cellar TI01 Ultrasonic Sonar Ranger is based on the sonar ranging circuitry from the Polaroid SX-70 camera system. The TI01 and the original SX-70 have similar performance but the TI01 Sonar Ranger requires far less support circuitry and interface hardware.

CHECK OUT THE NEW CIRCUIT CELLAR

HOME CONTROL SYSTEM

◆ Expandable Network

♦ Voice

- ♦ Digital and Analog I/O

- ◆ IR Interface

- ◆ Digital and Analog I/O

◆ X-10 Interface

- ♦ Remote Displays

- Telephone Interface

#### Call and ask about the HCS II

| To order the products shown or to receive a catalog,              |

|-------------------------------------------------------------------|

| call: (203) 875-2751 or fax: (203) 872-2204                       |

| Circuit Cellar Kits • 4 Park Street • Suite 12 • Vernon, CT 06066 |

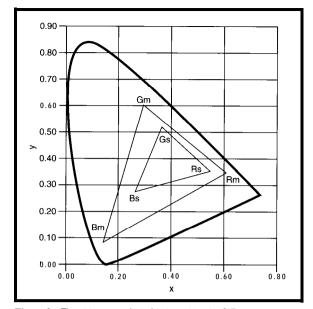

Figure 8—The slides are projected before taking the CIE measurements so they are viewed in the environment they will most often be seen in. Thus, this color gamut is a result of both the film's color response and the projector light bulb's color bias.

frequencies mix in and the frequency difference is not as dramatic.

• do not display high spatial frequencies in color

High spatial frequencies (e.g., closely spaced thin parallel lines) are a lot easier to recognize in black and white than in color. Rods have higher spatial discrimination than cones.

#### COLOR GAMUTS

A color is a color, right? Wrong. The color a device is asked to display and the color that comes out are usually different. The range of colors that a graphics device is capable of displaying is referred to as a *color gamut*.

Before discussing color gamuts, we need to introduce the *CIE chromaticity diagram.* Figure 6 shows this diagram which was created in 193 1 by the Commission Internationale d'Éclairage (CIE) and was the result of experiments in human color vision.

Although it is interesting to delve into how the graph was created or why it is the shape it is, the important thing to know is that the interior of the graph represents the total color set humans perceive. The horseshoe represents the electromagnetic spectrum from 380 nm (blue) in the lower-left corner to 520 nm (green) at the top and 780 nm (red) in the lowerright corner. The equalenergy white point lies at the coordinate (0.33, 0.33). The distance from the white point measures saturation, and the angle around the white point is considered the hue.

Colors on the outline of the horseshoe are *pure colors* (i.e., composed of a single wavelength). The exception to this rule is the diagonal straight line from blue to red, known as the *magenta line*. The line is pictured because display monitors mix blue and red to get magenta, so it is handy to have some way of showing this, even though the electromag-

netic spectrum does not.

For the color C in the interior, the shortest distance to the outline of the horseshoe produces the color's dominant wavelength, D. A line through the white point (W) produces the color's complementary color C'.

The CIE diagram provides a standard measurement methodology for comparing color on different devices. CIE color is measured with an instrument called a *spectracolorimeter*. Different devices (CRTs, paper, film) have different color gam-

uts.

For example, Figure 7 shows the color gamut for a particular Silicon Graphics monitor (measured by a Photo Research PR-650 spectracolorimeter [4]). Note that the white of the monitor (Wm) is more toward the blue part of the gamut than the overall white point (W). Monitor vendors have discovered what laundry detergent makers have known for some time: humans perceive a slightly bluish white as being more "white" than pure white.

Obviously, there are many colors the eye detects that the monitor cannot display, primarily in the green areas. This problem is most critical in generating realistic images, but in scientific visualization, color usually represents something else.

It does, however, become a major consideration when moving scientific visualization images from the monitor to another display device (e.g., a screen dump of a monitor display which sends the RGB values directly to a slide film recorder). Figure 8 shows the color gamut of projected slides.

Not surprisingly, Figure 8 shows a good range of color reproducibility, but with a distinct bias toward the yellow portion of the spectrum. This bias is a result of the yellowish color coming from the bulb in the projector. This drift mostly hurts the reproducibility of blues in the original image.

The biggest color gamut problems come in subtractive color printing. Figure 9 shows the color gamut for a Canon CLC-500 color printer. As you can see, the color gamut for the CLC-500 is much smaller than that of the SGI monitor.

Besides having a smaller gamut, this example shows the more insidious problem of color rotation. Lines drawn from the white point through each of the two green points show a considerable rotation around the white point. As a result, not only are the saturated

Figure 9-The biggest problems with co/or gamuts occur in subtractive color printing. As you can see, there can be quite a difference between the color gamut of a monitor and a color printer.

monitor colors not able to be printed, but attempting to print them results in a considerable hue change.

Much work has been done on the use of color theory to match the colors of different display devices [5],[6], and [7].

#### LIMITATIONS OF NTSC VIDEO

Frequently, scientific visualizations are recorded to videotape. It would be nice if this was an automatic process (i.e., what you see on the monitor is what you get on the video).

Sadly, this is not even close to true. NTSC [North American) video has a set of idiosyncrasies that must be understood to make the production of scientific videos hassle free. The following are some general guidelines when going to NTSC video from a display:

- Don't wait until the last minute to consider video issues. The best time to begin thinking about them is when you start to design your display. The colors, layout, and amount of fine detail all come into play when you eventually go to video.

- NTSC does not handle saturated colors well. Use a saturation of 0.80 or less.

- Use two or more pixel thicknesses (no single-pixel thicknesses).

- The resolution of NTSC video is approximately 640 x 480. Keep this in mind when deciding how large to make text, graphs, and so on.

- NTSC is encoded with 267 intensity cycles occurring per scanline. Any more than this does not show up.

- NTSC is encoded so that 96 cycles of orange-blue and 35 cycles of purplegreen occur per scanline. (Orangeblue is emphasized more than purple-green because this range includes flesh tones.) Much less detail can be encoded in color than can be encoded in intensity because of the sensitivity of the human eye. Fine detail should be displayed in black and white, not color.

- Most workstation video must be passed through a standards converter before it is NTSC compatible. It is important to understand the characteristics of your standards converter

and how it downsizes the image. For more information, see Blinn [8].

#### PREVENT COLOR POLLUTION

Finally, avoid overuse. Just because you have  $2^{24}$  colors, doesn't mean you have to use them all.  $\Box$

Dr. Mike Bailey is a senior staff scientist at the San Diego Supercomputer Center and an associate professor at the University of California at San Diego. Mike specializes in scientific visualization and computeraided engineering. He may be reached at mjb@sdsc.edu.

#### REFERENCES

- Jim Foley, Andy van Dam, Steve Feiner, and John Hughes, *Computer Graphics Principles and Practices*, Reading, MA, Addison-Wesley, 1990.

- [2] Roy Hall, Illumination and Color in Computer Generated Imagery, Springer-Verlag, 1989.

- [3] Haim Levkowitz and Gabor Herman, "Color Scales for Image Data," *IEEE Computer Graphics* and Applications, 72-80, January 1992.

- [4] Photo Research, PR-650 Spectra-Colorimeter, Specification Sheet.

- [5] Maureen Stone, William Cowan, and John Beatty, Color Gamut Mapping and the Printing of Digital Color Images, Xerox Report EDL-88-1, 1988.

- [6] Maureen Stone, Color Printing for Computer Graphics, Xerox Report EDL-88-5, 1988.

- [7] Maureen Stone, William Cowan, and John Beatty, "Color Gamut Mapping and the Printing of Digital Color Images," *ACM Transactions on Graphics*, Vol. *7, No. 4, 249-292.*

- [8] Jim Blinn, "NTSC: Nice Technology Super Color," Computer Graphics and Applications, 17-23, March 1993.

401 Very Useful 402 Moderately Useful 403 Not Useful

# Virtual Reality Position Tracking

Until recently, magnetic trackers existed solely in the workstation domain. But, with the poplular advent of VR, trackers have joined the PC world. Here, Herschell and Mark introduce us to tracker technology.

## FEATURE ARTICLE

Herschel1 Murry & Mark Schneider

irtual reality is the science of generating an immersive, synthetic environment about a person. It simulates a real environment where we can move in any direction and automatically get different views of our world. We could generate a similar environment in a virtual world if space, time, and money were no object *and we* had the USS Enterprise and its holodeck.

Failing that, we don a helmet with displays right before our eyes and move around in a cyberworld. Displayed scenery moves as we move. A computer can do this kind of simulation quite nicely if we can tell it our movements so it knows where to scan the scene. And, this is where motion trackers enter into the virtual reality cybersystem design.

The head tracker determines the position and orientation (P&O) of the head, which the computer then uses to generate the appropriate scene for display. Trackers also are used on instrumented gloves (e.g., the DataGlove) for enabling physical interaction in a virtual world.

Since virtual-reality tracking systems are likely to become affordable in the near future, now is a good time to get a jump on understanding them. A thorough explanation of trackers requires a sizable text. We'll explain enough about tracker technology, its use, and interface requirements to give you a working knowledge. Hopefully, it'll be enough to keep you out of trouble.

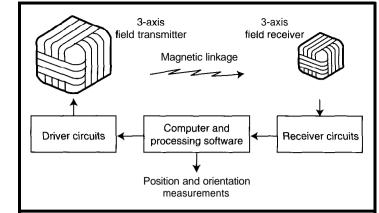

#### TRACKING FUNDAMENTALS

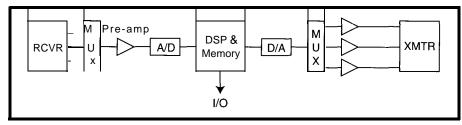

The best current tracking systems are based on the AC electromagnetic coupling between two sets of threeaxis dipole antennas (i.e., three mutually perpendicular coils of wire about a common center). A typical low-cost tracker has a transmitter (the reference set of antennas), a receiver (the tracked set of antennas), and a PC-compatible electronics board (see Figure 1). One of the lowest cost PC-compatible trackers available today, the Polhemus Insidetrak, is shown in Photo 1.

The tracker's PC-compatible electronics can be separated into analog and digital portions. Three receiver antennas are connected to three analog input channels as pictured in Figure 2. These channels are composed of three low-noise, high-gain amplifiers whose outputs are multiplexed into a single fast, high-resolution A/D converter.

The three transmitter antennas are driven by three high-power analog outputs. These outputs are digitally generated via low-resolution DA converters.

No doubt, you realize that other configurations are possible: separate A/D converters representing each channel, a multiplexed D/A converter, and so on. The tradeoffs between the different configurations affect overall price and performance of the tracker.

Analog inputs and outputs are under control of a microprocessor. In recent designs, a DSP has become common since it better performs digital-filtering functions. The DSP is responsible for generating the transmitter signals, collecting the multiplexed input data, processing the raw input data into P&O data, and interfacing to the I/O bus.

These processes occur during a typical tracker measurement cycle. During the data-acquisition time, the transmitter antennas are driven and the induced receiver voltages are measured. This process takes most of the measurement cycle.

Calculation of P&O from the collected data occurs next and uses a smaller part of the cycle. The remaining time is dedicated to performing I/O over the PC bus (or buses like RS-232/422 or IEEE-488 for external tracker

designs). Once a cycle completes, a new measurement cycle begins.

The equations defining the antenna couplings are well known and are solved to give the P&O of the receiver with respect to the transmitter. The main fault with this type of tracker is exhibited when it is used near conductive materials.

Because trackers generate AC magnetic fields, nearby conductive

materials receive and retransmit these fields as well. These additional fields are not accounted for and do not fit the assumptions of the tracking algorithm.

The advantage, however, is that magnetic trackers do not require an unobstructed view between receiver and transmitter like an infrared or ultrasonic system. And, when designed correctly, they are reasonably immune to interference from other electronic gear, but more on that later.

#### TRACKER SPECIFICATIONS

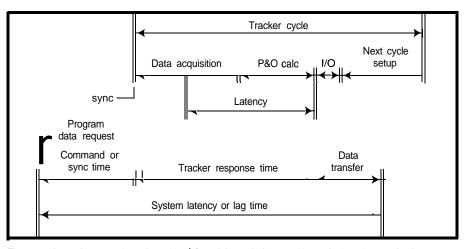

One of the problems in tracking real-time movement is the interval of time called *latency*. Latency is measured from the midpoint of the time period during which data collection occurs (i.e., the midpoint of the motion during this interval) to the start of the output of a P&O solution.

You might wonder about the data taken before and after the midpoint. The crafty tracker designer, using linear prediction, adjusts the collected data from the ends of the data acquisition toward the middle. However, this only covers *tracker* latency. When a tracker is integrated into a VR system, the overall [or system) latency needs to be reckoned with (more on this later).

Other tracker specifications that need definition are:

- update rate

- accuracy

- resolution

- repeatability

Update rate is the interval of time between P&O solutions. If the mea-

Figure 1-A magnetic motion tracker system typically includes a transmitter, receiver, and a PC-compatible electronics board.

surement cycle is 33.3 ms long and the tracker computes a new P&O solution each measurement cycle, the update rate is 30 Hz.

Accuracy indicates how well the computed P&O matches the actual position and orientation. Accuracy is affected by many of the overall system-engineering design considerations including the size of the receiver and transmitter antennas, mechanical assembly of the antennas, drive signal, and signal-to-noise ratio (SNR), among others. SNR itself is affected by a combination of factors including tracker design, its electromagnetic environment, and the range between transmitter and receiver.

A typical contributor to environmental noise is the display. Although many are electrically quiet LCDs, TVs and display monitors are CRTs which generate magnetic fields during refresh. The relatively low-frequency vertical refresh can easily overload the tracker's sensitive front end. The higher-frequency horizontal refresh has become less of a problem recently as these rates have increased beyond the tracker's passband.

As noted earlier, the other environmental threat stems from conductive materials. Every effort should be made in system design to use nonconductive materials like

plastic, wood, and glass. If that is impossible, poor conductors such as cast iron and some types of stainless steels can often be tolerated with small effects. The worst materials to use are good conductors like copper, aluminum, and brass.

The signal strength that combats such noise drops off as the cube of the transmitter-receiver separation since the magnetic field must flood the 3D space. In other words, if the range of separation is doubled, the signal drops to one-eighth of its earlier value (i.e.,  $1/2^3 = 1/8$ ). Obviously, SNR is always an issue in trackers. You'll note the same problem occurs with resolution.

Resolution is the smallest change a tracker can detect in position and orientation. As with accuracy, both system and environmental factors affect resolution. Internally, the resolution of the A/D converter and P&O computation, the circuitry SNR, and a

Photo 1-The Polhemus Insidetrak board is one of the lowest cost PC-compatible trackers available today.

Figure 2—The motion tracker links three antenna coils carrying signals coupled from three transmit coils that are being driven simultaneously. This communication with itself is an idea/DSP application.

magnetically noisy environment degrade the final resolution.

The final and ultimate limiter of resolution is the separation between the receiver and transmitter. A VR tracker might have a working range of 1-5'. Because the strength of the magnetic field varies at 1/range<sup>3</sup>, the signal

Figure 4-The dipole field is symmetrical around any axis drawn through ifs center.

#### drops rapidly with separation.

The maximum signal is designed to occupy the full range of the A/D converter. As the signal decreases, the number of bits required to represent it also decreases so that only the leastsignificant bits are left taking readings.

Positional resolution is therefore specified as a function of range. It can be expected to be on the order of 0.0003–0.001 inch per inch. Orientation resolution, being based on ratios of measurements, is independent of range (except that it's still dependent on data which is represented by a smaller and smaller range of bits] and is usually something like 0.1-0.5".

Repeatability refers to the tracker's proficiency at providing the same P&O output when the receiver is placed in exactly the same position and orientation with respect to the transmitter over and over again. While not normally specified, it obviously is related to both accuracy and resolution. If the accuracy varies due to uncorrected drifting of the circuitry, repeatability suffers. Likewise, if the resolution is so gross that you can easily straddle the demarcation line between two adjacent ADC readings, repeatability again suffers.

#### TRACKER INTERFACING

Now that we know how a tracker works and what its key definitions are, it's time to get to what an application buff might call the "good stuff." A low-cost tracker board is usually based on the 16-bit ISA bus standard for maximum utility (it should work on an EISA bus also). Input commands, tracker status, and data are 16 bits long. A jumper block or switches for setting a bus address are available. Assuming you've read the tracker manual, you have set the correct address to a value different from anything else on the bus.

Being able to access tracker data directly on an internal bus is a plus. Considering that quite a few bytes of data are transferred per P&O answer at least 30 times a second, a great deal of real-time data must be handled. Many trackers on the market today use a serial bus such as RS-232, -422, or -485. However, these units not only must run at a high baud rate, their system software must navigate considerable overhead. As you know, overhead delays getting the data.

Typically, one would like that data directly in the binary representation of the computer. This facility usually is not the case with external interfaces, adding a formatting or conversion task to the software, and thereby adding more delay.

So, with a PC, having the tracking data available right on the ISA bus is a marvelous feature. It makes the tracker appear faster than it really is compared to external trackers.

#### SYSTEM ALIGNMENT

Probably one of the hairiest parts of setting up a motion tracker is getting the transmitter and receiver coordinate systems figured out and coordinated with the video. Of course, everything in a magnetic motion tracker is referenced to its own signal source the transmitter.

This reference frame typically is called the *space frame*. The coordinate framework for the receiver is typically called the body *frame* since it usually is located on your body.

Two processes need to be understood to get these frameworks to cooperate with your video world: transmitter alignment and receiver boresight.

Figure 4-The tracker transmits and acquires data and then calculates position and orientation. Tracker latency extends from the motion acquisition midpoint to the start of the output. Data out continues at the pace of the host computer as the tracker prepares to start the next cycle.

Alignment of the transmitter can be done mechanically, but it is much harder than the mathematical method provided in the tracker. Aligning the transmitter is similar to setting up a camera to pan in the horizontal plane. If you turn left and see nothing but sky and turn right and see nothing but ground, you know the camera is tilted.

Similar processes are available in the

tracker to carry out transmitter alignment through collecting data and making mathematical adjustments. Going through the whole process is beyond this article's scope, but your tracker user's manual is a lot of help.

Once alignment is done, the receiver(s) can be similarly adjusted, but it is much easier. Remember the receiver navigates relative to the transmitter's space-frame coordinates.

Figure 5—If you compare this figure to Figure 4, if is obvious *fhaf the* continuous mode *results* in much greater efficiency.

But, the body frame can be referenced simply by orienting the receiver in a certain direction and executing a boresight command. This position becomes the (0, 0, 0) reference in the body frame. However, if the transmitter has not first been aligned, don't expect a boresight to align it. The boresight only helps with the receiver.

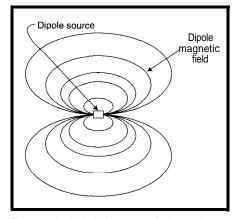

With a magnetic motion tracker, hemisphere is also important. Refer to

the dipole field shown in Figure 3. It is easy to see that it is symmetrical about any axis drawn through its center. This symmetry means there are identical answers 180" apart. Hence, the user must define which hemisphere obtains the right translational output.

Determining this is usually quite easy because you are walking either on the floor or on the ceiling, sitting in-

side the cockpit or outside the canopy. And, the tracker has means for defining the hemisphere in its manual.

However, be cautious with distortion and hemispheres. Sometimes distortion can create an answer that throws the reading into the opposite hemisphere. Needless to say, it's easy to detect, can be very disconcerting, and should be accounted for in system design.

Circuit Cellar INK Issue #60 July 1995 29

#### SYSTEM LATENCY

In Figure 4, you see a complete application cycle, including system lag from cycle initiation to receipt of data.

Of course, you can't afford to wait for data after kicking off a tracker cycle, but it is important to determine what the latency time period is. Once you know the interval, you can go about other tasks and come back for the P&O answer when it is ready. By doing this, little time is lost.

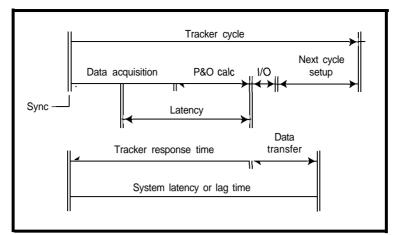

It is even more efficient to set the tracker into continuous tracking operation. By syncing up with it, you only need to return when an interrupt indicates output is available (Figure 5). Hence, each P&O answer precedes display computation. The display frame updates while the tracker comes around with the next cycle.

You can also reduce system latency by using only the parameters you need and obtaining them in the most efficient format for you. You might want binary data rather than ASCII or your application may need only orientation angles and not position. Besides saving memory space, such cuts save code run time, I/O transfer time, and formatting.

#### TRACKER EFFICIENCY PERKS

Even with an efficient internal bus like the ISA, the user can realize even more efficiency by

- requesting only the parameters needed

- . choosing a compact, directly usable data format

- integrating the system cycle with the tracker cycle through proper sync generation

- metering out the system cycle in the most logical and computationally sensible sequence

In his 25-year career, Dr. Herschel1 Murry has served as chief scientist, program manager, and project engineer for companies such as Andrew Government Systems, Rockwell International, and Martin Marietta Aerospace. As vice president of engineering at Polhemus, Herschel1 oversees product design and development.

In his 15 years at Polhemus, Mark Schneider has led the design and analysis for commercial products. This year he received the Academy Award for Technological Achievement from the Academy of Motion Picture Arts and Sciences, Mark serves as Polhemus's manager of newproduct design. Mark may be reached at (802) 6553159, ext. 290.

#### SOURCE

Insidetrak Tom Jones Polhemus, Inc. P.O. Box 560 Colchester, VT 05446 (806) 655-3159, ext. 234 Fax: (802) 655-1439

#### IRS

404 Very Useful 405 Moderately Useful 406 Not Useful

## FEATURE ARTICLE

#### **James Goel**

# Digital Video Resizing and Compression

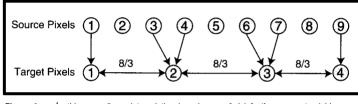

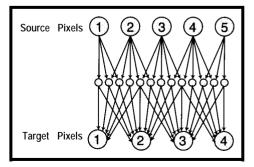

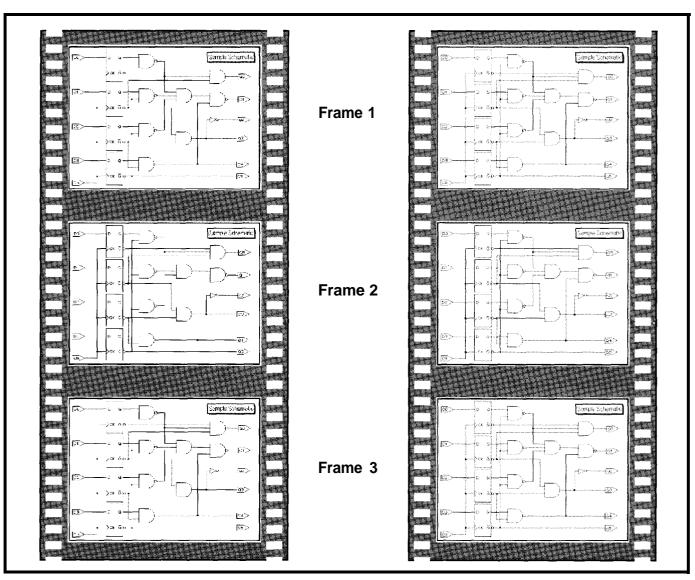

Powerful processors and imaging techniques have made computer video possible. Here, James introduces Genesis's resizing chips. They reduce, bypass, or zoom using FIR filters with up to 65 taps.

eal-time image resizing (often called scaling) is essential in modern video systems. Powerful workstations combine graphics and scaled digital video to create today's hottest computer animation. Everything from huge video walls in trendy night clubs to video-in-a-window teleconferencing on a desktop PC requires digital-video resizing. With the invention of modern graphical user interfaces, people expect to control how and where their video data is displayed-they're no longer content watching fixed-sized video.

Multiple resizable video windows are the next evolutionary progression for modern computers. In fact, the upcoming release of Windows 95 contains integrated video playback software for applications like video conferencing, advanced computeraided learning, and CD-ROM games.

But, before a digital nirvana of cost-effective, high-quality integrated video arrives, a number of difficult problems must be solved. The first is a lack of storage and transmission bandwidth. Video data is too massive to be stored or transmitted without compression, though this situation has improved with video compression standards like the Moving Pictures Experts Group (MPEG-1 and 2), H.261, and the Joint Photographic Experts Group (Motion JPEG). These standards are widely accepted and use various algorithms to achieve compression ratios of 100: 1 and beyond.

The second problem is a lack of quality scaling. Efficient video compression is just one link in a chain. It must be coupled with effective resizing to create an image worth viewing. Until recently, systems relied on the "cheap and nasty" *nearest neighbor* or the slightly better *linear interpolation* algorithms for video scaling.

Unfortunately, these algorithms produce video images suffering from aliasing (visually evident as absent image detail or extraneous artifacts). Until now, resulting picture quality has ranged from barely acceptable to poor. Fortunately, new cost-effective, high-quality scaling algorithms have been developed.

Distortion-free scaling is crucial in applications like video production, teleconferencing, navigation instrumentation, and medical imaging because these applications demand high-quality output. Modern systems chain devices together to manipulate digital video during production. Throughout this process, quality video scaling must be used to prevent contamination of final video output.