# EREUres

# THE COMPUTER APPLICATIONS JOURNAL #65 DECEMBER 1995 PROGRAMMABLE DEVICES

In-Circuit-Programmab GALs

Low-Cost FPGA Programmer

Design Contest Winners In EPC: Novell's NEST

\$3.95 U.S. \$4.95 Canada

# **EDITOR'S** INK

# Start Ups

Ithough most of us get to participate in the beginning of projects, seldom do we get involved in the start up of a company, association, or—for that matter-publication.

I guess I'm lucky. In 1987, I was asked to add "technical editor" to my engineering duties. With the publication then being bimonthly, I was still able to devote much of my time to engineering. The editing **part** of my job provided a nice touch of spice to an otherwise engineering-only diet

As the magazine has grown to a monthly publication, my responsibilities have shifted accordingly. In the last week before an issue ships, how I almost long for an engineering-only diet! The engineering is now what keeps me sane.

With the start of *INK's Embedded PC*, Circuit Cellar is opening itself up to another adventure. What started as a quarterly insert in 1995 is already scheduled as a bimonthly insert in 1996. Starting in February's issue, there will be an additional 32 pages devoted entirely to the embedded PC industry.

What changes has this brought in-house? While I stay editor-in-chief of the magazine as a whole, Janice becomes a hybrid of technical editor for *INK* and managing editor of *Embedded PC. New* to the ranks is Carole, joining us as a technical editor, alleviating an overly tight workload and giving room for growth.

The only area we remain a little tight on is the need for *EPC* articles. *Embedded PC* will focus on both PC software and hardware. We'll be covering off-the-shelf motherboards, expansion boards, networking, PCI, other buses, assemblers, compilers, debuggers, multitasking, and operating systems. In other words, assuming your manuscript meets our readership standards, we'll print it. Just send your proposals in.

This issue's *Embedded PC* offers a good mix of topics. Novell introduces their networking expertise to the embedded PC world while Larry Fish shows us how to get the benefits of **32-bit** unsegmented architecture under DOS and BIOS. Ken Prada covers **PC/104** instruments in oceanography and Russ overviews PC buses.

In the main issue, Stuart Ball takes a close look at PLDs that can be programmed in-circuit, along with some sample applications. David Van den Bout shows us how to build a simple CPLD development system. Finally, Fred Eady overviews the PIC16Cxx family.

For our columns, Ed covers Virtual-86 interrupts from the **32-bit** side, Jeff finishes up his two-part article on a carrier current modem, and Tom overviews the conference circuit.

# 7Cen

#### editot@circellar.com

APPLICATIONS JOURNAL

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

THE COMPUTER

EDITOR-IN-CHIEF Ken Davidson

EPC MANAGING EDITOR Janice Marinelli

TECHNICAL EDITOR Carole Boster

ENGINEERING STAFF Jeff Bachiochi & Ed Nisley

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Rick Lehrbaum Russ Reiss

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR Lisa Ferry

PRODUCTION STAFF John Gorsky James Soussounis

CONTRIBUTORS: Jon Elson Tim McDonough Frank Kuechmann Pellervo Kaskinen PUBLISHER Daniel Rodrigues

PUBLISHER'S ASSISTANT Sue Hodge

CIRCULATION MANAGER Rose Mansella

CIRCULATION ASSISTANT Barbara Maleski

CIRCULATION CONSULTANT Gregory Spitzfaden

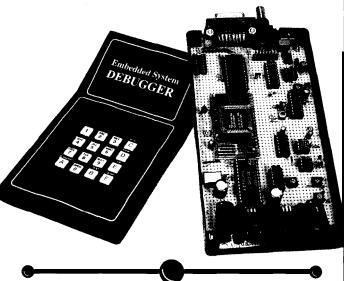

> BUSINESS MANAGER Jeannette Walters

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK\*. THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0896-8985)is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite20, Vernon, CT 06066 (860)875-2751. Second Class postage paid at Vernon, CT and additional offices. One-year (12 issues)subscription rate U.S.A. and possessions \$21.95, Canada/Mexico \$31.95, all other countres \$49.95 All subscription orders payable in U.S. funds only. VIa International postal money order or check drawn on U S bank. Direct subscription orders and subscription related questions to Circuit Cellar INK Subscriptions, P.O. Box 696, Holmes, PA 19043-9613 or call (800) 269.6301.

POSTMASTER: Please send address changes to Circuit Cellar INK, Circulation Dept. P 0 Box 698, Holmes, PA 19043-9613.

Cover photography by Barbara Swenson PRINTED IN THE UNITED STATES

For information on authorized reprints of articles. contact Jeannette Walters (860) 8752199.

#### HAJAR ASSOCIATES NATIONAL ADVERTISING REPRESENTATIVES

| NORTHEAST &                  | SOUTHEAST                         | MIDWEST                           | WEST COAST                       |

|------------------------------|-----------------------------------|-----------------------------------|----------------------------------|

| MID-ATLANTIC<br>Barbara Best | Christa Collins<br>(305) 966-3939 | Nanette Traetow<br>(708) 357-0010 | Barbara Jones<br>& Shelley Raine |

| (908) 741-7744               | Fax: (305) 985-8457               | Fax: (708) 357-0452               | (714) 540-3554                   |

| Fax: (908) 741-6823          |                                   |                                   | Fax: (714) 540-7103              |

Circuit Cellar BBS-24 Hrs. 300/1200/2400/9600/14.4k bps, 6 bits, no parity, 1 stop bit, (860) 871-1988; 24001 9600 bps Courier HST, (860)871-0549. World Wide Web: http://www.circellar.com/

All programs and schemata In Circuit Cellar INK® have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or informationpublished in Circuit Cellar INK®.

Entire contents copyright © 1995 by Circuit Cellar Incorporated. All rightsreserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. isprohibited.

| 1                                                                                                | 2          |       | System-Programmable PLDs from Lattice<br>Stuart Ball                                                       |                                                                                              |     |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|------------|-------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|

| 2                                                                                                | 0          |       | Building a Low-Cost CPLD Development System<br><i>by David Van den Bout</i>                                |                                                                                              |     |  |  |  |  |  |  |  |  |

| 2                                                                                                | 8          | A L   | Take Your PIC<br>A Look at the PIC 16Cxx Family<br>by Fred Eady                                            |                                                                                              |     |  |  |  |  |  |  |  |  |

| 3                                                                                                | 6          |       | 7th Annual Circuit Cellar Design Contest Winners<br>by Janice Marinelli                                    |                                                                                              |     |  |  |  |  |  |  |  |  |

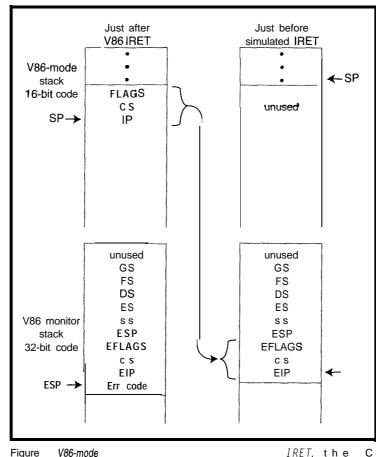

| 7                                                                                                | 4          |       | <b>Firmware Furnace</b><br>Journey to the Protected Land: Behind the Interrupt Curtain<br><i>Ed Nisley</i> | 1                                                                                            |     |  |  |  |  |  |  |  |  |

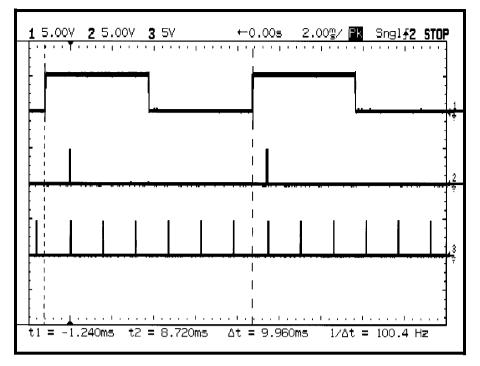

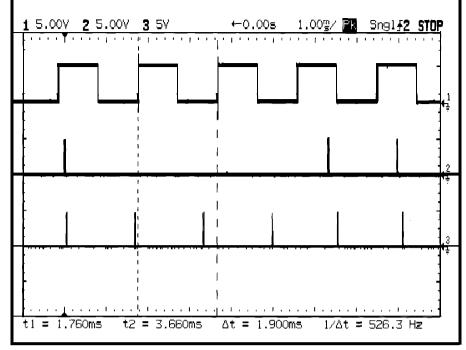

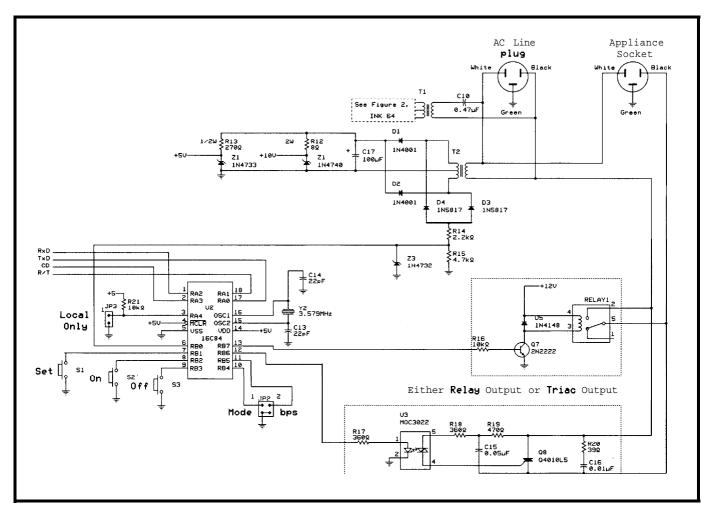

| 8                                                                                                | 4          |       | From the Bench<br>Carrier Current Modem<br>Part 2: Alternative Control<br>Jeff Bachiochi                   |                                                                                              |     |  |  |  |  |  |  |  |  |

| 9                                                                                                | 2          |       | Silicon Update<br>PC Times in Silicon Valley<br>Tom Can trell                                              |                                                                                              |     |  |  |  |  |  |  |  |  |

|                                                                                                  |            |       | BEDDED P(                                                                                                  |                                                                                              |     |  |  |  |  |  |  |  |  |

| See                                                                                              | e I        | pag   | ges 39–73 for OUI Special Box                                                                              | nus Sectior                                                                                  | 1   |  |  |  |  |  |  |  |  |

| <ul> <li>2 Editor's<br/>Ken Dav</li> <li>Start Ups</li> <li>6 Reader's<br/>Letters to</li> </ul> | idson<br>S | ditor | <b>INSIDE</b><br><b>ISSUE</b>                                                                              | <b>ConnecTime</b><br>Excerpts from<br>the Circuit Cellar BBS<br>conducted by<br>Ken Davidson | 99  |  |  |  |  |  |  |  |  |

| 8 New Pro                                                                                        |            |       |                                                                                                            | Steve's Own INK<br>The Powers that Be                                                        | 112 |  |  |  |  |  |  |  |  |

|                                                                                                  |            | -     | $O_{O}$                                                                                                    | Advertiser's Index                                                                           | 81  |  |  |  |  |  |  |  |  |

# **READER'S INK**

#### A BETTER LEAD

Ed Lansinger's articles on developing an engine control system really interested me, especially since I've gone from having computers as a career and cars as a hobby to the other way around.

I think readers should know about the ignition wires my company imports to Australia from the USA. Magnecor ignition leads are wire-wound leads with 5-20 times more windings than other "heli" leads. They also suppress more RFI and EMI.

While using these wires won't stop your competitors' cars from bringing your ECM unglued due to RFI, the EM1 suppression may help when your sensor wiring goes near your plug wires. Contact:

> Magnecor Australia Pty. Ltd. 2000 Oakley Park Rd., Unit 104 Walled Lake, MI 48390 (810) 669-6688 Fax: (8 10) 669-2994

Neil Fisher neilf@zeta.org.au

#### **Contacting Circuit Cellar**

We at *Circuit Cellar INK* encourage communication between our readers and our staff, so have made every effort to make contacting us easy. We prefer electronic communications, but feel free to use any of the following:

- Mail: Letters to the Editor may be sent to: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066.

- Phone: Direct all subscription inquiries to (800) **269-6301**. Contact our editorial offices at (860) 875-2199.

- Fax: All faxes may be sent to (860) 872-2204.

- BBS: All of our editors and regular authors frequent the Circuit Cellar BBS and are available to answer questions. Call (860) 871-1988 with your modem (300–14.4k bps, 8N1).

- Internet: Letters to the editor may be sent to **editor@circellar**. corn. Send new subscription orders, renewals, and address changes to **subscribe@circellar.com**. Be sure to include your complete mailing address and return E-mail address in all correspondence. Author E-mail addresses (when available) may be found at the end of each article. For more information, send E-mail to **info@circellar.com**.

WWW: Point your browser to http://www.circellar.com/. FTP: Files are available at ftp://ftp.circellar.com/pub/circellar/.

TM

| <ul> <li>Memory mapped variables</li> <li>in-line assembly language option</li> <li>Compile time switch to select 8051/803 1 or 8052/8032 CPUs</li> <li>Compatible with any RAM or ROM memory mapping</li> <li>Runs up to 50 times faster than the MCS BASIC-52 interpreter,</li> <li>Includes Binary Technology's SXA51 cross-assembler &amp; hex file manip. util.</li> <li>Extensive documentation</li> <li>Tutorial included</li> <li>Runs on IBM-PC/XT or compatibile</li> <li>Compatible with all 8051 variants</li> <li>BXC51 \$ 295.</li> <li>508- 369- 9556</li> <li>FAX 508-369-9549</li> <li>Binary Technology, Inc.</li> </ul> | <ul> <li>General And Analog I/O along with gover supply regulation and control system in a %-cubic-inch package. The fotted Net-Port contains a variet of digital and analog I/O along with gover supply regulation and communication line drivers. Net-Port requires no programming. A simple ASCI communication line drivers. Net-Port requires no programming. A simple ASCI communication line drivers. Net-Port requires no programming. A simple ASCI communication line drivers. Net-Port requires no programming. A simple ASCI communication line drivers. Net-Port requires no programming. A simple ASCI communication line drivers. Net-Port requires no programming. A simple ASCI communication line drivers. Net-Port requires no programming.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to 15kbcs.</li> <li>Mexaza, RS-422, and RS-485 at 300 bosts to</li></ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P.O. Box 541 • Carlisle, MA 0 1741                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | actures subject to change<br>4 Park Street • Vernon, CT 06066 • (860)871-6170 • Fax (860) 872-2204<br>#119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>in-line assembly language option</li> <li>Compile time switch to select 8051/803 1 or 8052/8032 CPUs</li> <li>Compatible with any RAM or ROM memory mapping</li> <li>Runs up to 50 times faster than the MCS BASIC-52 interpreter,</li> <li>Includes Binary Technology's SXA51 cross-assembler &amp; hex file manip. util.</li> <li>Extensive documentation</li> <li>Tutorial included</li> <li>Runs on IBM-PC/XT or compatibile</li> <li>Compatible with all 8051 variants</li> <li>BXC51 \$ 295.</li> <li>508-369-9556</li> <li>FAX 508-369-9549</li> <li>Binary Technology, Inc.</li> <li>P.O. Box 541 • Carlisle, MA 0 1741</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## NEW PRODUCT NEWS Edited by Harv Weiner

#### TARGET-CONTROLLER SOFTWARE

Stimgate releases a new productivity tool for developing portable software for embedded microcontroller systems. The **Target Controller for ANSI C** enables software to be written in ANSI C on the PC using well-known tools such as Borland C or Microsoft C. Portability between processor types is ensured by Stimuli-Gateway I/O functions that complete ANSI C with standardized I/O operations for the target microcontroller. By using files and libraries, you can reuse code between different target platforms or C compilers.

The Stimgate Target Controller hardware connects I/O in embedded target processor systems to the PC. It interfaces to the target system by plugging into the EPROM slot and emulates the most popular EPROM, EEPROM, and RAM devices. As with in-circuit emulators, software for different microcontrollers and derivatives of the same processor can be tested without additional personality modules. Prototype software runs out of the target controller memory, which speeds up testing and debugging over traditional program, burn PROM, and edit cycles.

The Stimgate system has built-in hardware stimulation facilities and a library of test functions for test and debugging applica-

tions. High-level messages can be sent to the PC to aid in debugging without using the UART. The Stimgate stream windows facilitate message handling from the target system. Once the code has been proven, it can be recompiled and ROMed for the target system using the target microcontroller compiler.

The full development system, which supports embedded controllers such as 8051, 68HC11, 80x86, 683xx, H8/300, H8/300H, and more, sells for \$3950.

#### **CMX Company**

5 Grant St., Ste. C • Framingham, MA 01701 • (508) 872-7675 • Fax: (508) 620-6828 • E-mail: cmx@cmx.com

#500

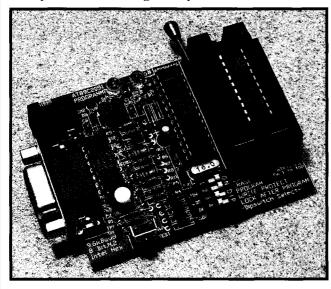

#### FLASH MICRO PROGRAMMER

AirBorn Electronics announces a development programmer for the AT89C2051 microprocessor, **Model PG2051**. The AT89C2051 is a 20-pin 805 I-compatible microprocessor [including serial port) with 2 KB of flash

memory. The PG205 1 erases, programs, and verifies the AT89C2051 chips in 6 s.

The PG205 1 may be connected to a PC or other host by a serial cable. According to the settings on its DIP switches, the programmer tests, erases, programs, verifies, and write and security protects as it receives the file. The unit features a test switch which enables the user to check in just one second if the target microprocessor is blank, working, programmed, or failed without needing the PC connected.

The PG2051 Programmer sells for **\$188** and includes data sheet. A complete evaluation kit is available for \$233. It includes the programmer, plug back, two AT89C2051 devices, a small prototype board, sample code, and a shareware assembler and disassembler.

#### AirBorn Electronics

19-21 Berry St., Ste. 201 • P.O. Box 1491 North Sydney, NSW 2060, Australia (61) (2) 9925-0325 • Fax: (61) (2) 9925-0297 E-mail: stevenmQzeta.org.au

# NEW PRODUCT NEWS

#### PC IN A BOX

Kila Systems PC-in-a-Box is a complete DOS system configured as a dedicated controller to run one program for many users. Typical applications are ticketing terminals, POS systems, factory automation, and alarm systems.

PC-in-a-Box is powered by a Chips and Technology F-8680 microprocessor, an ATequivalent integrated chip with internal peripherals. Its architecture is identical to a PC, except onboard solid-state memory replaces the hard disk. An alphanumeric keypad and graphics LCD provide input and output. DOS applications are developed using high-level compilers and run exactly as they would on a PC. The final code is placed in ROM, flash, or battery-backed RAM. The system runs unattended off an internal rechargeable battery.

The unique features of the PC-in-a-box are an onboard CGA controller and graphic LCD, extensive use of flash and battery-backed SRAM, PCMCIA support, and a customized BIOS for portable applications with extensive power management. Three serial and two parallel ports are also available, and an 8255 chip provides 24 I/O lines. The unit typically requires 100 mA at +5 V and, in suspend mode, power consumption is less than 2 mA.

The PC-in-a-Box is enclosed in a 8.8" x 5.5" x 1.6" custom plastic enclosure. An evaluation kit sells for \$399. The CPU card with 256-KB PSRAM and one serial port sells for \$229 in quantities of 100.

#### Kila Systems

2300-C Central Ave. • Boulder, CO 80301 • (303) 444-7737 • Fax: (303) 786-9983 E-mail: kilaQrainbow.rmii.com

#### #502

#### SCOPE-TRIGGERING DEVICE

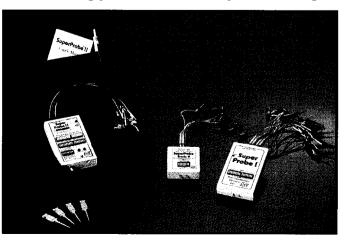

Programmable Designs introduces a family of oscilloscope-triggering devices that provide a wide range of event-triggering options and work with any oscilloscope. With up to four triggering modes, fast input-to-trigger timing, numerous status indicators, and portability, **SuperProbes** are superior to logic analyzers and cost less.

**SuperProbe** II features 18 signal inputs and a clock input. It supports three clock-triggered modes and one combinatorial (pattern match) triggering mode. Flexible logic combinations for specifying trigger events include No-Match triggering for signaling when certain unexpected events occur. The unit has separate "Pattern-Select" and "Don't Care" configuration DIP switches as well as numerous status LEDs for monitoring power, **SuperProbe** I is a pattern-match (or word-recognition] triggering device for a logical combination of up to 17 signals. In microprocessor-based systems, this feature enables triggering on a processor write or read operation to a selected memory or I/O device location. SuperProbe I (standard version) sells for \$249 and includes an interface cable with permanently attached grabbers designed primarily for through-hole component leads. SuperProbe I (deluxe) sells for \$395 and includes a SuperProbe II-like interface cable.

**SuperProbe** Basic-S supports pattern-match triggering with up to eight input signals. The Basic-8 includes a cable with permanently attached through-hole grabbers and is capable of meeting the triggering needs of many

input signals, triggering activity, and clock activity.

SuperProbe II comes with an interface cable that has gold-plated, machined pin contacts designed to fit easily onto IC clips, 0.025" square posts, and the included through-hole or surfacemount component grabbers. SuperProbe II sells for \$649.

basic circuit checkout and debugging applications. SuperProbe Basic-8 sells for \$99.

Programmable Designs, Inc. 41 Enterprise Dr. Ann Arbor, MI 48103 (313) 769-7540 Fax: (313) 769-7242 E-mail: **design@prog**designs.com

#503

# NEW PRODUCT NEWS

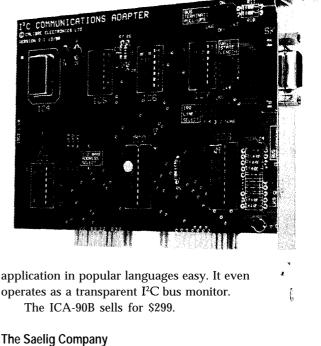

#### **I<sup>2</sup>C** ADAPTER

Saelig is offering a useful tool to save development time for those involved with the  $I^2C$  bus. The  $I^2C$  bus is a two-wire serial bus standard developed by Philips that lets all circuits within a system communicate with each other bidirectionally. It is widely used in television and audio systems and is becoming increasingly common in multiprocessor systems.

Advantages of using  $I^2C$  rather than a parallel architecture include reduced pinout and EMI, simplified wiring and circuit boards, and data rates up to 100 kHz, with communication independent of speed. The bus also offers multimaster capabilities with on-chip collision detection and wire lengths of 12' or more.

The **ICA-90B** kit includes the industry-standard ICA-90 ISA adapter half-card for plugging into your PC, a 3%" disk with an I<sup>2</sup>C function library with many readymade routines in C and TurboBasic, and a helpful I<sup>2</sup>C instruction manual. All I<sup>2</sup>C functions can be controlled through an adaptable library of routines. The ICA-90B demonstrates I<sup>2</sup>C master/slave modes in receiver and transmitter operations. Both polled and interrupt-driven modes are shown, making further programming for your

#504

The Saelig Company 1193 Moseley Rd. • Victor, NY 14564 (716) 425-3753 • Fax: (716) 425-3835

# NEW PRODUCT NEWS

#### **REMOTE PC POWER CONTROL**

Server Technology introduces an upgraded version of Remote Power On/Off, a telephoneactivated power switch for PCs. The new version adds several reboot enhancements to support remote

computing users who leave their PC on continuously.

Features include: No Answer Automatic reboot (any incoming call that is not answered causes the host PC to automatically reboot); Eight-Ring, No-Answer Forced reboot (a reboot is forced if the call is not answered within eight rings); and Infinite Power On feature (a user can call the host PC and turn it on or off).

Also featured are Locked Modem Safeguard (provides a two-hour connect limit to prevent a stuck modem from locking the line) and One Second reboot. Remote Power On/ Off lists for \$169.95. It is also available with **pc**-ANYWHERE for \$199.95. It is fully compatible with standard internal or external modems, comm software, remote-control applications, and Net-Ware. Installation requires three cables, which are provided.

Server Technology, Inc. 1288 Hammerwood Ave. Sunnyvale, CA 94089 (408) 745-0300 Fax: (408) 745-0392 http://www.powerboot.com/

#505

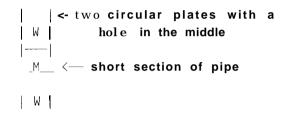

# **STEP MOTOR DRIVER** 8003-DM Step Motor Driver... \$80 302SM Step Motor... \$39"

I/2-step, full-step, remote enable, 3A/phase, 35V max, single supply operation, LED's indicate pwr & motion, TTL, parallel printer port compatible. FREE SOFTWARE for running from Printer Port

• 60 oz-in,12VDC, 200 steps/rev, size 23 (as shown)

# **FEATURES**

12

PLDs from Lattice

In-System-Programmable

Building a Low-Cost **CPLD** Development System

Take Your PIC

36

7th Annual Design Contest Winners

Programmable PLDs from Lattice

In-System-

# FEATURE ARTICLE

Stuart Ball

. pack a lot of logic into a single chip

- · reduce inventory-the same device can be used in different designs by changing the internal programming

- fix bugs without adding wires to the board.

But, for the experimenter or independent designer, PLDs have been something of a problem. While PLD development software is available, the equipment needed to program the devices is expensive. And, unlike EPROMs, the programming specifications for PLDs are not published by the manufacturers, making it difficult to design your own programmer.

Even for the engineer, PLDs have drawbacks. Because the parts have to be programmed, they must be handled twice, increasing the opportunity for damage from electrostatic discharge or other causes. And, if the parts are soldered to the board for better reliability, the flexibility to fix problems by reprogramming them is lost.

Lattice Semiconductor has changed all that. They have a line of PLDs and larger high-density devices that can be programmed in-circuit. In this article, I'll look at these Lattice parts and show how they can be used to produce a useful debugging tool.

#### PLD PRIMER

Imagine that an IC manufacturer has developed a small PLD. The device

While PLDs have been around for many years, Lattice has put a new twist on an old workhorse. With their line of ISP parts, the devices can be programmed without taking them out of the circuit.

fits in an 8-pin miniDIP package. This part has three inputs (on pins 1, 2, and 3) and two outputs (on pins 5 and 6). Figure 1 shows the logic of such a device. Like an actual PLD, the true and complement of each input is available, and the outputs are wrapped back into the fuse array (labeled as columns A-H in Figure 1).

The AND gates represent the product terms of the PLD. Each product term produces the product (logical AND) of any combination of terms in the fuse array. Next, the product terms are summed with the OR gates.

This AND/OR structure is typical of PLDs, and is referred to as a sum-of*products architecture.* In this hypothetical PLD, each output term has two corresponding AND gates and therefore has two product terms. To put it another way, the output can be the OR of any two AND functions.

Let's say you want to program the output at pin 6 to perform the exclusive-OR function of pins 1 and 2. You can write this logically as: Pi n 6 = Pin 1 AND (NOT Pin 2) OR ((NOT Pin 1) AND Pin 2). If you want pin 5 to be high when pin 6 is high and pin 3 is low, you can write: Pin 5 = Pin 6 AND (NOT Pin 3).

To make the PLD perform these functions, you'd have to program fuses in the fuse array to direct the appropriate (true or inverted) inputs to the correct product-term AND gates. The circles in Figure 1 indicate the fuse connections. The topmost AND gate generates the ( Pi n 1 AND (NOT Pin 2)) term, and the second gate decodes the ((NOT Pin 1) AND Pin 2) term. The third gate decodes the term for pin 5. The fourth (lowest) gate is unused.

If you work this out, you'll find that the number of connections required in the fuse matrix equals the number of product terms times the number of input and feedback terms. Actual PLDs have several product terms per output, so even the 16L8 (a relatively simple PLD with 10 inputs, 8 outputs, and 64 product terms) needs an array of 1280 fuses. Most PLDs have additional fuses to control output tristate, registers, and other capabilities.

PLDs come in several flavors. Some have D-type registers at the outputs. On these PLDs, the sum-ofproducts term drives the D input to the flip-flop. Some PLDs have fixed output polarity, some have programmable polarity, and some have a mix of registered and combinatorial outputs.

Early PLDs used bipolar technology and could only be programmed once. This is where the term "fuse" came from, since there was a silicon fuse that blew open when the part was programmed. Newer parts use flash or other memory technology that permits the part to be reprogrammed. Although people still sometimes talk about fuses in these parts, they are really referring to programmable memory cells.

PLDs are used anywhere a logic function can be reduced to a set of sum-of-terms equations. They permit designers to pack several ICs' worth of discrete logic into one chip. Typical

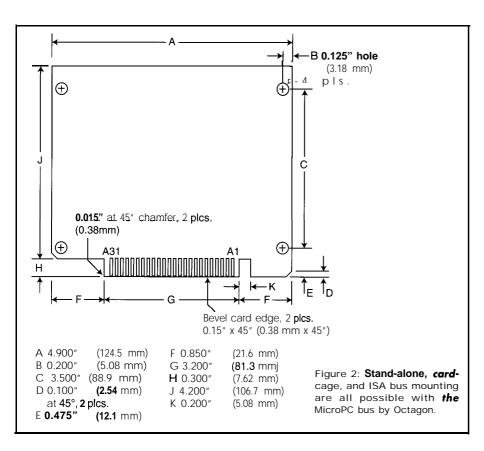

Figure 1—An example of a simple PLD shows how the inputs and outputfeedback lines are combined first through AND gates, then OR gates.

applications include memory-address decoders, small state machines, and random-logic replacement.

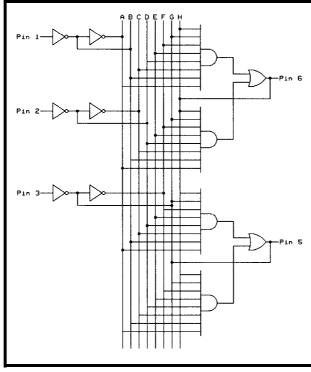

#### THE 22V10

The 22V10 has become one of the most popular PLDs. Figure 2 shows the internal structure of the 22V10, the DIP and PLCC pinouts, and a simplified diagram of the OLMC. Designated the GAL22V10 by Lattice (GAL for Generic Array Logic), it has 12 inputs and 10 outputs. The outputs can be combinatorial or registered and can be tristated to drive a bus.

A global-product term can set or reset all the output registers. Unneeded outputs can be used as inputs. And, while early versions of the 22V10 from some manufacturers were onetime programmable, the Lattice parts can be erased and reused. The productterm array has 132 product-term (AND) gates. Each product-term gate has 44 inputs-one for the true and complement of each input pin and one for the true and complement of each output-feedback term.

Each output is driven by an Output Logic Macrocell (OLMC), as shown in Figure 2. Each OLMC has as inputs a unique sum-of-products term, a tri-

> state-control product term, and the global clock, reset, and preset inputs.

Each OLMC contains a D flip-flop. The D input of the flop is driven by the sum-ofproducts term for that OLMC. The output of each OLMC can be individually programmed to be the true or complement of either the flip-flop output or sum-of-products term. The true and complement of the output is fed back into the product term array, and may be used as a product term itself. If the D flip-flops are used, the clock comes from pin 2 (PLCC, pin 1 on the DIP). All flip-flops are driven by this common clock.

Not all outputs of the 22V10 have the same number of product terms. The product terms for the PLCC pinout are allocated as in Table 1. So, if

you need, say, 15 product terms for a given output pin, you put that function on output pins 21 or 23 since those are the only pins with enough terms.

#### ISPGAL22V10

Even with the flexibility of the 22V10, it has the same drawbacks as any other PLD that is programmed in a programmer. However, Lattice has introduced the ISPGAL22V10 (ISP stands for In-System Programmable), one of a family of parts that can be programmed in-circuit. These parts do

| Pin 17 | 8 terms  | Pin 23 | 16 terms |

|--------|----------|--------|----------|

| Pin 18 | 10 terms | Pin 24 | 14 terms |

| Pin 19 | 12 terms | Pin 25 | 12 terms |

| Pin 20 | 14 terms | Pin 26 | 10 terms |

| Pin 21 | 16 terms | Pin 27 | 8 terms  |

|        |          |        |          |

Table 1—Not all the device outputs support the same number of product terms. Care must be used when defining the outputs that enough terms are available for the intended function. not require a special programmer. ISP parts can be programmed:

- in-circuit

- using a cable from a PC

- using a processor [if one exists) incircuit

- soldered to a board

- using an inline header and a PC cable after the board is stuffed

- . with a special configuration to simplify a factory board-test procedure.

ISP parts make PLDs accessible to the experimenter because they can be programmed without using an expensive programmer. The ISPGAL22V10 is only available as a 28-pin PLCC.

Figure 2 shows the pinout of the PLCC part; it isn't available in a DIP package because Lattice took advantage of the four unused pins of the ordinary GAL22V10 PLCC device to add the ISP capability. These pins (indicated by an asterisk) are used as follows:

- Mode defines the mode of the other ISP pins

- SDI moves serial data into the ISP device

- SDO moves serial data out of the ISP device

- SCLK is the serial data I/O clock.

#### INTERNAL ARCHITECTURE

A complete description of the ISPGAL22V10, including all programming information, takes several pages in the Lattice data book and is not reproduced here. However, here's an overview of the ISPGAL22V10 programming architecture.

Lattice ISP devices contain a bank of internal shift registers. The SDI pin shifts data and commands into the device, and the SDO pin reads data out. The ISPGAL22V10 contains four shift registers: Device ID, Instruction, Data, and Architecture.

The 8-bit Device ID register verifies the device type before programming. The 22V10's device type is 08 The Instruction register is 5 bits long. It allows 10 commands like the following:

- shift data into the Data shift register

- erase the device

- . program the addressed row

- load data from the addressed row for readback

The 138-bit Data register is loaded with the address and data to be programmed. Each programmable cell in the device is numbered and individually programmed. An internal state machine directs data to the proper registers and executes commands loaded into the instruction register.

#### PROGRAMMING ISP DEVICES

If you want to program ISP devices in-circuit using software you have written, you should get the Lattice ISP manual. Fortunately, if you plan to program the parts from a PC, Lattice provides software that makes it easy.

The first step in programming any PLD is getting a JEDEC file. This file

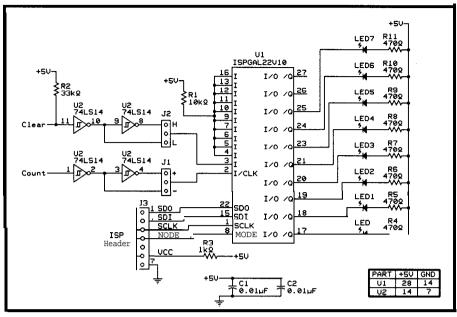

Figure 3-A counter circuit can be made using the ISPGAL22V10.J1 selects c/o&polarity, J2 selects c/ear polarity, and J3 is the ISP programming connector.

informs the PLD programmer which fuses need to be programmed in the chip. The JEDEC file is a standard format, understood by all PLD programmers and Lattice conversion software. Several software packages, including CUPL, ABEL, and PALASM, can produce a JEDEC file from input information. While CUPL and ABEL are somewhat expensive, early versions of PALASM often were provided free by

ENGINEERING PRODUCTIVE EVER HOPING YOU WILL TOO!

Note the provided thousands of college students with industry-quality development tools and information. This program to the time.

Stree 1994, we have provided thousands of college students with industry-quality development tools and information. This program to the time.

Stree 1994, we have provided thousands of college students with industry-quality development tools and information. This program to the time.

Stree 1994, we have provided thousands of college students with industry-quality development tools and information. This program to the time.

Stree 1994, we have provided thousands of college students with industry-quality development tools and information. This program to the time.

Stree 1994, we have provided thousands of college students with industry-quality development tools and information. This program to the time to the tools tools.

Stree 1994, we have provided thousands of college students, we'd like to give you and all of your students free tools tools

Kose Mansella, Circulation Coordinator Circuit Cellar INK 4 Park St. Vernon, CT 06066 Tel: (860) 875-2199 Fax: (860) 872-2204 Internet: rose.mansella@circellar.com MMI (Monolithic Memories Inc.), the company that originated PLD devices. You might be able to find an old copy; version 2.23 was the last MMI version, as far as I know. MMI was bought out by AMD a few years ago, and the new PALASM is no longer free. But it is still inexpensive, and it supports PLDs such as the 22V10.

PLD compilers can take input in several forms. The simplest form is Boolean equations, like those used for

our hypothetical miniPLD earlier but with symbols for the logical functions. For example, PALASM uses \* for AND, and + for OR. CUPL uses & and #, respectively.

Once you have entered and compiled your equations, use the Lattice ISP software to program the parts. For the 22V10, there are two programs:

- JEDTOISP, which converts the JEDEC file to an ISP file

- I22\_PROG, which programs the ISP format file into the device.

A third program, JEDFIX, can be used to make the JEDEC file compatible with JEDTOISP. While standard, the JEDEC file includes header information that can cause problems for JEDTOISP because different PLD compilers produce different headers. JED-FIX strips the header out as you can do with a text editor.

I'll describe the syntax for using these three programs in just a minute. First, let's look at a circuit that makes use of the ISPGAL22V10.

#### THE SUPER LOGIC PROBE

In debugging circuits, I've used everything from a voltmeter to a \$15,000 logic analyzer. One of the most useful techniques I have found to use a counter and an LED bank.

A typical logic probe shows you if a signal is high or low and has a latch to capture state changes. A really good logic probe, like those sold by HP, blinks to show a pulse train. The drawback to these is that you can't always tell how many or how often pulses occur in a group.

The Super Logic Probe consists of an S-bit binary counter driving a bank of LEDs. Each bit of the counter drives an LED, so the LEDs represent the binary count. The counter gets a clock input and a clear input. Three-pin shunt jumpers increment the counter on the rising or falling edges of the clock and reset it when the clear input is high or low.

| Printer<br>conne<br>DB-2<br>Fcn                   | ctor    | • | rcuit<br>ader<br>Fcn                                           |

|---------------------------------------------------|---------|---|----------------------------------------------------------------|

| 'ACK<br>D0<br>D1<br>D2<br>*FLT<br>GND<br>D6<br>PE | 4<br>15 |   | SDO<br>SDI<br>SCLK<br>MODE<br>VCC (sense)<br>GND<br>Port sense |

Figure 4—The cable for in-circuit programming connects the printer port on the PC and the 7-pin header on the circuit board's logic probe.

> The circuit (Figure 3) is implemented with an ISPGAL22V10. The 74LS14s buffer the clock and clear inputs to provide polarity selection and to protect against noisy inputs.

A 7-pin header brings the ISP signals to the 22V10 so it can be programmed. Figure 4 shows the wiring of the cable for programming the board. I use a smaller header than the standard Lattice ISP cable. The other end of the cable plugs into the PC's printer port.

Listing 1 shows the PALASM equations for the logic probe. In addition to using \* for AND and + for OR, the symbol := indicates registered output and = indicates combinatorial output. The C L R input uses the 22V10 global clear function to force all the outputs off.

#### PROGRAMMING THE 22V10

After entering and compiling the equations, the JEDEC file must be created. The command

JEDTOISP COUNTER. JED COUNTER. ISP

**creates** the file **COUNTER. ISP** that contains the ISP programming infor-

FULL TECHNICAL **SUPPORT**...provided over the telephone by our staff. Technical reference &disk including test software & programming examples in Basic, C and assembly are provided with each order.

HIGH **RELIABILITY...**engineered for continuous 24 hour industrial applications with 10 years of proven performance in the energy management field.

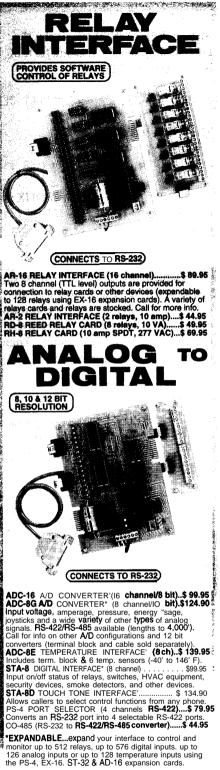

CONNECTS TO RS-232, **RS-422** or **RS-485...**use with IBM and compatibles, Mac and most computers. All standard baud rates and protocols (50 to 19,200 baud). Use our 600 number to order FREE INFORMATION PACKET. Technical information (614) 464-4470.

24 HOUR ORDER LINE (800) 842-7714 Visa-Mastercard-American Express-COD

International & Domestic FAX (614) 464-9656 Use for information, technical support&orders.

ELECTRONIC ENERGY CONTROL, INC. 360 South Fifth Street, Suite 604 Columbus, Ohio 43215-5438

ື #110

**INK<sup>®</sup>**

mation. If JEDTOISP rejects the JE-DEC format, modify it using JEDFIX before running JEDTOISP:

JEDFIX COUNTER. JED >FIXCOUNT.JED

Then run JEDTOISP this way:

JEDTOISP FIXCOUNT.JED COUNTER. ISP

An alternative to using JEDFIX is to delete everything in the JEDEC file up to the ctrl-B character with a text editor. Ctrl-B usually shows up as a happy face symbol.

To program the 22V10, connect power and ground to the counter circuit, and connect the ISP programming cable to the PC's printer port and the counter circuit's ISP connector. Then, use the following command:

I22\_PROG COUNTER. ISP 0

The 0 specifies which printer port to use. For a printer port other than LPTO, replace 0 with the appropriate number.

Listing 1-PALASM equations for the logic probe. ; Pin definition (PLCC pinout)  $\cdot$  PIN 2 3 4 5 6 7 9 10 11 12 13 14 CLK CLR NC NC NC NC NC NC NC NC GND PIN 16 17 18 19 20 21 23 24 25 26 27 28 NC /00 /01 /02 /03 /04 /05 /06 /07 NC NC VCC GLOBAL : Pin descriptions: CLK: Input clock CLR: **Clears** 00-07 ; Q0-Q7: An 8-bit binary counter. The outputs are true LOW, so a true output turns the LED on. EQUATI ONS ; Note that PALASM uses \* for logical AND, ;+ for logical OR, = for combinatorial outputs. ; and := for registered outputs. / indicates negation. GLOBAL.RSTF = CLR00 := /0001 := 00 \* /01+ 01 \* /00 Q2 := Q0 \* Q1 \* /Q2 + 02 \* /00 + 02 \* /0103 := 00 \* 01 \* 02 \* /03+ **Q3** \* /Q0 + **Q3** \* /Q1 + Q3 \* /Q2

(continued)

#111

Listing 1-continued

$\begin{array}{rcl} \mathbf{Q4} & := & 00 \ * \ 01 \ * \ 02 \ * \ \mathbf{Q3} \ * \ / 04 \\ & + & 04 \ * \ / 00 \ + \ \mathbf{Q4} \ * \ / 01 \ + \ \mathbf{Q4} \ * \ / 02 \ + \ \mathbf{Q4} \ * \ / 03 \end{array}$   $\begin{array}{rcl} \mathbf{Q5} & := & \mathbf{Q0} \ * \ 01 \ * \ 02 \ * \ 03 \ * \ \mathbf{Q4} \ * \ / 05 \\ & + \ \mathbf{Q5} \ * \ / 00 \ + \ 05 \ * \ / 01 \ + \ \mathbf{Q5} \ * \ / 02 \ + \ \mathbf{Q5} \ * \ / 03 \ + \ 05 \ * \ / 04 \end{array}$   $\begin{array}{rcl} \mathbf{Q6} & := & 00 \ * \ 01 \ * \ 02 \ * \ 03 \ * \ \mathbf{Q4} \ * \ \mathbf{Q5} \ * \ / 06 \\ & + \ \mathbf{Q6} \ * \ / 00 \ + \ 06 \ * \ / 01 \ + \ \mathbf{Q6} \ * \ / 02 \\ & + \ \mathbf{Q6} \ * \ / 03 \ + \ \mathbf{Q6} \ * \ / 04 \ * \ \mathbf{Q6} \ * \ / 06 \\ & + \ \mathbf{Q6} \ * \ / 03 \ + \ \mathbf{Q6} \ * \ / 04 \ * \ \mathbf{Q6} \ * \ / 06 \\ & + \ \mathbf{Q6} \ * \ / 03 \ + \ \mathbf{Q6} \ * \ / 04 \ * \ \mathbf{Q6} \ * \ / 06 \\ & + \ \mathbf{Q6} \ * \ / 03 \ + \ \mathbf{Q6} \ * \ / 04 \ * \ \mathbf{Q6} \ * \ / 06 \\ & + \ \mathbf{Q6} \ * \ / 03 \ + \ \mathbf{Q6} \ * \ / 04 \ * \ \mathbf{Q6} \ * \ / 06 \\ & + \ \mathbf{Q7} \ * \ / 04 \ + \ \mathbf{Q7} \ * \ / 05 \ * \ 06 \ * \ / 07 \\ & + \ \mathbf{Q7} \ * \ / 03 \ + \ \mathbf{Q7} \ * \ / 04 \ * \ \mathbf{Q7} \ * \ / 05 \ * \ \mathbf{Q7} \ * \ / 06 \end{array}$

I22\_PROG programs and verifies the device. If errors occur, it tells you. If the circuit won't program, first check the wiring of the ISP pins and the ISP cable. It may also be that the cable is too long, causing noise problems with the 22V10. Try to keep it under 3'.

#### TESTING AND USE

The simplest test you can perform is to jumper the clear input to be low true and the clock to be positive edge. The 33-k $\Omega$  pull-up resistor on the clear input ensures that it stays high if the wire is unconnected. Touch the clock input to ground. The contact bounce increments the counter and LEDs several counts. Touch the clear wire to ground, and the LEDs all go out.

You can perform a more exhaustive test by connecting a slow signal source to the clock input. If the signal source is slow enough (around 2 Hz), you can see each LED change and verify that the count increments in a binary fashion.

The uses for this circuit are many. I've used one to count the steps going to a stepper motor, the encoder pulses from a servo motor, and even the number of instructions that a balky microprocessor managed to execute before it died.

Since the 22V10 is reprogrammable, you can modify the counter as needed. For example, you could connect one of the unused inputs so it enables and disables counting without clearing the counter. Or, you could wire the inputs to decode a port address from a microprocessor, and count the number of times that port is accessed.

#### PROGRAMMING

The ISPGAL22V10 need not be programmed from a PC. Inputs can come from a microprocessor in the target circuit. This technique allows the 22V10 function to be changed at powerup, for example, when the microprocessor detects whether a particular option is installed.

While Lattice supplies details in the data book that tell how to do this, they also supply C source code so you don't have to write it all yourself. Lattice sells starter kits that include an ISPGAL22V10, a programming cable, and the appropriate programs. The programs themselves are also available on the Lattice ISP BBS. The filesneededare ISP22V10.ZIP and JEDFIX.ZIP,butchecktoseeifthere are later versions loaded with different names.

If you use the Lattice starter kit, wire your ISP header to match their cable. The diagram of the Lattice cable is included with the kit.

#### OTHER ISP DEVICES

In addition to the 22V10, Lattice makes a number of other ISP devices, including a line of high-density parts. I've used their ispLSI1016 in a number of designs. This part has 2000 gates, 96 D-type flip-flops, and 32 I/O pins. Unlike ordinary PLDs, these larger devices don't have a fixed number of product terms per output. Instead, they have a global-routing pool, an array of product terms allocated by special software to implement the required functionality.

Creating a design for one of these parts is typically a two-step process. First, the PLD compiler is run to create an intermediate file. Then, a fitter program from Lattice is run. The fitter reads the intermediate file produced by the PLD compiler and allocates the resources on the chip, producing a JEDEC file. Lattice provides DDOWN-LD, a download program for the large devices. Lattice also has a complete development system that does not depend on third-party compilers.

High-density logic devices are available in both ISP and nonISP versions. The nonISP parts are a little less expensive, so I put those on the manufacturing bill of materials. But, I keep a tube of ISP parts in my desk drawer for engineering prototypes.

#### WRAPPING UP

The Lattice ISP product line solves many of the problems you may have encountered in current PLDs, putting them within the reach of any designer. You, too, can use PLDs to create more innovative circuits than you did before, thanks to Lattice ISP products.

Stuart Ball has spent the last 15 years working on systems as diverse as Global Positioning Systems and single-chip interface translators. He is currently employed as a principal engineer at BancTec Technologies, a manufacturer of document-processing equipment for the banking industry. He may be reached at (405) 354-5042.

#### SOURCE

GAL22V10, ISPGAL22V10 Lattice Semiconductor Corp. 5555 NE Moore Ct. Hillsboro, OR 97124 (503) 681-0118 Fax: (503) 681-3037 BBS: (503) 693-0215

#### IRS

401 Very Useful402 Moderately Useful403 Not Useful

# FEATURE ARTICLE

David Van den Bout

# Building a Low-Cost CPLD Development System

Unlike Steve, David prefers software. You can easily fix errors, document through variables, and reuse modules. Hence, the CPLD fits his bill. He shows us how to build a complete CPLD development system. often design circuits, but I never seem to get around to building them! Searching for a breadboard, finding the right chips, cutting wires, and making sure they get in the correct holes takes the fun out of a project.

Then, once it's built, I have to transfer it to a soldered prototyping board to make room for another project. Next, I need to document it so I can fix it if it breaks. And, I have to build another complete copy of the circuit if I want to use it as a part of another project....

Software seems so much easier! I write subroutines and test them with a debugger. If 1 find errors, a little editing gets rid of them. If I choose reasonable variable and function names, most of the documentation gets done automatically. 1 can use each subroutine as many times as I want. I can even give copies to other people over the Internet or on diskettes.

That's why I enthusiastically greeted the appearance of complex programmable logic devices (CPLDs) and field-programmable gate arrays (FPGAs) in the mid 1980s. CPLDs and FPGAs make building hardware look like writing software.

CPLDs and FPGAs contain thousands of logic gates that can be rewired by reprogramming their internal memory. If I want to build a UART, I just write the truth tables or Boolean equations using a hardware description language (HDL), put them in a file, compile it, and download it into a CPLD chip. If I decide I'd rather have a microprocessor, I can change the programming and build one.

It wasn't that easy at first. Early CPLDs and FPGAs didn't contain many logic gates and cost hundreds of dollars each. Worse, the programming software cost thousands!

Luckily, things have changed. Today, you can buy CPLDs and FPGAs with up to 10,000 reconfigurable logic gates for less than \$100, and some of the programming software is free!

In this article, I'll show you how to build a simple but complete CPLD development system for just \$120. But first, let's take a look at the basics.

#### WHAT ARE CPLDS?

In the beginning [OK, in the '60s], there was discrete logic. Systems were built from lots of individual chips with a spaghetti-like maze of wiring between them.

Such systems were difficult to modify after you built them. In fact, after a week or two it was difficult to remember what each chip was for! Manufacturing the systems took a lot of time. Each design change meant rewiring, which usually meant building a new printed circuit board.

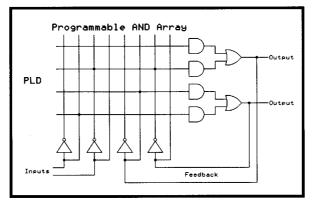

The chip makers solved this problem by placing an unconnected array of AND-OR gates in a single chip called a programmable logic device (PLD). You could program a PLD with a set of Boolean sum-of-product equations so it would perform the logic functions needed in your system. The ability to internally rewire PLDs lessened the need to redo the circuit board if a design change occurred.

Simple PLDs such as the one shown in Figure 1 only handle IO-20 logic equations, so you can't fit a large logic design into just one. You have to figure out how to break larger designs apart and fit them into a set of PLDs. This process is time-consuming and means you have to interconnect the PLDs with wires. The wires were a big no-no. Eventually, you made a design change that couldn't be handled just by reprogramming the PLDs, and you had to build a new circuit board.

Again, the chip makers came to the rescue by building much larger programmable chips called *complex programmable logic devices* (CPLDs). With these, you could essentially get a complete system onto a single chip.

A CPLD contains several PLD blocks whose inputs and outputs are connected by a global interconnection matrix. Thus, a CPLD has two levels of programmability. Each PLD block can be programmed as can the interconnections between the PLDs.

**Figure 1—***A simple PLD allows the connection of any input or output in any combination to the AND/OR logic.*

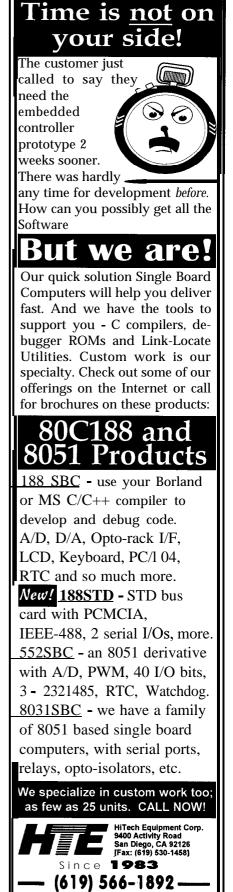

The EPX780 CPLD shown in Figure 2 is a good example of a CPLD. It contains eight configurable function blocks (CFBs) which are essentially 24V10 PLDs with 24 inputs and 10 outputs. Any output from any CFB can be connected to any input of any CFB through the global interconnection matrix. Most CFB outputs are accessible externally, but not all of them due to the limitations of the 84-pin PLCC package.

CPLD manufacturers make connections within and between PLD blocks several ways. Some make chips with fuses or antifuses that are programmed by passing a large current through them. These CPLDs and FPGAs are one-

time programmable (OTP); you can't rewire them internally if the fuses blow.

Other manufacturers make the connections using pass transistors. A charge, stored on the transistors' gate

electrodes with a highvoltage pulse, opens and closes them. This type of programmable device resembles an E(E)PROM. A special programmer erases or programs the chip before you place it in your circuit. That's fine, unless you have the CPLD or FPGA soldered into a circuit board and then decide you want to change it.

Finally, some manufacturers use static RAM bits to control the pass transistors for each interconnection. By loading a RAM bit with a 1 or 0. you control whether the switch is closed or open and therefore whether two logic elements are connected. You can reprogram CPLDs built with RAM switches without removing them from a circuit board. They are said to be in-circuit reconfigurable or in-circuit programmable. The EPX-780 CPLD falls into this category.

Regardless of the interconnection method, you can see that it would

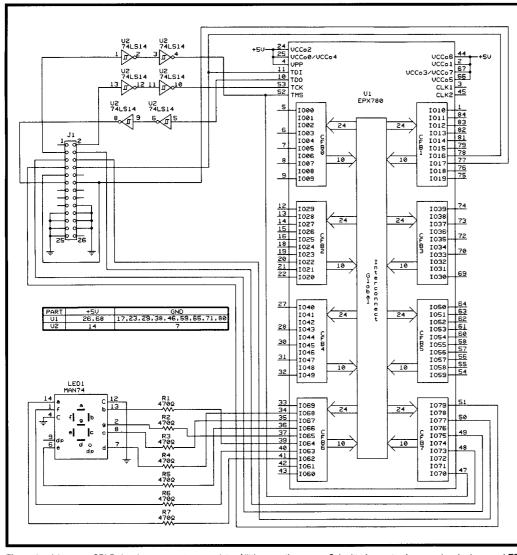

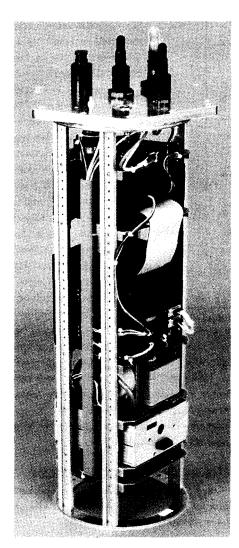

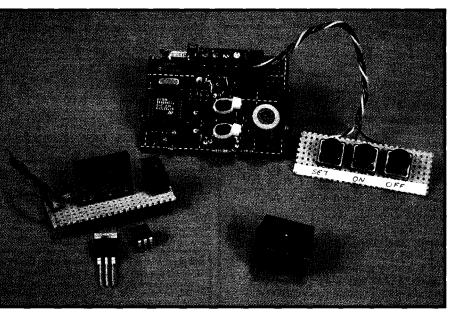

Figure 2—A low-cost CPLD development system consists of little more than some Schmitt triggers to clean up signal edges, an LED display for diagnostics, and a connector.

Circuit Cellar INK<sup>®</sup> Issue #65 December 1995 21

be quite a chore figuring out which switches to open and close to create a logic circuit. That's why the chip manufacturers provide *device fitters*.

These programs take a description of your logic design as input, compile it, and output a binary file that's downloaded into a CPLD so it acts like your design. Some device fit-

ters compile logic circuits directly from a schematic editor. Other device fitters require you to describe your logic circuit using an HDL like PAL-**ASM** or ABEL.

When choosing a CPLD, consider both the cost of the CPLD chip and of the programming software and hardware. For most people experimenting with CPLDs, the cost of the actual

chip is incidental to the thousands of dollars the programming software costs.

The EPX780 CPLD is a notable exception; its programming software is free of charge. Also, the EPX780 can be programmed by simply connecting it to a PC's printer port, so no expensive programming hardware is needed. And, since the EPX780 stores its configuration in RAM, you can use the same chip on many projects.

#### CPLD ASSEMBLY

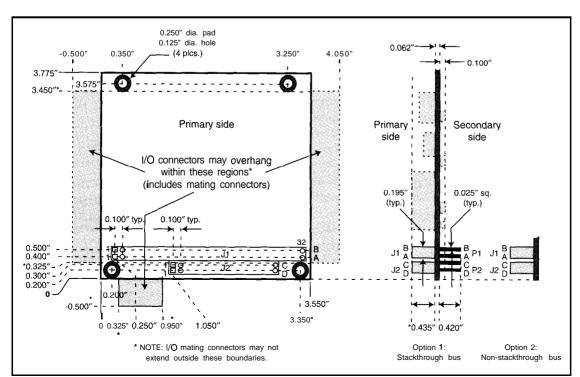

Any CPLD development system must allow you to:

- download new logic designs into the CPLD

- test the functions of the downloaded designs

- connect the CPLD to other components.

In the EPX780-based development system I describe here, all programming is done through the 4-pin JTAG port (consisting of the TCK, TMS, TDI, and TDO pins). You can control programming easily and cheaply by using the printer port of a PC. You can also use the printer port to apply low-

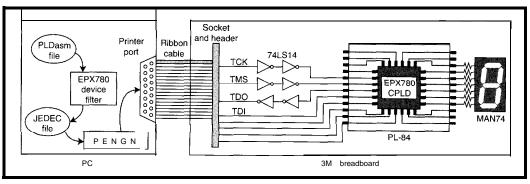

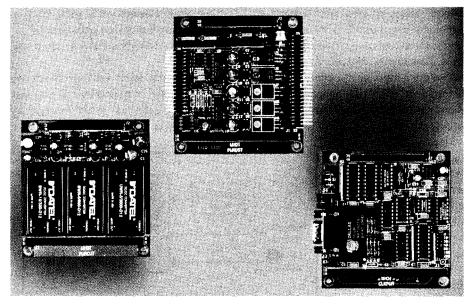

Figure 3- The development system minimizes the hardware necessary by relying heavily on PC-based software.

speed logic levels to some of the EPX-780's pins for debugging. A 7-segment LED digit provides visual feedback on CPLD functioning. By building the entire development system on a breadboard, you can change it easily, connecting other chips or components for various projects.

Figure 3 illustrates the basic system. The PLDshell software and pro-

| DOS/4GW Protected Mode Run-time Version 1.92                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INFO PENGN: Interpreting file: fx780.ap1                                                                                                                   |

| Target Device ID = 10621020h<br>Device Status Reg = 00001b OK                                                                                              |

| Reading from FX780's SRAM         1       1         11:       11:         21:       11:         31:       11:         51:       11:         54:       Done |

| Writing       JEDEC       test.jed         0:                                                                                                              |

Figure 4-The PENGN CPU-downloading program provides basic operational feedback.

> gramming manual can be obtained at no cost from Altera, while on-line software is available from XESS. The software provides a device fitter that generates a JEDEC file for the EPX780 based on:

truth tables

' Boolean equations

• state-transition statements that you provide using the PLDasm HDL.

The PENGN downloader program converts the JEDEC file into a configuration bitstream and sends it out through the PC printer port. A 25 -pin male D-subminiature connector, 26wire cable, 26-pin socket, and a 26-pin header carry the JEDEC bitstream to a

3M breadboard that holds the development system hard-ware.

From the header, the clocking signal for the bitstream (TCK) passes through two 74LS14 Schmitt-trigger inverters to prevent erroneous pulses brought on by slow signal transitions on the printer port.

The TMS signal, which controls the state of the EPX-780 downloading process, and the TDO signal, which carries status information back to the PC, are also buffered. The TDI signal that carries the actual circuit configuration information from the PC to the '780 doesn't need to be buffered. From the 74LS14, the bitstream is sent to the EPX780.

The other printer port outputs are attached to the EPX780's general-purpose I/O

pins so you can apply test signals. An adapter socket matches the 84-pin PLCC of the EPX780 to the 0.1" pin spacing of the breadboard. A 7-segment LED attached to the CPLD's seven general-purpose I/O pins provides feedback during design debugging.

Current-limiting resistors prevent overloading of the CPLD outputs.

Some electrolytic and nonpolarized bypass capacitors are sprinkled around to prevent noise from interfering with the system. The details of the wiring on the breadboard can be seen in Figure 2.

You should notice several details in the wiring. First of all, the printer port pins that carry the TMS and TDI signals during CPLD downloading also apply signals to the general-purpose I/O pins during debugging. This arrangement is permissible since arbitrary values on these pins cannot send the EPX780 back into the downloading mode.

However, the printer port pin carrying the TCK signal cannot be used during debugging because pulses on this output may cause the EPX780 to return to downloading mode and erase the design being tested. So, you can use only seven of the eight printerport outputs to apply inputs to the EPX780.

Also, never create a design that uses pins 47, 48, 49, 50, 51, 77, or 78 as outputs. These outputs might conflict with printer-port outputs.

Second, pins 9 and 12 of the printer port must be shorted together. The PENGN software uses this connection to test for the attachment of the downloading cable to the printer port. Pin 9 can apply test signals during design debugging because PENGN is not active at that time.

Third, note that pin 26 of the 2 x **13** header is left unconnected since the printer port only has 25 pins. Pin 1 of the header connects to pin 1 of the printer port, pin 2 to pin 2, and so on. A straight run of 26-wire flat cable between the male D-subminiature connector and the 26-pin socket, which mates to the 26-pin header, should ensure this.

You've now wired the breadboard, attached the printer-port-downloading cable between the printer port and the breadboard, and connected a 5-V power supply to the breadboard. It's time to test your system.

#### **TESTING THE SYSTEM**

Let's assume you installed PLDshell on the C: drive of your PC in a directory called P L  $\bigcirc$  S H E L L and put it Listing 1—The PLDasm code for a simple PLD circuit decodes a 4-bit number into seven signals that drive a7-segment LED display.

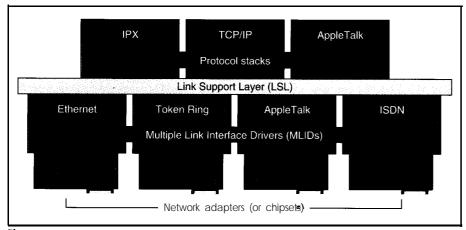

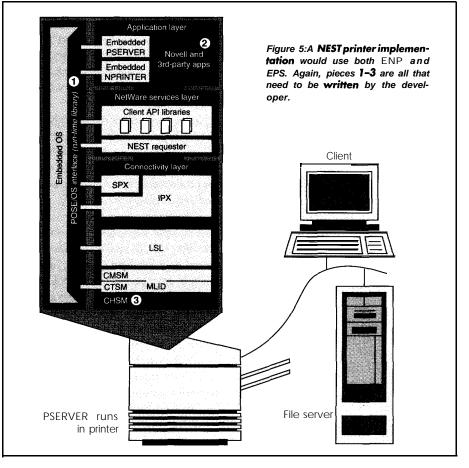

| CHI P                                                                                 | l edde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ecod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IFX780_84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |