# BEREICATIONS JOURNAL

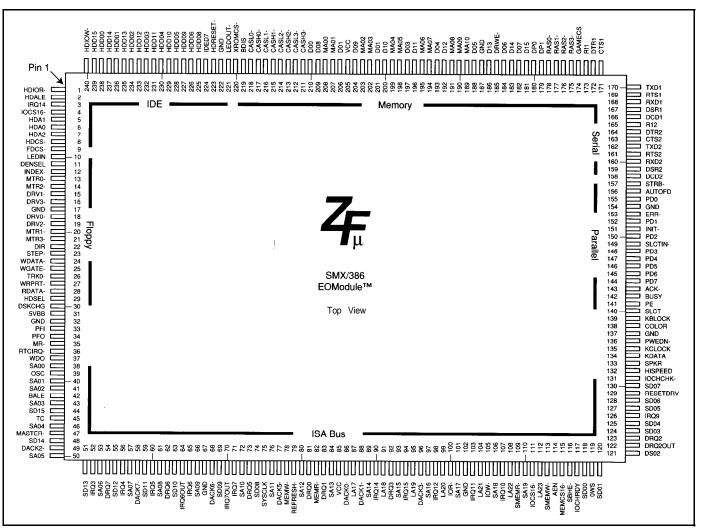

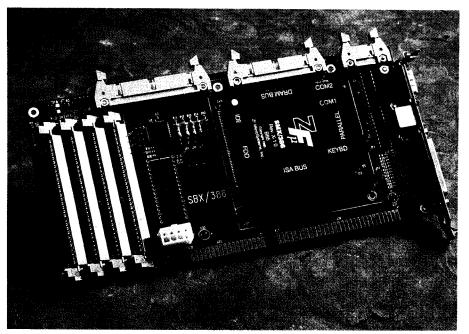

# #69 APRIL 1996 COMMUNICATIONS

Caller ID Fundamentals

Networking Inside an Automobile

**Embedding the SPARC**

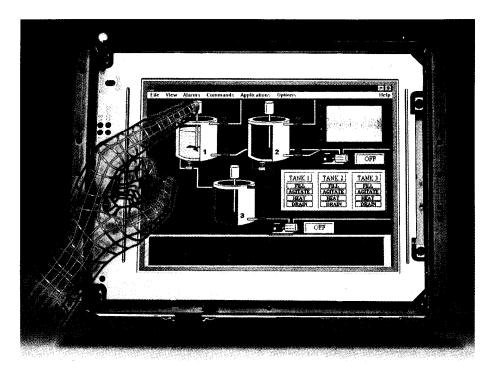

EPC: Designing PCs for Harsh Environments

# **ASK MANAGER**

### **Political Arachnids**

ith the campaign season firmly upon us, I just finished perusing several Republican candidate Web sites, looking for someone to vote for in the primaries tomorrow. While the traditional candidate's communications media have been TV and radio spots, it's interesting to see what they're doing with the newest mass communications medium: the World Wide Web.

You might think a Web site to be a convenient cross between the guick sound bites of a TV commercial and the more in-depth coverage of a print medium. What I found was an interesting range of coverage spanning the two.

I'm not really interested in a candidate's life history or pictures of his family (though you'll certainly find both). Tell me where you stand on the issues. Several of the sites made it easy to find out where the sponsor stood. Others were nothing more than feel-good extended television commercials with very little hard content. While the negative campaigning that has dominated television these days was minimal, it was still there on a few sites.

I shouldn't be surprised at what I found, but I was hoping for more. A Web site should afford the user the chance to do some in-depth research into the candidates. The textual nature of the medium allows the campaign ample room to discuss as much as they like without paying a lot. The graphical nature also enables them to make it attractive. Such a mix was, unfortunately, the exception rather than the rule.

Switching from political to technical communications, we start with a look at how the SPARC processor can be used in telco applications. Next, we take a quick look at how Caller ID works and is decoded. Moving from telephone communications to intravehicle communications, the next article gives an introduction to the latest in networking technologies used in today's (and tomorrow's) automobiles.

On the subject of software communications, we present a technique to allow tasks within a multitasking system to more effectively exchange information while making the code more reusable. Wrapping up our feature section is an article and a pair of sidebars that present some new SPARCcompatible processors designed specifically for embedded applications.

In our columns, Ed reveals the mysteries behind memory caches, Jeff uses some colorful language when describing the newest in the world of LEDs, and Tom presents the latest contender in his PID-Pong challenge.

In Embedded PC, we start with a look at a new technology: a complete PC in a module. Next, we explore the issues related to designing embedded PCs for use in harsh environments. In PC/104 Quarter, Rick overviews what's available for developing software for use on PC/104 processor boards. Finally, Russ concludes his reign in Applied PCs by looking at what's available for packaging embedded PCs for different environments.

R THE COMPUTER APPLICATIONS JOURNAL

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

**EDITOR-IN-CHIEF** Ken Davidson

EPC MANAGING EDITOR Janice Marinelli

**TECHNICAL EDITOR** Carole Boster

ENGINEERING STAFF Jeff Bachiochi & Ed Nisley

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Rick Lehrbaum Russ Reiss

**NEW PRODUCTS EDITOR** Harv Weiner

ART DIRECTOR Lisa Ferry

**PRODUCTION STAFF** John Gorsky James Soussounis

CONTRIBUTORS: Jon Elson Tim McDonough Frank Kuechmann Pellervo Kaskinen

PUBLISHER **Daniel Rodrigues**

PUBLISHER'S ASSISTANT Sue Hodae

**CIRCULATION MANAGER** Rose Mansella

**CIRCULATION ASSISTANT** Barbara Maleski

CIRCULATION CONSULTANT Gregory Spitzfaden

> **BUSINESS MANAGER** Jeannette Walters

ADVERTISING COORDINATOR Dan Gorsky

CIRCUIT CELLAR INK®, THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751, Second class postage paid at Vernon, CT and additional offices One-year (12 issues) subscription rate U.S.A. and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank. Direct subscription orders. and subscription related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

POSTMASTER: Please send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613

Cover photography by Barbara Swenson PRINTED IN THE UNITED STATES

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

#### HAJAR ASSOCIATES NATIONAL ADVERTISING REPRESENTATIVES

| NORTHEAST &<br>MID-ATLANTIC | SOUTHEAST<br>Christa Collins |  |

|-----------------------------|------------------------------|--|

| Barbara Best                | (305) 966-3939               |  |

| (908) 741-7744              | Fax: (305) 985-8457          |  |

| Fax: (908) 741-6823         |                              |  |

MIDWEST WEST COAST Nanette Traetow (708) 357-0010 Fax: (708) 357-0452

Barbara Jones & Shelley Rainey (714) 540-3554 Fax: (714) 540-7103

Circuit Cellar BBS-24 Hrs. 300/1200/2400/9600/14.4k bps, 8 bits, no parity, 1 stop bit, (860) 871-1988; 2400/ 9600 bps Courier HST, (860) 871-0549. World Wide Web: http://www.circellar.com/

All programs and schematics in Circuit Cellar INK® have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK®.

Entire contents copyright © 1996 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited

editor@circellar.com

| 1                              | 2      | SPA<br>by 1                                                                                                              | ARC Telco Applications<br>Richard Pedreau                                                  |                                                          |  |  |  |

|--------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| 1                              | 8      |                                                                                                                          | ler ID Fundamentals<br>Richard Newman                                                      |                                                          |  |  |  |

| 2                              | 2      | Vehicular Control Multiplexing with CAN and J1850<br>Part 1: Vehicular Multiplexing Fundamentals<br>by Willard Dickerson |                                                                                            |                                                          |  |  |  |

| 2                              | 8      | Par                                                                                                                      | Embedded Sun<br>t 1: Introduction to the Hardwar<br>Anindya Ray & Lee Hanson               | re                                                       |  |  |  |

|                                |        | DSP in RISC Embedded Processors<br>by Richard Pedreau                                                                    |                                                                                            |                                                          |  |  |  |

|                                |        |                                                                                                                          | tsu's SPARClite Alternatives<br>John Burns                                                 |                                                          |  |  |  |

| 3                              | 8      |                                                                                                                          | oedding a Message-based System<br>Pat Baird                                                |                                                          |  |  |  |

| 7                              | 8      |                                                                                                                          | <b>Firmware Furnace<br/>80x86 Performance</b><br>Cache Craziness Redux<br><i>Ed Nisley</i> | EMBEDDED PC                                              |  |  |  |

| 8                              | 4      |                                                                                                                          | <b>From the Bench</b><br>LEDs Finally Fill the Rainbow<br><i>Jeff <b>Bachiochi</b></i>     | see Pages 43–77 for our                                  |  |  |  |

| 9                              | 0      |                                                                                                                          | <b>Silicon Update</b><br>Fuzzy PID-Pong<br><b>Tom Can</b> trell                            | Special Bonus Section                                    |  |  |  |

|                                |        |                                                                                                                          | TNS                                                                                        |                                                          |  |  |  |

| Task Ma<br>Ken Dav<br>Politica | /idson | nide                                                                                                                     | TOO                                                                                        | ConnecTime 98<br>Excerpts from<br>the Circuit Cellar BBS |  |  |  |

| Reader                         |        | nius                                                                                                                     |                                                                                            | conducted by<br>Ken Davidson                             |  |  |  |

| Letters t                      |        | ditor                                                                                                                    |                                                                                            | Priority Interrupt 112                                   |  |  |  |

| New Pro                        |        |                                                                                                                          |                                                                                            | Not Just<br>Ferengi Values                               |  |  |  |

| Suncu D                        | יישרא  |                                                                                                                          |                                                                                            | Advertiser's Index 81                                    |  |  |  |

|                                |        |                                                                                                                          |                                                                                            |                                                          |  |  |  |

# **READER I/O**

#### FREEDOM OF SPEECH

Steve's *INK 67* editorial reminded me of the astuteness of a tagline I saw recently: "Law is not always just, and justice is not always legal."

Since this issue went to press, I'm sure you've heard the brouhaha over the book *Hit Man.* I'm not in favor of murder for hire. But, I am incensed that some would deny me the right to obtain the knowledge of how to do it! Right now, the author is a pariah because his book was seemingly used as instruction for an actual murder.

But, if circumstances were different...say, for instance, that a foreign power took over our government and the book was used for a successful assassination of the usurpers; the author would be a hero.

Context is all. My right to know should not be taken away just because someone used that knowledge to do evil.

I was surfing the Internet the other day and managed to land on a Web page sponsored by legitimate, honestto-God (pardon the pun) Satanists. I investigated, and when I found out that it was too wickedly serious for my taste and sensibilities, you know what I did? I refused to investigate further, got out, and left it behind.

In my opinion, that was censorship at its finest. Heck, I'm not even an elderly grandmother, and what I saw shocked me (but I do have breasts). I defined it as obscene. I had the freedom of choice and I exercised it, as I do every day.

You are so right that "unless we collectively head off the dim-witted thinking that government intervention and censorship are tools to preserve a free society, we are destined to lose a society and freedom worth preserving." I can decide for myself, thank you, and I can train up my children (well, he is grown now, but I did my best) in the way they should go. I don't need Big Brother's help.

Too bad I have to go to work and am rushed or I could have written you a letter worthy of another editorial. I just wanted you to know that "It Just Frosts My Chops" was greatly appreciated.

#### Pat Shields

via the Internet

#### **LETTERS** TO LETTERS

I would like to reply to a letter in *INK 67* from Jim Chaney regarding the Engine-Control System series (*INK 62-64*).

Mr. Chaney wrote, "Although Ed's two-coil ignition system is fine for drag racing, for a street application,

the increased plug wear over a four-coil system would be unacceptable. There's a need for a feedback of resistance at the spark plugs during various RPMs and load, which should also provide cylinder pressure calculations."

Buick has been using a distributorless ignition system with two cylinders per coil since the mid '80s. Spark plug wear was actually less in my Buick GN (turbocharged V6) than previous cars with traditional distributors. Now, practically all manufacturers use a similar system.

About measuring plug resistance, Chrysler uses a two-coil DIS system in the four-cylinder Neon. With the advent of OBD\_II regulations, monitoring the plug resistance was required for misfire detection. The waste spark system has a negligible amount of resistance from the plug not under load. So, total secondary resistance is dominated by the actively firing (compression stroke) plug. The waste spark helps emissions, as the extra spark on the exhaust stroke can ignite the remaining hydrocarbons.

Keep up the good work, *INK*!

Dave Cooley Wendell, NC

#### **Contacting Circuit Cellar**

We at Circuit Cellar *INK* encourage communication between our readers and our staff, **so** have made every effort to make contacting us easy. We prefer electronic communications, but feel free to use any of the following:

Mail: Letters to the Editor may be sent to: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066.

Phone: Direct all subscription inquiries to (800) 269-6301. Contact our editorial offices at (860) 8752199.

Fax: All faxes may be sent to (860) 872-2204.

- **BBS:** All of our editors and regular authors frequent the Circuit Cellar BBS and are available to answer questions. Call (860) 871-1988 with your modem (300–14.4k bps, 8N1).

- Internet: Letters to the editor may be sent to **editor@circellar.** corn. Send new subscription orders, renewals, and address changes to **subscribe@circellar.com**. Be sure to include your complete mailing address and return E-mail address in all correspondence. Author E-mail addresses (when available) may be found at the end of each article. For more information, send E-mail to **info@circellar. corn.**

WWW: Point your browser to http://www.circellar.com/. FTP: Files are available at ftp://ftp.circellar.com/pub/circellar/.

#### NEW PRODUCT NEWS Edited by Harv Weiner

#### ADD-ON SERIAL PORT FOR SBC

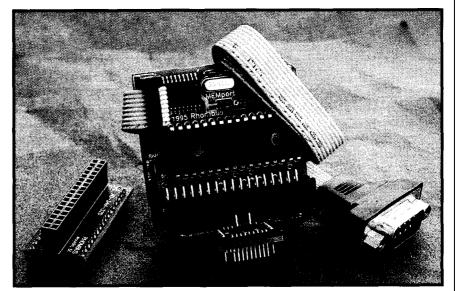

memPORT provides that extra serial port so often needed for debugging single-board computers during program development or on site. Prior to memPORT, developers had to temporarily relinquish a port or build an extra port into every product.

The 2" x 1.8" memPORT PC board is installed through an adapter into a 28- or 32-pin DIP or 32-pin PLCC memory socket. It contains a buffered UART, RS-232 level conversion, memory-mapping logic, and a DIP memory-replacement socket. Through the replacement socket, the system continues to use the dis-

placed memory IC, except for a small block of eight bytewide addresses.

In return, the system gains a memory-mapped RS-232 serial port with full-duplex operation at up to 115.2 kbps, double-buffer transmit, and a quadruple-buffer receive. Power, typically 35mA over and above that needed by the memory IC, is taken from the memory socket.

A flat cable assembly makes the transition from memPORT's10-pin header to an AT-compatible DE-9 connector. Software guidelines are included for setting up the UART and for typical polled transfer routines. If the user's software-development program can't be customized, the port can be used for the application itself.

memPORT comes complete with transition cable for \$139. Memory socket adapters are available as a DIP for \$25 or as an economy PLCC version for \$30.

#### Rhombus

P.O. Box 871 • Mauldin, SC 29662 • (803) 676-0012 • Fax: (803) 676-0015

#500

#### LOW-TEMPERATURE SENSOR

The M2020 NTC Thermistor replaces traditional electromechanical devices with an electronic component that provides more sensitive temperature regulation. When the M2020 is used with a microprocessor interface, actual temperatures can be displayed. The sensor was designed specifically for refrigerators and freezers.

Encapsulated in a molded plastic case, the M2020 withstands harsh temperature conditions. Under test conditions of 1,000 h at room temperature in water, the change in the resistance value is less than 1%. The M2020 also achieves fast temperature cycling. At temperatures changing 100 times from  $-40^{\circ}$ C to  $+60^{\circ}$ C, the change in resistance is less than 1%.

Siemens Components, Inc. 186 Wood Ave. S. • Iselin, NJ 08830 (908) 906-4300 • Fax: (908) 632-2830

# NEW PRODUCT NEWS

#### LOW-COST DAC

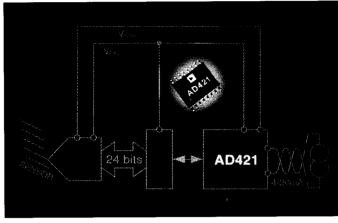

To control a variety of digital-processing functions, the AD421 looppowered D/A converter sends 4–20-mA signals to a microcontroller. It offers a zero-scale 4-mA output current with  $\pm$ 0.1% offset error and a 20-mA full-scale output current with  $\pm$ 0.2% gain error. Full-scale settling time to  $\pm$ 0.1% occurs within 5 ms.

The DAC is a highprecision, fully integrated, low-cost solution housed in a 16-pin package. It includes an Onboard voltage regulator which provides +5-, +3.3-, or +3-V outputs as well as onboard+1.25- and

+2.5-V precision reference voltages. The device also features a high-speed 2-Mbps serial interface, a clock oscillator circuit, and a programmable alarmcurrent capability which lets the transmitter send out-of-range currents to indicate a transducer fault. The AD421 is fully compatible with the standard Highway Addressable Remote Transducer (HART) protocol or other similar Frequency Shift Keying (FSK) serial-communications methods. This communication protocol allows simultaneous analog and digital communication with intelligent field instruments and transmitters.

The AD421 is available in 16-pin DIP, 16lead SOIC, and 16-lead SSOP packages. The part is specified over the standard industrial temperature range of -40°C to +85°C and costs \$6.95 in quantity.

Analog Devices, Inc. One Technology Way P.O. Box 9106 **Norwood**, MA 02062-9106 (617) 329-4700 Fax: (617) **821-4273**

#502

#### RS-232-TO-V.35 CONVERTER

The Model 240 Universal RS-232-to-V.35 Interface Converter efficiently steals power from the RS-232 interface and provides a DTE- or DCE-switchable configuration. It includes a unique LCD display, called DataSpy, that informs the user of the status of the data and handshake signals included in the RS-232 interface.

Supporting data rates that range from DC to 100 kbps, Model 240 includes conversion circuitry for 13 signals. The power to drive the unit is derived from the interface signals (data, control, and clocks) on the RS-232 port. At a minimum, TD and one control signal are required. The Model 240 incorporates an externally accessible switch to configure the unit as a DTE or DCE device.

The DataSpy LCD display provides status information about the interface signals being processed by the con-

verter. It operates from less than 1 mW of power and does not affect the operation of the Model 240. The graphic display presents the user with live status of the transmit and receive data signals (TD and RD) and control signals (CTS, RTS, DSR, DCD, and DTR).

The electrical interface for both ports is implemented in DB-25 female connectors. Each unit is supplied with a 10', male-to-male DB-25 extension cable which can be used on either the RS-232 or V.35 port. Additional cables are available.

Model 240 is packaged in a rugged metal case measuring 3.3" x 2.86" x 0.76" and sells for \$220.

Telebyte Technology, Inc. 270 Pulaski Rd. Greenlawn, NY 11740-1616 (516) 423-3232 • Fax: (516) 385-8184

# NEW PRODUCT NEWS

#### STEPPER CHIPSET

The MC1451A intelligent-motion chipset supports up to four axes of electronic gearing. The master input for each axis is provided by quadrature encoder input signals. The output consists of pulse and direction signals. The chipset is programmed using any standard microprocessor by sending high-level motion instructions which are then interpreted by the chipset.

Other standard features of the chipset include 32-bit motion registers, programmable breakpoints, host interrupts, and three user-selectable profiling modes: S-curve, trapezoidal, and velocity contouring.

In addition, a special motor-stall-detection capability has been added. This feature uses the encoder feedback signal to determine when the motor has lost steps, even while the motor is in motion. When the chipset detects a stall condition, it safely shuts down the ongoing move to avoid system damage.

The MC1451A is packaged in two 68-pin PLCCs, with an optional 44-pin PLCC used for encoder feedback. Pricing for the four-axis version with encoder feedback is \$129 in quantity. Performance Motion Devices, Inc. 97 Lowell Rd. Concord, MA 01742 (508) 369-3302 • Fax: (508) 369-3819

#504

#### PRECISION, THREE-TERMINAL REFERENCE

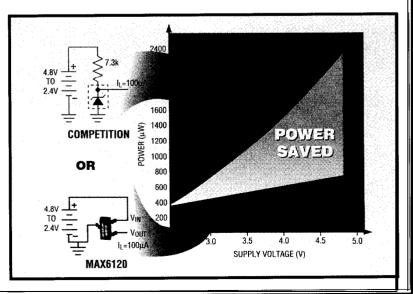

Maxim Integrated Products has released the MAX1620, the first 1.2-V micropower, precision three-terminal voltage reference offered in an SOT-23 package. Ideal for 3-V battery-powered equipment where power conservation is critical, the MAX1620 is a low-power alternative to existing two-terminal shunt references.

Unlike two-terminal references that throw away battery current and require an external series resistor, the MAX-1620's 70- $\mu$ A maximum supply current (typically only 42  $\mu$ A) is independent of the input voltage, which means max imum efficiency at all battery voltages. In addition, it operates from a supply voltage as low as 2.4 V, and initial accuracy is  $\pm 1$ %. The MAX6120's temperature drift is 100% tested in the SOT-23 package and guaranteed to be less that 100 ppm/°C (typically only 50 ppm/°C).

The MAX1620 is available in a 3-pin SOT-23 package, as well as an 8-pin SO package in the extended-industrial (-40°C to +85°C) temperature range. Prices start at **80¢** (1000s).

Maxim integrated Products 120 San Gabriel Dr. Sunnyvale, CA 94086 (408) 737-7600 Fax: (408) 737-7194

## **FEATURES**

12

18

22

38

SPARC Telco Applications

Caller ID Fundamentals

Vehicular Control Multiplexing with CAN and J1850

The Embedded Sun

DSP in RISC Embedded Processors

Fujitsu's SPARClite Alternatives

Embedding a Message-based System

In telecommunications, controllers are traditionally hardware based. However, Temic proposes a judicious mix of hardware and software. You gain the same performance for a fraction of the cost.

## FEATURE ARTICLE

#### **Richard Pedreau**

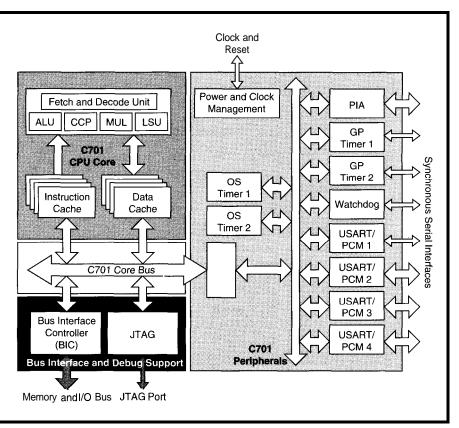

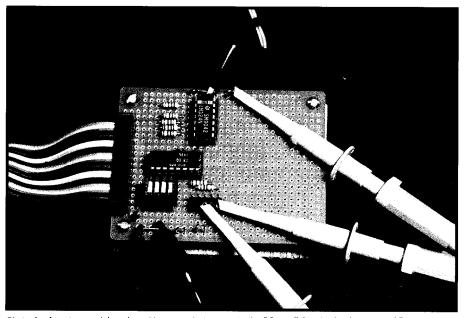

emic's TSC701 Advanced Communication Controller, pictured in Photo 1, initiates a new challenge in embedded telecommunication applications. This innovative concept is built on three premises: increased flexibility, combined online signal processing and protocol handling, and maintaining performance at the system level.

New multistandards (e.g., for base stations or handsets), proprietary protocols, and rapid product evolution bring with them the need for increased flexibility which outperforms the usual hardware-based solutions. A software approach, to the extent that it reaches the same overall performance level, brings much more flexibility.

Emerging communication applications need signal-processing features (e.g., compression capability) combined with real-time protocol handling and the usual control skills on a single chip. The ideal is to include only the necessary DSP functions, thus achieving the best performance-to-cost ratio from a component standpoint.

The performance-to-cost ratio extends to the system level. Subsequently, the challenge is to preserve the performance level at the highest level while using low-cost peripherals like PC-type DRAM.

#### MUI TISTANDARDS

The new telecommunication standards or multistandards originate in part from local regulatory organizations (especially in Europe) which force different rules from one country to the next. Because telecom equipment manufacturers are usually indus-

SPARC Telco Applications

28

try giants, the advantages of a flexible approach-keeping the customization operation as late as possible in the process-are obvious.

Most OEMs want to start with globally usable hardware (including wireless base stations, PABX, ISDN adaptors, and even telephone sets) and simply customize it with different line-interface daughterboards and software. This approach reduces manufacturing costs while improving overall quality.

A second reason for the new multistandards is the need to adapt the same equipment to different uses. An obvious example is the telephone handset.

The handset is slowly evolving to become a personal piece of equipment and not a community one. From one phone at home, one wireless, and one portable, the trend is toward one handset per individual, which can function both in GSM/PCN (portable) mode and DECT (wireless) mode for home or office.

This emerging general-purpose wireless handset must remain low cost while becoming at least five times more capable. In this area, these challenges pend:

- size constraints prohibit multicomponent solutions

- the silicon-area enlargement required for a comprehensive processor with full DSP implementation leads to an unacceptable cost increase for consumer electronics

Since a processor needs to control the equipment, it makes most sense to integrate chosen DSP features as coprocessors in a powerful but physically small RISC core.

Thus, the large computing power of the RISC CPU enables it to handle the integrated DSP coprocessors as another execution unit. Basic equipment management uses only about 10% of its CPU load, which is perhaps the only way such a versatile handset can be conceived.

This approach brings DSP functions back to where they left off over 10 years ago. Then, the lack of computing power in the main processor core of the CISC processors at the time of the

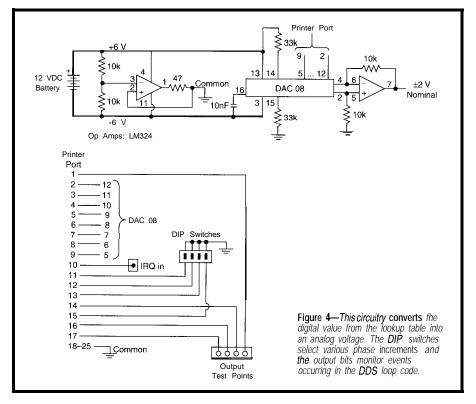

Figure 1-TSC701 combines online signal processing and protocol handling.

68k, 28000, and similar processors paved the way for specialized DSPs.

I don't mean to imply that DSP processors will become obsolete. On the leading edge of technology, there's always a place for high-end specialized DSPs. They're the only way to solve certain calculation problems. But, CPU architectures can usually come back a few years later with a "normalized" solution.

To enlarge the scope of this discussion, the tendency to actually integrate so-called "visual" instructions into the new processors (like Sun or Intel) is another example of the same evolution. Although until now this field has been restricted to highly specialized processors, in my opinion it will soon return to the standard processor area.

#### PROPRIETARY PROTOCOLS

Proprietary protocols are the norm in this field. Communications is an area where one finds very important multinational companies such as Alcatel, Nortel, Nokia, or Ericson. These companies logically have to preserve their know-how by using proprietary protocols. On the other hand, they must also remain close to the standard to preserve the industry compatibility.

In dealing with proprietary protocols, there are some very practical advantages to a software approach like Temic's TSC701. First, this approach makes it easy to respond to slight variations in protocol parameters like CRC polynom, recognition flags, channel filtering, and so on.

Also, competitive software solutions should come with a comprehensive library of drivers in documented source format as well as directly implementable binary files.

Thus, the user has two advantages: fast time to market using a provided turnkey solution, and the ability to later customize the drivers to react to application upgrades.

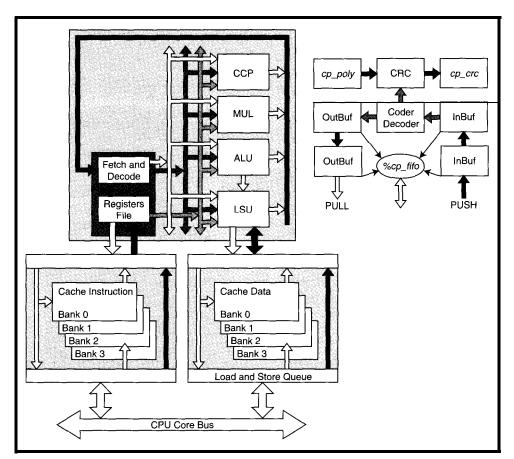

#### SPARClet ARCHITECTURAL CONCEPT

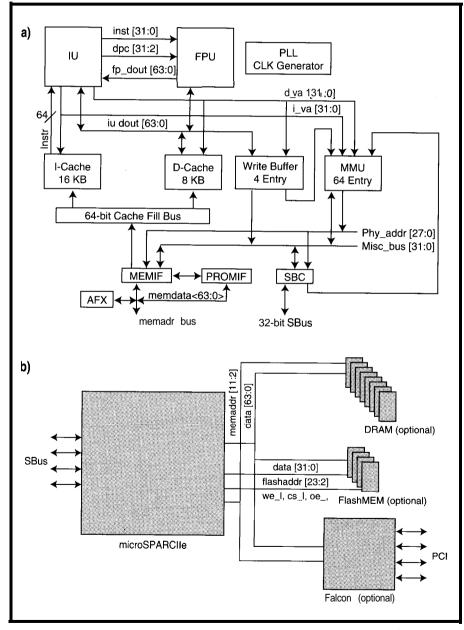

The TSC701, whose components are diagrammed in Figure 1, combines online signal processing and protocol handling.

As a principle, SPARClet maximizes use of all hardware resources when it's logically possible to do so.

Figure 2—Full message coding and sending is accomplished by the TSC701SPARClet core on the left using the process outlined on the right.

The first target, however, is not performance, but rather price to performance. In particular, resources are not duplicated to increase performance [i.e., it's not a superscalar design].

A resource (e.g., the adder) is used as soon as it is free and the operands are available. There are two reasons for an instruction to stall. The first is data dependency.

Because we want to proceed with an instruction as soon as possible and because operands often don't depend on the immediately preceding results, the general case to consider is that there is no data dependency.

Actual dependencies are checked to maintain compatibility with SPARC. When such a dependency is detected, one of the following behaviors is chosen depending on the situation:

- the dependent instruction is stalled, waiting for its operands to be available

- the operand is bypassed from a pipeline stage where it is available when it exists

The other reason an instruction can stall is resource dependency. Resources for most instructions are available every cycle. However, this is not always true.

For example, the multiplier is used for several cycles in order to multiply. When one multiplication follows another, the second one waits until the first is completed before proceeding to the multiplier.

Parallelism between instructions is especially visible for multicycle instructions (since SPARClet is not superscalar, single-cycle instructions are not executed in parallel). Long instructions include:

- integer multiplication (minimizes hardware)

- memory accesses on cache miss

Integer division and floating-point operations are not yet implemented but will be multicycle instructions when they are.

The same principles apply to the whole design, not just the SPARClet

core. For example, when the cache processes a miss, it's still available to process other requests from the core, especially in the case of a hit. Of course, the same hazard-detection mechanism is implemented to ensure data integrity.

Because SPARClet is coded in such a way that it can be parameterized, architectural enhancement can lead to gain in various areas, including:

- RAM speed

- power dissipation (it allows a lower frequency for the same processing power)

- chip area by reducing hardware resources (cache size, multiplier, etc.)

#### **DSP CAPABILITIES**

The emerging advanced communications systems require high-performance embedded devices to support new features such as real-time speech recognition or image and data compression. The half-rate GSM

protocol, which requires an overall computing power of 40 MOPS, is an example.

In these new systems, special-purpose devices (DSPs) or coprocessors frequently act in conjunction with microcontrollers. However, due to increasing application complexity and system constraints, reduction in components is an important issue in system cost.

SPARClet is a general-purpose, modular architecture combining superscalar techniques, digital signal functions, and on-chip peripherals specially designed to address these requirements.

DSPs traditionally have few unique architectural features that set them apart from general-purpose processors. In fact, most of those functions can be handled by a general-purpose architecture.

SPARClet extends the generalpurpose SPARC architecture to match these capabilities with a low-cost implementation target, which is a fundamental factor in embedded systems. SPARClet is a SPARC V8e-compliant architecture. The concept of this new implementation is based on a parallel but nonsuperscalar architecture which allows several operations to run in parallel. However, some superscalar techniques, such as out-oforder mechanisms, synchronize the infinite-input datastream.

Traditional processor architectures operate memory accesses, scalar instructions, and multiplication sequentially. So, they require fast computing and/or fastest access elements to achieve a high level of performance.

SPARClet parallelizes these operations to relax the constraints of the operational units' intrinsic performance and the speed of external devices such as memory.

The best way to give a clear picture of the architecture is to browse the main features of a DSP and see how the SPARClet architecture and the TSC701 address each one. DSP features include:

• single-cycle multiplier

- multiple operations per processor cycle

- zero overhead looping and circular buffers, implemented in specific instructions

Most of today's DSPs propose a single-cycle multiplier as a mandatory operator for digital signal processing. In reality, a software-pipelining approach can be used because such algorithms use a low percentage of multiplication (1030%).

Also, the necessary memory loadand-store operations can be inserted transparently during the multiplier latency cycles. In this way, high performance can be reached with a lowcost multiplier, which is linked to the silicon cost.

SPARClet offers a parameterizable multiplier speed that is set based on the application's requirements. In the TSC701 implementation, the chosen configuration is a 32 x 32-bit, 4-cycle multiplier. It offers accumulation on a regular window register (64 bits which can be double length if necessary)

concatenated with 8 bits of the y register. An extra cycle is used in case the accumulation register changes from the last executed multiply-and-accumulate instruction.

As mentioned, SPARClet is a nonsuperscalar implementation which fetches one instruction per cycle. However, the architecture allows multiple operations (like memory accesses, multiplication, and addition) to run in parallel.

A general-purpose architecture like SPARClet can actually achieve zerooverhead features by unrolling loops and software pipelining.

In the case of SPARClet, no specific instructions are required because the execution time for general-purpose instructions is masked by parallel execution flow. Circular buffers are already part of the original SPARC architecture.

On top of all these advantages, development is easier with a SPARC than a DSP chip because of the completeness of SPARC's development tools.

PROMJet®-ICE

Ultra compact EPROM and FLASH emulator with high st download speed (I-4 Mb/S), largest memory capacit -32Mb) and fastest access time (85~25ns) in the industry Other features include 3V target support, jumperless con guration, battery backup, 128 bit bus support and externa ower supply. → Fits directly into memory socket or use attension cable for flexibility. → Compact design based of high density FPGAs and double-sided surface-mounted 1 Actual Size IIIII layer PCB for added reliable operation

→ ICE option allows simulta neous access to PROMJet

memory while target is run ning without waitstate signal

→ Plug & Play drivers for industry standard debuggers

→ Call us at 206.337.0857 for a complete data sheet from our Faxback service or fax u at 206.337.3283. Price star at U\$295 for a one Mbit uni

> Everett Mutual Tower 2707 Colby Av, Suite 90 Everett, WA 98201, USA 30 day money-back policy Visa & Mastercard accepted

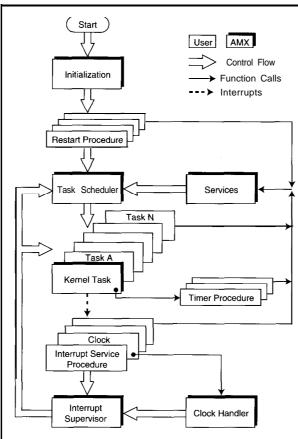

#### **TSC701** PROTOCOL HANDLING

The TSTSC701 microcontroller handles the HDLC protocol with a software-based method that is both innovative and flexible. There are three main benefits to the user:

- there's no physical limitation to the number of possible HDLC channels

- the CRC calculation can be customized, providing the ability to adapt the computation to proprietary protocols

- · data transfer between USARTs, external memory, and communication coprocessor uses software DMA instead of a regular DMA channel

Thus, adaptation and filtering can be done locally in the software DMA routine, enabling the user to maximize the performance-to-memory tradeoff.

For example, if the transaction involves only one channel in a PCM frame, frame buffer size can be limited by filtering the data stream inside the transfer routine. A regular DMA channel would transfer the

amount of external memory to be used. The necessary filtering would be possible only as a postprocess.

The full message coding-and-sending chain is detailed in Figure 2. The first step involves the coding of the data stream and is performed by the internal HDLC coprocessor. This coprocessor performs the HDLC coding and CRC calculation at a rate of one bit per cycle. The TSC701 then stores the coded data by 32-bit words in an external frame buffer located in DRAM.

This background process is interrupted by a trap initiated from the PCM/USART transmitter. This trap signals that its internal-transmission FIFO (16 bytes) has reached a level lower than the programmed limit.

As the trap has to be served with a highly deterministic behavior (to avoid any gaps in the transmission), the corresponding trap handler ought to be locked in the internal instruction cache

This trap handler performs the software DMA function of transferring words from the external frame buffer to the transmitter FIFO.

the roughly 50 MIPS available on the TSC701 working at 50 MHz.

#### BYPASSING SLOWDOWNS

SPARClet supports high throughput of the data stream in the user's system. Due to the parallel architecture, memory and I/O device access time has little impact on the computing performance of the processor.

The SPARClet I/O stream exploits internal features such as load-and-store buffers, which decouple the internal

> computing flow and external I/O accesses.

Data and instruction caches are sized quite high on the TSC-701 to provide the best hit rate (16 KB of instruction cache and 8 KB of data cache). When there's a cachememory hit, access time from the core is limited to one cycle. External memory consistency can be managed in Write Through as well as Copy Back mode.

SPARClet qualifies as a dataflow architecture in the sense that pipelining is extended up to the core bus and bus-interface controller. The core bus is based on a split-cycle mechanism (i.e., the

whole data stream, thus forcing a large

ter window disconnected from the regular SPARC circular windowing structure to spare save-and-restore time loss. In this case, the window permanently contains the pointers necessary to access the frame buffer in DRAM and temporarily stores the transferred data.

It must switch to a special 32-regis-

Reception mirrors the transmission process. This mechanism provides maximum flexibility in CRC computation (the polynom register is programmable by the user).

The CPU load used to handle the HDLC protocol remains low. Two fullduplex 2-Mbps links induce an overall consumption of about 10 MIPS out of

request and its completion are split).

Thus, the core is able to pipe requirements to the bus controller without waiting for the first access to complete.

SPARClet's core stalls only if a real data or resource dependency occurs. For instance, assume the program performs a load instruction from a memory location not present in the cache at the moment (i.e., a cache miss ), then

- the transaction request is posted to the bus interface controller

- during the waiting time for the data to be available, subsequent instructions are executed unless

Photo 1—Temic's TSC701 Advanced Communications Controller shifts signal-processing features out of the hardware and info software in order to provide equivalent performance, greater flexibility and lower costs.

they use the data expected from memory. Only in this case does a stall occur.

These three features work together to minimize the impact of externalmemory and I/Q-device access times. The embedded market drains high production volumes, so it's especially sensitive to manufacturing cost-not just the processor's cost but the cost of the whole system.

These parameters have been taken into account as major constraints when developing the SPARClet architecture and the TSC701 Advanced Communications Controller.

#### **GLOBAL CONCLUSION**

The three features highlighted in this article-software approach, DSP integration, and system cost reduction-provide processor manufacturers with a new challenge over the next few years. In addition to the industrial requirement for standardization, current trends are motivated by a strong market appeal. Cellular-phone manufacturers expect a dramatic increase in sales in conjunction with a big price reduction. Staying competitive in this market means changes in design methods.

The Internet boom brings with it communication cards (fast modems) or ISDN adaptors in almost every individual PC. This equipment will soon move from the office and factory into the home office, which means production will increase by four or five times in less than a decade.

Inside a worldwide company, LAN interconnections were just an advantage a few years ago. More and more, they are becoming a necessity.

These market factors will force OEMs and silicon providers to solve the triadic cost, performance, and flexibility equation.

Integrating signal-processing functions, adapting to low-cost peripherals, and implementing a software-driven approach for processors address this challenge. It also maintains an acceptable path from the wafer-fab technologies' standpoint& After receiving his Master in Electrical Engineering, Richard Pedreau worked as a test engineer for Philips. He joined Temic 11 years ago, where he has managed the microcontroller products engineering and technical marketing for the SPARC products division. Richard may be reached at richard.pedreau@matramhs.fr.

#### SOURCE

TSC701 Advanced Communication Controller Temic Matra MHS SA "Les Quadrants" 3, avenue du Centre 78054 St-Quentin-en-Yvelynes Cedex France (33) 40 18 18 18 Fax: (33) 40 18 **19 20**

#### RS

401 Very Useful402 Moderately Useful403 Not Useful

## FEATURE ARTICLE

Richard Newman

# Caller ID Fundamentals

As Caller ID has become popular, people want to know how to make the data available to computing devices. This introduction describes how information is transmitted, formatted, and decoded.

While Caller ID boxes are available for about \$19 from national discount chains, there is not a single inexpensive Caller ID interface for the PC. Most implementations are multiline or add storage features which increase the price significantly.

In this article, I present an inexpensive, straightforward, and simple Caller ID decoder. You can connect a telephone line to one side of it and out the other to get standard serial data just as if it were coming out of an offthe-shelf modem.

Since data is delivered serially, you can handle it with a standard modem program set to hex decode mode or with a custom program that decodes the data into uniformly formatted fields.

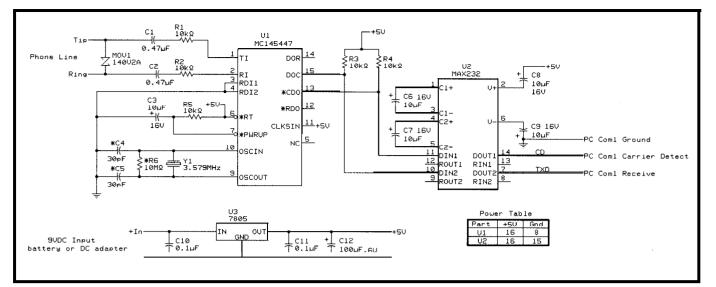

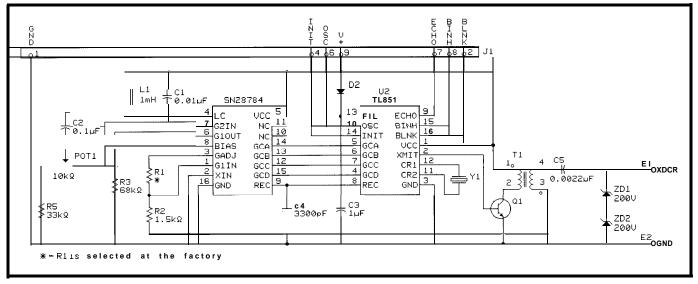

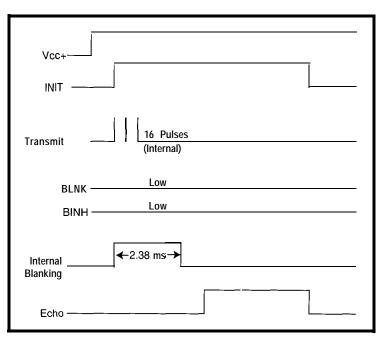

For this project, I'm using the Motorola MC145447P Calling Line Identification (CID) Receiver with Ring Detector and colorburst crystal FOX036S. The Motorola CID chip is inexpensive (\$2.60) and has integrated ring detection. You don't need any external circuitry to determine when a call is arriving.

#### THE BASICS

Caller ID data is transmitted from your local telephone company office to your telephone line directly after the first ring. During this time, your telephone line is on hook, and there is no DC current flow.

The data is transmitted onto the high-impedance line, which is only AC terminated by the phone's bell in your home.

Since the telephone company's equipment is expecting to see a highimpedance state on your phone line, the interface of the Caller ID receiver must pick the AC audio signal off the telephone line without terminating the line and answering the inbound call.

All telephone company exchanges operate slightly differently because of the make of the physical equipment and version of the software running on the switch. It is therefore possible for unique incompatibilities to surface.

For example, information is transmitted right after the first ring and is complete before the second ring starts. If you answer the telephone after the first ring, you might still receive the Caller ID data. However, if you answer during the first ring, the exchange usually aborts the transmission of the CID data, losing the information for the call.

#### **CIRCUIT DETAILS**

The Motorola MC145447 CID chip has an analog front end, which interfaces to the telephone line with two 47- $\mu$ F, 200-V nonpolarized capacitors in series with two 10-k $\Omega$  resistors.

The input to the CID chip is differential. Because of this, it attempts to decode any differential (AC) voltages seen on the line, which results in occasional periods of unintelligible garbage.

The data transmitted from the telephone company is in standard Bell 202 format, similar to the format used by the old 1200-bps modems we all had a few years ago [Bell 212). The data is transmitted at 1200 bps with 8 data bits, no parity checking, and 1 stop bit. It is asynchronous, serial, and binary.

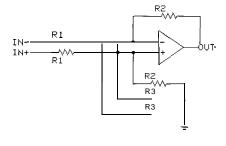

Figure 1-I The complete circuit brings the phone line in one side and delivers PC-compatible serial data out the other

A logical 0 [called a space) is sent as 2200 Hz, and a logical 1 (called a mark) is 1200 Hz. You can see there is nothing special or proprietary about the data. It comes to you exactly as your PC would send it out its serial port.

If you're using DSP to decode the CID signal, the typical worst-case amplitude of the transmitted signal is **-13.5** dBm from the telephone company. The facilities (the wires traveling though your town and ending at your house) introduce another -20 dB of attenuation.

This interference means that the CID receiver demodulator should be capable of decoding a worst-case signal of -34.5 dBm. I chose the Motorola device because it meets this worst-case specification.

If you look at the schematic presented in Figure 1, you see that the telephone line goes into one side of the CID receiver chip and data comes out the other side in inverted physical format.

If you take this inverted data and feed it into a MAX232 RS-232 driver/receiver, it inverts the data and translates it into RS-232 standard voltages.

At this point, you're ready to attach the RS-232 data to a PC or embedded controller and make a call to the chip. When the CID data is decoded, it is presented to the PC in an almost readable format. You can see the caller name, telephone number, time, and date along with some garbage data.

Since we aren't making a standalone box, but one that connects to a PC, I disregarded any features for power saving or ring detection. You should power the project from an isolated AC adaptor.

#### **RING SIGNALS**

The CID receiver is forced to stay active always because RDI1 and RD12 are held low and \*RT is held high. A standard delay-type reset circuit made from C3 and R5 makes \*PWRUP go low shortly after power is applied to the circuit.

In this always-active mode, the data out of the DOC pin attempts to decode any signals on the telephone line, including ringing voltages and occasional DTMF signaling, during the dialing of outgoing calls. This data appears as garbage. The circuit takes another signal out of the CID chip on 'CDO, which is only high when valid CID data is being received. The software of your system ignores and flushes all characters received when \*CDO is low.

As soon as \*CDO goes high, the software buffers all received characters in a queue. This technique ensures that the queue always contains usable data.

One discrepancy between the databook description of the device and my real-world prototype is the drive capability of the DOC and \*CDO pins. I found it necessary to apply a 10-k $\Omega$ pullup resistor for the MAX232 to receive the data correctly.

When you receive the Caller ID message, it can be up to 80 characters long and in one of two standardized formats called *fixed* and *variable*. The variable format is standard in North America and is what I will discuss here.

#### VARIABLE FORMAT

The variable-format service data is one long data package divided into subpackages. The first two characters

[0x80][0x27][0x01][0x08] 04301212 [0x02][0x0a] 2145554141 [0x07][0x0f] Caller's Name [0x01][0x01][0x00]

0x80—indicates the start of package indication 0x27—indicates the total number of characters (hex) to be transmitted in the main package 0x01 0x08—means that the date and time are coming next and are 8 characters 0x02 0x0a—signals that the calling number is next and is 10 characters 0x07 0x0f—indicates that the calling name is next and is 16 characters 0x01 0x01-is the checksum 0x00-marks the end of transmission received in the data package start with an 80 hex. The next char-

Table 1—An example of a complete caller ID stream from the telephone company includes name and number. acter is the number of characters total to be transmitted.

The subpackages follow, starting with a character that indicates the type of subpackage (name, number, date, time, service) and the total number of characters in the subpackage. The subpackage types include:

- 0x0 l-date and time in DDDDTTTT format

- 0x02-calling number

- 0x07-calling name

Table 1 offers an example of a package and indicates what the separate components of the package stand for.

Your software should sync on the 0x80 character and be able to accept any package type next. There is no guarantee that the subpackages will arrive in a certain order nor that all subpackages will be sent in a particular package.

There are other subpackage types I won't elaborate on but which might indicate private or blocked calls. Typically, even if a subpackage meaning

private or blocked is sent, a number package is also sent with an ASCII "P" or "B" in the first character of the called number field. Your software should not always expect numeric data for the number field.

If you decide to apply this circuit to an application which doesn't have differential input, you should be able to couple the signal directly into the tip pin. Since you're not using a differential input, this signal needs to be twice the recommended amplitude to activate the demodulator section of the Motorola device.

If you find this hard to do in a single supply system, you could add an inverting op-amp to the tip pin and apply your signal to the input of the op-amp and the ring pin. This modification simulates a differential input to the chip from an externally provided single-ended input.

#### **EXPECTATIONS & APPLICATIONS**

If you expected this article to be deeply technical, you're probably thinking, "Gosh! This is really easy!"

Yes, it is. So, when you apply this circuit or specification to your system, if you use the Motorola chip as a caller ID decoding block, it should be almost plug-and-play.

All that's left is the application. You could have a window pop up a caller's name and number onscreen. This read-out could be juxtaposed with another window that holds notes about the caller from a database and include details such as account status.

Heh! Before you know it, you're enabled! You've found a perfect application for Caller ID and you.  $\Box$

Richard Newman is an electrical engineer living in Dallas, TX. He designs specialized communications and industrial automation equipment either in partnership or on contract. He may be reached at ricardo@netcom.com.

> OEM (1K) PRICE INCLUDES: 5 SER (8250 USART) 3 PAR (32 BITS MAX) 32K RAM, EXP **64M**

STANDARD PC BUS -LCD, KBD PORT - BATT, BACK, RTC IRQO-15 (8259 X2)

8237 DMA 8253 TMR BUILT-IN LED **DISP**.

UP TO 8 MEG ROM CMOS NVRAM USE TURBO BASIC, MASM RUNS DOS AND

WINDOWS

EVAL KIT \$295

#### R S

PIECE

UNIVERSA

404 Very Useful 405 Moderately Useful 406 Not Useful

..55....195

MVS BOX 850

(508) 792 9507

MERRIMACK, NH

## FEATURE ARTICLE

#### Willard Dickerson

# Vehicular Control Multiplexing with CAN and **J1850**

Part 1: Vehicular Multiplexing Fundamentals

In this article, Willard lets engineers in on what vehicular multiplexing is, how systems interact, and how protocol is established. Why? So your automatic windows don't take precedence over your ABS. ehicle multiplexing is a means of passing information between vehicle control modules and/or subsystems through a serial data link. The link is typically one or two wires shared among several modules [also called nodes].

Link sharing is facilitated by placing a special vehicle multiplexing control unit at the interface of each node. The main computer-controller communicates with several distributed nodes through the same port.

The nodes are automobile modules such as sensors, ABS, audio system, traction control, multi- or single-point injection (gasoline engines), diesel injection (diesel engines), cellular telephone, cruise control, and so on.

This series overviews vehicular control multiplexing and evaluates the Motorola embedded controllers (the MC68HC708AS20 in J1850 and the MC68HC05X16 in CAN) in vehicular multiplex devices. Part 1 describes vehicle multiplexing as well as the J1850 and CAN protocols.

In part 2, I'll overview both the MC68HC708AS20 and '05X16. I'll conclude with how these controllers are implemented in their respective J1850 and CAN networks.

#### VEHICLE MULTIPLEXING ORIGINS

The concept of vehicle multiplexing comes from the computer-architecture technique of local area networks. In this concept, different nodes or modules share the same connection(s) for data communication.

Each node in a distributed system does not require a separate port into a main computer. As a result, fewer wires are needed to communicate between units. This concept has been used extensively in military aircraft, heavy-duty trucks, and factories.

Since the increase in vehicle electronics resulted in excessive, bulkwiring harnesses measuring several kilometers, automobile manufacturers recently standardized reduced-wire multiplexing in passenger vehicles.

#### **DEFINING THE PROTOCOLS**

J1850 or CAN can be described from three vantages:

- as a class of multiplex system

- in its layers

- as fields of information in its message structure

There are three main classes of vehicle-multiplexing systems: A, B, and C. Class D is currently being defined. The Society of Automotive Engineers (SAE) characterizes classes by transfer rates, recommended uses, and intent.

Class A defines vehicle-multiplexing protocols that support transfer rates up to 10 kbps. This protocol is typically used in trip or mileage computers, electric windows, solenoiddriven switches, stepper-motor driven devices, entertainment modules, and so on. It primarily reduces cost, power, CPU throughput, and EMI.

Class B protocols accommodate transfer rates in the range of 10–125 kbps. They are typically used in engine and transmission control functions and cluster data passing. They are also used for general-purpose applications and legislated diagnostics (in accordance with California regulations expected to become law across the U.S. by the year 2000).

Class C protocols support transfer rates from 125 kbps to 1 Mbps. These rates are typically used in advanced engine-control functions (e.g., variable valve timing and fine-gear correction], ABS, and suspension damping. Class C is intended for systems requiring a higher level of speed, intelligence, and safety than Classes A and B.

If you look at vehicle multiplexing protocols in terms of layers, each layer describes a predefined set of physical, electrical, or software characteristics.

For example, a physical layer describes the number and length of lines needed to communicate data at a certain speed. With the CAN protocol, to transmit 1 Mbps, you have a maximum line length of 100 m.

The type of transmission buffers required for a proto-

col is also part of the physical layer. In contrast, the size-of-message field is described in another layer. Each protocol has unique requirements for message-field sizes and arrangements.

Finally, the vehicle multiplex system can be described in terms of its message structure. This structure defines the number and size of each field, the type of information in the fields, and how they are recognized in a message.

For example, the message structure of Class A and B protocols is not as complex as Class C since Class C protocols facilitate control over more tasks in a shorter duration. Class A protocols have lean message schemes.

Conversely, the complexity of Classes B and C depends on their respective applications. Class B tends to communicate with a wider variety of modules and is typically the most complex message scheme.

Notably, the truck and bus vehicle multiplex committee has taken the J1850 (Class B) and put it on top of CAN (Class C), thereby making a more complex version of these protocols.

Class A and B direct functions like automatic window motors, switches, and simple LCD displays rather than functions requiring substantially faster bit rates and more diagnostic data. However, Class C data link controllers are capable of such simple applications, too.

#### MULTIPLEXING SCHEMES

Vehicle multiplex schemes typically provide more protection against noise and signal corruption than older serial protocols such as the SCI and SPI. As a result, vehicle owners have lighter weight cars with more reliable communication links.

Typically, vehicle-multiplex datalink controllers use fewer connections and provide lower susceptibility to automotive-related interference than

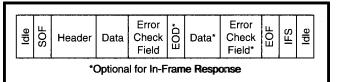

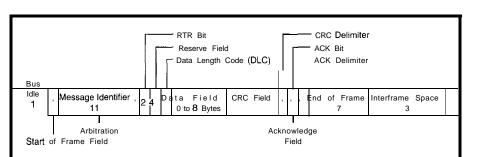

Figure I--The in-frame response is required for the J1850 message-frame format for the 41.6 kbps PWM encoding.

the simpler, more traditional data links.

A multiplexing scheme identifies which node can communicate on the shared link at a given time. There can be seven nodes on a single link. Vehicle multiplexing can take place via frequency division, time division, token slot, or token ring.

A scheme's protocol specifies how to implement the vehicle-multiplex model. It provides a set of rules for transmitter and receiver communication. Frequently, it includes error checking, acknowledge methods, signal rate, and signal encoding.

The protocol is implemented by a protocol handler, which consists of both hardware and software, depending on the task's complexity. Less complex tasks are often done in software. Sometimes, when vehicle-multiplex circuitry is found on embedded controllers, internal hardware and software resources implement vehiclemultiplex protocols.

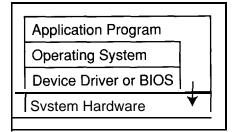

The partitioning of the multiplex protocol is determined by available hardware and software resources. The partitions provide an overall project structure. It determines whether the multiplex controller is implemented in an embedded controller or is standalone, what application to load in the CPU, what incremental loading is

> necessary on the CPU from each protocol layer, and what the cost goals arc. In many cases, partitioning tradeoffs are made to meet cost goals.

Additionally, simulation can help determine the most suitable partitioning for a

problem. For instance, a verilog simulation examines CPU use in a protocol-layer application. If the layer's throughput exceeds projected goals, then alternate strategies are examined.

Error-checking schemes involve parity checks, cyclic redundancy, noise sampling, as well as simple or complex error-handler routines.

The timing methods used in vehicle multiplexing are either synchronous or asynchronous. Data is transmitted serially by one of a variety of methods, which can include either communication mode.

Data flow for these methods can be simplex, half duplex, or full duplex. Whichever method is chosen, the actual bit-rate clock is not transmitted on a separate line but is embedded in the data transmitted.

Synchronous timing provides a known timing relationship between

| application layer-where legislative diagnostics are found. Standard messages provide<br>information about the condition of systems affecting vehicle emissions.<br>presentation layer-consists of the addressing strategy, diagnostic codes, and their<br>parameters. The addressing strategy has both physical and functional modes. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diagnostic codes and parameters are determined by legislative requirements.                                                                                                                                                                                                                                                           |

| session layer-places the system in an idle or sleep power-saving mode, or it can wake                                                                                                                                                                                                                                                 |

| up and alert the system when signals are present.                                                                                                                                                                                                                                                                                     |

| transport layer-includes message screening and filtering for hardware and software                                                                                                                                                                                                                                                    |

| and buffering for the bit, byte, or message level.                                                                                                                                                                                                                                                                                    |

| network layer-involves nondestructive arbitration in which the priority of a node is                                                                                                                                                                                                                                                  |

| determined by the message.                                                                                                                                                                                                                                                                                                            |

| data link layer-involves bus communication, message format, synchronization, and                                                                                                                                                                                                                                                      |

| requirements for response to the message or message errors. See the text for                                                                                                                                                                                                                                                          |

| more information on the J1850's message frame format.                                                                                                                                                                                                                                                                                 |

| physical layer-describes hardware performance aspects of the system such as bit rate,                                                                                                                                                                                                                                                 |

| bit encoding, drive type, redundancy, and media.                                                                                                                                                                                                                                                                                      |

Table I--The seven expanded layers for the J1850 can be embedded into three layers which are used in practise

Microcontrollers let you adapt your designs to changing requirements. Now, Field Programmable Gate Arrays can double your flexibility by letting you change your product's circuitry on-the-fly. But how do you quickly learn the tricks of combining FPGAs with microcontrollers?

The FPGA amplifies the capabilities of the 8031 Program the EPX780 to create custom address decoders, new Interrupt sources, additional timers, specialized coprocessors, real-time bus monitors and more! The only limit is your ingenuity!

It's easy to use the eoX31 You get a complete tutorial on FPGA design with our FPGA Wortout text. Or modify one of our design examples for your own application using the PLDSHELLFPGA programming tools and 0.31 assembler included with the epX31. Next, load the FPGA configuration + 8031 object code unto the epX31 through the PC parallel port. Then apply real-world test signals to your design under the control of your PC.

The **epX31** grows with your designs. You can cascade several epX31s to build multiprocessor or multi-FPGA systems. Or connect special-purpose chips to the epX31 through the breadboard interface

The epX31 lets you try out more designideas with less effort No more untangling wire-wrap or patching printed circuit boards. Just reprogram the static RAM and you're ready to try again That will but a smile back on your face from 9-to-51 So will the price!

Figure 2--- The CAN message frame format includes a parity bit in the CRC field.

the bits and bytes. The bytes are transmitted continuously until a condition halts or suspends their transmission.

The receiver recovers the clocking from transitions in the data. This technique allows fewer lines to be used than standard SPI controllers, which usually provide a separate line for the receiver clock.

Conversely, asynchronous controllers have a variable relationship between bits and bytes. That is, each bit can be transmitted separately or in groups. Typically, a start bit synchronizes the transmission.

#### ENCODING

Vehicle-multiplex messages are usually encoded to:

- reduce emissions in a harsh underthe-hood environment

- improve recognition of bits during arbitration for single-wire systems

- reduce physical media costs by facilitating single- or dual-wire systems

The common encoding types include NonReturn to Zero (NRZ), Pulse Width Modulation (PWM), Variable Pulse Width Modulation (VPWM), Frequency Modulation (FM), Modified Frequency Modulation (MFM), and Manchester.

The method of encoding is determined by cost, bandwidth efficiency, and the EM1 imposed on a given system. Cost increases with the more complex devices and circuits of certain schemes. Bandwidth efficiency becomes critical for higher-speed multiplex protocols such as CAN. The EM1 is essentially affected by the number of transitions per unit time a waveform generates and data encoding.

NRZ encoding represents data with unipolar (above ground) or bipolar

transitions. The width of a bit representing one or zero is the same, which allows infinite bits per transition. No edges are present if the same bit is asserted continuously.

The NRZ scheme offers a low number of transitions per bit (hence low emissions) and fixed transition or sample points.The bipolar version requires twice the voltage swing as the unipolar scheme.

On the other hand, NRZ accumulates clock errors among nodes, making it harder to synchronize the bits. This characteristic is a major nuisance in vehicle multiplexing since the clock is not transmitted on a line separate from the information. This problem can be solved by bit stuffing.

Bit stuffing guarantees at least a 1bit transition every 5 bits. A bit of the opposite polarity is inserted each time five consecutive 1s or 0s are detected. The receiver understands and uses the same rules by deleting the inserted bits from the stream.

PWM encoding represents each bit by varying the pulse width of periodic signals from one-third to two-thirds. The shape of the pulse and approximate locations of the edges are fixed during each periodic signal. It can use two edges on the data link for each bit transmitted. This encoding is commonly found in J1850 equipment with data rates of about 10.4 kbps.

PWM offers defined sample points, fixed bit lengths, the ability to arbitrate wired or contention buses, and the ability to resynchronize all receivers on a rising edge of each bit.

Conversely, PWM is less cost effective than an automotive data link (i.e., single wire). The dual edges increase radiated emissions. It's therefore more difficult recognizing bits, especially with extreme ground offset. VPWM represents a binary signal by varying a pulse within periodic boundaries. Unlike PWM, however, the variations in the pulse and edges can alter within each periodic pulse.

FM is represented by periodic clock pulses signifying a one if intervening time slots are pulsed or a zero if no change occurs. This technique adversely effects radiated emissions since several edges can potentially be generated at higher frequencies.

MFM encoding is similar to the FM, except that it eliminates the clock pulses unless the data remains constant for more than two consecutive bits. The pulses can be replaced with transitions. That is, a one is signified by a transition, and a zero by no transition. Unfortunately, there is more complexity distinguishing between clock pulses and logical transitions. This problem can be resolved due to the 41.6-µs bit times for J1850.

Additionally, arbitration is more complex with MFM than FM because for any given bit position, either a one or a zero has higher priority depending on the previous bit stream.

Manchester encoding is represented with transitions. It defines various fixed bit times (e.g., 96 µs for 10.4 kbps) and forces a transition at each defined boundary. A one is signified by an additional transition triggered in the middle of a bit time, and a zero by an unchanged pulse during a bit time.

#### 51850 OVERVIEW

J1850 is a one- or two-wire serial protocol for low- to medium-speed vehicle-multiplex applications. The lower transmission speed (IO.4 kbps using VPWM) is implemented in a one-wire system and the higher transmission speed (41.6 kbps using PWM) in a two-wire system [1]. It falls under the Class B protocol, and emissions are in-between those of NRZ and PWM. This protocol-or variations of it is used by domestic automotive companies. It controls such devices as window motors and lock solenoids, digital instrument display, antilock brakes, and fault communication [2].

As with other vehicle multiplex schemes, this protocol consists of a synchronous multimaster bus system. Multiple units connect to the same bus, and any unit can request control of the bus. Through arbitration, one unit is selected to master the bus.

This protocol offers:

- open architecture

- moderate complexity

- single-level bus topology

- multimaster peer-to-peer

- legislated diagnostics

As an open architecture, J1850 allows prioritization of frames and is compatible with CSMA/CR.

Moderate complexity reduces cost because it requires less hardware and software, which in turn decreases development and maintenance costs.

A single-level bus topology provides one link so all nodes transmit and receive from a single path. It receives all frames simultaneously.

A multimaster system enables multiple nodes to request access of a bus (i.e., any node can potentially be the master). This approach also reduces hardware and development costs since no special hardware and software is required for a separate or additional master node.

Legislated diagnostics consist of automated tests for vehicle emissions or any other environmental test required by law. These tests go federal in 1997.

Layers provide a standard means to categorize and describe fundamental hardware and software architectural characteristics of a vehicle-multiplex

- physical layer-consists of its drive capability, bit level, and format and transmission medium. transfer layer-includes message framing and arbitration, error detection and report,

- and fault confinement. object layer-includes message buffering, acceptance filtering, and prioritized message

- handling. application layer-presents the hardware and software trade-offs which are dictated by the specific application.

Table 2-The CAN layer information includes four basic layers.

## Running under Windows?

Using a standard **dat a acquisition**

board islike using an old

typewriter. They both get the job done, but ... there is a better way.

> Standard data acquisition boards can unknowingly sabotage your data. Ensure the integrity of your results.

ADAC's Windows Optimized 5800 Series gives you the resources you need: FIFOs, Channel Gain RAM, Dual DMA, aggressive prices, and some of the best noise performance in the industry!

5801MF: 16 channel12-bit A/D, 333KHz, 216-bit D/A, 40 digital I/O

**5803HR:** 16 channel 16-bit A/D, 100KHz, 2 16-bit D/A, 40 digital I/O

#### learn more -

voice 800-648-6589 fax 617-938-6553 web http://www.adac.com email info@adac.com

1.11

system. Table 1 illustrates the seven layers of the typical J1850 system can include.

In practice, however, these seven layers reduce to three. The presentation layer embeds in the application layer, just as the session, transport, and network layers are a part of the data link layer. Only the physical layer stands alone.

The message-frame format is required for the 41.6-kbps PWM and not for the 10.4-kbps VPWM

[1]. As you can see in Figure 1, the inframe response format consists of a start-of-frame signal (SOF); header, data, and error-check field; end of data (EOD); more data; and end-of-dataframe (EOF) check field [3]. Notably, the error field is optional with the inframe response format for 10.4-kbps VPWM [1].

A standard J1850 system requires the examination of four types of errors: cyclic redundancy check (CRC), frame length, out of range, and invalid bit, byte, and symbol detection [4].

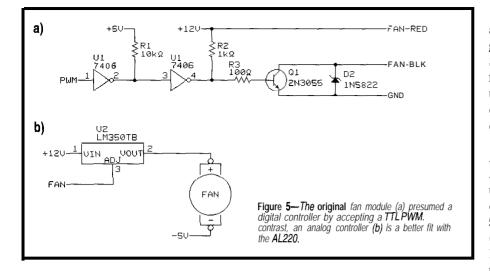

The first two errors are typically decoded by examining the number of bits or bytes within partitions of a transmission. However, the latter two error types are detected through a form of digital or analog filter.