# MIBEDIDED C MONTHLY SECTION

# GERGEUS GERGEUS THE COMPUTER APPLICATIONS JOURNAL

## THE COMPUTER APPLICATIONS JOURN #86 SEPTEMBER 1997 GRAPHICS AND VIDEO

HDTV—The New Digital Direction Compressing Audio & Video for Internet Build a Laser Billboard EPC: PC Manages a NASA Plant-Growth Chamber

\$3.95 U.S. \$4.95 Canada

## TASK MANAGER

#### Digital TV Now

m sure you've either seen a live demo or read about future scenarios. As the hype goes, a central part of your amazing, self-maintaining house is going to be the television in your living room. You'll have over 100 channels of local, network, and specialized programming including movies, pay-per-view, and digital music. An intelligent, interactive viewing guide will show you what's on based on personal criteria, give you onscreen summaries of listings, let you search the listings while watching another show, and prompt you when "can't miss" shows come on. Audio and video will arrive at your house digitally, eliminating snow, ghosting, and other irritating noise....

Of course, they always tease you at the end stating something along the line of, "The technology necessary to make this dream a reality is available today." Of course, the only reason most people don't have it now is because their local cable company still uses old technology like blocking filters on the line. Comparatively speaking, local cable companies are still writing monthly bills out longhand.

Well, all that is changing for some lucky cable customers. TCI, the nation's largest cable company, has just finished testing a new service that makes the dream demo real. Dubbed All TV (www.alltv.com), it offers the usual fare of basic and expanded analog cable channels. What it adds is up to 85 more channels (for a total of 118 in our area) of special-interest programming, movies, pay-per-view, and music. To fit all those extra channels into a cable system's limited bandwidth, the new channels are MPEG-2 encoded, allowing more to be squeezed into the same space while making the picture more immune to noise. I'm having the service installed tonight, so drop me a note if you're interested in an evaluation once I've had it for a while.

With the recent introduction of DVD and All TV, and with HDTV just around the corner, these are exciting times for what had become a rather mundane audio/video industry.

Speaking of HDTV, we kick off this month's Graphics and Video issue with an update from Do-While Jones on where HDTV is and what it will mean during the next few years. Next, Mike Podanoffsky explores what's necessary for sending audio and video over another popular communications medium—the Internet. Finally, David Prutchi tries to combat the high cost of highway billboards by putting together a laser image projector.

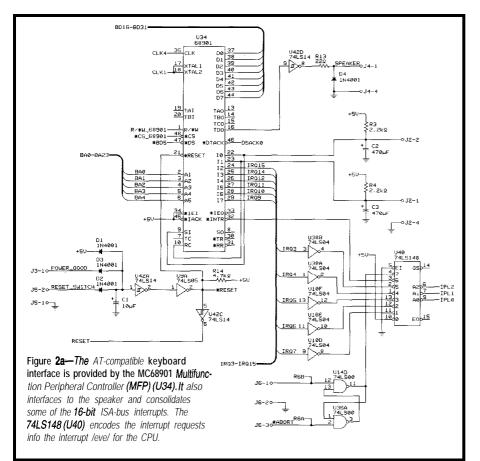

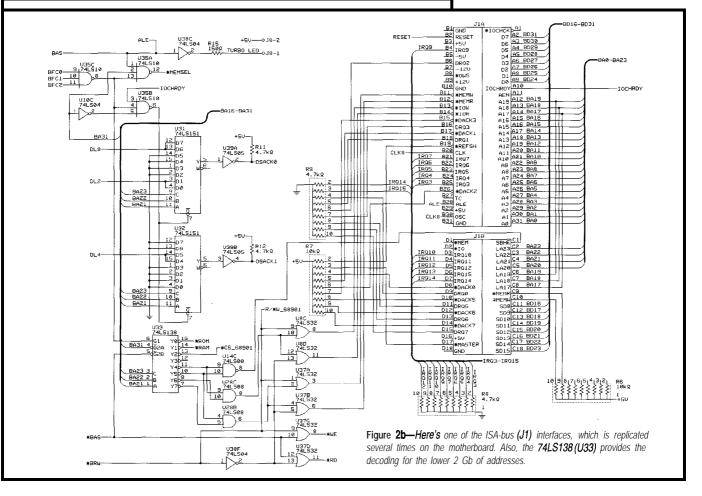

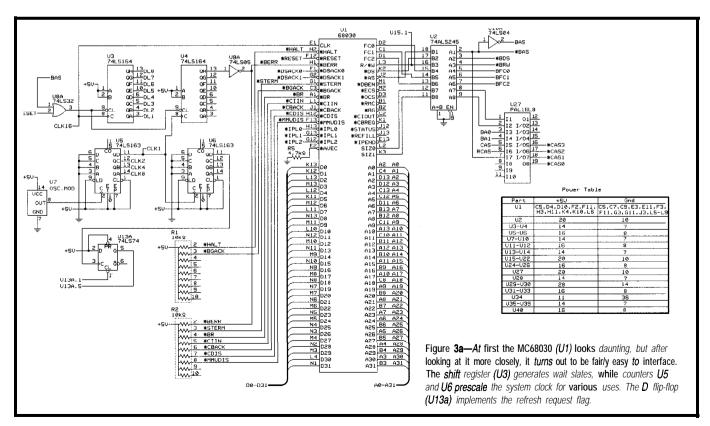

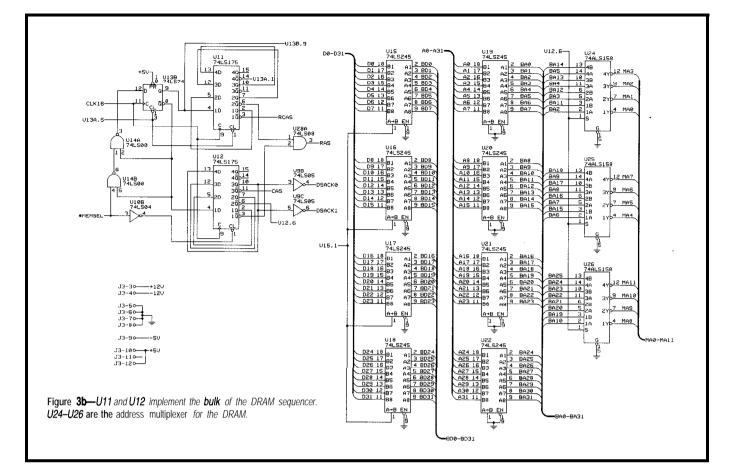

Starting a new MicroSeries, Ingo Cyliax presents the hardware of an MC68030-based workstation he put together for university courses. In upcoming articles, he'll go over software for the board. Jeff constructs a quick PC keyboard-to-serial ASCII converter, and Tom covers the latest silicon for wireless systems.

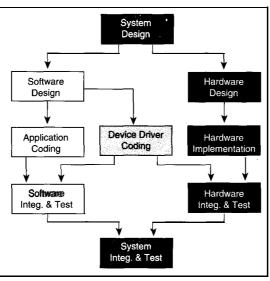

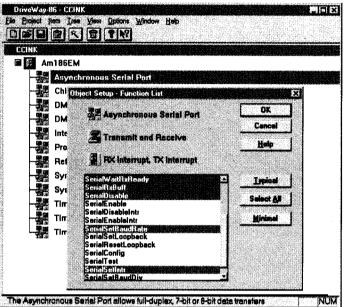

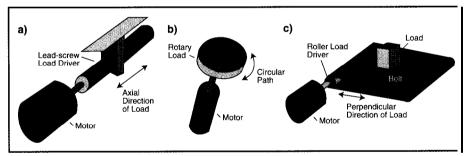

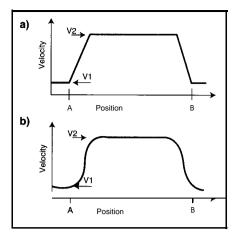

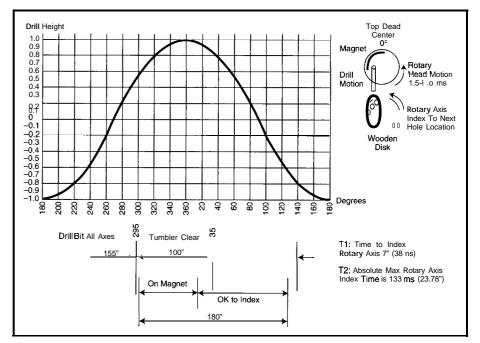

In *EPC*, Simon Napper starts with a look at the problems of writing device drivers, and explores solutions for maximizing productivity while minimizing learning curves and bugs. Chuck Raskin takes the PC/104 helm this month with an overview of controlling motion with PC/104 boards. And lastly, Fred introduces us to his latest embedded project: a plantgrowth chamber for the Space Shuttle.

editor@circuitcellar.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

EDITOR-IN-CHIEF Ken Davidson

MANAGING EDITOR Janice Hughes

TECHNICAL EDITOR Elizabeth Laurençot

ENGINEERING STAFF Jeff Bachiochi

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Rick Lehrbaum Fred Eady

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR KC Zienka

PRODUCTION STAFF John Gorsky James Soussounis ASSOCIATE PUBLISHER Sue Hodge

CIRCULATION MANAGER Rose Mansella

CIRCULATION CONSULTANT John S. Treworgy

> BUSINESS MANAGER Jeannette Walters

ADVERTISING COORDINATOR Valerie Luster

CIRCUIT CELLAR INK<sup>®</sup>, THE COMPUTER APPLICA-TIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. Oneyear (12 issues) subscription rate U.S.A. and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank.

VISIT OUR WEB SITE FOR SUBSCRIPTION INFORMATION AT www.circuitcellar.com Direct subscription orders and subscription related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301. POSTMASTER: Please send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Cover photograph Ron Meadows – Meadows Marketing PRINTED IN THE UNITED STATES

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

HAJAR ASSOCIATES NATIONAL ADVERTISING REPRESENTATIVES

NORTHEAST & MID-ATLANTIC Barbara (Best) Curley (561) 694-2044 Fax: (561) 694-2051 B.Best-Haar@worldnet.att.net MIDWEST & SOUTHEAST Christa Collins (954) 966-3939 Fax: (954) 985-8457 HajarChrista@worldnet.att.net WEST COAST Barbara Jones & Sheliey Rainey (714) 540-3554 Fax: (714) 540-7103 shelley.hajar@worldnet.att.net

Circuit Cellar BBS—24 Hrs., 2400/9600/14.4k bps, 8 bits, no parity, 1 stop bit, (860) 871-1988. For information, mail to info@circuitcellar.com. World Wide Web: www.circuitcellar.com

All programs and schematics in *Circuit Cellar INK*<sup>®</sup> have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers.

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK®.

Entire contents copyright © 1997 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

## NEW PRODUCT NEWS

#### FLAT-PANEL CRT REPLACEMENT

The **VAMP-PanVista** is a 17.7" CSTN-LCD color flat-panel CRT replacement featuring 1024 x 768 (XGA) resolution. Ideal for high informationcontent screens, it rivals color TFT screens in viewing quality.

reens in viewing quality.

The VAMP-PanVista screen offers the viewing area of a 21" CRT at a fraction of the weight, volume, and power consumption (30 W, compared to the CRT's 150+ W). Its color STN (super-twisted nematic) technology permits a brilliant display of 5 12 colors, 150-nit brightness, and a 25: 1 contrast ratio. The VAMP-PanVista accepts standard VGA signals, sync-on-green, composite, and other custom analog signals. Its design enables the use of the existing computer's video card.

The guided acoustic-wave touch option affords 92% optical clarity,

17.7" HIGH VISIBILITY

PANEL MONITOR

Edited by Harv Weiner

150-points/inch resolution, z-axis for pressure-sensitive feedback, and superb resistance to chemicals and scratching. Overall system dimensions for the open-frame

model are 18.7" x 14.3" x 3.5". The VAMP-PanVista sells for \$4490, including the 17.7" display, guided-wave touchscreen, and all interface electronics.

Computer Dynamics 7640 Pelham Rd. Greenville, SC 29615 (864) 627-8800 Fax: (864) 675-0106 sales@cdynamics.com www.cdynamics.com

#501

#### UNIVERSAL PROGRAMMER

The ALL-11 Universal Programmer features a native Windows interface and supports a wide range of flash, (E)EPROM, BPROM, serial PROMs, PLD/CPLD/FGPA, and microcontrollers. This full-featured programmer is affordable enough for project programming but powerful enough for the most demanding applications.

The ALL-1 1 has a 40-pin DIP socket to support devices with 8-40 pins in a DIP package. Available adapt-

ers and converter sockets support devices in almost any package configuration (8–300+) pins. The programmer connects to the serial port of any PC and communicates at up to 115 kbps. An embedded high-speed CPU controls all programming waveform generation by SMD pin driver circuits for guaranteed accuracy in any PC environment.

A Windows 95/3.1 user interface simplifies programming. For example, the AUTO function lists all available operations supported for a particular device. Simply check off the desired operations and press 0 K. For production operation, an external YES key on the programmer can be used to initiate operations, and an LED by the socket signifies that operations completed correctly. To program another device, just insert a blank IC into the socket and press Y ES again.

Priced at \$1095, the ALL-1 1 measures approximately 8.5" x 9.5" and weighs less than 3.2 lbs., including a built-in universal input power supply.

Tribal Microsystems, Inc. 44388 **S.** Grimmer Blvd. Fremont, CA 94538 (510) 623-8859 • Fax: (510) 623-9925 **sales@tribalmicro.com** • www.tribalmicro.com

#502

## **NEW PRODUCT NEWS**

#### **INCLINOMETER**

The ISU Inclinometer is a rugged, noncontact measurement transducer that uses a capacitive angle sensor working in concert with a microprocessor to provide a wide angular measurement range with excellent resolution and accuracy. The inclinometer comes stan-

The PWM output is 30 Hz, free running, and the pulse width varies 49.3 µs per degree. The unit measures 2.6" x 1.3" x 0.6", and it weighs 0.8 oz. Power input is 5 VDC at 2 mA.

The ISU Inclinometer is priced at \$85. Options include limited angle-range calibration, higher or lower accuracy versions, and 4-bit addressability.

dard with both PWM and serial digital outputs onboard, in addition to optional 4-bit addressability. Typical uses include wheel alignment, medical range-of-motion measurements, antenna elevation, construction equipment, and machine tools.

The ISU Inclinometer features a full 360" range with  $\pm 0.1^{\circ}$  accuracy at level and plumb, and  $\pm 0.2^{\circ}$  at other angles. Its time constant is 0.4 s (typical), and it has an angle output rate of 533 ms. Its serial port output is RS-232, except for voltage levels, and runs at 9600 bps.

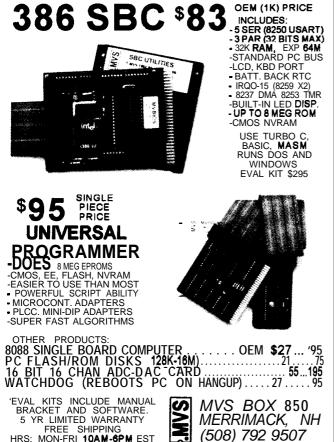

OEM (1K) PRICE

SmartTool Technologies 2030B Fortune Dr. San Jose, CA 95131 (408) 434-7000 Fax: (408) 434-7080 mdsmart@ix.netcom.com www.macdunc.com

#503

## Parts List Manager

#### For Engineers, Product Designers, Prototypers

HRS: MON-FRI 10AM-6PM EST

## NEW PRODUCT NEWS

#### SINGLE-BOARD COMPUTER

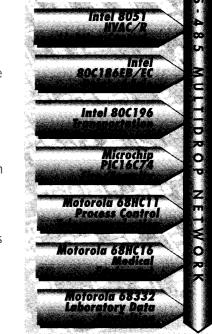

The CP-320 SBC is based on the 80C320 microcontroller and features a variety of interface options. In addition to a high-speed link to a PC parallel port, an RS-232C buffered serial port, and a bidirectional PC/ATcompatible keyboard interface. this board features an IR data link that operates at speeds up to **115.2** kbps. The card also features an RS-485 interface for multipoint data transmission.

The 80C320 microcontroller is an enhanced 8051 derivative. It now

features optimized instruction execution, up to 33-MHz clock speed, two full-duplex serial ports, dual data pointers, and powerfail reset. It also has a watchdog timer, 13 interrupt sources, and enhanced stop and idle operation. The board measures 4.5" x 6.5" and includes either 32 or 64 KB of EPROM, 32 KB of battery-backed SRAM, 82C55 PPI, and a DS1232 processor supervisory chip. In addition to the PC interface connectors, a number of header connec-

tors bring out various board resources.

The 33-MHz version of the CP-320 sells for \$219. A 25-MHz version is available for \$179. Allen Systems 2346 Brandon Rd. Columbus, OH 432211 (614) 488-7122

#504

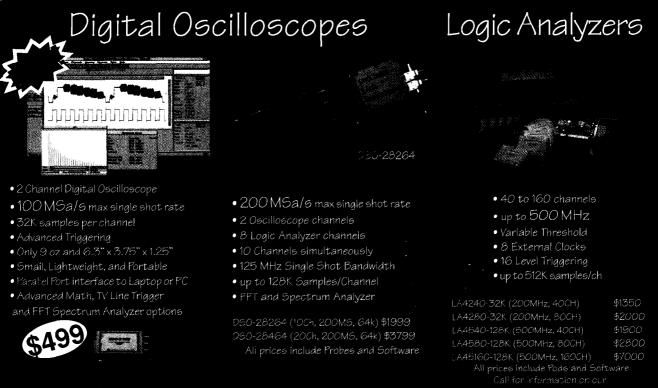

100 MSa/s Pattern Generator optio

#### Link Instruments (201) 808-8990

369 Passaic Ave • Suite 100 • Fairfield, NJ 07004 • Fax (201) 808-8786 Web: http://www.Linkinstruments.com/col9 · Email: Sales@Linkinstruments.com

For \$499 you get the model DSO 2102 Scope, Probes, Interface Cable, AC Adapter, and Windows and DOS Software.

8 Issue 86 September 1997 Circuit Cellar INK®

## **FEATURES**

28

| 10 | HDTV<br>The New Digital Direction             |

|----|-----------------------------------------------|

| 22 | Compressing Audio and Video Over the Internet |

| 28 | The Laser Billboard                           |

A Low-Cost Laser Image **Projection System**

## HDTV

## The New Digital Direction

Do-While traces the evolution of television technology, looking specifically at how compatibility with early technology has shaped current developments. He then introduces HDTV fundamentals, going over how the new monitors, bandwidth, and converters will work.

n rare occasions, decisions are made that affect nearly every body. Some people win; some people lose. The bigger the change, the bigger the opportunity and the bigger the danger.

The invention of the personal computer was one of those things. Bill Gates took full advantage of it. You didn't, so nobody talks about your bad haircut.

But now, there's a second chance at a once-in-a-lifetime opportunity. In 2006, all the televisions in 96 million American homes become obsolete. Nearly every one of those households will buy something new (a TV, converter, etc.).

Your mission, if you accept it, is to build something lots of people will buy. Of course, if you design something like the 8-track cartridge or Beta-format VCR, I will disavow ever knowing you.

Seriously, the FCC's decision to switch to high-definition (digital) television (HDTV) has significant impact.

For example, you won't be able to show any 8-mm camcorder home videos on an HDTV unless you have a converter or one built into your set. Your present VCR doesn't work with HDTV, so you need a new one to record your soaps and watch them after work.

But, I'm not going to tell you what to design or buy. The technical issues are far too intricate to explain here.

#### 10 Issue 88 September 1997 Circuit Cellar INK@

**Do-While Jones**

**FEATURE**

ARTICLE

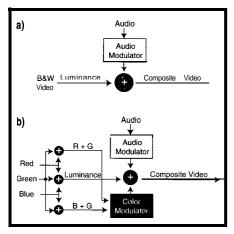

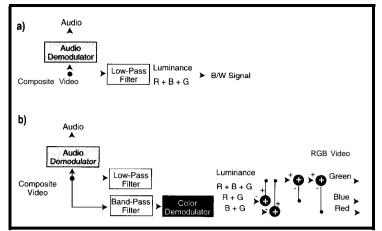

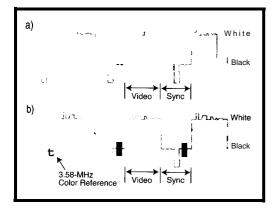

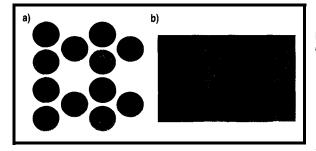

Figure 1a—B/WTV signals consist of a luminance signal with audio modulating a high-frequency carrier. b—The red, green, and blue signals from a color camera combine to form a luminance signal. Two chrominance signals, consisting of two of the three color signals, modulate a high-frequency color carrier and are added to the luminance to create a composite video signal.

Instead, I want to give you a general understanding of the issues.

Digital TV frees us from some limitations that resulted from the need to be compatible with technology of the 1950s. The change, however, is not without difficulties.

#### CONSIDER THE QUESTIONS

The practical ramifications of the switch to HDTV aren't generally understood-even by professionals.

I interviewed TV and satellite-dish employees after the FCC announced its decision to convert from analog to digital TV. Not one fully understood the compatibility problems involving camcorders, VCRs, and cable boxes.

A cable-TV manager's response was most surprising. He said 50% of his customers have cable-ready TVs or VCRs because they don't want to mess with a cable box. Only those wanting pay-per-view or premium channels have boxes, and they don't like them.

When TV stations switch to HDTV in 2006, he plans on converting digital video at the station and broadcasting good old NTSC analog video. He may change his mind if the customers who bought HDTVs drop his cable service and buy satellite dishes instead.

What will your cable company do? Broadcast analog video and add HDTV channels as they become available? After 2006, will they drop the analog or convert HDTV to analog and broadcast both converted video and HDTV? Do you own a satellite dish? It can already decode MPEG-2-encoded standard-definition digital television (SDTV), but what about MPEG-2 HDTV? Will you completely replace your receiver, or will someone sell software that makes the receiver HDTV compatible?

Do you have home videos of birthday parties? How will you watch them after 2006? Will you keep an old TV and VCR (stored beside your 8-mm movie projector) for this? Will you pay someone to convert your videos and 8-mm movies to HDTV-format video tapes or disks?

These are just a few of the far-reaching implications of the format change. To make intelligent decisions, you need to understand the reasons for the changes and the compromises made by the various solutions.

Perhaps the easiest-and most entertaining-way to understand the technological issues is to follow the history of TV in America. The performance of today's sets is poor because they're compatible with 1950s technology. Let's look at the foundation that determined how the entire structure came to be.

#### COLOR COMPATIBLE

In the old B/W days, the video signal (luminance) was added to the audio signal. The audio signal modulated a 4.5MHz carrier and could be separated from the video with a high-pass filter. The combined signal, or composite video, is shown in Figure la.

Color TV introduced a difficult problem. There were lots of B/W TVs-not as many as the 200300 million there are today, but quite a few nevertheless.

The number of TV sets went from 137,000 in 1947 to more than 7 million in 1957 [1]. Stations didn't want to broadcast in color if the programs could not be seen on B/W TVs, and people wouldn't buy color TVs if they couldn't watch their favorite B/W programs.

To solve this dilemma, they took advantage of the fact that the three primary colors of light (red, green, and blue) can be mixed to produce any color in the rainbow, including white.

Color-TV cameras measure the amount of red, green, and

blue light coming from the scene. Color-TV sets produce three pictures (a red, green, and blue] so close together that they are virtually on top of each other. If you mix "equal" amounts of red, green, and blue light, you get white light.

Adding the red, green, and blue pictures together creates a luminance signal like the one produced by a B/W camera. Of course, a color set separates the luminance back into red, green, and blue signals. Two added chrominance signals let the TV set do this. Figure lb shows the general method. (I'm fibbing a bit here, but you'll get the truth later.)

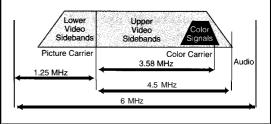

The video signal is applied to an RF modulator whose frequency depends on the broadcast channel. Each channel is allowed a 6-MHz bandwidth. Channel 2 is 54-60 MHz, channel 3 is 60-66 MHz, and so on.

There's a gap between channels 6 and 7 because that's where FM radio stations are. But typically, channels are 6 MHz wide and 6 MHz apart.

The modulation technique is Vestigial Side Band (VSB). All the upper side bands are transmitted, but only some of the lower side bands are. This cuts the transmission bandwidth almost in half.

Figure 2 shows the lop-sided frequency spectrum of the broadcast signal. In other words, old B/W TV signals had 4.5 MHz of upper sidebands, which produced sharp, clear pictures.

The new color-TV sacrificed some clarity by taking away bandwidth to add color. This was necessary to retain compatibility between color and B/W video.

The broadcast video goes from the transmitting antenna to the receiving antenna and into the TV tuner. The tuner demodulates the signal to obtain the composite video signal. Now, let's see what happens to the composite video for the color and B/W cases.

Figure 2—The composite video signal uses 6 MHz. The co/or signals occupy some of the bandwidth formerly used by B/W video.

As depicted in Figure 3a, B/W TV just strips off the audio signal and uses the remaining composite video as the luminance signal. It doesn't process the color signals because the B/W circuits were built before color TV was invented.

In old B/W TVs, the low-pass filter rejected the audio carrier, not the color signals. The high-frequency color signals cause the sharp edges of the picture to be a little fuzzier, but most people don't notice the degradation in quality.

Figure 3b illustrates how color-TV circuitry separates the composite signal back into its red, green, and blue components. The low-pass filter extracts the luminance, which contains the three color signals added together.

The band-pass filter extracts color signals from the upper portion of the spectrum and gives them to the demodulator. It extracts the two chrominance signals that separate the colors again.

In this simplified diagram, one of the chrominance signals contains red and green information. The other holds blue and green. Subtracting the red and green chrominance signals from luminance yields the blue signal. Subtracting blue and green yields red. And, of course, subtracting red and blue yields green.

The red, green, and blue signals go to the red, green, and blue guns in the color picture tube. If the input signal is B/W, then there are no chrominance signals and the R+G and B+G signals are 0. The red, green, and blue signals are all equal to the luminance, so the color TV produces a B/W picture.

Figures 1b and 3b aren't entirely accurate. In practice, it's more complicated. Adding equal amounts of red, green, and blue signals doesn't produce a signal that looks exactly like a B/W luminance signal.

A real B/W signal is more sensitive to green because our eyes are more sensitive to green. I ignored this in Figures lb and 3b to show how one intensity and two color signals produce a B/W-compatible color signal. Now you have the concept, I can risk telling you the truth.

Figure 3a—The B/W TV strips off the audio and uses the rest of the signal to modulate the picture tube. b—The color circuitry separates the composite video info ifs red, green, and blue aspects.

The luminance signal (i.e., Y) gives each color a different weight. So, the two chrominance signals (i.e., R-Y and B-Y) must be specially weighted sums so they can separate the luminance into red, green, and blue signals:

$$\begin{split} Y &= 0.59G + 0.30R + 0.11B \\ R-Y &= 0.70R - 0.59G - 0.11B \\ B-Y &= 0.89B - 0.59G - 0.30R \end{split}$$

Y, R-Y, and B-Y are the signals that come out of the S-Video connector on a satellite-dish receiver or high-end VCR. (For a slightly different formulation of these equations, see Mike Podanoffsky's "Compressing Audio and Video Over the Internet" in this issue.)

Adding Y to R-Y produces R. Adding Y to B-Y produces B. And, knowing R and B, lets you compute:

$$\frac{Y-0.30R-0.11B}{0.59} = G$$

R, G, and B are the signals that modulate the red, green, and blue of color TV.

But, you probably want to know *how* the RGB signals produce a color picture. The various mechanisms each set some limits on the picture's maximum resolution, so let's put off this discussion until we talk about resolution limits.

#### ASPECT RATIO

The first picture tubes were round because they were easier to build than rectangular ones. The ideal format for a round tube is a circular picture, but it needs a spiral scan. It's easier to design and build a system that scans a rectangular area horizontally and vertically.

The best rectangle, from a round picture tube's point of view, is a perfect square. Most people prefer rectangles because more interesting information lies to the left and right of center than above and below it. We live in a world where more things are laid out horizontally than vertically.

A square fits in a circle with the least wasted

space. A 16:9 rectangle (16 units wide x 9 units high) wastes a lot of space on the top and bottom.

As a compromise, the 4:3 aspect ratio rectangle was chosen. It gives more viewing area than the 16:9 rectangle and is more pleasing to the eye than the 3:3 square.

Modern picture tubes are rectangular rather than circular. They don't waste space at the top and bottom.

The first rectangular picture tubes were measured diagonally so they could be accurately compared with the predominant round picture tubes of the day, which were specified by diameter. We still use this measuring technique.

Since we can now make picture tubes in any shape, there's no reason to stick with the ugly 4:3 aspect ratio. HDTV uses the 16:9 aspect ratio, which is more visually pleasing and more compatible with commercial motion pictures.

The problem is, how do you display a 16:9 aspect ratio picture on a 4:3 tube? You have three choices-get rid of a picture's right and left edges, make the picture smaller and waste space on the top and bottom, or distort the picture.

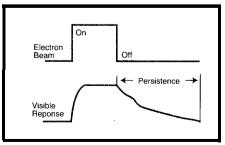

Figure 4—Phosphor starts glowing when the electron beam hits if and continues glowing for some time after the beam turns off due to oersisfence.

When movies are broadcast on TV, the first approach is usually taken. Things on the right and left sides of the screen are sacrificed, and the legal disclaimer, "formatted to fit your television screen," is displayed.

Often, this approach can't be used for the opening and

closing credits because the lettering goes from edge to edge. So, the picture is then distorted. Another option is to shrink the whole picture and add black bars at the top and bottom.

If you're going to build an HDTV-toanalog-TV converter, you must decide whether to throw edges away or make the picture smaller.

When you want to display an old 4:3 home movie on a new HDTV, you have the opposite problem. You can throw away the top and bottom or shrink the picture, which wastes space at the sides.

#### SCAN PROBLEMS

Pictures are rectangular-not circular-because they're painted onscreen via a raster scan. In other words, they're painted in the same way you read this magazine. You start with the line at the top of the page, read it left to right, move your eye down one line, back to the left, and read the next line.

American standard analog TV draws 525 lines -30 times per second (but not all appear onscreen). So, a line is drawn approximately every 63 us, and a frame takes about 33 ms. This 33-ms refresh rate causes a problem related to the phosphor in TV picture tubes.

Phosphor glows when struck by an electron beam. Picture-tube manufacturers can adjust the phosphor's chemical formula to alter its characteristics and make it glow red, green, blue, or white. (Remember this fact.)

Right now, it's important that they can make phosphor turn on and off very quickly or very slowly. Adjusting the phosphor's speed is critical.

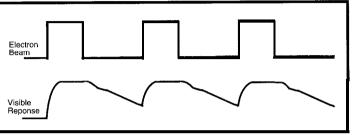

Figure 4 shows the visible response of phosphor to an electron beam. It doesn't start glowing until the beam hits it. And then, it takes little time to reach full brightness. Once the beam turns off, the phosphor glows for a while. This afterglow is called persistence.

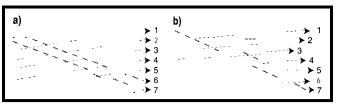

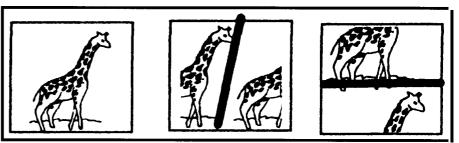

Figure Ca-An interlaced scan draws the odd-numbered lines first and then draws the second field of even-numbered lines to reduce flicker. The dotted lines show the horizontal retrace during the horizontal blanking period. The dashed lines show the vertical retrace. &Progressive scan draws the lines in order, from top to bottom.

The early picture-tube pioneers discovered that if the phosphor was too slow, then moving images looked smeared and blurry. They needed a fast phosphor that could display rapidly changing scenes.

Faster is better-to a point. If phosphor is too fast, it has no persistence. It stops glowing as soon as the electron beam stops shining, causing a flicker.

It turned out there wasn't a good compromise for phosphor speed. When the phosphor was fast enough to show moving scenes, it flickered badly at 30 Hz. To keep the flicker down, the screen had to be repainted at 60 Hz.

The solution was to paint 60 half frames (i.e., fields) per second instead of 30 full frames per second (fps) via a interlacing. All the odd-numbered lines are painted in the first field, and the even-numbered ones go in the second field, as shown in Figure 5a.

Some modern computer monitors draw complete frames at 60 Hz using progressive (noninterlaced) scan. This method is shown in Figure 5b.

Whether the TV signal is analog or digital, cathode ray tubes (CRTS) are analog devices. The electron beam is steered by magnetic fields produced by analog voltages.

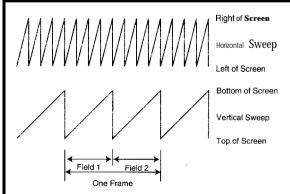

There are both horizontal- and vertical-sweep oscillators. Figure 6 offers simplified versions of their waveforms. For American TV signals, there are 525

cycles of horizontal sweep for every 2 cycles of vertical sweep.

In TV's early days (before networks and video tape), all programs were transmitted live from a local studio. The beam moving across the viewer's TV screen had to match the position of the beam in the studio's B/W camera.

So, the horizontal- and vertical-sweep oscillators in the camera and TV had to be phase-locked to each other. If they weren't, the picture resembled Figure 7.

At the time, the only commonly available frequency

reference in America was the 60-Hz power line. The TV station locked its camera vertical-sweep oscillator to it, as did the TV set in each viewer's home.

A vertical-hold knob on the TV controls let viewers adjust the phase to keep the picture from rolling off the top or bottom of the screen. The horizontalsweep oscillator was synchronized to a harmonic of the vertical-sweep oscillator. The user had a horizontal-hold knob that was even trickier to adjust than the vertical hold.

As the years went by, TV manufacturers built sets that automatically locked to horizontal and vertical sync pulses (I'11 explain shortly). No more horizontal- and vertical-hold knobs!

The early requirement to lock the sweep oscillators to the power line explains why American TVs use 60 Hz. In Europe, where the power lines use 50 Hz, the TVs have a 50-Hz field rate.

Older readers will remember that the picture used to "tear" when the channel was changed because signals originating from TV stations in different parts of the country were on different power grids running at slightly different frequencies. The propagation time between the places changed the signal's phase.

Now, we get so many signals from satellites and repeaters that none are

Figure 6—The horizontal- and vertical-sweep oscillators move the electron beam across the screen.

phase-locked to each other. But modern TVs phase lock before you notice it.

Color TV makes part of this possible. Recall that Figure lb showed a color modulator with two chrominance inputs. It's a synchronous modulator whose output must be synchronously demodulated. Every color TV must have a 3.58-MHz oscillator precisely locked to the transmitter's 3.58-MHz oscillator. You can't get that from a 60-Hz power line! So, let's talk about sync pulses and color bursts.

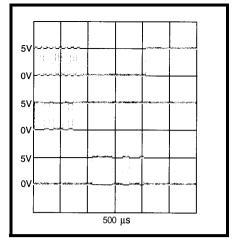

If you look at a TV signal on an oscilloscope, you see sync pulses every  $63.5 \ \mu s$  (see Figure 8a). The TV set can't mistake them for video information because they go outside the range of values from black to white.

Figure 8b shows an 8-cycle color burst that was added to the sync pulse so color TVs could synchronize their color demodulator to the transmitter's color modulator. Every 63  $\mu$ s, the TV adjusts its color oscillator against this color burst. The reference signal must be 3.579545 MHz  $\pm$  0.0002793%.

Since the color TV needs a precise reference to demodulate the color signal, that reference is used to generate the horizontal and vertical oscillators. The horizontal scanning frequency is exactly 2/455 times the color reference signal (i.e., 15.7 kHz).

Since there are 525 lines per frame, the frame rate is 29.97 Hz. There are two fields per frame, so the field rate is 59.94 Hz. Since B/W TVs use a field rate of 60 Hz  $\pm$  a few percent, the 59.94-Hz rate is within a B/W circuit's tolerance.

In Europe, there are 625 lines per frame. Dividing the 15.7-kHz horizontal scanning frequency by 625, you get a frame rate of 25.17 for a field rate of 50.3 Hz-very close to their power-line frequency (not a coincidence!).

Just to muddy the waters some more, movies are recorded on film at 24 fps. Maybe you've seen old movies of Babe Ruth hitting a home run and running the bases. He sure could run fast!

Each frame was scanned twice to produce two fields of video, which is 48 fields per second. But, they're broadcast at 60 fields per second, so he seems to run 25% faster than he really did. The time compression enhances the comic effect of silent films starring the

Figure 7—The picture at the left is properly centered, but if the horizontal or vertical sweep oscillators are out of sync, the picture will run off the screen as shown in the center and right pictures.

Keystone Kops or Charlie Chaplin, but it isn't acceptable for modern films.

The reason you don't notice the same effect on modern films on TV is that 3:2 pull down is used. The first frame of film is scanned three times to produce three video fields. The second frame is scanned twice to produce two fields.

During a 1 -s period, 12 film frames are scanned three times, producing 36 video fields. The 12 film frames are scanned twice to make another 24 video fields (e.g., 60 video fields per second).

When they broadcast at 59.94 fields per second, the speed error is only 0.1 %, which isn't noticeable. Neither is the jitter introduced by the 3:2 pull down. The new digital TV standard provides for several different aspect ratios at several different frame rates. The new sets will have to be much more flexible, potentially leading to a completely new display technology.

#### VCR ISSUES

VCRs record 6-MHz analog video. Since HDTV occupies the same 6-MHz channel as analog TV, you'd think your present VCR could record HDTV. Sorry.

VCRs aren't just tape recorders with a 6-MHz bandwidth. When they first came out, a friend tried to get a highquality recording of some l-MHz signals he was working with. It didn't work.

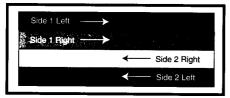

Figure 9 shows how a standard audio cassette-tape recorder records data along the length of tape. It only uses half the tape at a time so the cassette can be flipped over to record on the other side.

Although VHS now stands for Video Home System, when the technology first came out, it stood for Video Helical Scan. The original name gives some insight into how the recorder works.

Not only does the tape move, but the record heads move, too. The path of the head along the tape is helical, like lines on an old-fashioned barber's pole. The video signals are recorded almost perpendicular to the motion of the tape, as shown in Figure 10.

Although there are some obvious discontinuities at the tape edges, they don't cause a problem for analog video. The tape head's motion is synchronized with the vertical sync pulses.

Each stripe represents a whole frame. That's why you can push the VCR's pause button and see the same frame over and over. The head is moving, but the tape isn't, so the same stripe gets read again and again.

Since the tape isn't moving, the stripe of recorded video isn't perfectly aligned with the head's motion. It scans several adjacent stripes and the blank space in between, producing the snow you see onscreen when you hit pause.

The reason my friend couldn't get a good recording of the l-MHz signal was that there was a break at the edge of the

Figure 9-A stereo cassette tape stores audio information in four parallel tracks that run the length of the tape.

Figure 8a—A sync pulse goes from black to blacker-than-black at the end of every line of B/W video so the TV can synchronize ifs horizontalsweep oscillator (not to scale). b-A color reference signal is added to the sync pulses to keep the color demodulator properly synchronized.

tape every 33 ms. There, the data was lost and the VCR tried to insert a vertical sync pulse. That's why you can't record a 6-MHz digital bitstream on a 6-MHz VHS tape recorder.

You can build a VCR with a converter that changes HDTV to analog TV and records it in VHS format. It would include another converter changing the analog TV back to HDTV format, but with poor quality and a 4:3 aspect ratio. That solution may suffice for the short term, but eventually it will become unacceptable.

No doubt you've noticed that people are so accustomed to color TV, nobody watches B/W anymore. The day will probably come when people are so used to HDTV, they won't like analog video, either. When that day arrives, they'll demand digital VCRs that reproduce HDTV perfectly.

#### **VIDEO RAM**

Most personal computers (excluding laptops) use CRT monitors for the screen display. The interface between the digital data and the analog signals moving the electron beam across the screen is a video card that appears as memory to the computer.

Each memory location corresponds to a particular screen location. The program simply writes the desired color to that memory location, and the video card does the rest.

The video card scans the video memory synchronously with the horizontal- and vertical-sweep signals. Unless you *want* snow onscreen, you better not be changing the value in RAM at the same time as the video card's display circuitry is reading it!

About 10 years ago, I worked on a system that used a video insertion card to superimpose text on analog video. We had to update the card only during the vertical blanking interval when the electron beam was moving from the bottom of the screen to the top. I suspect modern video cards do that automatically now. They probably double-buffer the data so you can write to the buffer whenever you want. The card transfers data from the buffer to the video memory at the appropriate time.

The video RAM decouples the input data rate from the display refresh rate. I'm certainly not typing 29.97 characters per second. The screen doesn't flicker every time I press a key.

The computer remembers what I typed and updates RAM at whatever rate I type. The video card displays it using the proper screen-refresh rate.

The practical implication is that if I program my computer to decode MPEG-2 compressed digital video (from a disk file, broadcast video, the Internet, or other source), it doesn't matter if the display rate matches the frame rate or if the monitor paints the screen using progressive or interlaced scans.

As long as the data is buffered so a video RAM location isn't changing while the output circuitry scans it, there won't be a problem. If the frame rate is slower than the display refresh rate (almost certainly the case), then the video memory automatically displays

Figure 10—In a VHS recorder, the record head moves perpendicular to the tape, painting diagonal stripes of data on the tape.

the last frame [or half-frame, if interlaced) while waiting for new data.

So, there's more freedom (opportunity) for designing HDTV monitors. Just because the monitor receives digital information at a particular rate (e.g., 30 Hz) doesn't mean that the picture tube has to be refreshed at that rate. If it could, the monitor might display each frame three times, refreshing the screen at a 90-Hz rate.

The important point is that analog TVs had no capability to store the picture. They had to display every pixel the moment it was received.

Digital TVs receive compressed blocks of information, which are decoded and stored in memory. The TV

monitor can display the information stored in memory any way it wants to, as often as it wants to.

The digital-TV standard only specifies how the information is encoded and transferred. It tells how the TV *could* process the encoded information once it is received, but it's not required to work that way.

#### THE BANDWIDTH ISSUE

Although we commonly refer to American analog TV as having 525 lines, not every line is displayed onscreen. Some lines at the top of the screen contain calibration signals. The actual resolution is approximately 480 lines of 640 picture elements (pixels). Figure 1 **1a**—Early picture tubes had roughly 300,000 clusters of colored phosphor dots. Each color was illuminated by a different electron beam. b-Modem picture tubes have vertical bands of differently colored phosphors.

The HDTV standard lists four frame shapes broadcast at frame rates of

23.976-60 Hz. The most talked about is 1080 lines of 1920 pixels (16:9 aspect) at 29.97 Hz, which has about twice as many lines as analog TV and three times as many pixels per line.

Since HDTV has six times as many pixels as analog TV, you may expect it to take six times as much bandwidth to transmit. Since each analog TV channel is 6 MHz, early estimates were that digital TV would need roughly 36 MHz. It doesn't. It takes about 6 MHz.

How? The amount of bandwidth required depends on the amount of information transmitted. Sampling Walter Chronkite's face six times as often doesn't increase the information you get from him sixfold. From an information-theory point of view, each pixel in a high-definition picture doesn't contain as much data as each pixel in a standard-definition picture. That's because the high-definition picture is oversampled.

Each sample is not statistically independent from the ones around it. Whenever there's redundant information, there's an opportunity for compression.

The Motion Picture Experts Group (MPEG) has defined a standard data compression technique called MPEG-2. Although a complete discussion of MPEG-2 is beyond the scope of this article, I want to go over some general principles of data compression it uses.

You've probably seen a color-bar test pattern. One style has eight vertical bars that run white, yellow, cyan, green, magenta, red, blue, and black.

If you transmit this pattern on analog TV, each line is equivalent to 80 white pixels, followed by 80 yellow pixels, and so on. If you transmit this pattern on uncompressed digital TV with 1920 pixels per line, it would be 240 white pixels, followed by 240 yellow pixels,

#### **E-Series**

EPROM - FLASH - SRAM emulation and LIVE editing, 1 to 8Mbit, 70ns access time. Low voltage (3v)options.

Tel (902) 425 3938 Fax (902) 425 4098 Sales & Info (800) 352 9770

Design

Inc.

and so on. It's not more information, just more bits.

A compression technique called runlength encoding dramatically reduces the number of symbols to be transmitted. Instead of sending the message "white, white (240 times), yellow, yellow (240 times), etc.," you send the message "240 white, 240 yellow, etc.," reducing the number of symbols you need to send to describe one line.

In the color-bar pattern, if you've seen one horizontal line, you've seen them all. So, instead of transmitting the

same line 1080 times, you can send a message that says the next 1079 lines are identical to the previous one.

Taking this a step further, once you've seen a frame of color bars, you've seen them all. There's no need to transmit the same picture 30 times per second. Just transmit a message saying this frame is identical to the last

frame is identical to the last one.

It's possible to compress a color-bar test pattern to practically nothing since it contains little information. It takes very little bandwidth to send a color-bar test pattern regardless of the resolution. Real TV pictures contain more data.

From an information-theory perspective, however, TV is still a vast wasteland of little information. All TV signals can benefit substantially from compression techniques.

Generally speaking, MPEG-2 takes advantage of the fact that adjacent pixels tend to have the same value and that each new frame is similar to the preceding one. It effectively breaks the picture into little squares and scans them in a diagonal zigzag, hoping to find long runs of pixels that are the same value so it can do run-length encoding.

MPEG-2 also compares frames with previous frames. Imagine a camera sitting on a tripod looking at a mountain. The scene doesn't change, so no new information needs to be transmitted.

Suppose the camera pans slowly to the right. Some new pixels appear to the right, and some old ones fall off the left side. The pixels in the middle stay the same, just shifted left.

All you need to do is to transmit the amount to shift the old image and the

few new pixels on the right side of the screen. That greatly cuts down the number of pixels you have to send.

Suppose the camera is sitting on the tripod, not moving, looking at a mountain, when an airplane flies through the field of view. You just need to create a tiny subpicture that contains only the pixels that tell how the airplane looks.

Send this subpicture, and tell the receiver where to put it on the screen. As the airplane flies through the screen, keep telling the receiver how much to move the airplane on the background.

With so much motion, camera rotation, and frame-to-frame difference, the required bit rate might not fit in the allotted bandwidth. Frames will get lost, and the ones you get will be smeared and cluttered with so many artifacts that the commercial might be unwatchable. (Is this is a bad thing?)

In some instances, such as live TV news broadcasts, the encoding will be done in real time. But, in certain cases,

some processing will be done offline.

If you cut the ads, a halfhour TV show is about 22 min. It consists of 39,600frames ( $22 \times 60 \times 30$ ).

Suppose you had an old IBM PC XT sitting around to process those 39,600 frames at a rate of 1 fps. It would take 11 h to compact

the entire program and store it in a file.

At the scheduled broadcast time, you'd simply transmit the compressed file at 30 fps. Or, you could put the file on an optical disc and sell it. Or, you could put the file on the Internet and let subscribers pay to download it whenever they want. You don't have to do everything in real time.

The important new thing about digital video is that display rate is no longer tied to transmission rate, or power line frequency, or anything else. The receiver gets a bitstream that contains compressed frames of data.

Normally, the receiver decodes them on-the-fly and displays them at the rate that it receives them, but it doesn't have to. This is an advantage that can be exploited.

#### MONITOR LIMITATIONS

Building something that can display 1000 lines of video with that much real resolution won't be easy. To understand why, consider the color picture tube.

The first color picture tubes had three electron guns at the back and clusters of three phosphor dots (red, green, and blue) at the front as you see in Figure 1 la.

These three-gun tubes produced three electron beams. The beams were aimed

Figure 12-The electron beam has to refresh the phosphor frequently to keep it glowing.

The MPEG-2 encoding scheme uses a mixture of I-, P-, and B-frames. Iframes are pictures coded using information present only in the picture itself. Predicted P-frames are pictures coded with respect to the nearest previous Ior P-frame. B-frames use both past and future picture frames as a reference.

How does an MPEG-2 encoder know what the future frames will be?

There are both "hard" and "soft" real-time situations. A video teleconference is a hard real-time situation. You can't delay the video too long, or people will find it hard to communicate.

Most broadcast video, however, is a soft real-time situation. Those I *Love Lucy* reruns have been delayed for decades already. A few more seconds won't make any difference.

Therefore, you can delay the transmission a few frames and compare each frame with the next frame as well as the last one. Since it's easier to predict the future when you already know it, this technique greatly simplifies encoding. That's why MPEG-2 encodes a group of pictures rather than single pictures frame by frame.

Compression algorithms generally make compromises, and MPEG-2 is no exception. MPEG-2 is optimized for a typical program. It probably won't work slightly differently so that, for a particular horizontal- and vertical-sweep voltage, the first beam hit the red dot, the second the blue, and the third the green.

The red, green, and blue signals controlled each beam's intensity. As you can imagine, they were difficult to keep aligned-which is why they don't make them anymore. Modern color TVs use a single gun with vertical phosphor strips as shown in Figure 11b.

They sweep a single electron beam across vertical bands of phosphors. The beam's intensity is time-division multiplexed between the red, green, and blue signals.

An HDTV signal has 1920 pixels per line. To get 1920 pixels of color, you need 5760 (3 x 1920) bands of phosphor. If the picture tube is  $4'9'/_2''$  wide (57.6"), then

each phosphor band is 0.01" wide. If the CRT has to paint 1080 lines 30 times per second, that's 32,400 lines per second. Each line must be painted in 30.8 μs.

But, the beam has to be multiplexed 5760 times per line, so each phosphor is illuminated for 5.36 ns. An extra 5-ns delay makes everything red look blue, everything blue look green, and everything green look red. A stray magnetic field deflecting the electron beam 0.01" has the same effect.

Can someone build a TV that keeps the horizontal sweep synchronized to the intensity modulation to within 1 ns and keeps the electron beam shielded from magnetic and electrostatic fields? Probably so.

Can anyone mass produce such a TV at a price consumers will pay? I doubt it. Will such a TV require constant adjustment? You bet your assets it will.

Front-projection TVs have a better chance of achieving high definition than CRTs. These systems have what amounts to three separate B/W picture tubes mounted in a single chassis.

One tube is driven by the red signal and projected through a red lens onto a movie screen on the wall. The other tubes are driven by the green and blue signals and projected through green and blue lenses, respectively.

The CRTs can be smeared with a continuous layer of phosphor (like an

oscilloscope), so there's no problem with hitting specific phosphor dots or bands.

The tricky thing for projection TVs is to get the three pictures aligned. We have several of these systems at work, and they go out of alignment frequently. Every few weeks, we notice the white letters have a red tint to the left edge and a blue tint on the right edge (or some other color aberration), and the technician has to adjust things again.

The place to build a high-definition display is at a baseball park. You could build a big outdoor screen out of 5-lb.

Figure 13a—To convert analog video to MPEG-2 video, use conventional echniques to separate the composite video into three 525-line S-Video co/or signals and an audio signal. Encode the bottom 480 lines using the MPEG-2 encoder algorithm. b-To convert HDTV to analog NTSC video, store the digital image in memory and then convert a portion of that memory to a video signal.

coffee cans with three colored light bulbs in each can.

To get full 1920 x 1080 resolution, you'll have to drink a lot of coffee (5184 tons) to get the 2,073,600 cans you need. If they start selling coffee instead of beer at Dodger Stadium, you'll know why.

Such a screen could be made of modules, each consisting of a matrix of 96 x 54 cells. They'd need 400 modules to construct the entire screen. Each module could have a micro taking color information from a section of shared memory and setting the brightness of the 15,552 bulbs it's responsible for.

Technically, there's nothing to this. But anytime you have over 6 million light bulbs, you have to wonder, "How many maintenance workers does it take to change 6 million bulbs?"

Of course, there's a higher-tech way to build giant outdoor screens. Consider a video wall of CRT screens. You may have seen a TV news anchor standing in front of an array of I2 video monitors (3 rows x 4 columns, due to the 4:3 aspect ratio of analog TV).

The monitors can display 12 individual pictures or one-twelfth of a single huge picture. You could build a 1920 x 1080 outdoor display with 120 x 120 monitors, each displaying a 16 x 9 array of pixels. Or, you could build an array of 16 x 9 square monitors where each displays 120 x 120 pixels.

The design of an outdoor screen is primarily a study of tradeoffs. Several ways aren't technically challenging. Just

pick the best one after looking at performance in daylight, power consumption, cost, and maintenance issues. The real challenges come in making a high-definition display fit a living room.

#### NEW MONITOR TECHNOLOGY

Home HDTV requires a breakthrough in monitor technology. I believe the solution requires parallel processing. Here's why.

Let's go back to Figure 4, which shows the response of a phosphor dot to a single electron beam pulse. To reduce flicker, the electron beam must refresh each phosphor dot before persistence dies away, as shown in Figure 12.

Figure 12 isn't drawn to scale because doing so would be impossible. Earlier, I said that for a 1920 x 1080 color picture tube, the electron beam illuminates the each phosphor dot for 5.36 ns every 33.3 ms [assuming a 30-Hz scan).

Suppose I drew the 5.36-ns pulse 0.01" wide. The pulses would be 5182 apart. Imagine the fold-out drawing!

The basic problem is that, regardless of the frame rate, the duty cycle (the ratio of illumination time to time between illuminations) of the illumination pulse is O.OOOOI%! This is a natural result of serial processing.

In a 1920 x 1080 color CRT, 6.22 million phosphor dots have to be illuminated one after another. Such volume causes a serial processing bottleneck. In computing, we solve this problem via parallel processors.

Imagine a CRT with not one, not three, but 1080 electron guns. Each gun illuminates one line, so all 1080 lines can be illuminated in parallel. Suppose you want to refresh the screen not 30, but 300 times per second. There are 5760 (1920 x 3) phosphor bands per line. Each line is drawn every 3.33 ms, so each band is illuminated for 578 ns every 3.33 ms for a duty cycle of 0.017%.

I doubt it's practical to build a CRT with 1080 guns. But, maybe you could build a linear array of tiny red, green, and blue LEDs.

If you put 5760 LEDs in a line and multiplex the drive current to them, you can produce a line of video. Then, stacking 1080 of them would give you a full 1920 x 1080 display with a 300-fps refresh rate.

If you receive 30-Hz American video, you just display each frame 10 times. If you receive 25-Hz European video, you display each frame 12 times. Frame rate becomes irrelevant.

I don't expect anyone to build CRTs with 1080 electron guns or displays with 6 million LEDs. But, I do expect someone to develop a flat-panel display (perhaps using liquid crystals, phosphors deposited on silicon, or another technology) that's driven by a large array of simple processors which scan a section of video RAM and illuminate small portions of the screen in parallel.

#### **BUILDING CONVERTERS**

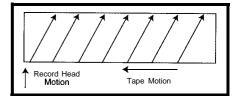

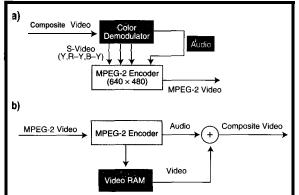

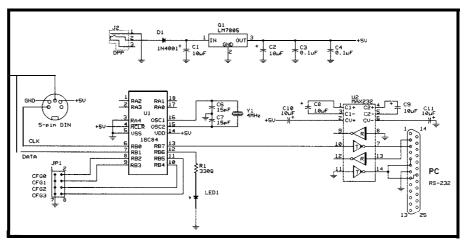

Figure 13a shows a general approach for converting analog video to SDTV.

The ATSC (Advanced Television Systems Committee) Digital Television Standard defines several data formats. One is 640 x 480 at 29.97 Hz, interlaced, which has a 4:3 aspect ratio. It was clearly designed for encoding the current American standard analog video.

Remember, the first several lines of 525-line analog video contain reference signals for diagnostic and automatic calibration purposes, so they don't need encoding.

You can use them to adjust the gains of your color circuits, but otherwise, they can be ignored. Use 480 of the lines below the calibration signals when encoding the picture.

Converting digital TV to analog is a bit trickier. Digital TV signals may be 640 x 480 SDTV, 1920 x 1080 HDTV,

or the somewhat less popular 1280  $\times$  720 and 704  $\times$  480 formats.

You need an intelligent decoder to figure out which format is being transmitted. Once you've done that, you can store the frame as an array in memory. Then, you need to process some (or all) of the data in this array and write it to a video RAM that produces 525-line analog video, as shown in Figure 13b.

When converting 1080-line HDTV to 525-line analog TV, you must decide if you want to simply discard every other line or average two adjacent lines together. (I suspect the former is the better choice.) You also need to decide if you want to throw away the right and left sides of the picture or shrink the picture and add black lines at the top and bottom.

#### MORE TECHNICAL INFO

Although this discussion barely scratches the surface, I hope you're now more familiar with the problems that need to be solved as well as the background material which the more advanced technical references assume you already know.

If you want to do some research on your own, start looking on the Internet. The HDTV standard adopted by the FCC is the one proposed by the Advanced Television Systems Committee [2].

MPEG's home page is a good place to get information on the MPEG-2 algorithm. This algorithm is at the heart of HDTV, and I really skimmed over it. It deserves a whole article all by itself.

DVD looks like a good candidate for recording digital television programs and movies. Work your way down the MPEG home page for a really good FAQ page.

Of course, lots of manufacturers have Web pages that bury useful information in with their sales pitches. Use your favorite search engine to look for ATSC, MPEG-2, DVD, or HDTV.

The sci.engr.television.advanced news group has an excellent information/flame ratio. Post specific questions, and you're sure to get good responses.

#### HOW WE GOT HERE

Our TV broadcast system is a legacy of 1950s technology.

Frame rates are tied to the powerline frequency and the persistency of phosphor. The picture area is driven by the compromise of fitting a rectangle in a circle. Every advance had to be backward-compatible with a 1950 TV.

Breaking tradition is hard. Backward compatibility is good, but there comes a time when you have to switch from DOS to Windows. It's painful at first, but once you make the change, you're free to do much more.

With HDTV, pictures will be clearer and screens larger. You can have fivechannel surround sound in your living room. Eventually, you'll be able to choose among different languages for some programs.

You will be able to store (and manipulate) the images in your computer. You can have picture-in-picture-inpicture-in-picture, so you can watch all the games (or soaps) at the same time. You can even watch TV while surfing the Internet. It is hard to imagine all the possibilities.

It's an exciting time to be working (for fun or profit) in the television or computer industry.  $\Box$

Do-While /ones has been employed in the defense industry since 1971. He has published more than 50 articles in a variety of popular computer magazines and has authored the book Ada in Action. You may reach him at do\_while@ridgecrest.ca.us.

#### REFERENCES

- A.G. Williams, Motorola general sales manager, quoted in "40 Years Ago in Electronic Design," *Electronic Design*, 45:8, 64, 1997.

- [2] ATSC, ATSC Digital Television Standard, Document A53, September 16, 1995.

ftp.atsc.org/pub/Standards/A53

#### Internet

DVD FAQs, www.mpeg.org/~tristan/ MPEG/dvd.html#dvd-intro sci.engr.television.advanced

#### IRS

401 **Very** Useful 402 Moderately Useful 403 Not Useful

## FEATURE ARTICLE

Mike Podanoffsky

# Compressing Audio and Video Over the Internet

With the advent of video technologies and the Internet, the plain old telephone service just doesn't cut it any more. Mike tells how a hardware/software codec maintains highperformance CD sound, full color, and highquality image size. uring the past year, I've been part of a team at PictureTel developing LiveLan 3.0, an Internet/Intranet video-conferencing system. As I'm sure you know, the Internet is a set of protocols (e.g., sockets, HTTP, ftp, news, gopher, and POP3 mail) that runs on top of basic TCP/IP.

Video conferencing over TCP/IP is based on the ITU H.323 standard. Other standards exist for video conferencing over ISDN (H.320) and POTS (H.324).

If you're in the market for H.323 products, there are other options. Microsoft is giving NetMeeting 2.0 away free as part of its Internet Explorer 4.0 suite, and Intel is pushing ProShare. Or, you could check out White Pine Software's popular Enhanced CU-See-Me system. All of these products require at least 32 MB of RAM and a Pentium processor for effective use.

With 28.8-kbps modems, it's difficult to achieve anything greater than 3 frames per second (fps) for gray images with little or no audio. You can appreciate this relatively low quality of service when you compare it to a 24-fps rate of motion pictures in the U.S. or to broadcast TV, which transmits color images at 30 fps in the U.S. and Japan and 25 fps in Europe.

For business-quality communications, you need 15-20 fps. This rate is difficult to sustain over typical T1 and T3 Internet connections using softwareonly video-conferencing systems.

PictureTel overcomes these limitations by using a hardware/software codec. This provides higher performance, including audio-CD sound, full color, and CIF [high quality) image size.

The codec is the heart of video conferencing. It's the component that compresses and decompresses video and audio datastreams.

The compression scheme is set by international standards and recommendations. Under H.323, the H.261 and H.263 proposal/standards define video codecs; G.711, G.721, G.722, G.723, G.728, and G.729 handle audio codecs; and H.245 defines how a call is established and capabilities exchanged.

Some of these protocols are also part of the ISDN and POTS standards, making it possible to communicate packets of data between different types of systems.

#### VIDEO COMPRESSION

H.261 video compression is essentially MPEG compression. This lossy compression scheme allows some information to be lost in order to gain substantial compression ratios (on the order of 10:1 to 20:1). Visible quality loss can be perceived at the higher compression ratios.

Under H.261 and H.263, there are two basic image sizes-CIF or QCIF. CIF (Common Intermediate Format] defines an image of 352 x 288 pixels, roughly 4" x 4", or one-quarter of an 800 x 600 screen. QCIF is 176 x 144 pixels, which is about one-quarter the size of a CIF image (-2" x 2").

Undersampling of color data is possible without perceptible loss because the human eye is far more sensitive to changes in brightness than color. Color frames are actually only 176 x 144 for CIF and 88 x 72 for QCIF. In other words, only a quarter of the color data is ever sampled, stored, or transmitted.

MPEG exploits motion detection as part of its compression algorithm. That is, successive frames in a videostream need only send and detect differences. Each transmitted frame, whether it's a full or fractional part of an image, is encoded using JPEG's Discrete Cosine Transform (DCT) compression.

The value in each MPEG frame is encoded using YUV-the same color representation system employed by video cameras. This system represents the value of luminance (brightness) as Y, followed by the blue and red chrominance. Green can be derived from these values.

Blue chrominance is always represented as the value of blue color minus the luminance value. Similarly, red chrominance is always represented as the value of red minus luminance.

This color coding technique creates values that can be converted to traditional RGB values via:

$$\begin{split} |Y'| &= 10.299 \ 0.587 \ 0.1141 \ |R| \\ |B' - Y'| &= | \ -0.299 \ -0.587 \ 0.8861 \ |G| \\ |R' - Y'| &= | \ 0.701 \ -0.587 \ 0.1141 \ |B| \end{split}$$

(Do-While Jones offers slightly different versions of these equations in "HDTV— The New Digital Direction," pp 10–21.)

MPEG frames are divided into 16-x16-pixel macroblocks. Each macroblock consists of four 8 x 8 luminance blocks and two 8 x 8 chrominance blocks-one for blue and one for red chrominance.

Each block is compressed using DCT. Macroblocks are created only if they represent a difference in motion.

Frames can be encoded in three types: intra-frames (I-frames), forward predicted frames (P-frames), and bidirectional predicted frames (B-frames).

Listing1 — This portion of the JPEG decoder shows how JPEG information is packed to take advantage of every bit. Four fables exist at the beginning of every JPEG file to store the actual DCT coefficients. The remainder of the frame uses offsets to these values, which further reduces the size of every image.

```

Huffman Decoder for dct_coeff_first and dct_coeff_next. It

examines the next 8 bits of the input stream and performs the

following cases:

'0000 0000'-examine 8 more bits (i.e., 16 bits total) and perform table lookup on dct_coeff_tbl_0.

0000 0001'-examine 4 more bits (i.e., 12 bits total) and perform

table lookup on dct_coeff_tbl_1.

0000 0010'-examine 2 more bits (i.e.,

10 bits total)

and perform

table lookup on dct_coeff_tbl_2.

'0000 0011'-examine 2 more bits (i.e.,

10 bits total) and perform

table lookup on dct_coeff_tbl_3.

Each time, one more bit is examined to determine sign of level.

static void decodeDCTCoeff

(unsigned short int *dct_coeff_tbl,

int *run,

unsi gned

int *level)

show bits32(next32bits);

flushed = 0;

/* show_bits8(index); */

index = next32bits >> 24;

if (index > 3){

value = dct coeff tbl[index];

*run = (value & RUN-MASK) >> RUN-SHIFT;

if (*run == END OF BLOCK) {

*level = END-OF-BLOCK; }

se if (index == 3)

index = next32bits >> 22;

/* show_bits10(index); */

value = dct_coeff_tbl_3[index & 31; }

else if (index) {

/* show_bits12(index); */

index = next32bits >> 20:

value = dct_coeff_tbl_1[index & 151: }

el se {

index = next32bits >> 16;

/* show_bits16(index); */

value = dct_coeff_tbl_0[index & 2551; }

*run = (value & RUN_MASK) >> RUN-SHIFT:

*level = (value & LEVEL-MASK) >> LEVEL-SHIFT:

flushed = (value & NUM_MASK) + 2;

if ((next32bits >> (32-flushed)) & 0x1) *level = -*level;

/* Update bitstream; */}

flush_bits(flushed);

```

An MPEG image always begins with an I-frame. These I-frames are inserted at regular intervals in the stream, usually every 400 ms.

This timing is crucial for synchronization. For instance, should the stream only contain differences, once some data becomes lost or corrupted, the remainder of the video is useless.

I-frames are encoded as a single image with no reference to past or future frames. The encoding scheme is similar to JPEG compression.

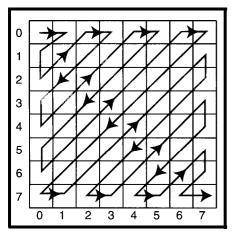

Each 8 x 8 block is encoded independently, and its values are transformed using a DCT, which separates the image into independent frequency bands. The resulting data is quantized and run-length encoded in a zigzag pattern, as shown in Figure 1.

If you take an image as shown in Table la, the coefficients produced by the DCT logic produce the result in Table 1b. Notice the unique zigzag pattern produced by the algorithm.

Quantization is the lossy part of JPEG compression. It reduces the size of the resulting data by removing the difference between like values.

So, if an image contains ten hues of red, they are reduced to three (or fewer). How much is removed from the datastream dictates how much compression is achieved.

A P-frame-or, forward-predicting frame-is encoded relative to the past reference frame, which is the closest preceding reference frame. It can be either a P- or an I-frame.

Each macroblock in a P-frame can be encoded as an I- or P-macroblock. An I-macroblock is encoded just like one in an I-frame. But, a P-macroblock is encoded as a 16 x 16 area of the past reference frame plus an error term.

To specify the 16 x 16 area of the reference frame, a motion vector is included. A motion vector (0, 0) means the 16 x 16 area is in the same position as the macroblock being encoded. Other motion vectors are relative to that position and may include half-pixel values, in which case, pixels are averaged.

The error term is encoded using the DCT, quantization, and run-length encoding. A macroblock may also be skipped, which is equivalent to a  $\{0, 0\}$  vector and an all-zero error term.

#### SOFTWARE

- C Cross Compilers

- Macro Assemblers

- Simulator Debuggers

- Integrated Development Environments (IDEs)

- Real Time Operating System (RTOS)

#### HARDWARE

- In-Circuit Emulators

- Eprom Programmers

#### CHIP SUPPORT

- 8051/251/930

- 80C51XA

- 68XXX / 68HC16

- Z80/Z180/64180

- 68HC05

- 68HC11 / 68HC12

- 8096 / 80196

- PIC 16 / 17CXX

- 6800 / 6801 / 6803

- 6500 / 6502

and Much Much More

Rockport, Maine 04856 USA sales@avocetsystems.com http://www.avocetsystems.com

(800) 448-8500

(207) 236-9055

The search for a good motion vector (i.e., one giving a small error term and good compression) is the heart of any MPEG video encoder. It's also the primary reason why encoders are slow.

A B-frame can be encoded relative to the past reference frame, the future reference frame, or both. The future reference frame is the closest following reference frame (I or P).

Encoding for B-frames is similar to P-frames, except motion vectors may refer to areas in the future reference frames. For macroblocks using both past and future reference frames, the two 16 x 16 areas are averaged.

Frames don't have to follow a static IPB pattern. Each individual frame can be of any type. For simplicity, however, a fixed IPB sequence is often used throughout the entire videostream.

Frames can also be sequenced in an IBBP BBP order. In this case, the B frames may depend on information in future P-frames, which is why they're referred to as future frames.

The codec may have two frames in memory-I and P-and may be sending B-frames that appear to the receiver to be referencing future frames. In other words, the sender may have sent frames in the order IBBP BBP BBP, but the receiver must process them in the order IPBB PBB PBB.

Obviously, B-frames aren't much good until the future frame arrives, but the transmission channel is used as soon as the information is available. Dead channel time gets wasted.

Since the encoding is figured out, let's try decoding. This article's source code includes MPEG and audiostream decoders, located in Vi deoConf. zi p. The MPEG code is taken from <br/>bmrc. berkeley.edu/projects/mpeg/mpeg\_play. html>.

Listing 2—Sound in ADPCM encoding (taken from a ud  $i_0 \setminus a$  dcpm. c) is represented as specific offset values from a base or step value. Those values are taken from the *i* n dex Tab 1 e array shown in step 5. The previous steps determine whether a new step is required.

for (; len > 0 ; len--){ val = \*i np++:diff = val - valpred; /\* Step 1-Compare with previous value \*/ sign = (diff < 0)? 8 : 0;if (sign) diff = (-diff); delta = 0;/\* Step Z-Divide : \*approx\* computes: \*/ vpdiff = (step >> 3);/\* delta = diff\*4/step; \*/ if (diff >= step) { /\* and vpdiff = (delta+0.5)\*step/4; \*/ delta = 4: diff -= step; vpdiff += step; } step  $\rightarrow = 1;$ /\* shift >> step by 1 \*/ if (diff >= step) { delta |= 2: diff -= step; vpdiff += step; } step  $\rangle\rangle=1;$ /\* shift >> step by 1 \*/ if (diff >= step) { delta |= 1; vpdiff += step; } i f (sign) /\* Step 3-Update previous value \*/ valpred -= vpdiff; el se valpred += vpdiff; if (valpred > 32767) /\* Step 4-Clamp prev value to 16 bits \*/ val pred = 32767;else if (valpred < -32768) val pred = -32768;/\* Step 5-Update index and step values \*/ delta = sign;index += indexTable[delta]; if (index < 0) index = 0; if (index > 88) index = 88;step = stepsizeTable[index]; if (bufferstep) /\* Step 6-Output value \*/ outputbuffer = (delta << 4) & 0xf0;el se \*outp++ = (delta & 0x0f)| outputbuffer; bufferstep = !bufferstep;}

Figure 1—The Discrete Cosine Transform used by JPEG converts pixel information into coefficients in cosine functions. These values are usually distributed in a zigzag pattern. The encoder takes advantageof this by ordering the coefficients in this pattern to eliminate all unnecessary zeros.

The code is thorough, fairly well documented, and very useful in analyzing MPEG streams. It's written for Unix and X/Windows and has not been ported to Windows, but it should run under Linux. (I didn't write this code, so please don't call me with problems.)

The MPEG macroblock decoder, where everything starts, is handled by the ParseMacroBlock functionin **mpeg\vi deo.** C. It decodes macroblocks and reconstructs motion vectors, which in turn leads to reconstructing DCT values and setting pixel values.

The code that decodes the DCT values from the input stream is more interesting. It is handled by decode - **DCTCoeffinmpeg\decoders.c.** Listing 1 shows a portion of this code.

As you can see, an MPEG image has lots of control information and manipulation of bits. Bandwidth shouldn't be wasted, even at the expense of computer time.

#### AUDIO COMPRESSION

The human ear is much more sensitive than the human eye. Hearing can typically perceive frequencies between 20 Hz and 20 kHz, with the human voice capable of producing frequencies between 40 Hz and 4 kHz. For desktop video-conferencing systems, the challenge is reproducing the highest fidelity of sound in real time. To faithfully reproduce a signal, it must be sampled at twice the highest frequency. The high-quality audio of audio CDs is sampled at nearly 44 kHz, while the telephone samples voice at 8 kHz. Encoding the entire 8-kHz range requires at least 12 bits of data.

To achieve compression, 256 values are selected that can be encoded in 8 bits. Since human voice is concentrated at the lower frequencies, the algorithm uses a logarithmic scale to determine which frequencies to code.

Each value in the raw analog input is mapped to the closest lower frequency in a technique called Pulse Code Modulation (PCM). **G. 711** uses this technique to encode audio and achieves a 1.5: 1 compression ratio (12:8 bits).

Two different logarithmic curves are used as standards-u-law and a-law. u-law is used in North America and Japan, while a-law is used elsewhere.

Neither one really has a technical advantage over the other. They reproduce audio slightly differently, and any preferences between them tend to be based primarily on personal taste.

A sampling rate of 8 kHz encoded as 8-bit data using a single mono channel requires a bandwidth of 64 kbps-much higher than a 28.8-kbps modem can sustain. Some compression is necessary.

Experience shows that adjacent values in an audiostream can be similar to each other. Moreover, a sample's value can be predicted with some accuracy using the value of adjacent samples.

ADPCM (Adaptive Differential Pulse Code Modulation) encodes the differences between the predicted and actual values of a sample. In G.721, these differences are encoded as 4-bit values, requiring only 32 kbps. G.723 uses the same technique to provide 24- and

|        |   |   |   |     |     |    | - |   | -  |     |   |     |     |     |     |     |      |

|--------|---|---|---|-----|-----|----|---|---|----|-----|---|-----|-----|-----|-----|-----|------|

| a)     |   | 0 | 1 | 123 | 345 | 56 |   | 7 | b) | 0   | 1 | 2   | 3   | 4   | 5   | 6   | 7    |

| 0      | 0 | 0 | 0 | 0   | 1   | 0  | 0 | 0 | 0  | 4   |   | 0 - | 2 ( | 0   |     | 0(  | ) () |

| 1      | Ō | Ō | 0 | 1   | 1   | 1  | 0 | 0 | ľ  | 0.  |   |     |     |     |     |     |      |

| 2<br>3 | 0 | 0 | 1 | 1   | 1   | 1  | 1 | 0 | 2  | - 2 |   | 0   |     | 0 ( | ) 1 | 0.0 | 0 (  |

| 3      | 0 |   |   |     |     |    |   |   | 3  | 0   | 1 | 0 ( | 0 ( | ) - | 1   | 0   | 0    |

| 4      | 1 | 1 | 1 | 1   | 1   | 1  | 1 | 0 | 4  | 0   | 0 | 1   | 0   | 0   | 0   | 0   | 0    |

| 5      | 0 | 1 | 1 | 1   | 1   | 1  | 0 | 0 | 5  | 0 ( | 0 | 0 - | - 1 | 0   | 0   | 0   | 1    |

Table 1 -A simple pixel image (a) will convert to the coefficients shown in (b). All coefficients are stored in one of several fables located at the start of a JPEG file. All references to values in frames are represented as offsets in these fables.

6

0 0 0 0 0 0 0 0

0 0 0 0 0 1 0 1

0

40-kbps audiostreams. These all use 3 and 5 bits for encoding audiostreams.

G.722, developed by AT&T in the U.S. and CNET in France, is another standard using ADPCM. It samples data at a higher 16-kHz rate and then divides this data into two channels-one for higher and one for lower frequencies.

It uses 8 bits to encode differences. The output is Huffmanized (run-length encoded) and can be transmitted on one or two channels simultaneously, providing a 4: 1 compression ratio.

Audio compression is a little more readable, so let's take a look. This example is similar to that used in G.721 and is also easier. Listing 2 is part of audio\adcpm cfromVideoConf. zip.

ADPCM is encoded by taking the difference between the current and previous values. The difference value may be too large to encode in 4 bits, so a step value is adopted, which forms the basis for future values.

When a call is placed, it's unlikely that both systems will have the same capabilities. Given the likelihood of mismatched systems, using the H.245 standard is probably best. It recognizes and negotiates the best-quality audio and video possible.

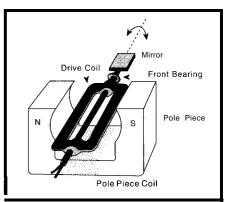

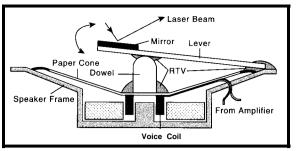

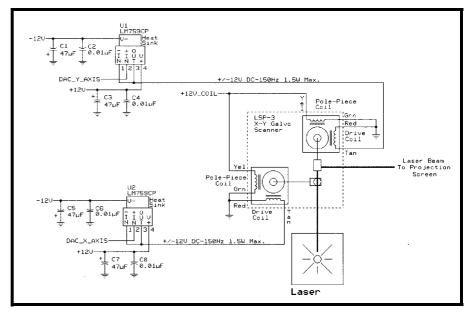

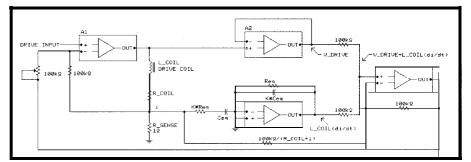

When two systems connect under H.245, they select a random wait time. One system wins and drives the process of finding the best quality of service based on an exchange of capabilities.