# MREDDED C MONTHLY SECTION

# THE COMPUTER APPLICATIONS JOURNAL #89 DECEMBER 1997 DEBUGGING TECHNIQUES

Test

est

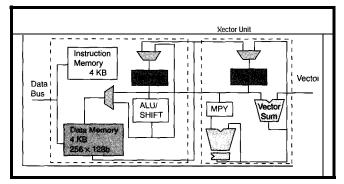

The Zen of BDM

**Remap Your Keyboard**

Logic Analyzers— Two Construction Projects

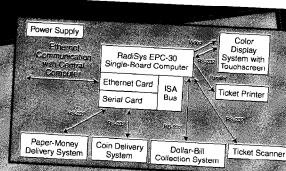

EPC: Meet EPC Design Contest Winners

HOUSE & GAR Made We

> \$3.95 U.S. \$4.95 Canada

### No Slowing Down

ince I only write one guest editorial a year, it always makes me nostalgic. I think about columnists who have come and gone. I recall frantic moments when a photo isn't in and we're shipping to press. I start to remember a long time ago when I had far fewer phone calls and interruptions, and I'm pining for the "simpler" life.

However, the reverie is short. In truth, I like action and am thrilled to have been a part of the changes that have taken place in INK over the three and a half years I've been on staff. It's good to see that companies now fully recognize that we have good readers who know a lot about designing things. Suddenly, they want to sponsor contests, advertise, send editorial.... Our pages fill up fast.

In 1997, probably the most gutsy thing INK did was sponsor the Embedded PC Design Contest. Although we had companies interested in advertising in EPC, the section was new. But, in the bold tradition of INK, we gambled. We decided that if anyone was going to lead the embedded industry it should be us. We knew that if we could organize a contest that made sense, you'd come through for us.

And you did. Take a look at the projects that won prizes. There are some very impressive, marketable products in that lot. I know two of the winners are already seeking corporate sponsorship of their designs. More power to them. It's to encourage this kind of enterprise that *INK* continues to support embedded design contests.

In 1998, Circuit Cellar INK will continue to look for opportunities for growth. In Embedded PC, for instance, while Rick Lehrbaum will keep on bringing us updates on trends with PC/104 and the embedded-PC world, he'll be joining us as an EPC feature author. Many thanks to Rick for a splendid job anchoring PC/I 04 Quarter.

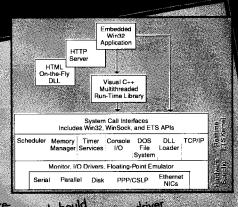

What are we putting in its place? RPC-Real-Time PC-a column dedicated to helping you get to know all there is to know about real-time operating systems. We're placing this column in the EPC section since a high percentage of embedded-PC implementations fall into real-time control.

However, as always, we approach technology by offering a multiprocessor approach. If you make RTOSs for nonPC processors, we want to hear your angle on real-time issues as well. Just send your proposals and manuscripts in.

But enough on what's to come. Let's take a look at what's already here. Craig Haller kicks off this Debugging Techniques issue by giving an overview of on-chip debugging, while Ingo Cyliax zeros in on ColdFire's serial BDM interface. Frustrated with the limitations of low-cost logic analyzers, Janusz Mlodzianowski builds his own, and Cheng-Yang Tan, unwilling to have his keyboard settings dictated to him, remaps it for his own purposes.

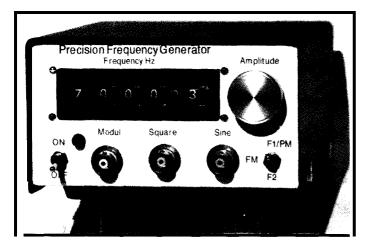

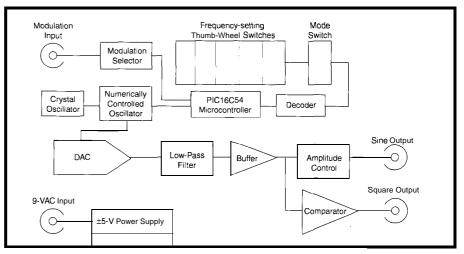

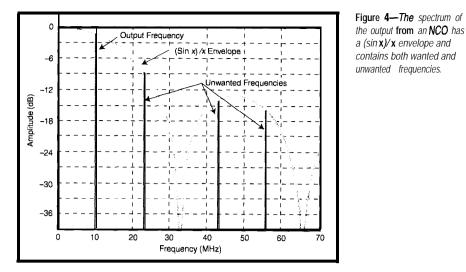

Tom Napier opens a new MicroSeries on NCOs. He spends his first column discussing the manipulation of wave signals. Jeff makes magnetic field strength audible, and Tom checks into another Hot Chips conference.

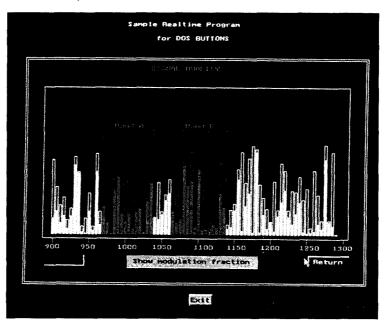

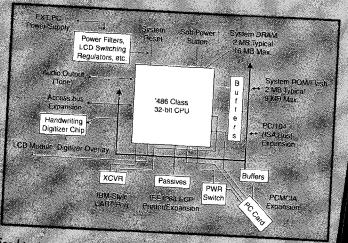

In EPC, after I give you a glimpse of the Embedded PC Design Contest winners, Francis Deck introduces you to a high-speed logic analyzer for Windows 95. Rick closes PC/104 Quarter by showing how embedded PCs get bolstered to take on the environment, and Fred simulates a paper-tape reader for an industrial milling machine.

### janice.hughes@circuitcellar.com

THE COMPUTER APPLICATIONS JOURNAL

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

EDITOR-IN-CHIEF Ken Davidson

MANAGING EDITOR Janice Hughes

TECHNICAL EDITOR Elizabeth Laurencot

ENGINEERING STAFF Jeff Bachiochi

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Rick Lehrbaum Fred Eady

NEW PRODUCTS EDITOR Harv Weiner

ART DIRECTOR KC Zienka

PRODUCTION STAFF John Gorsky James Soussounis

ASSOCIATE PUBLISHER Sue (Hodge) Skolnick

CIRCULATION'MANAGER Rose Mansella

> BUSINESS MANAGER Jeannette Walters

ADVERTISING COORDINATOR Valerie Luster

CIRCUIT CELLAR INK®, THE COMPUTER APPLICA TIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 6752751. Periodical rates paid at Vernon, CT and additional offices. One. year (12 issues) subscription rate U.S.A. and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. All subscription orders payable in U.S. funds only, via international postal money order or check drawn on U.S. bank.

VISIT OUR WEB SITE FOR SUBSCRIPTION INFORMATION AT www.circuitcellar.com Direct subscription orders and subscription related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301. POSTMASTER: Please send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043.9613.

Cover photograph Ron Meadows - Meadows Marketing PRINTED IN THE UNITED STATES

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

### **HAJAR ASSOCIATES** NATIONAL ADVERTISING REPRESENTATIVES

| NORTHEAST &                                            | MIDWEST&SOUTHEAST             | WEST COAST                                            |

|--------------------------------------------------------|-------------------------------|-------------------------------------------------------|

| MID-ATLANTIC                                           | Christa Collins               | Barbara Jones                                         |

| Barbara (Best) <b>Curley</b>                           | (954) 966-3939                | &Shelley Rainey                                       |

| (561) 694.2044                                         | Fax: (954) 965-6457           | (714) 540-3554                                        |

| Fax: (561) 694-2051                                    | HaiarChrista@wordnet.att.net  | Fax: (714) 540-7103                                   |

| Fax: (561) 694-2051<br>b.curley-Hajar@worldnet.att.net | HajarChrista@worldnet.att.net | Fax: (/14) 540-7103<br>shelley.hajar@worldnet.att.net |

Circuit Cellar BBS-24 Hrs., 2400/9600/14.4k bps, 6 bits, no panty. 1 stop bit, (860)871-1988. For information, mail to info@circuitcellar.com. World Wide Web: www.circuitcellar.com

All programs and schematics in Circuit Cellar INK® have been carefully reviewed to ensure their performance is in accordance with the specifications described, and programs are posted on the Circuit Cellar BBS for electronic transfer by subscribers

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK®

Entire contents copyright © 1997 by Circuit Cellar Incorporated, All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# **READER I/O**

### APOLOGYTOREADERS

We at Dartmouth Printing Company extend our apologies to you for the unfortunate omission of editorial copy and the advertisement for R4 Systems that occurred within Jeff Bachiochi's article on page 76 of the November 1997 issue. The magazine you received is not representative of the quality that normally leaves our plant.

Tim Gates Dartmouth Printing Company

Jeff's November column, "Nonintrusive Interfacing— Using Kid Gloves," and R4 System's advertisement are available in their entirety via the Circuit Cellar Web site in both viewable and downloadable formats.

Editor

### **BIG GUNS**

I enjoyed Do-While Jones' "HDTV-The New Digital Direction" *[INK* 86], but I had one small comment. The author said he doubted that it would be practical to build a CRT with 1080 guns. In fact, there are a couple companies doing just that with even more "guns," although perhaps in a different sense than he described.

A new technology-Field Emission-uses microscopic pyramids of emitters, multiple pyramids per pixel, a fraction of an inch from the phosphors. It uses x-y drivers to put a high voltage on a batch of emitters for a particular pixel which emit the electrons that are accelerated to the screen with another voltage (like to a regular CRT). This way, you have the potential for high resolution and high brightness in a flat screen. I'm not certain if any of this is in production yet, but I've seen several articles in *Electronic Engineering Times* about the technology.

Bob Bass rpbassQionet.net

I was referring to a traditional CRT (a large vacuum tube with filament-heated cathodes, many inches from the screen). I agree that new technology, such as you describe, might find its way into living rooms some day.

**Do- While** Jones do\_while@ridgecrest.ca.us

### **BUT I ALREADY KNEW THAT!**

During my Thursday class on "Fuzzy Logic Technology in Appliances" at this year's ESC-West, Constantin von Altrock put a viewcell on the overhead projector and said, "This is a great magazine in which to learn more about fuzzy-logic designs." It was Circuit *Cellar INK*!

So, at least 200 engineers saw your magazine cover that day! I had to smile to myself because the latest issue was waiting back in my hotel room for me to read that night.

Stephen **Buol** Cedar Rapids, IA

### AMPLITUDE ERROR

I enjoyed reading Mike Podanoffsky's article ("Compressing Audio and Video Over the Internet," *INK 86*) until I came to the section on audio PCM encoding. The a- and n-law codecs have variable *amplitude* encodings, not frequency. Higher frequencies tend to have smaller amplitudes, but the codecs don't inherently know that.

Analog or digital band-pass filtering is used to shape the spectrum being encoded. Offhand, I can't provide any specific references, unless you want to go back to the early Bell Labs Technical Journals of the late '50s and early '60s and the T1 carrier channel banks.

Roger J. Pryor rjpryor@unix.infoserve.net

I stand corrected. The a- and p-law codecs have variable amplitude encoding. The reference was my error in describing the compression. Thank you for pointing it out.

Mike Podanoffsky mikep@world.std.com

### **HDTV THANKS**

Thanks for Do-While Jones' "HDTV—The New Digital Direction" (*INK 86*). It's the most informative article I've read in *INK* in a while. It did a good job of filling in some holes in my knowledge base. Keep up the good work!

Mark Nelson markn @ tiny.com

STATEMENT REQUIRED BY THE ACT OF AUGUST 12, 1970, TITLE 39, UNITED STATES CODE SHOWING THE OWNERSHIP, MANAGEMENT AND CIRCULATION OF CIRCUIT CELLAR INK, THE COMPUTER APPLICATIONS JOURNAL, published monthy at 4 Park Street, Vernon, CT 06066. Annual subscription price is \$21 95. The names and addresses of the Publisher, Editorial Director, and Editor-in-Chief are: Publisher, Steven Ciarcia, 4 Park Street, Vernon, CT 06066. The names and addresses of the Publisher, Editorial Director, and Editor-in-Chief are: Publisher, Steven Ciarcia, 4 Park Street, Vernon, CT 06066. The names and addresses of the Publisher, Editorial Director, and editor-in-Chief are: Publisher, Steven Ciarcia, 4 Park Street, Vernon, CT 06066. The awarage number of copies of each issue during the preceding weble months are: AT Total number of objects printed (net press un) 33283, IP Jacid Circulation (1) Sales through dealers and carriers, street vendors and counter sales : 4,751, (2) Maii subscriptions: 22,810; C) Total pied circulation: 9,551: D) Free distribution varial (samples, complimentary and other free): 4,424; E) Free distribution outside the mail (carrier, or other means): 150; F) Total tree distribution: 4,974; G) Total Distribution: 3,935; H) Copies not distributed: (1) Otal unuber of copies printed (net press run) 37,000; B) paid Circulation: 17,500; B) paid Circulation: 9,7500; B) paid Circulation: 3,942; G) Total tree distribution outside the mail (carrier, or other means); C; F) Total tree distribution and currer sales: 4,707, (2) Maii subscriptions: 20,317, (2) Total paid circulation: 25,024; D) Free distribution: 3,423; H) Total tree distribution: 3,992; G) Total tree distribution: 3,423; H) Total tree distribution: 3,992; G) Total tree distr

### DIGITAL THERMOMETER AND MEMORY

The DS1624 Digital Thermometer and Memory IC combines a digital temperature sensor and 256 bytes of EEPROM on chip to store temperature-related compensation information. The chip converts temperature directly, climinating the need for an ADC, and it is calibrated at the factory. No external components are required, and the chip does not consume microcontroller resources. Applications include temperature-compensated crystal oscillators for test equipment and radio systems.

The thermometer provides 13-bit temperature readings (two-byte transfer), which indicate the temperature of the device. It measures temperature from -55°C to +125°C in 0.03125°C steps. Thermometer accuracy is 05°C across the 0-70°C range. Tempcraturc is converted to a digital word in less than 1 s and read or written via the popular two-wire bus architecture. This architecturc features three-bit addressability, which permits users to multidrop up to eight chips along the bus.

The DS 1624 operates from 2.7 to 5.5 V and is available in either eight-pin PDIP or eight-pin SOIC packages. The PDIP package sells for \$3.40 in quantity.

Dallas Semiconductor 4401 S. **Beltwood** Pkwy. Dallas, TX 75244-3292 (972) 371-4448 Fax: (972) 371-3715 www.dalsemi.com

#501

### DATA-ACQUISITION ADAPTER

The LPT:Analog! model 8c-I/O is a low-cost 12-bit data-acquisition adapter for the PC parallel printer port. The device features an 8-channel12-bit ADC with user-selectable input ranges, two 12-bit DACs, and two 100-µA current sources for direct sensor excitation, as well as an uncommitted current mirror and multiple digital I/O lines.

The device is designed primarily as a universal sensor interface, and the supplied signal conditioning information makes it easy to collect data from analog output instruments, sensors, 4–20-mA loops, and many other analog signal sources at rates of up to 7500 samples per second. The DACs and digital I/O lines onboard arc ideal for automatic sensor offset cancellation (auto-zero), as well as for real-time control applications.

LPT:*Analog!* is supplied with drivers, data-acquisition utilities, programming examples (QuickBASIC), and VB DLLs at no extra cost. The adapter sells for \$99.

ADNAV Electronics 58 Chicory Ct. Lake Jackson, TX 77566 (409) 292-0988 www.tgn.net/~adnav

#502

### DATA-ACQUISITION MODULES

New data-acquisition modules from B&B Electronics can receive signals from up to eight external sensors, control various devices, and output analog voltages. The compact modules plug into DB-25 serial ports. Applications include monitoring sensors, controlling process and test equipment, and monitoring and controlling on/off states.

RS-232 and RS-485 modules have the ability to interface seven A/D channels, two digital input channels, one digital output channel, and four channels of eight-bit D/A outputs. Only four commands are needed to control the modules. For applications where long wire runs arc required or a lot of line noise may be encountered, there are two 4-20-mA current-loop models. Serial Port MD, DJA with 4-20 m Current Loop On 8 E Eler

Pricing for the four data-acquisition modules in the series ranges from \$89.95 to \$109.95. Each module comes complete with a demo program and API programs.

**B&B Electronics Mfg. Co.** 707 Dayton Rd. Ottawa, IL 61350 (815) 433-5100 Fax: (815) 434-7094 sales8 bb-elec.com www.bb-elec.com

### **GRAPHICS CONTROLLER CHIP**

The SED1354 is a low-cost, low-power color/monochrome LCD/CRT controller interfacing to a wide range of CPUs and LCDs. Its virtual display and split-screen capability is intended for embedded applications such as office automation equipment and mobile communication devices.

The SED1354 supports LCD interfaces with data widths up to 16 bits. Using frame rate modulation, it can display 16 shades of gray on monochrome LCD panels, up to 4096 colors on passive color LCD, and 64K colors on active-matrix TFT LCD pancls. CRT support is handled via an external RAMDAC interface, enabling simultaneous display of both the CRT and LCD panels. A 16-bit memory interface supports up to 2 MB of EDO or FPM (fast page mode) DRAM.

and so forth. The SED1354 sells for \$9.70 in high volume. S-MOS Systems

150 River Oaks Pkwy. San Jose, CA 95134-I 951 (408) 922-0200 Fax: (408) 922-0238 literature@smos.com www.smos.com

#503

#504

Flexible operating voltages from 2.7 to 5.5 V provide for very low power consumption. Power consumption is reduced through the USC of two power-down modes-one hardware and one software. Additionally, LCD powersequencing signals are provided by the SED1354 to control an external LCD BIAS power supply, LCD backlight,

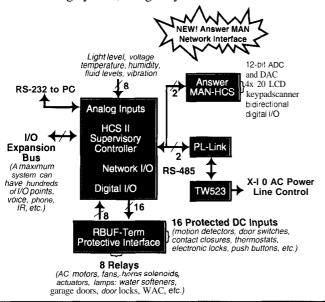

### C-PROGRAMMABLE CONTROLLER

The BL1700 is a C-programmable controller that's ideal for machine control, embedded systems, and OEM applications. It features 32 digital I/O lines (16 protected inputs and 16 high-current outputs), 10 A/D inputs, an 18-MHz processor, four duplex serial ports, LCD and expansion-bus ports, and DIN rail mounting. Up to 256 KB of nonvolatile flash memory facilitates in-system programming.

Programming the BL1700 controller is accomplished via Z-World's Dynamic C-a C programming language optimized for real-time, multitasking control. Dynamic C is an integrated software-development system providing an editor, compiler, and interactive debugger. The software comes with prewritten functions and software drivers.

The BL1700 is available with a development kit that includes a manual, schematic, programming cable, power

The BL 1700 includes conditioned analog inputs that interface directly with a variety of devices (c.g., photosensors, temperature and pressure sensors, and strain gauges). It also fcatures digital outputs that directly drive solenoids and relays, and it can instantly add digital I/O, displays, relays, and D/A channels using the LCD and expansion-bus ports.

supply, 128 KB of flash memory, and three standard wiring terminal blocks. The BL1700 is priced at \$199 in quantity.

Z-World 2900 Spaff ord St. Davis, CA 95616 (916) 757-3737 Fax: (916) 753-5141 www.zworld.com

#505

Web: http://www.LinkInstruments.com/cci12 · Email: Sales@LinkInstruments.com

### COMPACT NETWORK SERVER

The Secure Network Interface (SNI) provides simple server-based real-time management of RS-232-compatible devices and Intranet/Internet networks. This Ethernet "micronode" has a discrete IP address, and the TCP/IP stack supports FTP, HTTP, SMTP, and telnet protocols. It provides many of the capabilities of larger servers and does not require a Mac or PC. The SNI is user programmable via enhanced BASIC using a remote HTML-compatible browser over the network.

Applications include creation of HTTP Web sites for serial devices, providing configuration and data-publishing capabilities over a network, replacement of bulky PC-based servers with an inexpensive and compact device, and remote access for troubleshooting. A demonstration is available at <weather.dawning.com>.

The SNI contains a 40-MHz16-bit 'x86-compatible processor and 1-MB nonvolatile memory. It has an RJ-45 eight-pin RS-232 connection and is switch selectable for DCE or DTE communications. The network connection is 10 Mbps and can be either 10Base2 or 10BaseT. A 30-W wall transformer providing 12 VAC is included. The SNI sells for \$595.

LOW COST., LOW POWER., OEM (1K) PRICE \$1.99 EVAL KIT 7.00 A LOWER COST. FASTER. EASIER TO PROGRAM SINGLE CHIP COMPUTER 16C54 COMPARE: MVI200 PINOUT: OEM (1K) PRICE \$2.57 \$1.99 NO YES PROGRAM DOWNLOAD RESET 20 VCC SINGLE CHIP OPERATION NO YES PD0 2 19 PB7 BUILT-IN BASIC NO YES PD1 3 18 PB6 EEPROM DATA MEMORY NONE 64 XOUT 17 PB5 PROGRAM MEMORY 768 OTP 1K FLASH XIN 5 16 PR4 MATH REGISTERS PD2/INT 32 6 7 15 PB3 14 MAX INSTRUCTIONS/SEC -5M 20M PD3 PB2 MAX COUNTER BITS 16 18 PD4/TMR 8 13 PB1/AD1 INPUT / OUTPUT BITS 12 15 PD5 9 12 PB0/AD0 YES GND 10 PD6 11 A TO D COMPARATOR NO HARDWARE INTERRUPTS NONE 3 - LONGER WORD INSTRUCTION-FRIENDLY SYMMETRIC ARCHITECTURE REDIT CARD OEM (1K) PRICE EVAL KIT \$75.00 -SER PROGRAM DOWNLOAD -256kb NONVOLATILE MEM. -LCD / KEYPAD INTERFACE -ISA BUS (MODEM, MEM, ETC.) -RS232/485 SERIAL TO 115.2KB -ASSEMBLY / BUILT-IN BASIC -100 MICROAMP OPERATION MVS BOX 850 MERRIMACK,NH 03054 5vr Limited Warrantv Free Shipping (508) 792-9507

Hrs: Mon-Fri 10-6 EST

Dawning Technologies, Inc. 409 Mason Rd. Fairport, NY 14450 (716) 223-6006 • Fax: (716) 223-8615 sales@dawning.com • www.dawning.com

#506

## Think *Circuit Cellar INK* is a great technical resource?

Do you know anyone who might appreciate it just as much?

Most subscribers get to know us by reading someone else's copy. Satisfied readers are our best supporters.

We'll send you a bunch of complimentary copies so you can show us off. Give us your name, where you live, and how many you need.

Contact Rose Mansella (860) 8752199 rose.mansella@circuitcellar.com

Thanks for your Shipping costs for all foreign and Canadiancomplimentary copies must be prepaid by credit card

# <u>FEA</u>TURES

| 12 | The Zen of <b>BDM</b>                   |

|----|-----------------------------------------|

| 20 | Serial BDM Interface for<br>ColdFire    |

| 28 | A Simple Multipurpose<br>Logic Analyzer |

| 62 | A Hardware Keyboard<br><b>Remapper</b>  |

# FEATURE ARTICLE

### Craig Haller

# The Zen of BDM On-Chip Debugging

Still doing the old crash and burn debugging? Perhaps it's time to try your hand at debugging with on-chip resources. In Craig's opinion, it's the safest way to avoid intrusive overhead that alters the way your code runs. verybody's talking about BDM (Background Debug Mode). But, what is it

really? What is the essence of BDM? Strictly speaking, "BDM" is Motorola's term for a method of debugging and refers to a hardware port on their microcontroller chips. Other manufacturers use JTAG (IBM), OnCE (Motorola's On-Chip Emulation), MPSD (TI), and EJTAG (MIPS) ports, but many still call it BDM debugging.

For clarity, I refer to it as on-chip debugging (OCD). OCD includes various methods of using on-chip resources that enable complete software debug and aid in hardware debug.

In this article, I review OCD, what it is, and how to use it effectively.

### WHAT'S OCD?

OCD is the latest addition to the debugger arsenal, which already includes the basic crash-and-burn debugging, hardware single stepping, ROM monitors and emulators, as well as incircuit emulators (ICEs).

Early on-chip debuggers were debug monitors written into the microcode of the target processor (Motorola's CPU32). More advanced systems added features like real-time reading of the program counter [Analog Devices' SHARC processor) and near-real-time reading of memory locations (Motorola's ColdFire).

OCD permits code download, reading and writing memory and processor resources, single stepping, processor reset, and status (running or halted). On-chip peripherals may be set to shut down during OCD (as opposed to while the chip is executing user code).

Some processors enhance OCD with other resources. IBM's '4xx PowerPC embedded processors have a seven-wire interface (RISCTrace) in addition to the OCD (RISCWatch), enabling a complete trace of processor execution. By capturing these lines in real time, a debugger can display a full trace of the last x instructions executed.

The new OCD standard for MIPS processors-Extended JTAG (EJTAG) can retrieve a complete program trace as well as standard debug commands.

There arc only a few drawbacks to OCD. The target usually needs RAM instead of ROM for debugging, and there is typically (not always) no form of real-time tracc.

### OCD HARDWARE AND SOFTWARE

In the general sense, OCD is a combination of hardware and software, both on and off chip.

On-chip OCD may be a microcodebased monitor (Motorola CPU32) or hardware-implemented resource (IBM PPC4xx). There may be resources available for the end user's code (e.g., breakpoint registers) or dedicated hardware (e.g., instruction stuff buffers), as with embedded PowerPC implementations.

OCD needs minimal external hardware. The chips and debugger host must communicate, often via a dual-row pin header and several pins on the processor.

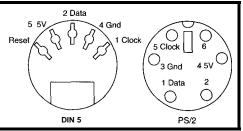

The IBM '4xx and '6xx families use JTAG port pins in addition to reset, power sense, and ground, and connect via a 16-pin dual-row header, as shown in Figure 1. Motorola BDM uses five dedicated pins (sometimes multiplexed with real-time execution functions), power, ground, and at least one reset, all terminating in a IO-pin dual-row header.

Many DSP chips use a TI-style standard JTAG interface. Motorola expanded the interface's internal definition to include its DSP BDM equivalent, OnCE. But, on-chip resources are only half the story. A target with an OCD processor and its dual-row header is useless without a host to communicate with.

The host runs the debugger software and interfaces to the OCD header. The debugger implements the user interface, displaying your code, processor resources, target memory, and so on.

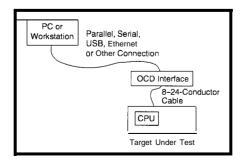

The simplest hardware interface is a wiggler-a device that interfaces the parallel port of an IBM-type PC to an OCD header. It's both simple and slow. Other interfaces are scrial port (RS-232) to OCD converters, high-speed parallel port to OCD, Ethernet to OCD, ISA-bus card to OCD, and others (see Figure 2).

Cost of host software runs from \$49 to several thousand dollars. Hardware cost ranges from \$100 to \$5000.

### BDM AS OCD

Motorola coined the term BDM with its CPU32 family of controllers, which was followed by the CPU16 family and ColdFire. These BDMs build on the concept of a ROM monitor and have a similar command set. The core of the hardware interface consists of a serial data in, serial data out, serial clock/ breakpoint, and freeze status signal.

The commands are shifted into the chip serially and are 17 bits long. Table 1 lists the command set for the CPU32.

These commands closely mirror those used for years in ROM monitors. Single stepping is accomplished via hardware control of the BDM port or by software breakpoints in the codestream.

The processor is unaware of the BDM engine. It is not seen as an exception or interrupt. The background instruction **B** GN D causes the processor to enter BDM. When GO is executed, BDM is exited and real-time code execution resumes.

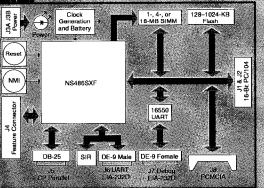

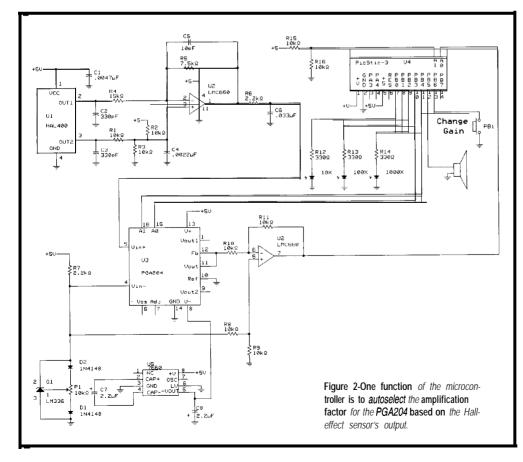

Figure 2—OCD interfaces come in many styles. All sit between a host-based debugger and the target.

| TDO    | • • | NC           |

|--------|-----|--------------|

| TDI    | • • | Reset        |

| QREQ   | • • | Power Source |

| TCK    | • • | NC           |

| TMS    | • • | NC           |

| SRST   | • • | GND          |

| HRST   | • 0 | No Pin (Key) |

| CHKSTP | • • | GND          |

|        |     |              |

Figure 1 -- This '6xx PowerPC pinout is typical of OCD pinouts. Most OCD processors have unique connections.

The embedded PowerPC BDM (Motorola MPC5xx, MPC8xx) works quite differently from the CPU32 type of BDM. The hardware interface is similar, but there isn't a specific command set.

Any serial stream entered is 7 or 32 bits in length (except for start, control, and length bits). The 32-bit bitstreams go into the instruction stuff register and come out the debug data register.

The host debugger stuffs PowerPC opcodes into the processor to be executed. This powerful design enables all system resources to be accessible, since the debug port has the same power as executing system code.

The 7-bit datastreams control on-chip breakpoint functions. Debug control registers exist to enable single stepping and other special controls.

The processor is aware of this BDM since it's a CPU exception. BDM may be entered on one of any number of exception-causing events (e.g., invalid opcode, address bus misalignment, nonmaskable interrupt, etc.) To resume real-time execution, the debugger stuffs a returnfrom-exception instruction (RF I) into the processor's instruction register.

### **ON-CHIP EMULATION**

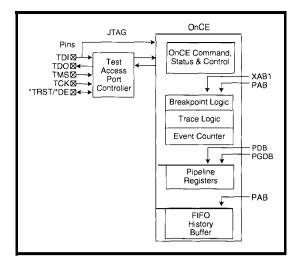

The OnCE interface on Motorola's DSP chip family enables the same types of debugging as the BDM interface. On most chips, the OnCE interface is implemented via dedicated pins. More recently, it's accessed via JTAG port pins as illustrated in Figure 3.

The OnCE port is more complex than the BDM port since it's a state machine controlled by the external debugger. Table 2 lists its capabilities.

### JTAG DEBUGGING

The JTAG specification (IEEE 1149.1) is a method of doing full chip testing and was originally implemented to

enable testing of all the pin connections of a chip and its interconnections to other chips on the printed circuit board.

It's a serial protocol, and chips on the board may be daisy-chained together. In simple terms, the JTAG serial chain through the chip may bc wired through any on-chip devices but minimally connects to all I/O pins and buffers.

The chain may be several score long to thousands of elements. There is no specification stating any inclusion of resources for software debug, nor is there a prohibition.

Various processors implement OCD via JTAG differently. The 600series PowerPCs use the hardware test chain, which winds its way through many on-chip resources. Somewhere in the multithousandstage serial chain is the instruction register, for example.

Debugging with this system is tedious since each core OCD action may take many trips through the entire JTAG chain. Although the debugger may only want a 32-bit piece of the chain, all elements must be traversed multiple times. Downloading user code may run less than 100 Bps

(vs. over 40 kBps with other methods). Another drawback of a shared hardware test/software debug chain is the

way the chain is routed during chip design. Since this part of the design is typically the least critical, designers let the silicon autorouter lay out the chain's path after the rest of the chip is laid out.

Therefore, each revision may have a different JTAG chain, and the host debug software must be aware of every revision. TI often updates its OEM emulator software tool kit, but this approach doesn't help end users unless they have reliable debugger vendors.

An alternative method to the JTAG OCD is to use a different chain via the JTAG port. This approach is allowed for in the IEEE specification.

With this method, one chain is available for the hardware test and debug, another for software debug. This method is used in the IBM 400 series of PowerPC as well as in the Analog Devices SHARC DSP and the MIPS EJTAG-supported devices.

This secondary chain provides access to debug specific registers (usually only

two or three are needed]. In IBM chips, the debug port has access to an instruction stuff buffer, debug control register, and debug status register.

The instruction-stuff buffer lets the dcbuggcr stuff any opcode into the core processor's instruction register, causing a single step to occur. By executing the proper instructions, any necessary action may be performed.

The debug control and status registers enable typical debug commands

| Command                                                                                                   | Definition                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAREG/RDREG<br>WAREG/WDREG<br>RSREG<br>WSREG<br>READ<br>WRITE<br>DUMP<br>FILL<br>GO<br>CALL<br>RST<br>NOP | Read address or data register<br>Write address or data register<br>Read system control register<br>Write system control register<br>Read memory<br>Write memory<br>Read memory block<br>Write memory block<br>Write memory block<br>Run CPU<br>Call user patch code<br>CPU reset instruction<br>Null command |

Table 1 -Some OCD processors have dedicated command sets for software debug.

(e.g., single step and run). Since a separate chain from the hardwarc test chain is used, the chain length is less than 50 bits. There is some small overhead with each JTAG action to ensure that the proper chain is being accessed.

Note that TI uses different flavors of the JTAG port on DSP chips. The C30 family has an MPSD port-similar to but not exactly like JTAG.

An advantage of the JTAG port for software debug is that it doesn't need additional pins on the processor for separate hardware and software debug. A disadvantage is the added overhead needed for each basic action.

### **DESIGNING A PROTOTYPE**

There are many things to consider in designing your prototype target to take advantage of OCD capabilities.

First of all, USC it! Some designers are so accustomed to ROM monitors or emulators, they ignore OCD features.

If possible, place the specified header on your board. If the prototype isn't the same PC card as the end product, then there's sure to be room on the board for the header.

If there isn't, look at the header specification from the manufacturer and debugger you plan on using. You'll probably find signals you don't need. IBM's RISCWatch header has several noconnect signals and a key [missing) pin.

Or, you can substitute a smaller header and make a conversion cable. The Motorola BDM for the CPU16/'32 family contains two ground signals and a DATA STROBE signal. Typically, one ground may suffice, and most debuggers don't use the data strobe.

The header doesn't have to be a dualrow header on 0.1" centers. Although this is the specification, feel free

to modify it to fit your needs.

Next, be careful about the layout. It's helpful to keep higher frequency lincs separated. If you're using a wiggler, there's no problem since the frequency doesn't usually surpass 100 kbps.

And, watch those traces. It's best to keep the OCD connector close to the CPU since the lines are typically not buffered. It's important to keep the traces approximately the same length, especially if they're serial communications lines.

For Motorola, these arc DSI, DSO, and DSCK, and for JTAG interfaces, TMS, TDO, TDI, and TCK. I've seen problems, even with low-speed wigglers, when the lines meander around the board from the processor to the header, particularly with 3.3-V parts.

Remember, some JTAG ports are used for both hardware and software testing. The hardware use may necessitate connecting many chips on the board together via a JTAG daisy chain. This setup will greatly affect software testing and noise on the chain.

Also, watch the resistors. Motorola chips, in particular, set up the OCD configuration and access during hardware reset. It's important that the dcbuggcr correctly control these lines during this time.

Equally important is what happens when you test the board without a debugger. The manufacturer will also offer a recommended circuit for the OCD/JTAG header, which may or may not include resistor pull-ups and/or pull-downs. Other signals on the header may also have recommended circuits.

Virtually all OCD-equipped processors have multiple chip selects. One is typically configured during a hardware

Figure 3—Some OCD engines include sophisticated hardware to bridge the gap between OCD debugging and in-circuit emulators.

reset to be used with whatever boot ROM or start-up code ROM is in the system. Many newer designs use flash memory for this purpose.

During debug, it's advantageous to use RAM instead of ROM to hold the code under test. You can have another chip select point to a bank of RAM.

The problem is that when you or the debugger cause a hard reset, the chip select for the RAM isn't appropriately configured. Also, you test code running with a chip select different from that in the final product-a situation that's better to avoid.

I recently developed a new solution. My boot chip select and general chipselect zero went to a 2 x 3 pin header. Onboard was a 128-KB flash memory and 128-KB SRAM. By changing the jumpers on the header, either device could be controlled by either chip select.

During initial debug, the RAM received the boot chip select. After code was burned into the flash (in the target, via an OCD flash programmer), the jumpers were changed, and the final debug and test were conducted.

You'll find if you socket your boot ROM, there may be a RAM with the same footprint that can fit in the socket during debug, or a simple socket adapter may be fabricated. Don't forget to make the socket writablc.

Another common practice in a final product is to have the application code in as slow, small, and narrow a boot ROM as possible. This enables inexpensive storage.

The boot code sets up the hardware (minimally, the other chip selects) and copies the application code from the slower ROM to faster system RAM. These tasks are followed by a jump to the start of the application.

This kind of simple boot program is easy to implement. You may want to have the boot section of the code written and placed into a ROM on the boot chip-select line. During debug, the application code would not be in the ROM but still on the host.

When you reset the target under test, you execute the beginning of the boot code to set up the hardware and then return to the OCD. Now, your application under test may be downloaded to the RAM on the chip select it will run with in the final system.

There are tools on the market that let you program flash memory while it's on the target board. These tools work through the on-chip debugger.

By configuring the flash so the processor can write to it, programming it becomes easier. You may need to run a WRITE line to the chip and/or add 12 V controlled by a port pin (preferred) or a jumper. This technique may involve adding a trace or two to the PC board definitely worth the added copper.

### DESIGNING YOUR PRODUCT

There are many reasons to have access to the OCD in a final product. With the proper host support, flashmemory programming, production-line testing, and in-field debug are all possible. Even if you don't use it after production starts, the lack of access to OCD, if it is needed, may be costly.

It's not nearly as important as with the prototype to use the factory-specified header. But, watching the traces is as important, if not more so. Your product may be in a less friendly environment (e.g., electrical noise) that you may not be able to control as easily.

Watching the resistors is important, too. You want to ensure all start-up parameters are correct, which is especially important with Motorola's BDM interfaces.

Finally, setting up flash memory for writability is crucial. The ability to easily program flash-on the production line and in the field-will prove invaluable. And, you can eliminate the use of sockets for EEPROMs.

### **CHOOSING A DEBUGGER**

First, consider the invasiveness of debuggers (i.e., the amount of system setup the debugger does for the user). A ROM monitor typically does some setup. An OCD debugger doesn't have to do this but often does. Why does this matter?

If the debugger does any setup and your code doesn't reproduce it in the exact way (and possibly at the exact time), your code won't run in the same environment as when it is tested. This is a perfect example of why your code will work with the debugger but not directly out of ROM.

Whether an OCD debugger has to do setup depends on your hardware configuration. Other similar invasions are the initialization of general registers, setup of an oscillator PLL, and so forth.

There arc different thoughts on how much the debugger should protect the user. A common target has a bank of RAM into which your code is loaded for testing.

Assume your code is running in real time and goes into the weeds. If there's an errant pointer, you're now executing out of uninitialized RAM, which is garbage code. The code may go for a while, wreaking all sorts of havoc, until the debugger somehow regains control. This problem is tough to debug without a large trace buffer.

Alternatively, the debugger could have filled memory with some specific instruction before downloading your code. If this instruction is a BREAK, BGND, TRAP, or INTERRUPT that the debugger recognizes, a break would occur at the first errant instruction. Should debuggers automatically do this? What about interrupt vector tables? Should debuggers fill in uninitialized vectors and trap on their use?

Some of these issues are easier to dcal with, depending on the target chip. The embedded PowerPC chips have many options for protecting the user.

By setting bits in a register, you can cause the OCD mode to be entered for various events (e.g., execution of an unrecognized opcode, misaligned data fetch, ctc.). If the debugger secretly sets these bits, you're debugging in a differcnt environment than the one your code runs in. This is probably OK, but does your debugger give you access to these bits?

### OCD SPECIFICS

A handful of OCDs are on the market, ranging in price from freeware to several thousand dollars. They all provide the basics-read and write registers, read and write memory, download code, single step, run, and so on. Most have source-level debug capabilities. Some work only with assembly code, others with any language.

Of most concern are the situations I mentioned. Is there hidden initialization? Are there user-friendly traps? And what about that start-up stuff?

Assume you ignore my suggestions for prototype design. Your target has its boot chip select attached to some type of ROM chip. Since this is debug time, there is no code in ROM yet.

The debugger is connected to the OCD header, and you want to start testing code. You have the debugger reset the target and then download your code. Wrong!

On reset, the only properly set-up chip-select line will be the boot chip select, and it's pointing to useless ROM. Whichever chip select is attached to your RAM must be initialized. But, by who (or what]?

Some debuggers have built in setups for known hardware. Usually, you can describe your custom target via dialogs to tell the debugger how to set up the board.

Others let you write command files (e.g., macros, scripts, etc.) to do the setup. These files have commands such as **WRITEL 0x1234**, **0x5678**, which

writes a **LONG** value of hex 1234 to location hex 5678.

With some debuggers, you must explicitly run the command file every time you reset the processor. Others do it automatically.

Again, the problem is that your code is now in an environment that's different from the reset environment, and your code didn't cause this change. If the only command is a setup of the RAM chip select, this problem probably isn't too big. Probably.

Another set-up issue is target-processor speed. Many new processors use an inexpensive 32-kHz crystal with an onchip PLL to boost the system frequency.

On reset, the PLL is at some default value, possibly a slow one. Often, your application's initialization code sets the PLL to a faster value, but during debug, this only happens after your code downloads.

If the debugger doesn't do any setup (hidden or not) and you do a download (via the boot chip select), the processor is most likely running at a slow speed. This slows your download.

All OCD protocols are implemented serially. The maximum OCD speed is usually a function of the CPU clock speed (about one-third or one-half the CPU speed).

Most OCD hardware interfaces start at a slow speed since the processor speed usually can't be determined. If the interface speed isn't set for maximum (either the fastest the CPU can handle or the interface can run, whichever is slower), the debugging speed is affected.

This situation is most obvious in the download speed of code. Some debuggers let you modify the interface speed in a command file. You'd do this only after you set the PLL speed, of course.

You probably have to set the interface speed to be slow at the start of the command file. Why?

Once you resct the target processor, it runs at its default speed. If it's slow, you must slow the interface to do your PLL setup and then speed up the interface.

Ideally, you may have a macro that runs whenever you hit the debugger RESET TARGET button or a command on your debugger that resets the target CPU, lowers the OCD speed, sets the Interrupt/break into debug mode on program-memory address Interrupt/break into debug node on datamemory address Interrupt/break into debug mode on an on-chip peripheral access Enter debug mode using a DSP instruction Read/write any DSP core register Read/write peripheral memory-mapped registers Read/write program or data memory Step one or more instructions Trace one or more instructions Save or restore current chip pipeline Read real-time instruction trace buffer Exit debug mode

Table 2—Motorola's OnCE engine offers a powerful command set for debugging.

processor PLL for desired speed, and raises the OCD speed to as fast as the processor allows.

### ONWARD!

Use this information to ask questions of the vendor, and see the debugger in use. Does it work with your favorite compiler? How does it communicate with the target? What is its invasiveness, and are those items fully documented!

I'm prejudiced about debuggers. I've written and marketed several-from basic DOS assembly-language-based debuggers to complete Windows-based high-level systems. But, I'll leave you to your own devices.

Good luck, and good debugging.  $\Box$

Craig Haller is president of Macraigor Systems, an OEM of embedded systems debug tools, and a firm believer that silicon manufacturers aren't marketing the advantages of OCD nearly enough. You may reach him at craig@macraigor. corn.

### SOURCE

### Debuggers

Macraigor Systems, Inc. P.O. Box 1008 Brookline Village, MA 02147 (617) 739-8693 Fax: (617) 739-8694 www.macraigor.com

### I R S

401 Very Useful 402 Moderately Useful 403 Not Useful

# Serial BDM Interface for ColdFire

# FEATURE ARTICLE

Ingo Cyliax

Since conventional debugging techniques often don't work on embedded systems, Ingo checks out ColdFire's on-chip debugger. He builds a simple BDM-toserial interface that helps him control and modify the chip. n my three-part MicroSeries (INK 86–88), I describe a MC68030-based workstation used by computer-science undergrads at Indiana University to learn more about computer architecture.

While this platform served us well for several years, I'm always looking for new architectures and technologies to enhance this lab. For the students, gaining experience with current technology is almost as important as learning the fundamentals when it comes to finding a job after graduation.

In my search for a new architecture to replace the MC68030 workstation, I'm currently evaluating the Motorola ColdFire architecture. In particular, I've been looking at the MCF5204 and MCF5206 implementations. Both are integrated microprocessors and include I/O and SRAM on chip.

Besides the ColdFire CPU core and 512 bytes of SRAM, the MCF5204 has one serial port, two timers, eight bits of general-purpose I/O, and a flexible 8-/16-bit bus interface. The MCF5206 adds a 32-bit bus interface, a DRAM controller, one more serial port, and an I<sup>2</sup>C two-wire device bus interface. These chips can implement a complete micro-processor system with only the addition of a boot PROM.

The ColdFire is well-suited for use in our lab because it's a 32-bit processor based on the 68000 architecture. Motorola has reduced the complexity by only implementing the most frequently used instructions and addressing modes. So, the ColdFire core is very lean, which is important if you target the low-end embedded 32-bit market where the cost/performance ratio is crucial.

Since the ColdFire core and chips are targeting the embedded-systems market, conventional debugging techniques are inadequate most of the time. Embedded systems usually don't have the luxury of a keyboard and display system, and many don't even have a serial port.

This situation makes softwarebased debugging not feasible or often intrusive. In a "hard" real-time system, software-based debugging techniques can't be used, since any additional software overhead may alter system response time.

Imagine a motor controller that synthesizes the AC waveforms used to drive a motor. A well-designed system would have enough processing power to perform this task and stay cost effective, but it might not have sufficient power to run a software debugger, which responds to breakpoints and traces sections of the code.

In embedded applications where software debugging is not feasible due to performance issues or I/O restrictions, you'd typically use an in-circuit emulator [ICE). An ICE emulates the signals and timing of the CPU and replaces the CPU in the system under test. It gives an external debugging host a window into the system by allowing real-time traces and access to the state of the CPU.

The ICE uses a pod that plugs into the processor's socket, thus replacing the processor, and a cable that connects the pods to the ICE interface. The interface unit is usually fairly bulky.

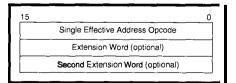

Figure I--The ColdFire instruction format consists of one 16-bit base opcode with one or two extension words, depending on the address mode used. Most register-to-register movements and ALU operations can be specified using the single-word instruction format. However, in this article, I examine the on-chip debugging features of Cold-Fire. I also want to show how you can build a simple BDM (Background Debug Mode) to serial interface that enables the user to control the processor and examine and modify its state.

With this interface, it's also possible to read and write memory in the target system while the CPU is running. But first, let's take a brief look at the Cold-Fire architecture.

### **COLDFIRE** ARCHITECTURE

ColdFire is a variable-size instruction RISC processor. Many of its RISC-like instructions that operate on registers are encoded as short 16-bit instructions, while instructions that use immediate data or addressing information use extensions to the short instructions. Figure 1 depicts the general instruction format.

The 68000 has always implemented variable-sized instructions, and this fact can be demonstrated by showing that ColdFire binaries run on a 68030 processor, but not the other way around. The 68030 implements many more instructions and instruction forms, and also has an MMU and FPU coprocessor.

Like the 68000, ColdFire has eight general-purpose data registers and eight address registers. It differs from the MC68000 series in that it only has a single stack pointer.

The ALU in the ColdFire is a leaner version of the 68000 ALU, so it doesn't implement all the 68000's operations and data types. All these reductions have made ColdFire so lean that it can now be synthesized from a hardwareTablel - - Here we can see all the commands which are implemented in the ColdFire BDM. Each command can take input data, output data, or both.

description model. The ColdFire core is portable across different chip technologies, so its architecture enables optimal chip-level integration.

### BACKGROUND DEBUGGING MODE

The BDM module is a hardwarebased debugging module that's embedded on chip. It has connections to the CPU core and the internal CPU bus. Since the BDM module sits so close to the CPU, it has essentially the same view of the system as the CPU.

This setup is important if the CPU core is embedded in a chip with on-chip resources and cache. It's quite difficult to debug systems with cache turned on.

But, BDM isn't exactly new. It was first implemented on Motorola's CPU32 core and appears in most MC683xx embedded processors (e.g., '68332 and '68360). It can also be found in the CPU16 core, which shows up in the MC68HC16 series of processors.

By using a simple serial interface, the BDM module permits an external debugger to examine the state of the

| Command                                                                                                                                           | Data     | In/Out                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 218x<br>208x<br>1900<br>1940<br>1980<br>1800<br>1840<br>1880<br>1D00<br>1 D40<br>1 D80<br>1 coo<br>1 C40<br>1 cao<br>0C00<br>0000<br>2980<br>2880 |          | /2<br>/1<br>/1<br>/2<br>/1<br>/1<br>/2<br>/1<br>/1<br>/2<br>/1<br>/2<br>/1<br>/2<br>/1<br>/2<br>/1<br>/2<br>/2<br>/1<br>/2<br>/2<br>/2<br>/1<br>/2<br>/2<br>/2<br>/2<br>/2<br>/2<br>/2<br>/2<br>/2<br>/2 | Read CPU data register<br>Write CPU data register<br>Byte read<br>Word read<br>Long read<br>Byte write<br>Word write<br>Long write<br>Byte dump<br>Word dump<br>Long dump<br>Byte fill<br>Word fill<br>Long fill<br>Go<br>NOP<br>Read CPU control register<br>Write CPU control register |

| 2D8 <i>x</i><br>2C8 <i>x</i>                                                                                                                      | /2<br>2/ |                                                                                                                                                                                                          | Read BDM register<br>Write BDM register                                                                                                                                                                                                                                                  |

CPU, read and write memory, and control the execution of the CPU. Extra status signals provide detailed information about the CPU's state in its various execution phases.

The original BDM on the CPU32 core was implemented in the CPU's microcode. And, the CPU would have to be in a halted state before BDM could become active.

This situation occurs when the CPU executes a HALT (BGN D) instruction or encounters a catastrophic condition (e.g., a double bus fault] or when the external  $\bullet$  BGND pin is asserted by the debugging interface. In all BDM implementations, asserting the \*BGND pin while resetting the CPU causes the CPU to enter a halted state before fetching the reset vector and initial stack pointer.

On ColdFire, BDM is implemented in a separate hardware module and runs in parallel to the CPU. Therefore, by stealing bus cycles, the BDM module can read and write memory while the CPU is running.

An external debugging system can also monitor the CPU state through the BDM interface. Real-time debugging features are implemented in the BDM module via programmable 'lardware-trigger facilities.

### PROTOCOL

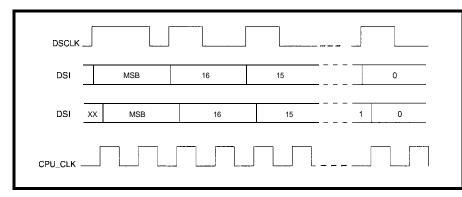

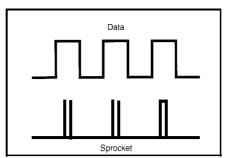

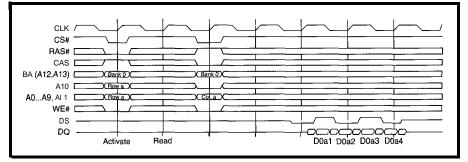

The basic BDM protocol consists of a three-wire interface (i.e., DSI, DSO, and DSCLK). The external debugger transfers data by simultaneously clock-

| 1510     | 9 | 8    | 76     | 5 | 4 | 3    | 20       |

|----------|---|------|--------|---|---|------|----------|

| Opcode   | 0 | R/*W | Opsize | 0 | 0 | A/*D | Register |

| Operands |   |      |        |   |   |      |          |

Figure 3-A BDM instruction specifies the data sizes requested and the command code to perform.

ing data in and out of the chip using the DSI and DSO lines. The DSCLK can run at any speed between DC and half the CPU clock.

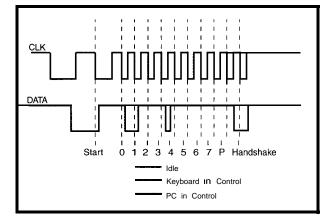

Commands and responses are 17 bits long and shifted most significant bit first. With the most significant bit-the S/C bit-the CPU indicates if the response is an error or not. The debugger always clears this bit on all transfers. Figure 2 shows the basic timing and word structure of the BDM protocol.

Commands and data are encoded in these17-bit words. The BDM module decodes these commands and performs the required action. The commands sent to the BDM have the general format shown in Figure 3 and can be simple commands, requiring no data, or complex commands, requiring data to be sent to the BDM. Commands that read registers and memory also respond with data from the BDM module.

There are three types of transactions-command only, command plus data, and command plus data plus response. BDM overlaps the response from a phase with the command/data for the next phase. A sophisticated debugger might be able to optimize these overlaps to squeeze some extra performance from the interface.

In particular, it could send the next command while reading the commandcompletion code from the last command. A simple dcbugger may just send a N 0 P command whenever it reads the response from the BDM.

To execute any command that can alter the CPU registers or state, the CPU must first be halted by asserting the \*BKPT pin on the BDM interface. The processor status signals (PST[3:0]) indicate \$F when the CPU halts. The debugger can also read the BDM status register at any time and determine the state of the CPU and BDM module.

Once the CPU is halted, the debugger can examine and alter any CPU and BDM register. Memory can be read or written at any time. Table 1 shows all the BDM commands available in ColdFire.

### REAL-TIME DEBUGGING SUPPORT

There are two facilities in the ColdFire BDM that aid

debugging in real-time environments. The hardware-trigger facilities cnable generation of breakpoints and external trigger stimuli, and the tracing facility gives a window into the state of the CPU while it is executing.

A hardware trigger can be generated on memory references, program counter locations, and operand data values. These can be combined to generate caseaded triggers (i.e., one trigger arms the second trigger) or simple triggers.

Once a trigger occurs, the response can either cause the CPU to halt or generate an exception to the CPU or a noop. The noop function is useful if you only want to trigger an external oscilloscope or logic analyzer.

The BDM module also routes internal signals to the outside using the PST and DDATA interfaces. A configuration register can be programmed to specify the kind of information displayed on these signals.

The PST interface monitors processor status, enabling an external monitor to trace the internal CPU activity. Table 2 shows the encoding for the internal CPU state on these signals.

The DDATA interface provides additional information. Depending on the CPU state, it may present data such as operand values or branch locations. Also, the processor can send data to this interface using special debug instructions. DDATA with

the PST interface can give an accurate view of what's going on inside the CPU.

Table 2—*The PST[3:0]* signals provide a window info the inner workings of the ColdFire CPU. Each code signals a state in the core.

### SIMPLE SERIAL BDM INTERFACE

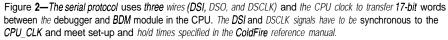

Let's see how to build a simple RS-232-based BDM interface using a Basic Stamp II and a PLD. The interface lets any serial-based workstation and even a terminal control a ColdFire CPU through its BDM interface.

I chose a Basic Stamp since it's readily available and easy to prototype with. The interface isn't fast, but it's functional.

Since the ColdFire BDM module is implemented in hardware, it requires all of its input signals to be synchronous to the CPU system clock. This task is easily accomplished by using the flip-flops in the PLD to synchronize signals to the CPU clock. Simple D-type registers can be used, too.

The Stamp generates the 'BKPT signal, which halts the CPU, and the \*RESET (hardware reset) signal. The Stamp also generates the DSCLK and DSI signals, while monitoring the DSO line.

I also wired in the PST[3:0] to some spare signals on the Stamp. Even though the signals change too fast for the Stamp to trace them, they can be used to detect if the CPU is halted.

This information is redundant, since the command and status register (CSR) in the BDM also contains it. However, it's more efficient for the Stamp to read a four-bit nibble from the I/O pins to determine the CPU state than to execute a scrial BDM command to read a register.

The Stamp communicates with the debugging host/terminal over its RS-232 interface using the TX and RX pins. Care must be taken that the ATN

| PST[3:0] | Definition                                 |

|----------|--------------------------------------------|

| 0000     | Continue execution                         |

| 0001     | Begin execution of instruction             |

| 0010     | -                                          |

| 0011     | Enter user mode                            |

| 0100     | Begin PULSE or WDDATA                      |

| 0101     | Begin execution of taken branch            |

| 0111     | Begin execution of RTE                     |

| 1000     | Begin I-byte transfer on DDATA             |

| 1001     | Begin 2-byte transfer on DDATA             |

| 1010     | Begin 3-byte transfer on DDATA             |

| 1011     | Begin 4-byte transfer on DDATA             |

| 1100     | Exception processing                       |

| 1101     | Emulator-mode entry exception processing   |

| 1110     | Processor is stopped waiting for interrupt |

| 1111     | Processor is halted                        |

|          |                                            |

signal is not driven low by DTR on the Stamp, which puts the Stamp into its programming mode. I added a jumper to isolate the signal during normal operation.

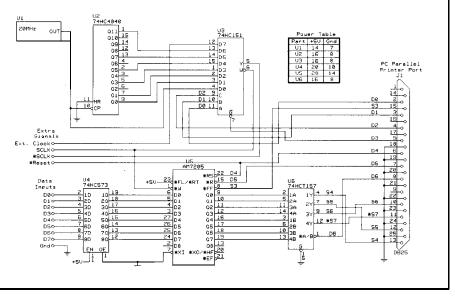

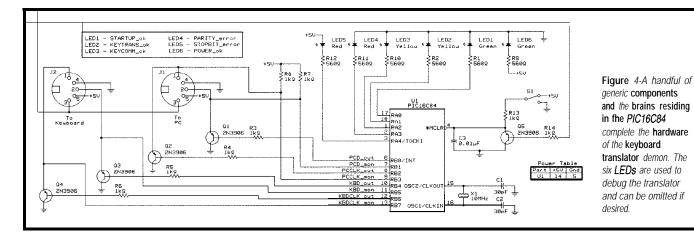

The Stamp and external circuitry get their power over the BDM interface connector from the CPU. The interface schematics arc shown in Figure 4.

The software is organized bottom up. First, the routine **bdm** (see Listing 1) takes the data in **bdmsnd** and transmits it using DSCLK and DSI. At the same time, it records the response from the CPU to the last transfer over DSO and records it in the variables **bdmrcv** and **bdmmsb**.

, The next level up executes the serial BDM command primitives. read 1 in Listing 2 implements reading a 32-bit word from memory. It takes two 16-bit words-a d d r h and a d d r 1 -to specify the memory location to read, and it records its response in da t a h and datal.

To perform a long-word read, the Stamp sends the value \$1980, followed by the two address words, using **bdm**. After sending the command, I wait for the BDM to perform the read operation by stealing deadtime on the bus.

The Stamp does this by sending a N 0 P command (\$000) and looking at the response. It continues until the response is either valid data (\$0xxxx) or a bus error (\$10001). The first data word is stored in da t a h, and another NOP is sent to read the second word to be stored in datal.

Other BDM commands (e.g., go) and reading/writing registers are implemented the same way.

At the top level of code, a command interpreter reads a command packet from the host over the serial port. After decoding it, it calls the appropriate BDM subroutine to execute the BDM commands necessary to implement the request and collect its response.

The response gets encoded properly to send it back to the host over the serial port. To inform the debugger of the CPU state, it displays the current PST[3:0] encoded as a hex digit as part of the command prompt.

The command interpreter reads line-oriented text commands much like a debugging monitor would. Thus, Listing 1—bdm is a low-level function that clocks out the 17-bit command word and clocks in any data sent from the BDM in the ColdFire chip. All the bdm subroutines implemented in the serial BDM inferface use this function to communicate with the ColdFire BDM.

```

perform one BDM transaction

send 17 bits starting with '0' and the word

"bdmsnd"

n bdmrcv

receive 17 bits-S/C in bdmmsb and the rest

bdm

dsi = 0

'MSB is always low on sending

pdsclk.1

clock it out

pul sout

read MSB

bdmmsb = dso

send 16 bits of cmd and record 16 bits of status at same time

for i = 0 to 15

dsi = bdmsnd >> (15 i)

pulsout pdsclk,1

bdmrcv = (bdmrcv << 1 | dso

next

dsi = 0

restore every thing

dsclk = 0

return

```

a debugger can use the interface with a dumb terminal program, maybe even remotely over a modem connection. The Reference section directs you to the PBasic program for this project.

With this interface, I can now control the execution of the ColdFire core and read and write CPU registers and system memory. I can also control the BDM registers to program triggers and DDATA[3:0] sources.

Except for the execution speed, this little gadget is quite useful. A faster implementation of this BDM interface could be based on a PIC CPU programmed in assembly or C, which would *also* make it inexpensive-always a bonus when working in academia.

### INTERFACING WITH GNU GDB

I introduced the GNU source-level debugger (gdb) in Part 3 of my Micro-Series (*INK* 88). It can use a serial port or the network to remotely debug processes running on a different system. It can also be extended to implement various protocols needed to talk with ICEs or debugging monitors.

gdb also has a generic remote protocol interface. I'm currently working on interfacing gdb with my serial BDM interface. A serial-based BDM debug-

Listing 2-r e a d7 is a typical function implemented in the serial BDM interface. It sends the "read long" command and address and receives the long data, which is stored at that location by sending NOPs.

| readl :                            | read long memory              |

|------------------------------------|-------------------------------|

| bdmsnd = \$1980                    | ' send read long command      |

| gosub <b>bdm</b>                   | Sona road rong communa        |

| bdmsnd = addrh                     | high word of address          |

| gosub <b>bdm</b>                   | -                             |

| bdmsnd = addrl                     | low word of address           |

| gosub <b>bdm read1 again</b> :     |                               |

| bdmsnd = \$0000                    | send NOP to read status       |

| gosub <b>bdm</b>                   | r BDM to complete transaction |

| if bdmmsb = 0 then read1           |                               |

| if bdmmsb = 1 AND bdmrcv           |                               |

| serout 16, n19200, ["Error         |                               |

| hex bdmmsb, hex bdmrcv,            | cr,10]                        |

| return                             |                               |

| BDM is done and has se             | ent high word of data         |

| read1 done:<br>datah = bdmrcv      |                               |

| datan = bdm cv<br>bdm snd = \$0000 | 'send NOP to read low word    |

| gosub <b>bdm</b>                   | Schu hor to reau row word     |

| data1 = bdmrcv                     | record low word of data       |

| return                             |                               |

|                                    |                               |

Figure 4—This simple RS-232 BDM interface uses a Parallax Basic Stamp II and a PLD. Check the References for information on obtaining the PLD JEDEC file and Stamp code for this interface.

gcr module that works with a terminal and source-level dcbugger is useful.

### WHAT ELSE?

The BDM module is a powerful debugging feature of ColdFire-especially during system and program development. It can also reduce manufacturing costs, since this interface can be used to perform in-circuit tests of a system during assembly and burn-in. It also enables in-circuit programming of flashand EE-based memory for program and configuration and parameter storage.

The BDM module makes ColdFire a good candidate for our architecture lab. Wc can build a minimal system consisting of a MCF5204 or MCF5206 and some useful I/O for experimentation.

BDM can then bootstrap the processor and write the students' code into SRAM or external DRAM. Such a system offers all the essentials for our class (e.g., interrupt-driven I/O, timers, etc.).

And since ColdFire chips are costsensitive and the BDM interface can be made cheaply, it's feasible for students to buy a ColdFire module that they can take home. GNU software could be bundled with this system on a CD-ROM, enabling students to do development on their own PC.

Ingo Cyliax works as a research engineer in the Analog VLSI and Robotics Lab and teaches hardware design in the computer science department at Indiana University. He also does software and hardware development with Derivation Systems, a San Diego-based formal synthesis company. You may reach Ingo at cyliax@EZComm.com.

### REFERENCES

### Text

- Motorola, MCF5200PRM/ADCold-Fire Programmer's Reference

- *Manual,* Phoenix, AZ, 1995. Internet

- MC5206 Evaluation Module bundle, www.hh.avnet.com/marketing/ coldfire.html.

- GNU tools (gdb), prep.ai.mit.edu/ pub/gnu.

- Stamp code and PLD JEDEC file for the serial interface, ftp.cs. indiana.cdu/pub/goo/SerBDM.

### SOURCES

### **Basic Stamp II**

Parallax, Inc. 3805 Atherton Rd., Ste. 102 Rocklin, CA 95 765 (916) 624-8333 Fax: (916) 624-8003 info@parallaxinc.com www.parallaxinc.com

### ColdFire

Motorola MCU Information Line P.O. Box 13026 Austin, TX 7871 I-3026 (512) 328-2268 Fax: (512) 891-4465 www.mot.com/SPS/HPESD/prod/ coldfire

### IRS

404 Very Useful 405 Moderately Useful 406 Not Useful

# FEATURE ARTICLE

### Janusz Młodzianowski

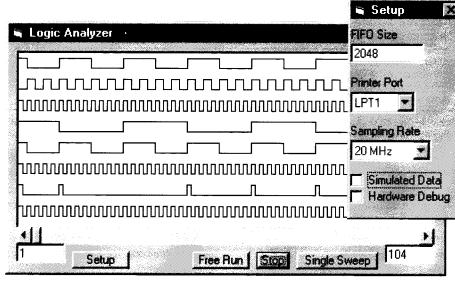

# A Simple Multipurpose Logic Analyzer

There are times when what's available on the market is not what you want. The price, features, or expandability just doesn't meet your current needs. What do you do? If you're Janusz, you build your own.

Dedicated analyzers are available on the market, but the price (in excess of \$1000) is too high for small-scale designers. The price of smaller PC add-on card analyzers isn't much lower.

Some manufacturers offer simple devices capable of capturing up to eight signals via a PC parallel printer port. Although such analyzers cost less, their functionality is limited. The maximum sampling frequency is on the order of a few tens of kilohertz.

Since I've designed digital circuitry for a number of years now, I concluded that the only sensible solution would be to build my own logic analyzer. I needed a simple yet expandable instrument with at least 16 TTL probes, capable of capturing data at about 50 MHz and connected to a PC via a bidirectional parallel printer port.

I didn't want to use any exotic components and microcontrollers. The hardware had to be built with off-theshelf components and fit a short 3U Eurocard. Photo 1 shows the result.

### THE BASICS

A logic analyzer is basically a multichannel probe that can read, store, and process a number of digital data vectors.

In the measurement phase, the data is clocked into the analyzer's internal storage RAM. While reading, each captured vector is compared with a preset trigger pattern.

When the comparator matches data with the trigger vector, measurement ends. The captured data transfers to the host PC and is presented to the operator.

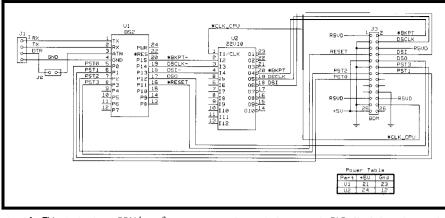

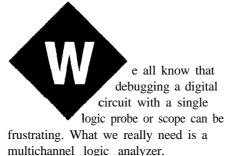

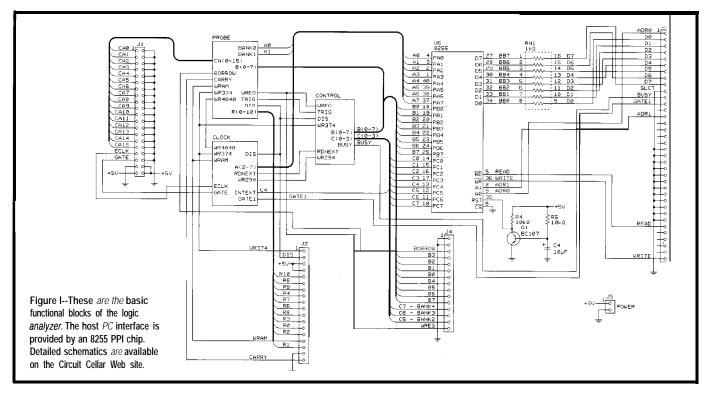

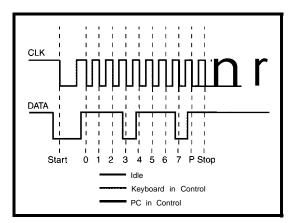

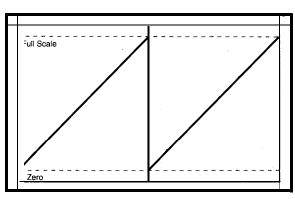

Figure 1 illustrates the hardware, including the modules for the PC interface, logic probe with input register and data storage, programmable comparator, and control circuitry. Figure 2 shows the timing diagram and the key signals controlling the hardware.

Once all measurement parameters are set up, the measurement cycle is initiated by a momentary pulse on the START line, which sets the BUSY line active. Once BUSY is asserted, low-tohigh transitions on the WR374 line registers in the input buffer the data vector present on all probes.

The WR374 strobe originates from the internal time base clock or the analyzed circuitry. In Figure 2, this clock (internal or external) is shown as INPUTCLK. Signals WR4040 and WRAM are derived from WR374.

When the data vector is registered, the falling slope on WR4040 advances the RAM address generator. The following rising slope on WRAM stores the data in the analyzer's internal RAM. The analyzer is then ready to accept the next vector.

Once the data vector is registered, it is compared with the trigger word. When a match is detected, the TRIG line asserts high and decrements the preprogrammed Event Counter. When the Event Counter reaches zero, the second preprogrammed counter-the Delay Counter-is enabled.

Once enabled, the Delay Counter counts WR374 pulses. When it reaches zero, its output signal (DELAYTC) ends the measurement cycle.

The end of the measurement is signalled by BUSY reverting to an inactive state. Strobes WR374, WR4040, and WRAM are disconnected from the source. The measurement cycle can

also be stopped by asynchronously pulsing the STOP line.

Once the measurement cycle ends, the data stored in the RAM can be read back to the host PC. While reading the data, the RAM address generator is advanced by pulsing RDNEXT.

Let's examine the functions of the Event and Delay Counters. The analyzer's objective is to detect a particular pattern in the registered data. Usually, the operator is interested in the first instance of the vector (e.g., the first call to int10 after reset in a PC).

But sometimes, you might want to catch the tenth call to int 10. The Event Counter then skips the first nine calls and is preprogrammed to 10. An Event Counter feature is not present in the simple analyzers I know of.

The Delay Counter enables the hardware to capture a given number of data vectors after the final trigger. Suppose I want to see up to 50 proces-

sor machine cycles after the tenth call to int 10. The Delay Counter should then bc set to 50.

A closer analysis of the timing diagram shows the measurement cycle ends after two more vectors (e.g., 52 in this example) are captured. This can be compensated for with the software.

In this design, the RAM operates as a ring buffer. When the entire RAM is filled with data, the counter wraps around and the process continues.

It doesn't matter where in RAM the data is stored. When the measurement cycle ends, the RAM address generator points to the first location after the last registered vector.

The ring-buffer approach enables the use of some simple counting arithmetic. When the Delay Counter is preset to 0, no additional samples are taken after the last trigger, so the buffer contains the maximum count of samples acquired before the last trigger. When the Delay Counter is set to maximum, the RAM contains the maximum count of samples after the last trigger.

From the user point of view, the delay count set in the Delay Counter can be positive (i.e., after the trigger) or negative (i.e., before the trigger). The count equal to zero means the buffer contains one half of the buffer size samples before and after the last trigger.

Figure 2—From this timing diagram, you see that the hardware operates in two modes—Measurement and Program.

| Data Port<br>D7<br>D7(9)    | <b>(Base+O)</b><br>D6<br>D6(8) | D5<br>D5(7)               | D4<br>D4(6)        | D3<br>D3(5)      | D2<br>D2(4)           | D1<br>D1(3)    | D0<br>D0(2)     |

|-----------------------------|--------------------------------|---------------------------|--------------------|------------------|-----------------------|----------------|-----------------|

| Status Po<br>D7<br>BUSY(11) | D6                             | D5                        | D4<br>SELECTED(13) | D3<br>ERROR(15)  | D2<br>X               | D1<br>X        | DO<br>X         |

| Control Po<br>D7<br>X       | ort (Base<br>D6<br>X           | <b>−2)</b><br>D5<br>INOUT | D4<br>INTR         | D3<br>SLCTIN(17) | <b>D2</b><br>INIT(16) | D1<br>FEED(14) | D0<br>STROBE(1) |

Table 1 — The PC Centronics printer port is controlled by three registers. Here are the signal names and corresponding pin numbers.

### HOST-PC INTERFACE