THE COMPUTER APPLICATIONS JOURNAL

#91 FEBRUAR Y 1998

## **COMMUNICATIONS**

**Making NT Play Nice with Unix**

**Embedding Voice Recognition**

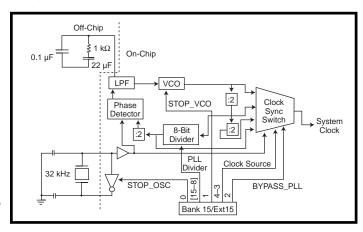

Zilog's Z89xx3 = DSP + MCU

**Converting PC GUIs for NonPC Devices**

## TASK MANAGER

#### And Yet More Change

n my tenth-anniversary editorial last month, I spent some time talking about change—specifically, the changes that have come about over the past decade. One area in which we've seen drastic change just in the past few years is how we communicate.

Printed publications have been around since the printing press was invented in the 15th century, and will continue to thrive for the foreseeable future. There is something about holding a book or magazine that people still enjoy and aren't willing to give up. They don't require special equipment to read. They're lightweight, low cost, highly portable, and don't require any power. On the downside are the cost of entry, use and cost of paper, required lead time, and limited distribution.

Along came the electronic bulletin board system, and suddenly time and distance were compressed, enabling anybody with a computer and modem to publish their own work for anyone in the world to access instantly. The next step was the Internet and the World Wide Web, further reducing cost and increasing availability and quality.

Publishers of print media are seeing the handwriting on the wall in a big way, and virtually everybody has some kind of on-line version of their print publication. We at Circuit Cellar brought the Circuit Cellar BBS on-line back in 1986 to first support Steve's *BYTE* articles and to later support *Circuit Cellar INK*. It was a tremendous success, fueling active discussions between talented engineers located throughout the world. Long-time readers were also treated to a sampling of those discussions each month through my ConnecTime column.

The Circuit Cellar BBS has just gone off-line for good as a BBS. However, various Internet elements have replaced it, making the same functions available to anyone in the world with Internet access. Magazine information and articles can be obtained from the Circuit Cellar Web site (www.circuitcellar.com). Files can be downloaded from our FTP site (ftp.circuitcellar.com). And, messages can be exchanged in a public forum through our new newsgroup server. Don't look for our newsgroups among the other Usenet groups you may be receiving from your ISP (Internet Service Provider), though. You must point your newsreader at our server at bbs.circuitcellar.com to see what groups are available and what discussions are going on. If you're still not sure what I'm talking about, there is more information on the Web site.

In the coming months, I'll be spending more time enhancing and developing our on-line presence. Please send any suggestions or comments along with those article proposals and ideas to editor@ circuitcellar.com and I'll respond as quickly as possible. I'll see you on-line!

Van

ken.davidson@circuitcellar.com

# CRCUIT CELLAR®

#### THE COMPUTER APPLICATIONS JOURNAL

EDITORIAL DIRECTOR/PUBLISHER

Steve Ciarcia

ASSOCIATE PUBLISHER Sue (Hodge) Skolnick

EDITOR-IN-CHIEF Ken Davidson CIRCULATION MANAGER Rose Mansella

MANAGING EDITOR

Janice Hughes

BUSINESS MANAGER

TECHNICAL EDITOR

Jeannette Walters

Elizabeth Laurençot

ART DIRECTOR KC Zienka

WEST COAST EDITOR

ENGINEERING STAFF

Tom Cantrell

Jeff Bachiochi

CONTRIBUTING EDITORS

PRODUCTION STAFF

Rick Lehrbaum Fred Eady James Soussounis

**NEW PRODUCTS EDITOR**

Harv Weiner

Cover photograph Ron Meadows – Meadows Marketing

PRINTED IN THE UNITED STATES

#### **ADVERTISING**

#### ADVERTISING SALES REPRESENTATIVE

Bobbi Yush Fax: (860) 871-0411

(860) 872-3064 Email: bobbi.yush@circuitcellar.com

ADVERTISING COORDINATOR

Valerie Luster Fax: (860) 871-0411

(860) 875-2199 Email: val.luster@circuitcellar.com

#### CONTACTING CIRCUIT CELLAR INK

#### SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199

GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411

INTERNET: info@circuitcellar.com. editor@circuitcellar.com. or www.circuitcellar.com

EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066

AUTHOR CONTACT

E-MAIL: Author addresses (when available) included at the end of each article.

ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK®.

Entire contents copyright © 1998 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

| 12                                                                          | <b>Low-Co</b><br>Brad Ste                                        | st Voice Recognition<br>ewart                                                       |                                                      |    |

|-----------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|----|

| 20                                                                          | <b>Building an Embedded Web Server from Scratch</b> Richard Ames |                                                                                     |                                                      |    |

| 30 Integrating Windows NT 4.0 into a TCP/IP Environment Bill Payne          |                                                                  |                                                                                     |                                                      |    |

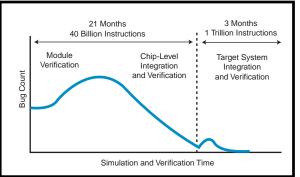

| 60                                                                          |                                                                  | n<br>Olving Relationship Between Hardware and Software<br>Moseley                   |                                                      |    |

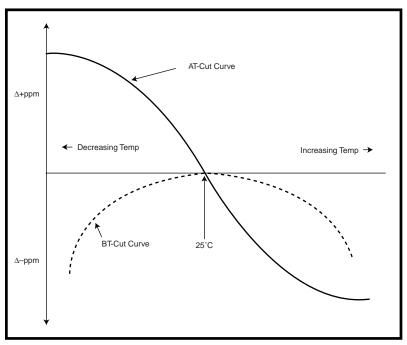

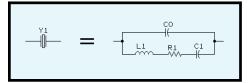

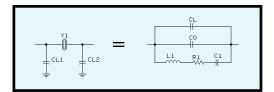

| 66                                                                          |                                                                  | ng the Right Crystal for Your Oscillator<br>n Bujanos                               |                                                      |    |

| 72                                                                          | EM<br>Pai                                                        | croSeries  II Gone Technical rt 1: Surge Suppression e DiBartolomeo                 |                                                      |    |

| 78                                                                          | Ch                                                               | om the Bench<br>noose the Right Vehicle Before Riding the Air Waves<br>of Bachiochi | Task Manager<br>Ken Davidson<br>And Yet More Change  | 2  |

| 82                                                                          | Do                                                               | icon Update<br>ouble-Duty DSP                                                       | Reader I/O                                           | 6  |

|                                                                             | To                                                               | m Cantrell                                                                          | <b>New Product News</b> edited by Harv Weiner        | 8  |

|                                                                             |                                                                  |                                                                                     | Advertiser's Index                                   | 65 |

|                                                                             | X                                                                |                                                                                     | Priority Interrupt<br>Steve Ciarcia<br>Techno-Jargon | 96 |

| 3                                                                           | 6 Nouve                                                          |                                                                                     | 7                                                    |    |

| edited by Harv Weiner  40 Converting PC GUIs for NonPC Devices  Dan Johnson |                                                                  |                                                                                     |                                                      |    |

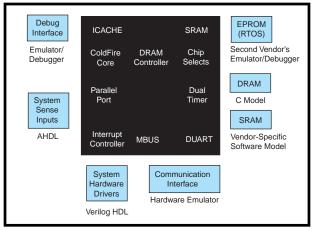

|                                                                             | 7 RPC                                                            | Real-Time PC Real-Time Operating Systems Part 2: RTOS Interfacing Marc Guillemont   |                                                      |    |

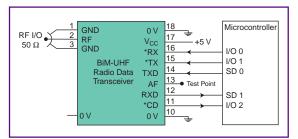

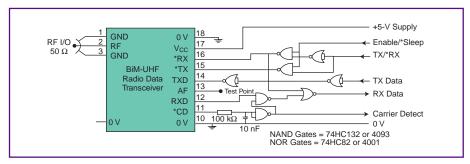

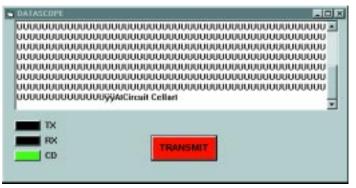

| 5 T T                                                                       | 3 APC                                                            | Applied PCs RF Telemetry Part 2: You're on the Air Fred Eady                        |                                                      |    |

|                                                                             |                                                                  | WW                                                                                  | w.circuitcellar.co                                   | m  |

3

## READER I/O

#### THAT DARN x-y RATIO

As a broadcast professional with over 20 years in the (PAL) business, I was happy to read Do-While Jones' article "HDTV-The New Digital Direction," (INK 86). Anything that helps people understand how high bandwidth content travels along a limited-size pipe is good.

One very minor mistake that I've seen made a thousand times is the reference to a  $4 \times 3$  video wall. If you stack monitors symmetrically 4 across  $\times$  3 vertically, you end up with a 16:9 video wall—oops! To retain the aspect ratio of the individual monitors, you need to expand both dimensions by the same ratio!

#### Michael Coop

mcoop@pop.jaring.my

#### RENAMING "FUZZY LOGIC"

Ken's editorial in INK 88 ("Stuffed Mentality") made a good point—"fuzzy logic" sounds like fuzzy thinking. I suggest we rename it "quantitative logic." It is logic in which truth is a quantity (i.e., something you can have a little or a lot of).

There are other nonclassical logics, too. I'm currently doing research on defeasible logic, a system where generalizations are automatically overruled by specific exceptions. It's a good fit to the way human beings describe things.

#### Michael A. Covington

mc@ai.uga.edu

#### **SLACKING OFF?**

A programmer friend passed me a copy of INK 88 for the articles on automotive applications for fuzzy controls. Constantin von Altrock's "Fuzzy Logic in Automotive Engineering" was very clear and gave me a much better understanding of how and why fuzzy logic is being used. Unfortunately, Constantin shows his lack of automotive background (and/or the results of reading a poorly translated paper) in a couple of places—the article would have been much more convincing without these mistakes.

First of all, when the car is moving and a wheel stops turning, it is "locked" (not "blocked").

Also, the variable s in the text (p. 13) and in Figure 1 is "slip ratio" (not "slack"). There are a number of definitions for *s* used in different parts of the world.

There's a summary of eight different slip-ratio relationships starting on p. 39 of Race Car Vehicle Dynamics (W.F. and D.L. Milliken, SAE, www.sae.org, 1995).

In Figure 1, the curve for "Snowy Road" would perhaps be more accurate if labeled "Hard Packed Snow". The three curves shown are all representative of tire performance on "hard" surfaces, where there is a definite peak in *m* (tire-road friction coefficient).

To give but one example of the difficulty of designing an ABS algorithm, consider that unpacked snow, gravel, and sand are all "deformable" surfaces, and braking on deformable surfaces has a completely different characteristic than on hard surfaces. On a deformable surface, a locked wheel usually gives the best braking (but no steering control), perhaps by building up a wedge of material in front of the tire. I say "perhaps" because tire-road friction on different surfaces is still not well understood. The inability of current production ABSs to properly distinguish between different surfaces remains a major problem.

The stopping ability of ABS on various slippery surfaces was discussed in a recent article (D. Simanaitis, "ABS: Putting a Stop to it All," Road & Track, July 1997). In their tests, locking the brakes (with the Mercedes-Benz ABS disarmed) produced shorter stopping distances on three out of four different icy/snowy surfaces tested. The ABS also lost on gravel and tied on sand. ABS won on wet roads and won dramatically on dry roads.

#### Douglas Milliken

bd427@freenet.buffalo.edu

Thanks for such detailed feedback. I'd like to briefly comment on your issues.

I have no doubt that it's "locking" instead of "blocking." I used "blocking" because "ABS" stands for Anti-Blockier System in German.

Regarding s, the German is "Schlupf," which in technical dictionaries is translated to "slack" (which Oxford defines more precisely than it does "slip"). And, you're right: s has many definitions worldwide. Rather than discussing these, I took one, showed the definition, and focussed on fuzzy-logic use in this system. I don't think any other approach would have helped the reader.

I limited the discussion on hard surfaces because discussing all the different things that occur within an ABS situation was not my goal. But, you're absolutely correct: there's a lot more to say about ABS.

Constantin von Altrock cva@inform-ac.com

## NEW PRODUCT NEWS

#### **BATTERY POWER MINDER**

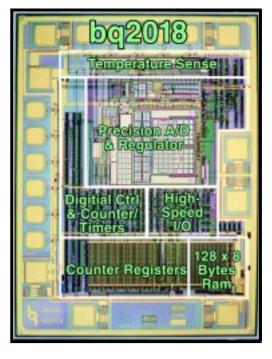

The bq2018 Power Minder IC provides state-of-charge information for any type of rechargeable battery, including Li-Ion, NiMH, NiCd, lead acid, and rechargeable alkaline. Designed for battery-pack integration, the 8-pin bq2018 communicates critical battery information over a single-wire control/data serial interface to an intelligent host controller. Typical applications include cell phones, PDAs, and personal organizers.

The bq2018 measures the voltage drop across a low-value series sense resistor between the battery's negative terminal and the battery-pack ground contact. By using the accumulated counts in the charge, discharge, and self-

discharge registers, an intelligent host controller can determine battery state-of-charge information. An internal offset count register improves accuracy.

The bq2018 features 128 bytes of NVRAM, including 115 bytes of user RAM for storing battery characteristics, charge data, or ID information, thus eliminating the need

#### **Edited by Harv Weiner**

for a separate battery ID chip. An internal ADC and reference operate from 2.8 to 5.5 V and at less than 80  $\mu$ A. Standby-mode current is less than 10  $\mu$ A and data-retention current is less than 50 nA, so critical information can be stored for over 10 years with 5 mAh of battery capacity.

The 8-pin, 150-mil SOIC package of the bq2018 is small enough to fit in the crevice between two adjacent cells. It is priced at \$1.85 in 10k quantities. The bq2118 Power Minder miniboard incorporates all of the necessary components for a fully functional implementation that sells for \$4.40 in 10k quantities.

Benchmarq Microelectronics, Inc. 17919 Waterview Pkwy. Dallas, TX 75252 (972) 437-9195 Fax: (972) 437-9198 www.benchmarg.com

#501

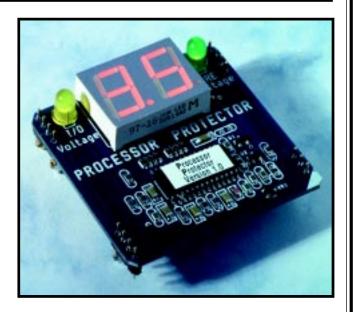

#### PROCESSOR PROTECTOR

Incorrect jumper settings for the dual voltage levels on new microprocessors manufactured by AMD, IBM, Cyrix, and Intel can shorten CPU life and cause erratic operation. System lockup, memory errors, and other intermittent phenomena may be the result of an over- or under-voltage condition. Poorly written instruction manuals and the limitations of verifying the core voltage on the chip are two reasons why incorrect settings can occur. The

**Processor Protector** provides a simple means to confirm the proper values.

The Processor Protector plugs into the CPU socket and indicates the value of the core and I/O voltages applied on a two-digit LED. Lights on the unit indicate which voltage is being measured. The Processor Protector is compatible with Socket 5 and 7 mother-boards and sells for \$59.

Autotime 6605 SW Macadam Blvd. Portland, OR 97201

(503) 452-8577 • Fax: (503) 452-8495

www.autotime.com

## NEW PRODUCT NEWS

#### TMS320C6x SINGLE-PROCESSOR DEVELOPMENT SYSTEM

The **HEVAL6A** TMS320C6x single-processor development system integrates a 200-MHz (1600 MIPS) TI TMS320C6201 processor with several memory types, including SBSRAM, SDRAM, and asynchronous SRAM. A mezzanine slot supporting a pair of serial interfaces and two I/O interface slots supporting a variety of data-acquisition and communications modules enable developers to integrate the hardware into their chosen application environment. The DSP hardware can be programmed and debugged via the PC board's 16-bit ISA-bus host interface and JTAG controller. It can be booted without a host computer (for stand-alone or embedded applications) via its onboard flash memory.

Development tools include the TI 'C6x Code Development Tools (C compiler, assembly optimizer, assembler, and linker), software loader utility, GO DSP Code Composer for C source debugging, and PC-based API for DOS and Windows.

The HEVAL6A is priced at \$14,000.

Traquair Data Systems, Inc. 114 Sheldon Rd. Ithaca, NY, 14850 (607) 266-6000 • Fax: (607) 266-8221 www.traquair.com

#503

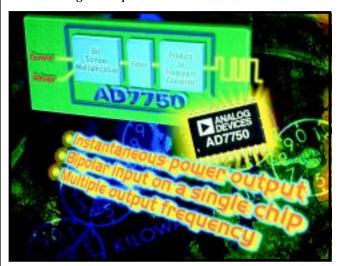

#### POWER-TO-FREQUENCY CONVERTER

The **AD7750** is designed for residential and industrial power-metering applications. It can be configured for power measurement, voltage-to-frequency conversion, or converting the product of two voltages to a frequency.

It contains two ADCs, a multiplier, offset compensator, digital-to-frequency converter, reference, and other conditioning circuitry. Both channels are driven by differential gain amplifiers—channel 1 with selectable

gains of 1 and 16, and channel 2 with a gain of 2. A high-pass filter can be switched into the signal path of one channel to remove offset effects.

The AD7750's switched-capacitor architecture allows a bipolar analog input of 11~V with a single 5-V power supply. Nonlinearity for either input is less than 0.05% maximum.

The device features two sets of frequency outputs that consist of fixed-width pulse streams with pin-selectable frequencies. Low frequencies are suitable for stepping motors, while higher frequency pulse streams are appropriate for calibration and test. In the signed mode, outputs can be configured to represent the result of four-quadrant multiplication. In the unsigned mode, magnitude-only outputs are always positive regardless of the input polarities. A reverse-power indicator activates when negative power is detected in the unsigned mode.

The AD7750 comes in 20-pin SOIC and DIP packages and is priced at **\$2.50** in 100,000-piece quantities.

Analog Devices, Inc. 804 Woburn St. • Wilmington, MA 01887 (781) 937-1428 • Fax: (781) 821-4273 www.analog.com

## NEW PRODUCT NEWS

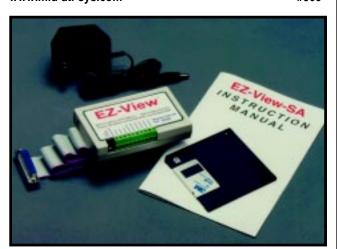

#### SCOPE UTILITY SYSTEM

**EZ-View-SA** functions as a data-acquisition system, oscilloscope, digital voltmeter, and chart recorder. The hardware module attaches to a parallel printer port and provides six single-ended channels of input with 12-bit resolution. An input range of  $\pm 10$  VDC is available at an input impedance of 330 k $\Omega$ .

The software features auto-installation and configuration, mouse or keyboard control, remote start, and trigger controls. It works with all MS-DOS-, Win3.1-, and Win95-based computers with '386 or higher processors and VGA or better screens. Operating modes include real-time monitoring (oscilloscope), data acquisition (record), and rapid record (burst).

Features include gain adjustments, bias offsets, scale selection, variable sampling-rate and run-time selection, channel labeling, triggering, auto-scaling, and remote-start options. Acquired data can be transported to standard spreadsheets and expanded for detailed analysis. A notes feature permits a brief text description of the data to be attached to saved files.

EZ-View-SA costs **\$199**, including the data-acquisition module, power supply, data cable, instruction

manual, and screwdriver. Options include 16-bit data resolution, remote battery power supply, and probes.

Mid-Atlantic Systems Co. 2284 Golden Pond Ct. • Fenton, MI 48430-1097 (810) 750-4140 • Fax: (810) 629-4988 www.mid-atl-sys.com

## EW PRODUCT NEWS

#### WIRELESS KEYBOARD

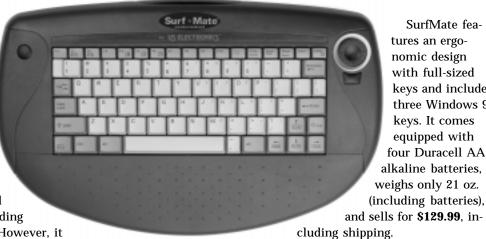

**SurfMate** is a 79-key plug-n-play wireless keyboard that requires no software installation. The user plugs Surf-Mate's receiver unit into the computer's keyboard port to establish the interface. An optional integrated pointing device replaces the mouse. Surf-Mate is compatible with all Internet applications, including Web browsers and E-mail. However, it

SurfMate can be positioned almost anywhere in a room and still maintain complete control of the computer. It transmits through infrared LED at distances up to 45' (14 m) and, depending on the distance to the PC, at horizontal angles up to  $\pm 60^{\circ}$  and vertical angles up to ±50°.

can be used with any software (e.g., presentation

programs, games, word processing, accounting, etc.).

**US Electronics** 585 N. Bicycle Path, Ste. 52 Port Jefferson Station, NY 11776 (516) 331-2552 • Fax: (516) 331-1833 www.uselectronics.com/surfmate

SurfMate fea-

tures an ergo-

nomic design

with full-sized

keys. It comes

equipped with

four Duracell AA

keys and includes three Windows 95

#### **FEATURES**

60

66

Low-Cost Voice Recognition

Building an Embedded Web Server from Scratch

Integrating Windows NT 4.0 into a TCP/IP Environment

Codesign: The Evolving Relationship Between Hardware and Software

Choosing the Right

Crystal for Your Oscillator

## FEATURE ARTICLE

**Brad Stewart**

## Low-Cost Voice Recognition

Brad's Tiny Voice—based on an 'HC705 and powered off a 9-V battery—can be trained to recognize up to 16 command templates and costs less than \$5. Toys, voice-activated padlocks, and remote controls had better listen up.

oice recognition has come a long way in the past five years, due mainly to the advent of cheap and powerful PCs equipped with Pentiums and MMX technology. Performance continues to improve to the point where parts of this article were comfortably voicedictated via Kurzweil VoicePlus.

But, this performance comes at a cost. You need fast Pentiums with MMX, at least 16 MB of DRAM, and even more disk stroage.

What if your application has a budget of a couple dollars? Can you still embed some form of voice recognition or voice command and control into your product?

In this article, I'll show you how to implement a voice-command system for under \$5. I conclude with some application examples and recommendations to improve the system even further.

#### **TINY VOICE**

My system—Tiny Voice—is based on a low-cost, 20-pin single-chip controller. It's a speaker-dependent, templatebased, isolated-word recognizer. You train it to recognize your voice.

Up to 16 voice patterns are stored in a nonvolatile 512-byte serial EEPROM. Five push buttons enable programming

and operation, and seven LEDs give status.

For embedded systems, Tiny Voice can be controlled over a parallel or serial protocol from a host microcontroller or it can run stand-alone. The source code may be modified to fit your requirements.

At under \$5, Tiny Voice won't do dictation. But, it's good for applications like toys, repertory phone dialers, voice-activated padlocks, security systems, remote controls, and other low-cost consumer products.

A voice command can be one or several words, with a total maximum length of 1.6 s and a mini-

mum of 0.2 s. Response time is typically <100 ms. By carefully selecting the vocabulary and context, over 95% recognition accuracy is possible.

The heart of the system is the 68HC-705J1A Motorola 8-bit processor. There were a number of reasons why I chose this part over a comparable one from Zilog or Microchip.

There's sufficient RAM (64 bytes) to buffer the input waveforms and hold template structures, and its 1240 bytes of ROM provide enough program storage. Also, interrupts are supported, including changes on the I/O lines.

This system is inexpensive (<\$2) in high volume. The development kit is cheap, too, at \$99.

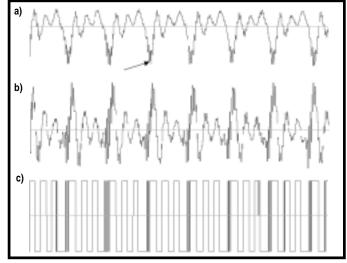

Figure 1a—This is a waveform of the voiced sound "ee" as in "speech." The arrow points to high-frequency wiggles corresponding to the second formant (F2). Note that these wiggles do not cross the zero axis. b—After preemphasis or high-pass filtering, the F2 components now cross the zero axis with the same waveform. c—After being infinitely clipped, the waveform of Figure 1b is a square wave showing both F1 and F2 components. This signal is applied to the microprocessor via a digital input pin.

Shown in Photo 1, the Tiny Voice system was built on a  $3'' \times 3''$  breadboard and is powered off a 9-V battery. Standby current consumption is ~2 mA, which is primarily due to the op-amp and electret microphone bias.

With some added power management, standby current could be reduced to a few microamps. Operating power while sampling and analyzing speech is ~10 mA.

#### THEORY OF OPERATION

The 68HC05 processor is very simple. There are no ADCs, so you need a way to convert the time domain signal to a format the microcontroller can recognize.

The small amount of memory requires a lot of approximations and simplifications to convert the speech into a small set of features.

To meet these limitations, I use a simplified formant tracker. The microphone input is high-pass filtered and then infinitely clipped using two operational amplifiers. The resulting square wave is connected to an MCU input.

By sorting and tallying long and short pulse widths of the square wave, you get a crude but effective two-channel frequency analyzer. One channel gives frequencies below 1500 Hz, and the other ranges from 1500 Hz to 5 kHz.

These two frequency areas roughly define F1 and F2, the two formant regions of speech. It's a well-known principle that F1 and F2 for a given speaker and a given set of vowels remain the same.

Using F1 and F2 was first tried in 1952 by Bell Labs employing vacuum tubes and capacitors for memory. Crude as it sounds, that system achieved 97% recognition accuracy!

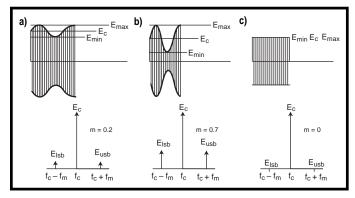

The input signal is high-pass filtered (i.e., pre-emphasized) to accentuate the F2 frequencies. Figure 1 illustrates why this is necessary.

Figure 1a is a sample of the voiced vowel sound "ee" as in "speech." Note the F2 component shown by the arrow. Also note that these high-frequency

wiggles do not cross the zero axis. Thus, if the waveform is infinitely amplified and clipped, the square wave would not reveal the F2 component.

However, Figure 1b shows what happens after pre-emphasis. The F2 wiggles cross the zero axis, and the resultant infinitely clipped square wave now contains both F1 and F2 (see Figure 1c).

#### **TINY HARDWARE**

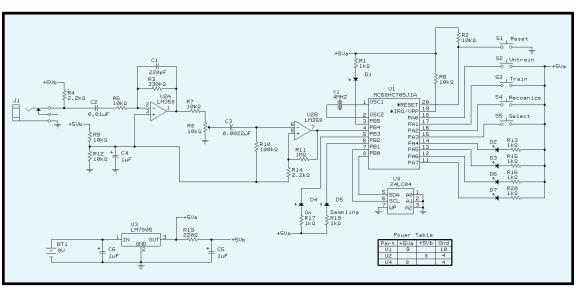

Figure 2 shows a schematic of the system. An electret condenser microphone is biased to 5 V via R4. The signal is then amplified by U2a.

C2 and R6 (along with C3 and R10) form a highpass filter, with a cut-off frequency of 1600 Hz with an added zero at 800 Hz. This setup provides a pre-emphasis function.

C1 serves as a mild antialiasing low-pass filter. The output is fed to the second op-amp, which is configured as a comparator with some hysteresis. R8 sets the

threshold of the comparator.

The comparator's output is a square wave that's applied to an input pin of the processor. The threshold defines the beginning and end of a speech utterance. With no signal present, the second op-amp's output is at a DC level.

Voice pattern data is stored in a non-volatile EEPROM. For this project, I selected Ramtron's FM24C04, which uses ferroelectric cells.

It has several advantages over a more generic part. For one thing, the FRAM part can be written to over 10 billion times, compared to about 10k cycles with a generic EEPROM. This feature is important here because the first 128 bytes are used for scratch-pad memory and are constantly written to.

Also, it has a deep write buffer. So, once the starting address is specified, memory address is autoincremented

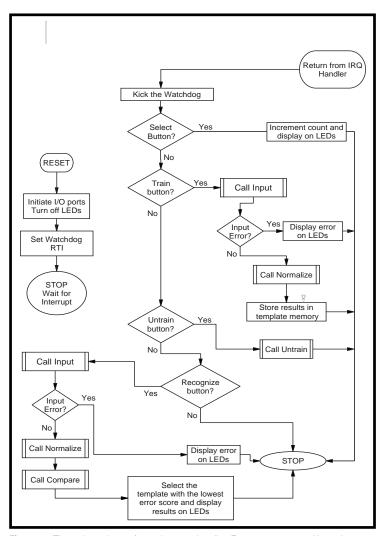

**Figure 3**—The main routine performs the event handler. Events are generated by an interrupt caused by pressing a push button or by system reset. The events dispatched are Select, Train, Untrain, and Recognize.

and additional writes can be performed with no more intervention. As a result, writing to the device is very fast.

Generic parts, however, require you to set up the address every other byte before you write data. This task creates additional time overhead that may cause a bottleneck in the software flow—a major concern in a real-time system.

The FM24C04 has a low standby current of 25  $\mu A$  as well as a low operation current of 100  $\mu A$ . So, it's well suited for battery operation.

The EEPROM's first 128 bytes hold the transformed input utterance to be recognized or trained. Locations 128–512 store the feature vectors of a previously trained utterance. Each vector occupies 24 bytes, so the maximum number of templates that can be stored is 16.

The rest of the circuit comprises a 5-V regulator, switches, and LEDs.

#### TINY USER INTERFACE

Before discussing the voice-recognition software, I want to describe the interface and how the system works from the user's point of view.

Seven LEDs and four switches compose the Tiny Voice user interface. LEDs D2, D3, D4, and D5 make up a four-bit binary number that gives Tiny Voice's status. It can either be the index of a voice command or an error message.

When power is connected or when the Reset switch is pressed, the Stop mode is entered. Pressing a push button activates the system and performs a certain function.

Pressing Select displays a binary number from 0 to 15 on four LEDs which selects the template number to be trained or untrained. Each time Select is pressed, the number increments to 15 and back to 0.

Pressing Train starts the Training mode. The On LED is activated, and the user is prompted to

say the command to be trained.

While the user is speaking, the Sampling LED is lit during periods of speech and off during periods of silence. If the training is successful, the template is stored in EEPROM at the selected template location and the system enters the Stop mode.

Untrain modifies the data in the stored template so the pattern-matching algorithm skips over this template and does not consider it as a possible candidate.

This is useful for context switching of vocabularies. For example, out of the 16 templates, you may only need to scan for two words (e.g., "yes" or "no"), while ignoring the remaining 14.

To enable a template that was previously untrained, press the Train button and then press another button (e.g., Select) before speaking.

Photo 1—My prototype was built on a 3"× 3" breadboard and is powered off a 9-V battery. The only ICs are the 68HC705J1 processor, LM358 dual-operational amplifier, the 4096-bit FM24C04 FRAM serial memory, and a 78L05 5-V regulator.

In Recognition mode, the speech is sampled and analyzed. The On LED is activated, and the user is prompted to say a previously trained command. As before, the Sampling LED is lit during speech and off during periods of silence.

The input is compared to the templates in memory and a decision made. If recognition is successful, the result is displayed on the four LEDs in binary.

When Reset is pressed, Stop mode is entered and the system is ready to accept a push-button command. Previously trained commands are not erased.

When an error occurs, the Error LED (D1) is lit and the error code is displayed in binary using the same four LEDs that display the template index number. After  $\sim$ 2 s, the LEDs go off and the system enters Stop mode.

The error codes—Time Out, Buffer Full, and Not Recognized—are defined in the header file.

After Train or Recognize is pressed, the system waits for valid speech input. If no input occurs after ~6.5 s, the system enters the Stop condition and the Time Out error code is displayed.

On the other hand, if the length of the utterance is longer than 1.6 s, the system enters the Stop mode and the Buffer Full error is displayed.

The Not Recognized error code is displayed if the input utterance doesn't match a stored template. The system then enters Stop mode and waits for new input.

#### TINY ALGORITHMS

The software for Tiny Voice was written entirely in assembly. There is a total of eight routines.

The main program, MAIN.ASM, responds to events and schedules the remaining subroutines.

COMPARE. SUB handles the pattern matching. It compares the input template to each active template in memory and calculates the best match.

EEPROM. SUB handles the reading and writing of data to the EEPROM. It bit-bangs two I/O pins to simulate an I<sup>2</sup>C protocol used by the EEPROM.

IRQ. SUB is the interrupt handler. Interrupts are caused by a button press.

The most complicated routine is INPUT. SUB. It samples the input, determines where the word starts and ends, and builds up the voice template.

TIME\_NOR.SUB normalizes the length of the speech input to a fixed length of twelve two-element data values.

DIV16\_8. SUB is an integer divide routine that divides a 16-bit number by an 8-bit number. This routine is called repeatedly by the time-normalization routine.

And finally, DELAYMS. SUB is a simple program where a delay is set by the value passed in the accumulator.

Tiny Voice is entirely event-driven and spends most of its time in the Stop mode. Events are caused by the interrupt of pressing push buttons. The event handler is shown in Figure 3.

#### INPUT ROUTINE

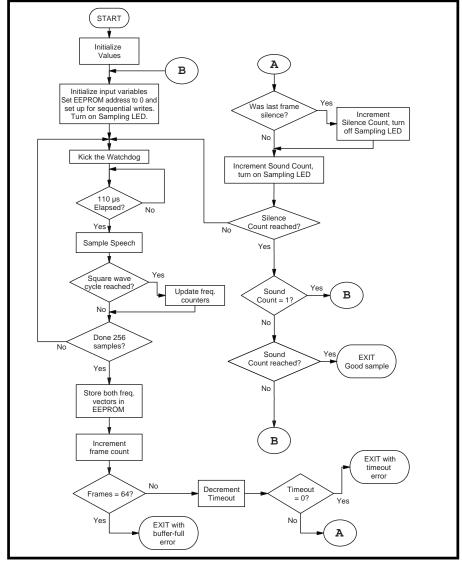

When a Recognize or Train event occurs, the input routine is invoked (see Figure 4). A timer is set up and polled until 110 µs has elapsed.

An interrupt routine could have been used to time the samples every  $110 \mu s$ ,

but I was concerned that the overhead to service the interrupt might make it difficult to complete all the paths in the input routine within 110 µs.

Once the time elapses, the input square wave is sampled. If the sign changes from the previous measurement, one of the two frequency bytes is updated.

The threshold limit is set to six. In other words, if the pulse (positive or negative) is greater than six samples (roughly corresponding to 1.5 kHz), the "high" frequency byte is incremented by one. If it's less than six, the "low" frequency byte is incremented.

The rest of the routine is basically a state machine that uses speech activity as an input to determine a utterance bounded by silence. At each rising or falling edge, another byte counts the zero crossings.

After 256 samples, a frame counter advances and several tests are made. If the frame counter is greater than 64, the input buffer is filled (i.e., you spoke too long) or there is too much background noise, and an error is generated.

Otherwise, a timeout value is decremented and tested. This setup enables the routine to exit if too much time elapses before any sound is input.

If the buffer isn't full or a timeout has not occurred, then it tests the zerocrossing counter. Too low a value signifies silence, and a silence counter is incremented.

Otherwise, a sound-activity counter is incremented. If the sound-activity value is above a certain threshold and the silence value is high enough, the routine exits with a valid data sample.

#### TIME NORMALIZATION

Words vary in length. But for this algorithm to work, the lengths must be normalized to a fixed value.

Each sample consists of two bytes sampled over one frame of 256 samples. The unnormalized data in the first 128 bytes of the EEPROM is normalized to a set of 12 vectors in main RAM.

The vector in RAM is built up, element by element, by down- or upsampling the raw data in EEPROM. Since there are two elements per feature, a template has a fixed memory length of 24 bytes.

Figure 4—Every 110 μs, the square-wave input is sampled and several options are considered, depending on the state of the frame, zero-crossing, silence, and sound counts. The state machine effectively captures the input utterance, while rejecting short bursts and input errors due to excessive background noise.

#### THE MAIN ROUTINE

If the event is for training, the normalized vector in RAM is stored in memory according to the template number selected. Templates are stored in memory locations 128–512, which allows for sixteen 24-byte templates. No comparisons are performed.

If the system is recognizing, the normalized input utterance, which is stored in RAM, is compared element by element to each previously trained template stored in EEPROM.

The comparison is a simple Euclidean distance measure, and an error value accumulates. The minimum error value is selected and compared to a threshold.

If the result is above the threshold, the system rejects the recognition. If the value is low enough, the word is recognized.

Well, almost. Two more criteria must also be met: the score must be low enough, and the two smallest scores must differ by a large enough value.

#### TINY APPLICATIONS

For testing purposes, the system was trained with eight words: "VCR", "television", "telephone", "stereo", "CD", "PC", "yes", and "no". Each word was trained twice, thereby occupying 16 templates.

Recognition accuracy approaches 100% when background noise isn't too severe. It also works with ~90% accuracy using speakers who didn't train the system.

A speaker-independent vocabulary can be constructed by having multiple trainings of a few words. For example, training "yes" and "no" eight times over a set of different speakers yields excellent results.

A note of caution: when using Tiny Voice, don't use a lot of short words (e.g., the numbers "one", "two", etc.). They're a bit beyond its capabilities.

And watch for commands that sound alike. For example, "on" and "off" will get you in trouble. Instead, try "turn on" and "off please".

A fun application might be a voiceactivated padlock. Change the code so you have to enter one, two, or three voice commands in sequence. Then, multiply the scores. If the result is small enough, then "open sez me."

#### FUTURE TINY ENHANCEMENTS

Naturally, there are ways to improve the system. I was surprised by the HC05's speed. I also wound up with at least 200 bytes of leftover ROM for more code. Tiny Voice's code is modular, and updates can be easily added.

I can increase the EEPROM capacity to 1 or even 2 KB. This size would provide more template storage or allow for more frame features to better resolve differences in speech patterns.

I'd also like to add some fuzzy logic to the pattern-matching algorithm to improve recognition accuracy and the rejection criteria.

Adding a serial port instead of push buttons and LEDs could reduce cost and add more functionality. Threshold values could be changed, templates uploaded and downloaded, and so on.

I want an MCU-controlled gain adjustment on the input for different microphone levels and background noise.

Another improvement would be to add a dynamic time warp (DTW) algorithm to the pattern-matching routine. The DTW takes into account slight variations on how each word is pronounced—in particular, variations in lengths of phonemes.

But with only 200 bytes of code space left over, adding a DTW would be challenging. A first-order approximation may be achievable, however.

I'd rather use C than assembly language. When I started this project, I knew squeezing this functionality into 1200 bytes would be tough. So, a high-level language was out of the question.

Since then, I've had the opportunity to try out a C compiler from Byte Craft. The good news is, it generates small enough code. The bad news: I wish I'd used it earlier.

And as a final wish, I would like to use a different processor. Of all these improvements, this one is probably the best. You can now get equivalent MCUs with built-in ADCs, which would provide more elaborate signal processing and better noise rejection.

One of the best candidates for a low-cost system is the Sharp SM8500 8-bit MCU. It has almost everything you need for an embedded voice-command system, including a 10-bit ADC (8 channels) and an 8-bit DAC, which is useful for voice feedback and verification.

The SM8500 features SIO and UART ports to communicate with other system devices, 2 KB of internal RAM, as well as internal ROM and the ability to access external ROM or RAM. It also offers 80+ I/O pins for keypad and display interfacing, hardware multiply and divide, and a 250-ns instruction cycle time. And, it costs under \$3.

If you're willing to spend a bit more, then a new level of performance may be realized. New 32-bit RISC MCUs are becoming available in the sub \$15 or even sub \$10 range.

For example, the Sharp ARM710M RISC processor, running at a conservative 16 MHz, performs a complete FFT-Mel-Cepstrum analysis using only 50% of the processor's resources.

With the ability of RISC processors to address large amounts of memory, you have the ingredients to put together a dictation system like the one I'm using now. And, it can run off a couple pen-light batteries!

Brad Stewart is currently the product technical manager for RISC processors at Sharp Electronics. He also served as technical director for IPI, which specialized in voice-recognition and speech-compression software, and vice president of Covox, which specialized in multimedia products. You may reach Brad at bstewart@e-z.net or bstewart@sharpsec.com.

#### **SOFTWARE**

Source code (tinyvoice.zip) for this article may be downloaded from the Circuit Cellar Web site.

#### **REFERENCES**

B. Georgiou, "Give an Ear to Your Computer," *BYTE*, 56–91, June, 1978

Motorola, MC68HC05J1A Technical Data Manual, 1997.

Sharp Electronics, SM8500 User's Guide. 1997.

B.C. Stewart and S. Sidman, "Design and Use of Voice Recognition in Embedded Applications," Paper presented at ESC East, Boston, MA, 1997.

#### **SOURCES**

#### 68HC705J1A

Motorola MCU Information Line P.O. Box 13026 Austin, TX 78711-3026 (512) 328-2268 Fax: (512) 891-4465

#### FM24C02

Ramtron Intl. Corp. 1850 Ramtron Dr. Colorado Springs, CO 80921 (719) 481-7000 Fax: (719) 481-9294 www.ramtron.com

#### C Compiler

Byte Craft Limited 421 King St. N. Waterloo, ON Canada N21 4E4 (519) 888-6911 Fax: (519) 746-6751 www.bytecraft.com

#### ARM710M, SM8500

Sharp Electronics Corp.

Microelectronics Gr.

5700 NW Pacific Rim Blvd., Ste. 20

Camas, WA 98607

(206) 834-2500

Fax: (206) 834-8903

www.sharpmeg.com

#### IR S

401 Very Useful 402 Moderately Useful 403 Not Useful

## FEATURE ARTICLE

**Richard Ames**

## Building an Embedded Web Server from Scratch

Tired of surfing?

Ready to make some waves of your own?

Richard demonstrates how to implement your own embedded

Web server—from creating a base

TCP/IP application to writing interactive

HTML forms.

eb surfing may be an absorbing and potentially educational activity, but there's something about it that's just so...passive. Sometimes, you yearn to not only partake of the networked wonders of the world, but to add to them as well.

So, you take this opportunity to create your own Web page, complete with scanned images of your pets, a local map highlighting your favorite pizza parlors, and links to magnetic media duplicators.

But, the hit counter isn't incrementing quickly. And besides, the page is stored on some massive drive in some computer you've never seen before.

Being a hands-on sort of person, you're ready for the next step. It's time to put together your own embedded Web server from scratch.

Your own Web server can do a lot more than serve up text and GIFs. It can also provide a way to monitor and control an embedded system.

Since powerful Web browsers are given away free today, there's a great opportunity to add a graphical front end to control your embedded system and display status or supply control parameters in a user-friendly manner.

Fortunately, the protocol that describes the operations of a Web server

is rather straightforward. The most recent version of the formal specification HTTP 1.1 is contained in RFC 2068. The preceding version—HTTP 1.0—is simpler to implement and widely supported.

The example I present here follows the earlier standard. But first, let me briefly summarize Web-server operation.

#### SERVER OPERATION

In a typical client/server system, the client establishes a connection with the server, submits a request to the server, interprets the server's response, and then sends further requests or closes the connection if it's no longer needed.

A Web browser is a client application that establishes a connection with a Web server, requests a resource from the server, reads the information that the server sends, displays it using the built-in formatting information, and then closes the connection.

If the page just loaded contains references to multimedia resources that haven't been loaded yet, then additional connections are established to read and display this information.

This action continues until all the resources on a Web page are retrieved. At this point, the system waits for you to click on a new resource, which leads to a server being contacted to request the new resource and the cycle starts anew.

To implement your own Web server, you need to create your own TCP/IP application that runs on top of a TCP/IP stack. The application establishes the connection, reads and writes data, and closes the connection using func-

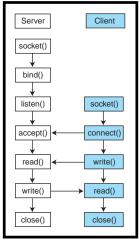

Figure 1—When clients and servers are written using the BSD Sockets interface, these are the typical function calls made to transfer information.

**Listing 1**— This code implements a minimal Web server that can be set up to deliver ROMed Web pages. This example compiles and runs under Linux, and can be easily adapted for other environments.

```

#include <stdio.h>

#include <sys/types.h>

#include <sys/socket.h>

#include <netinet/in.h>

#include "romfile.h"

#define HDR "HTTP/1.0 200 OK\r\n"

#define HDRHTML "Content-type: text/html\r\n"

#define HDRJPEG "Content-type: image/jpeg\r\n"

#define DEFAULTRESOURCE "index.html"

main(){

char buf[500]; /* holds incoming request, outgoing response */

char defaultresource[] = DEFAULTRESOURCE;

char resourcename[80]; /* holds name of requested resource */

char *filename;

/* pointer to requested resource */

char *extension; /* ptr to extension for requested resource */

int remSize;

/* holds size of address structure */

int retcod:

/* general purpose return code */

/* handle to listening socket */

int s:

/* handle to socket being serviced */

int s2;

long filelen;

/* size of requested resource */

struct sockaddr_in locAddr; /* addr struct for local address */

struct sockaddr_in remAddr; /* addr struct for remote address */

RFHTYPE rfhandle;

/* handle for rom file */

printf("Sample Web Server v0.0\n");

s = socket(AF_INET, SOCK_STREAM, 0); /* create listening socket */

if (s < 0) {

printf("Error opening socket\n");

return -1;

memset((void *) &locAddr, 0, sizeof(locAddr));

locAddr.sin_family = AF_INET;

locAddr.sin_addr.s_addr = htonl(INADDR_ANY);

locAddr.sin_port = htons(80);

retcod = bind(s, (struct sockaddr *) &locAddr, sizeof(locAddr));

if (retcod < 0) {

printf("Error binding socket\n");

close(s);

return -1; }

retcod = listen(s, 5);

if (retcod < 0) {

printf("Error in listen\n");

close(s);

return -1; }

while (1) {

remSize = sizeof(remAddr);

s2 = accept(s, (struct sockaddr *) &remAddr, &remSize);

if (s2 < 0) {

printf("Error in accept\n");

close(s);

return -1; }

retcod = read(s2, buf, sizeof(buf));

/* read request */

if (retcod >= 0)

buf[retcod] = 0;

/* change to null terminatd str */

printf("%s\n", buf);

write(s2, HDR, strlen(HDR));

/* display request for debug */

/* write first response line */

/* find resource */

sscanf(buf, "GET %s", resourcename);

filename = defaultresource; /* use this resource for deflt */

if (strcmp("/", resourcename) != 0)/* is this default request? */

filename = resourcename + 1; /* no, skip past initial '/' */

extension = filename;

/* isolate extension */

while ((*extension) && (*extension != '.'))

extension++:

if (strcmp(".html", extension) == 0)

/* write type */

write(s2, HDRHTML, strlen(HDRHTML));

else if (strcmp(".jpg", extension) == 0)

write(s2, HDRJPEG, strlen(HDRJPEG));

(continued)

```

tions provided by the stack. (Refer to "TCP/IP in Embedded Systems" [*INK* 79] for an overview of stacks in embedded systems.)

Although the RFCs suggest the general form and the capabilities to be supplied by the interface between a network application and TCP/IP stack, they don't fully specify the Application Program Interface (API).

A number of APIs have been established, but by far the most common is the BSD Sockets interface, which is provided by BSD releases of the Unix operating system. A close relative, the WinSock interface, is used for Windows networking applications.

I'll use the BSD Sockets interface to illustrate a sample Web-server application because it is well known and widely available. Of course, my code may need slight adaptation to work with other TCP/IP-stack implementations.

Figure 1 illustrates a typical sequence of BSD Sockets functions that are called by server and client applications in a network transfer. They act as a road map to the Web-server code in Listing 1.

#### **GETTING A HANDLE ON THINGS**

The Web server's first task is to indicate its interest in receiving TCP segments directed to port 80, which is the default port for an HTTP server. Under BSD Sockets, four function calls are made to set this up.

The first step allocates a socket for the server to use. A socket is a data structure that maintains information on a network connection.

The prototype for the function is:

```

int socket(int domain, int

type, int protocol);

```

The first parameter is the communications domain, which in this case is PF\_INET, indicating that I want to work with the Internet protocol family. Other domains can be specified for other communications families (e.g., ISO).

The next parameter is the socket type, which I specified as SOCK\_STREAM, indicating that I want reliable bytestream service (i.e., TCP). SOCK\_DGRAM would be specified for UDP service.

The final parameter can be used to further specify the protocol, but for Internet bytestream service, a 0 suffices. socket() returns a handle to the socket or -1 to indicate an error.

This seems like a roundabout way of indicating that you want a handle to a socket that talks TCP. However, the BSD Sockets interface is used for more than applications running over a TCP/IP stack.

There's a whole world of protocols—old, current, and yet to be defined—that can be coupled to an application through this interface. The protocol doesn't even need to be a network protocol. For example, the Unix domain protocol permits interprocess communication within the same system.

Once you have a handle to a socket, you need to specify the port at which you're listening for incoming information. This task is accomplished via a call to the bind() function:

```

int bind(int s, struct sockaddr

*my_addr, int addrlen);

```

The first parameter is the handle to the socket that was returned earlier. The second parameter passes a pointer to a socket address structure that specifies the local IP address and port number for this connection.

For Internet addresses, the <code>sock-addr\_in</code> structure is used, which contains fields for the address family, IP address, and port number. You clear the structure and then fill in these values before passing a pointer to the structure in the call to <code>bind()</code>. The port-number field is a two-byte value that should be expressed in network byte order, which is Big Endian.

To make the code portable, the utility function <code>htons()</code> translates between the host's native format and network byte order before saving the value in the structure. The constant <code>INADDR\_ANY</code> indicates that this socket should accept connections from any of the system's network interfaces. This fourbyte <code>IP</code> address also needs to be translated by the <code>htonl()</code> utility function to put it in network byte order before storing the value in the structure.

The last parameter in the call is simply the size of the sockaddr\_in

```

Listing 1—continued

```

```

rfhandle = romfileopen(filename);

/* open local resource */

filelen = romfilelen(rfhandle);

/* determine size */

sprintf(buf, "Content-length: %d\r\n\r\n", filelen);

write(s2, buf, strlen(buf));

/* write size */

/* write out resource */

while (1) {

if ((retcod = romfileread(rfhandle, buf, sizeof(buf))) > 0)

write(s2, buf, retcod);

else

break; }

romfileclose(rfhandle);

/* close resource */

/* close connection */

close(s2); }

return 0; }

```

structure, another indication of the flexible design of the socket's interface. It returns –1 if there is an error.

Now, I have a socket associated with a port. The next step is to put the socket into the listen state, so it's ready to service incoming requests for connections to port 80. This task is done with a call to listen:

```

int listen(int s, int backlog);

```

Here, I simply specify the socket and a backlog value, which indicates the number of connections that will be held in a queue awaiting service. An error is indicated by a -1 return value.

Finally, I make a call to accept a connection:

```

int accept(int s, struct sockaddr

*addr, int *addrlen);

```

Here again, I pass a socket handle and then a pointer to an address structure, followed by a pointer to the size of the address structure.

In this case, the accept() function fills in the IP address and port number of the remote system that is establishing a connection on the socket in the address parameter. The application therefore knows a little about the remote system requesting services when the function returns.

The address-length parameter should contain a pointer to an integer with the length of the address structure. On return from accept(), this parameter contains the length of the address structure that was filled in.

For Internet protocols, this value doesn't change. The accept() function

blocks until a connection is established and then returns a handle to a new socket associated with the client that connected.

The original socket continues to collect subsequent clients that want to connect to port 80. A return value of –1 indicates an error.

#### ITERATIVE VS. CONCURRENT

When a client establishes a connection with a server, the server creates a data structure that holds the state of the connection until the connection closes. The server then listens for and responds to client requests until one side or the other indicates that the connection should be closed.

What happens if another client contacts the server while the first client is being served? The outcome depends on the design of the server.

In an iterative server, the second client's requests are ignored until the connection with the first client closes.

In a concurrent server, the code that services a connection is set up as a task, and this task is launched every time a connection is established. So, a concurrent server can serve more than one connection at once, assuming that the system software supports multitasking.

For this demonstration, I take the approach of an iterative server. This approach isn't the most common for a Web server, but it will do, especially since I expect the server to only service one client at a time.

Other clients that request services are forced to wait until a previous request has been fulfilled. This scenario is often quite workable but doesn't make sense for a large-scale server.

#### **Basic HTML**

Hypertext Markup Language (HTML) is the formatting language that transforms plain text into the attractive Web pages that fill the Internet. Creating effective HTML pages for an embedded system requires an extra measure of skill because you need to make the most of a limited set of resources. We all know how graphic images can eat up memory, so it makes sense to keep GIF images to a minimum and make the most of the other formatting features.

The formatting information is included in the document via tags that appear between angled brackets (e.g., < TT>, which specifies a teletype-like font). The syntactic rules for HTML can be inferred by reviewing examples, and RFC 1866 can be consulted for the specifics of HTML V.2.0.

Much of the formatting is specified by a pairing of a start tag and an end tag, such as <I>italic</I>, where the slash indicates the end of italic font. Some tags stand alone though. For example, <HR> creates a horizontal line across the page.

Tags may also contain attributes which may further specify formatting information. Listing i shows the basic form of a document and when displayed appears as Photo i. In most cases, the browser treats all white space in the same way, allowing you to format the information so it is easier to follow.

The document is made up of HEAD and BODY sections. A TITLE must be present in the HEAD section. This title is typically displayed in a title bar on the Web browser and is also stored in a browser's list of saved links. The BODY section contains the contents of the page. Table i lists some formatting features that can liven up this section.

**Photo i**—The code of Listing i produces this minimal Web page. It looks good as 109,208 pixels.

```

Listing i—A minimal Web page can be rather short. Here are 274 bytes worth.

<!DOCTYPE HTML PUBLIC "-//IETF//DTD HTML 2.0//EN">

<HTMI>

<HEAD>

<TITLE>Embedded Web Server</TITLE>

</HEAD>

<BODY>

<H1>Features</H1>

<UL>

<LI>Intuitive Interface

<LI>Contemporary Styling

<LI>Small Footprint

</UL>

<P>One paragraph is all we have ROM for.

</BODY>

</HTML>

```

A number of utilities—commercial and otherwise—can be used to simplify the creation of HTML text. Most browsers have a View Source option that lets you to see how a particularly neat feature of a Web page has been implemented. Beware of incorporating nonstandard HTML into your ROM, though.

```

<H1>-<H6>

Headers of increasingly less emphasis

Starts new paragraph, leaving a blank space to separate from the previ-

<P>

ous paragraph. A </P> end tag is optional.

<PRE>

Preformatted text. Preserves line breaks in the original text. Usually, line

breaks are ignored and the text is flowed to fit in the browser's window.

<UL>

Starts unordered list, typically presented as a series of bulleted items.

Within this section, the <LI> tag starts a list item.

<0L>

Starts ordered list, similar to above, but with numerals

<FM>

Starts emphasis, often expressed as italics

<STRONG>

Starts strong emphasis, usually in bold

<BR>

Forces line break. An end tag is not needed.

<HR>

Inserts horizontal line

<IMG>

Inserts graphical image

```

**Table i—**These common formatting tags help spice up the text on your pages.

Now is the time for the server to read() a request from the server. The read() function is similar to a file read:

```

int read(int s, char *buf,

int count);

```

The application specifies the socket handle, a pointer to a buffer that stores the incoming data, and the buffer size. When the function returns, the number of bytes that were read is returned.

This value may be less than the requested amount of information, and the application should continue to issue calls to read from the connection if the application-level transaction syntax indicates that more information is expected.

TCP acts like a pipeline delivering a bytestream, and the read() function delivers information as soon as it is available. However, the application developer should be aware that there may be more in the pipeline, especially if the buffer being read is large.

So, let's assume now that the server program is running on your Web server, which you set up with the IP address of 192.168.173.15. You fire up your favorite Web browser and request the URL <a href="http://192.168.173.15/">http://192.168.173.15/</a>>.

**Photo 1**—Using HTML form tags, we achieve something very much like a traditional graphical user interface. Listing 4 contains the code to instruct the browser to generate this image.

**Listing 2**—When you pull up a simple page, your Web browser and server trade data. The request that the Web browser sends to the Web server (a) results in the Web server giving this response (b).

```

a)

GET / HTTP/1.0

Connection: Keep-Alive

User-Agent: Mozilla/3.01(Win95;I)

Host: 192.168.173.15

Accept: image/gif, image/x-bitmap, image/jpeg, image/pjpeg, */*

b)

HTTP/1.0 200 OK

Date: Sun, 06 Nov 1994 08:49:37 GMT

Content-Type: text/html

Content-Length: 1523

<HTML>

<HEAD>

<TITLE> Sample Embedded Web Page </TITLE>

[the rest of the contents of the default page]

</HTML>

```

On the server end, the first buffer of data might look something like Listing 2a. This buffer is filled with the request message from the browser, the first line of which is called the request line. The next lines contain headers that provide additional details about the request.

The request line is of the form:

```

Method <SPACE> Resource <SPACE>

HTTP-Version <CR><LF>

```

This request indicates that the Web browser would like for the server to GET the resource known as "/", and that this request is coming from an HTTP V.1.0 client.

At this point, the Web server should examine the requested resource and provide an appropriate response. Since the resource identified as "/" corresponds to the default Web page, that's the page that will be delivered.

The response might look like Listing 2b. Here, the first line is a status line, indicating that the server was able to locate the resource and is about to send it.

The next three lines are headers providing more information about the resource to be transferred. The first line is a time stamp, which indicates the time that the resource is being delivered by the server, followed by the type and length of the resource.

A blank line separates the end of the header fields from the contents of the resource itself, known as the Entity Body. See the sidebar "Basic HTML" for more details on the formatting and features of hypertext documents.

After this response is sent, the server should close the connection. Under HTTP 1.1, the default behavior is to leave the connection open to reduce the overhead of HTTP transfers.

#### FOLLOWING THE LINKS

The beautiful thing about Web pages is that they can be "deeply intertwingled," as Ted Nelson described the concept when first introducing the idea of hypertext in 1965. Within the body of the first default Web page that is delivered, a number of hyperlinks can be indicated by anchor tags:

```

<A HREF="newstats.htm"> The

Latest Statistics </A>

```

The text "The Latest Statistics" is displayed as a hypertext link on a browser, and should the user point to this text and click the mouse, a fresh GET request will be sent by the browser, specifying the resource indicated in the HREF attribute (i.e., newstats. htm). The Web-browser function that interprets this request tries to look up this resource and deliver it as a fresh Web page to the browser.

#### FROM DISK TO ROM

The easy way to satisfy a resource request is to defer to a file system to look up and deliver the resource requested by the Web browser. Unfortunately, a file system isn't standard equipment with all embedded systems.

A reasonable facsimile, however, isn't hard to come by. Instead of storing information in a file on a disk, the same information can be compiled into large arrays of data that can be linked into the image in the embedded system's ROM.

To accomplish this, the example Web server includes two utility programs. The first utility, rfmake, converts a binary file into an array of data that is acceptable to a C compiler.

After all of the file images have been converted into C data arrays, these arrays are collected into a directory-like structure using the romdir utility. The output from romdir is another C structure that acts as a directory to all the ROMed file images.

When the output from the utilities is linked in with the Web server, this data can be accessed through a set of routines that resemble file I/O functions (see Listing 3). Another advantage of this system is that if a disk-based file system is available, then the server program can easily be adapted to use real file I/O functions.

#### INTERACTIVITY

Although it may be great fun to have your embedded Web server dishing up those pages with the best of them, things get really interesting when you add interactive functions.

To accomplish this, the server needs to be implemented with a combination of appropriately written HTML documents and functions that can interpret interactive requests, such as image maps and forms.

An image map is usually included in the body of a page as part of an anchor, such as:

```

<A HREF="panelmap"><IMG ISMAP

SRC="panel.gif"></A>

```

The ISMAP attribute in the IMG tag indicates that this image should be treated in a special way. The contents of panel.gif will be displayed as a clickable image on the browser, and when the user clicks within this area, a request is sent to the server specify-

ing the offset into the bitmap where the mouse click occurred.

The server may see a request for panelmap?12,4, which indicates that the user clicked inside this area at a point 12 pixels from the left edge and 4 pixels down from the top of the image.

By supplying a routine on the server that interprets location information, the system recognizes the object a user points to and responds appropriately. So, clicking on a darkened window in an image of a house might command a home controller to turn on the lighting in this area.

To obtain full style points, the server could update the image with one that shows the window being lit.

Form submission is another technique that can be used to send information to a server, providing many of the familiar dialog box tools, such as text boxes, check boxes, radio buttons, and lists. These features start with a FORM tag in an HTML document.

Listing 4 presents an example of a form with two text boxes and a submit button. The second line refers to the first text box. The fourth line in the form definition defines the submit button, which is needed whenever there is more than one input in a form.

The user can type any text string into the boxes for the time at which the home controller should turn the lights on and off. When the user clicks on the submit button, the home-control Web server is sent the request:

```

control?LiteOn="7:00p";

LiteOff="9:30p"

```

Photo 1 displays this interface.

Again, an appropriate routine needs to be provided on the server to interpret this information and take appropriate action. The server should also generate a page that tells the user that the command was successfully processed.

#### **ERROR HANDLING**

In a number of situations, the Web server may not be able to respond to a request. The user may have typed in a request for a resource the server has never heard of, or the user may have used an interactive control to submit information the server won't accept. **Listing 3**—These function prototypes form the link between the Web server and a file system. They have been defined to make it easy to use either a disk- or memory-based file system.

```

RFHTYPE romfileopen(char *romfilename);

long romfilelen(RFHTYPE handle);

int romfileread(RFHTYPE handle, char *buf, int bufsize);

int romfileclose(RFHTYPE handle);

```

**Listing 4**—In the second line of this section of HTML, TYPE=TEXT specifies that the form's input will come as a text box, NAME="LiteOn" is the variable name associated with the input, SIZE=10 entails that 10 spaces will be available in text box, and Lights On is the label to be displayed beside the box on the form. See Photo 1 for the end result.

When everything is in order, the server sends the string "200 OK" response as part of the status line for the response.

Additional three-digit codes that are suitable for other conditions that might arise are divided into a series of related responses.

Codes in the 100 series are informational, the 200 series indicates success, the 300 series indicates a need for redirection, and the 400 and 500 series are for client and server errors, respectively.

For example, a request for an unknown resource could generate a status line containing "404 Not Found". In the response, the Entity Body could contain HTML text to further explain that the resource couldn't be found on this server.

#### ON YOUR OWN

Of course, this discussion just begins to describe the sorts of capabilities that might be implemented on an embedded Web server.

Additional information on HTML and HTTP is available online and from a library of ever thicker books, and there's a variety of software tools that do everything from verifying the syntax of an HTML page to providing a turn-key server.

Now you can sleep well, knowing your home page could be served up from a networked controller living in a shoebox under your bed. ▲

Richard Ames is a staff engineer at U.S. Software. He finds that working with networking software allows him to gather more computers around him than the average engineer. You may reach Richard at richard@ussw.com.

#### **SOFTWARE**

The rfmake and romdir utilities discussed in this article are available on the Circuit Cellar Web site.

#### REFERENCES

- S. Berners-Lee, R. Fielding, and H. Nielsen, *Hypertext Transfer Proto- col—HTTP/1.0*, RFC 1945, 1996.

- T. Berners-Lee and D. Connolly, Hypertext Markup Language— 2.0, RFC 1866, 1995.

- R. Fielding, J. Gettys, J. Mogul, H. Frystyk, and T. Berners-Lee, *Hypertext Transfer Protocol—HTTP/1.1*, RFC 2068, 1997.

- T.H. Nelson, *Computer Lib/Dream Machines*, Tempus Books, Redmond, WA, 1977 (Reprinted by Microsoft Press).

- D. Raggett, *HTML Tables*, RFC 1942, 1996.

- W.R. Stevens, *Unix Network Programming*, **1**, Prentice-Hall, Englewood Cliffs, NJ, 1998.

#### IR S

404 Very Useful 405 Moderately Useful 406 Not Useful

## FEATURE ARTICLE

#### **Bill Payne**

## Integrating Windows NT 4.0 into a TCP/IP Environment

Bill needs to connect Windows NT stations into an existing TCP/IP network, but Microsoft gave the Domain Name Server its own personal twist. After reviewing the protocols, he shows how to get Windows and Unix to talk.

was recently involved in a large-scale project in which I integrated Windows

NT 4.0 servers and workstations into an existing TCP/IP network. The network comprised multiple Unix,

IBM mainframe, PC, and DEC Alphabased hosts.

In addition, approximately 3000 clients were to be upgraded from Windows 3.11 to Windows 95 and Windows NT 4.0 Workstation.

The network used the Dynamic Host Configuration Protocol (DHCP), an open industry standard designed to reduce the complexity of managing a TCP/IP network.

Every computer and resource on a TCP/IP network must be given a unique IP address and computer name. DHCP assigns a client an IP address from a pool of addresses when it starts up. This enables the IP addresses to be managed from one central point on the network.

The network also uses the Domain Name System (DNS) for name-to-IP address resolution. Cisco routers were implemented to segment the network into smaller manageable sections.

After the initial installation of the Windows NT 4.0 servers, we began having problems with the address resolution process on various clients

throughout the network. And, the problem wasn't DHCP. It worked properly, assigning IP addresses to client workstations as requested.

But, if we used a command that tried to resolve a name to an IP address, we had problems. Sometimes the name would resolve, but not necessarily.

We also began seeing a lot of traffic on the segments that had been created with the routers. One thing stood out—if the name to be resolved was on the same segment as the client issuing the query, it worked.

After many hours of going through traces from a network sniffer, the problem was found and corrected. It turns out that even though DNS is a standard, certain companies give it their own personal twist.

Such is the case when interconnecting devices that use the enhancements developed by Microsoft. The problems do not manifest themselves until routers are added to a network.

Routers in general do not forward broadcast messages. The reason for using routers in the first place is to segment the network and to isolate traffic to separate segments.

Windows NT relies on a process called Windows Internet Name Service (WINS) for name resolution. This service augments the traditional DNS service with dynamic name registration capabilities and uses the NetBIOS protocol encapsulated in TCP/IP for communication between nodes.

To help you gain an understanding of the problem, I first present the basic concepts of TCP/IP, DNS, and WINS as implemented by Microsoft. Once you have the nuances down, interconnecting systems using TCP/IP in a routed network becomes fairly straightforward.

#### TCP/IP

The Transmission Control Protocol/ Internet Protocol (TCP/IP) suite is a standard set of networking protocols. It was originally developed by the Department of Defense and is sometimes referred to as the DOD model.

A protocol is an agreed-to set of rules governing the communication of data between two parties. You could compare it to two people trying to communicate with each other. They must both speak the same language or no transfer of information occurs.

TCP/IP is a scalable, robust, clientserver networking protocol. It connects dissimilar systems and is the basis of the global Internet.

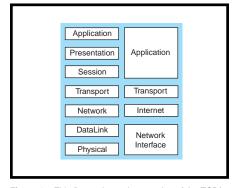

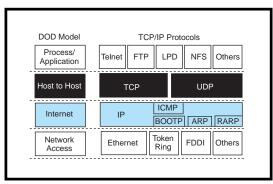

The TCP/IP family comprises four layers—network interface, Internet, transport (host-to-host), and application. These layers map to one or more layers of the International Standards Organization (ISO) seven-layer Open Systems Interconnection (OSI) model as shown in Figure 1.