# COMPUTER APPLICATIONS JOURNAL #95 JUNE 1998

# **GRAPHICS AND VIDEO**

Steve & Jeff Turbocharge a Security System

Wearable Multimedia

Designing Low-Power Systems

HTML and Hand-Held Devices

64.95 Cana

IVE

# TASK MANAGER

# A Mind is a Terrible Thing...

ow often do you get the opportunity to influence and shape tomorrow's design engineers? If you're involved in education, you're already there. I'm not talking to you. I'm talking to the engineers who sit in a lab or in front of a computer all day and whose community involvement may extend to playing softball with the town's rec program.

One of our local universities (Eastern Connecticut State University) is exploring the possibility of building upon their already-established computer science program by adding one or more new majors and/or minors. One of the steps school officials are taking is to get feedback from the local community about what programs should be offered and how they should be structured. The Computer Science Advisory Board asked Circuit Cellar to select a representative to join the group, and I was elected. Other members include representatives from insurance companies, computer vendors, primary and secondary schools, community colleges, and nearby nationally known universities.

At our first meeting last night, I was amazed at how well such a diverse group could work together to discuss a common goal: what can we offer today's college students to best prepare them for the changing world of MIS and computer engineering. Being able to tap into my own educational background coupled with over a decade of work experience, I hope I'm able to offer some useful feedback and suggestions in the coming months.

As a magazine, I like to think we have some influence over tomorrow's engineers as well. Many dyed-in-the-wool engineers begin experimenting with computers and electronics long before entering college. We have many readers who fit that category and who benefit from articles written by engineers in the field. We also have our college program in which we supply professors with free copies of the magazine for all the students in their engineering classes.

So what's my point? I want your help. We've been doing some work on our Web site, and are going to start offering perks to subscribers. Among those will be short application notes. If you have a favorite tip or technique that you'd like to share, send it along and perhaps we can use it on the Web site. Our published articles are a technical source for these college students. Supplemental application notes and technical tips can only add to their total understanding.

At the same time, I want to encourage you to become involved in your local school system. Students need to be exposed to computers as early as possible if they are going to come out ahead in today's high-tech society. Teachers have enough to do without having to figure out what's wrong with a PC's configuration or why they can't see the server on the network. Our readers possess an incredible wealth of computer knowledge, and just a fraction of that applied to the schools could benefit dozens of young minds.

I look forward to continued work on the Advisory Board. And when my oldest daughter starts kindergarten in a few months, I plan to check with her school to see if I can do anything to help.

ken.davidson@circuitcellar.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia ASSOCIATE PUBLISHER Sue (Hodge) Skolnick

CIRCULATION MANAGER Rose Mansella

BUSINESS MANAGER

ENGINEERING STAFF

**PRODUCTION STAFF**

Jeannette Walters

ART DIRECTOR

KC Zienka

Jeff Bachiochi

John Gorsky

James Soussounis

MANAGING EDITOR Janice Hughes

EDITOR-IN-CHIEF

Ken Davidson

TECHNICAL EDITOR Elizabeth Laurençot

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ingo Cyliax Fred Eady Rick Lehrbaum

NEW PRODUCTS EDITOR Harv Weiner Cover photograph Ron Mead

Cover photograph Ron Meadows – Meadows Marketing PRINTED IN THE UNITED STATES

#### ADVERTISING

ADVERTISING SALES REPRESENTATIVE Bobbi Yush Fax: (860 (860) 872-3064 E-mail: b

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster F (860) 875-2199 E

Fax: (860) 871-0411 E-mail: val.luster@circuitcellar.com

CONTACTING CIRCUIT CELLAR INK

#### SUBSCRIPTIONS: INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIPE: (200) 260-6201 or via our oritorial officer: (260) 275-210

TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 ENERAL INFORMATION: TELEPHONE: (860) 875-2199 FAX: (86

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066 HOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar INK<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK<sup>®</sup> disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK<sup>®</sup>.

Entire contents copyright © 1998 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

|   |                                                                                |                                                                                                                                                                                                                 | _  |  |  |

|---|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|   | 11                                                                             | <b>Gotcha!</b><br>Alarming the Alarm System<br><i>Steve Ciarcia &amp; Jeff Bachiochi</i>                                                                                                                        |    |  |  |

|   | 18                                                                             | WearCam: Personal Imaging System<br>Steve Mann                                                                                                                                                                  |    |  |  |

|   | 26                                                                             | <b>Design Embedded Systems for Low Power</b><br>Brian Kurkoski                                                                                                                                                  |    |  |  |

|   | 33                                                                             | <b>Design98—PIC of the Lot</b><br>Janice Hughes                                                                                                                                                                 |    |  |  |

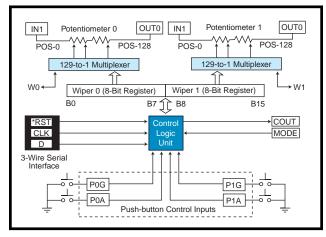

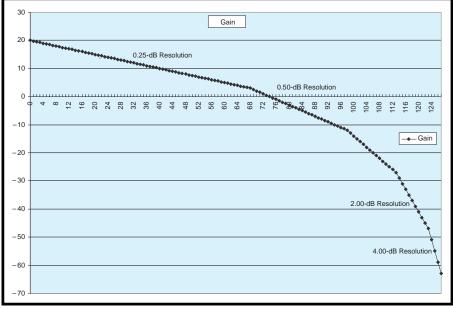

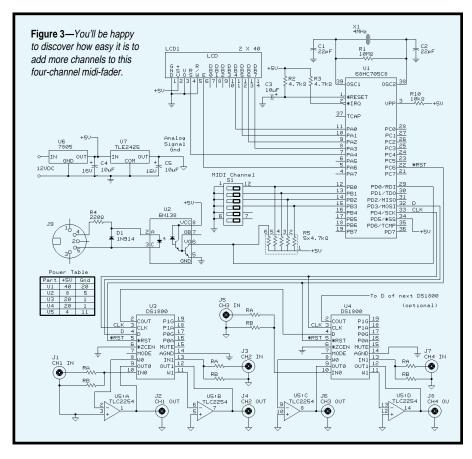

|   | 68                                                                             | <b>Digital Attenuators</b><br>Brian Millier                                                                                                                                                                     |    |  |  |

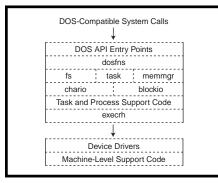

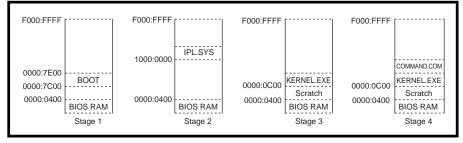

|   | 74                                                                             | <ul> <li>MicroSeries</li> <li>FreeDOS and the Embedded Developer</li> <li>Part 1: Kernel Design</li> <li>Pat Villani</li> <li>Task Manager</li> <li>Ken Davidson</li> <li>A Mind is a Terrible Thing</li> </ul> | 2  |  |  |

|   | 80                                                                             | Silicon Update Fabulous '51s Reader I/O                                                                                                                                                                         | 6  |  |  |

|   |                                                                                | Tom Cantrell New Product News edited by Harv Weiner                                                                                                                                                             | 8  |  |  |

|   |                                                                                | Advertiser's Index                                                                                                                                                                                              | 65 |  |  |

|   |                                                                                | Priority Interrupt<br>Steve Ciarcia                                                                                                                                                                             | 96 |  |  |

| T |                                                                                | Darwin Couldn't Have<br>Done Better                                                                                                                                                                             |    |  |  |

|   |                                                                                | 8 Nouveau PC<br>edited by Harv Weiner                                                                                                                                                                           |    |  |  |

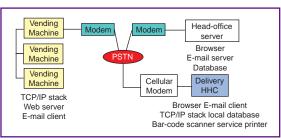

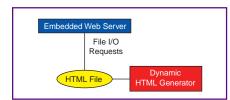

|   | 41 Building Web-Enabled Mobile Devices<br>Greg Bergsma                         |                                                                                                                                                                                                                 |    |  |  |

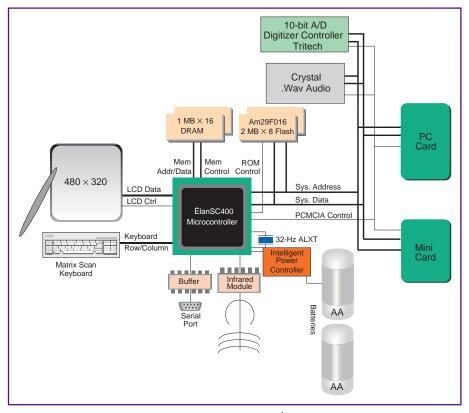

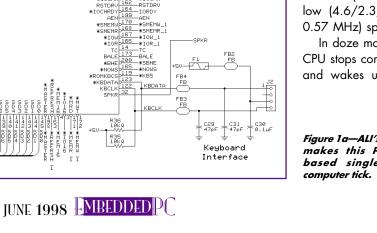

|   | 48 'x86 Processor Survey<br>Part 1: '386-Class Embedded CPUs<br>Pascal Dornier |                                                                                                                                                                                                                 |    |  |  |

|   |                                                                                | 4 RPC Real-Time PC<br>Multimedia in Real Time<br>Ingo Cyliax                                                                                                                                                    |    |  |  |

|   |                                                                                | 1       APC       Applied PCs         A New View       Part 2: Data Acquisition with         Virtual Instruments       www.circuitcellar.com         Fred Eady       ★June's Password is Gotcha                 | *  |  |  |

# **READER** I/O

#### MORE THAN JUST THE BOTTOM LINE

I enjoyed Steve's April Priority Interrupt ("What You Get with a Handshake," *INK* 93). Over the years I've been a distributor, I've seen quite a few changes as well.

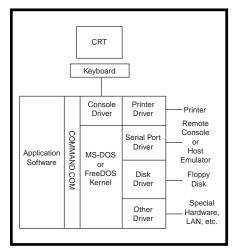

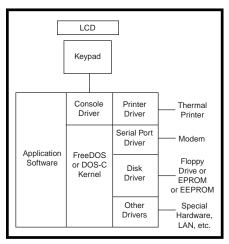

The most interesting trend is customer reliance on pre-sales engineering design support. The problems arise when the purchasing department is tasked only with component cost and cannot justify higher cost, regardless of the support offered. This is where the fear of catalog sales companies comes into play.

I look forward to several more years of change in our industry.

#### **Chris Kracht**

Hamilton Hallmark ckracht@hh.avnet.com

#### MICROPROCESSORS IN TOASTERS? YES!

As an engineer in charge of designing electronic controls for appliances, I read Steve's May editorial ("Design98—A Marketer's PICnic," *INK* 94) with glee. Yes, in answer to his question, there are plenty of toasters that use microprocessors. Rival has had one on the market for two years, Proctor-Silex has one, and so do many others. I'm working on a PIC-based toasteroven controller, and the microprocessor design ends up being cheaper than a thermostat, because we can eliminate some peripheral components.

I put a microprocessor into a steam iron to implement a new automatic shut-off mechanism (patent pending). That's the least complex appliance I know of that uses a micro.

Lawrence Lile lilel@toastmaster.com

#### AND HOW MUCH MORE HAS CHANGED?

Steve's editorial about manufactures reps and distributors ("What You Get with a Handshake," *INK* 93) reminded me of two other changes worthy of note.

First is humor—or rather, where has it gone? Commercial publications have "matured" so much, they're basically humorless. Remember what used to be:

- the Signetics WOM

- Steve's April article in *BYTE* one year when he went to "raid" the fridge. The word picture was just great.

• Unix man pages used to have a section on bugs, which was more of a comment on how to do it right the next time. But, no one admits to bugs anymore, do they?

Second, consider year-2000 problems in embedded processors. I can't remember when the common engineer has had to think so much about project liability, when fear-mongers have predicted so much doom and gloom, and when there has been so little risk assessment.

Sure, there will be problems come Jan. 1, 2000 and Feb. 29, 2000. That's a given. What I don't see is a good solid risk assessment in the popular press. Maybe crying wolf sells more paper, or vendors and professional service providers see an opportunity to make some big bucks.

I'm looking forward to the day *INK* runs an April Fools' article. Steve could always write it under a pseudonym.

Larry Pajakowski

Gurnee, IL

#### **STOP THE PRESSES**

Thanks for Jeff's interesting article, "Proprietary Serial Protocols" (*INK* 92). I'd like to comment on one small point. He says a stop bit is used to "signify the end of the single character transmission". Not so.

As far as I understand it, a stop bit doesn't signify anything. Its presence (an electrical "high") merely ensures that, whatever the state of the preceding data or parity bit, there is always a high-to-low transition for the start bit of the next data byte. This transition notifies the receiver that a new data byte transmission is about to begin.

#### Terry Koh

Singapore

What I meant was the end (or last part) of the data words protocol. You are correct. Without the stop, we could only see a start bit about 50% of the time.

Jeff Bachiochi

#### PICARO CORRECTION AND UPDATE

Figure 1 in "Picaro" (*INK* 93, p. 31) incorrectly shows R9–R16 as 10 k $\Omega$ . These resistors should all be 1 k $\Omega$ .

Also, an updated version (April 14, 1998) of the Picaro software is available on *INK*'s Web site.

# NEW PRODUCT NEWS

#### MULTIPLE VIDEO DISPLAY UNIT

The **SuperView 500** is an advanced display input system that combines up to 10 computer screens and/or video signals on a single monitor or projector. It is compatible with virtually all PCs, workstations, and any monitor or data display projector up to  $1600 \times 1200$  resolution. The SuperView 500 was developed for sophisticated applications where multiple video and computer sources must be displayed simultaneously, such as operations centers, control rooms, and teleconferencing and training facilities.

The SuperView 500 is an external stand-alone peripheral that connects between the host computer and display. It combines the multiple signals downstream of the computer so it doesn't burden the host CPU. Input signals may come from virtually any source like NTSC, PAL, S-Video, FLIR, or any computer signal up to  $1280 \times 1024$  pixels. Video and computer inputs are shown as windows on the main screen. All windows can be positioned, scaled from icon size to full screen, overlaid with computer graphics, or overlapped with other windows. Also, each input can be panned and zoomed to emphasize areas of interest.

SuperView 500 supports software control to manipulate the video windows. X.TV software provides full integration under X Windows, and W.TV software for Windows 95/NT.

Pricing starts at **\$10,990** for a camera with two NTSC/ PAL inputs. Additional NTSC/PAL inputs and RGB/FLIR inputs are available.

RGB Spectrum 950 Marina Village Pkwy. Alameda, CA 94501 (510) 814-7000 Fax: (510) 814-7026 www.rgb.com

#501

#### ELECTRONIC COMPASS MODULE

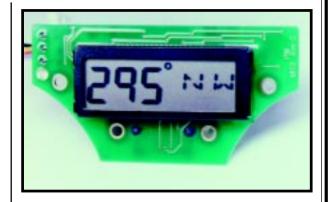

The **Navifinder-200** electronic compass module is ideal for use in RVs, snowmobiles, motorcycles, boats, and van/truck conversions. It can easily be mounted in a dash or enclosed in a housing. This module uses advanced calibration algorithms that discriminate between the earth's magnetic field and those generated externally, such as from the metal and electronics in a vehicle. By electronically compensating for these external factors, the Navifinder-200 can provide highly accurate compass readings in all vehicle environments.

The Navifinder-200 is easily wired to any 12-V battery supply and ignition system or externally mounted on/off switch and battery. It outputs the compass heading on a LCD in 5° numeric digits and eight cardinal points (N, NE, E, SE, etc.), with an accuracy of 2°. To provide different viewing angles, the Navifinder-200 can be mounted with up to  $\pm 30^{\circ}$  of tilt without losing accuracy.

The Navifinder-200 uses Precision Navigation's patented Magneto-Inductive magnetic sensor technology to provide high sensitivity, a large dynamic range, low power consumption, and a low price.

This compass module sells for **\$75** in single units and **\$32** in quantities of 1000.

Precision Navigation, Inc. 1235 Pear Ave., Ste. 111 Mountain View, CA 94043 (650) 962-8777 Fax: (650) 962-8776 www.precisionnav.com

# NEW PRODUCT NEWS

#### PCI CONTROLLER DEVELOPMENT KIT

A new **Motorola MPC860 development kit** simplifies design efforts to use the Anchor Chips AN3041Q CO-MEM PCI controller to interface between the PCI bus and the Motorola MPC860 family of processors. The kit features a development board with an AN3041Q device interfaced without glue logic to the MPC860. The addin card contains no onboard memory and plugs directly into the PCI bus in a desktop PC. The cache memory in the AN3041Q caches the local processor's memory needs across the PCI bus to host memory. The designer defines how much host memory (up to 16 MB) is allocated to the MPC860 board through software.

The CO-MEM Mapper software, which runs on any Windows-based PC, defines the MPC860's memory map and automatically configures and displays the AN3041Q's internal registers. Once the AN3041Q is configured, the MPC860 processor can be released from reset to run the application. Mapper software contains debug tools to aid in the integration of the MPC860 processor and its application with the host system.

The AN3041Q uses a highly intelligent cachememory architecture instead of the FIFO/DMA architecture to provide a high-speed communication interface from a local microprocessor or DSP to the PCI bus. It interfaces directly to most 8-, 16-, and 32-bit processors. The bus interface engine in the AN3041Q enables the local processor to have direct access to the PCI bus. The dual-mode caching controller enables the controller's internal memory to easily interface between the local processor, PCI bus, and host memory.

A design guide shows a step-by-step procedure for developing a system with the AN3041Q. Other reference materials are provided in the kit to make a complete development package.

The Motorola MPC860 development kit sells for \$495.

Anchor Chips, Inc. 12396 World Trade Dr. San Diego, CA 92128 (619) 613-7900 Fax: (619) 676-6896 www.anchorchips.com

#### NONCONTACT ULTRASONIC SENSOR

The Senix **ULTRA-30-VA** noncontact ultrasonic sensor provides a 0–10-VDC output proportional to the measured distance to target materials. The analog output spans easily between any two distances in its 3–80" operating range. Packaged in a 30-mm threaded alumi-

num housing, the sensor features push-button operation to simplify setup and eliminate potentiometers, target status indication to convey target range and stability status, and stable output under lost target conditions. It offers dual-range operation for optimum performance at different target ranges and a user-selectable output response filter for stability under noisy or poor target conditions.

This sensor has a resolution of 2 mm (0.078") and accepts 15–30-VDC input. It connects easily with PLCs, motor drives, or other controls.

The ULTRA-30-VA is designed for motion-control applications including the measurement of roll diameter

and free loop positions for the purpose of tension, speed, and/or diameter control. It's ideally suited for medium-volume OEM machine controls in the pulp and paper, printing, and converting industries.

Senix Corp. 52 Maple St. Bristol, VT 05443 (802) 453-5522 Fax: (802) 453-2549 www.senix.com

#504

# **NEW PRODUCT NEWS**

#### **REMOTE I/O MICRO CONTROLLER MODULE**

The **Model HCON-1** remote I/O microcontroller module accepts commands over the RS-485 serial bus to control output drivers and obtain inputs from quadrature encoders, temperature modules, and switch inputs. High-current output drivers directly control up to 20 relays or LEDs.

Applications include remote equipment control, home automation, temperature control, and remote relay control.

Up to 256 Dallas DS1820 or DS1821 digital temperature inputs can be scanned over the single-wire interface. Key switching can be from a  $5 \times 5$  switch matrix or 10 discrete inputs. ASCII or binary commands can be sent over the RS-485 interface at a data rate up to 19.2 kbps. The compact board measures  $1.8'' \times 2.7''$ .

The supplied software includes sample interface code under Visual Basic, Visual C++, and ActiveX control.

The Model HCON-1 sells for \$119.

J-Works, Inc. 12328 Gladstone St., Ste. 4 Sylmar, CA 91342 (818) 361-0787 • Fax: (818) 270-2413 www.j-works.com

## CIARCIA'S CIRCUIT CELLAR

Steve Ciarcia

#### Jeff Bachiochi

**FROM THE**

BENCH

# Gotcha! Alarming the Alarm System

R

Alarm companies fall a little short if what you want is entry and exit printouts. Sure, they'll do them. But only at \$20 a pop—or the cost of a new system. So, what do you do? If you're Steve and Jeff, you add a little electronic sleuthing to the system.

was just about ready to pack it in for the night when Jeannette called down the cellar stairs.

"Steve, the alarm service is on the phone. The alarm at the office just went off! They called the police. Shall I say you're on the way to meet them?"

As I grabbed my coat and keys, I cast a quick glance back at Jeannette. Her expression said far more than any verbal exchange.

The gist of it was that if anyone was going to play hero tonight, it wasn't going to be her. She's happy to run a business with me, but gunslinger is definitely not in her job description.

There was a time when sharing the "business experience" might have prevailed, but after a real break-in at our office when the police actually dragged a burglar out in handcuffs, she decided this was one event she'd rather stay away from. Besides, anyone stupid enough to break into a building attached to a courthouse and surrounded by a half-dozen TV cameras probably isn't bright enough to listen to reason anyway. As I ran for the car, I heard her yell, "Be careful...! Call me...!"

Like most businesses, we have a commercial alarm system. The reason isn't as much to deter crime as it is to qualify for discount on insurance rates. That's the good news.

The bad news is that, because I live closest to the office, I'm first on the call list when the alarm goes off. I get to greet the police and walk around a building with a lot of dark hiding places.

There really aren't a lot of options. If you want the police to treat the call seriously, you better meet them there. And, you also have to watch the false alarms.

Everyone had a sense of humor when someone set the alarm while Ken was still working on the third floor. Since then, the last one out is supposed to page the building or check the parking lot. There has to be a bit of seriousness. After all, the police did nab somebody that one time.

As I pulled into the parking lot, the lights from state and local police cruisers greeted me. All I could think was, please, let them find Jeffery Dahmer or someone, not another false alarm. After the appropriate introductions, we trooped into the building—they with their guns drawn and flashlights blazing. I don't know why they didn't just turn on the lights, but they preferred to search each room in the dark.

I still don't understand the tactic. Maybe they presumed someone this dumb would invariably use tracer ammo or something else that's easy to see in the dark. Needless to say, I waited until the lights were on before roaming anywhere unescorted.

The results of the search were less than spectacular and somewhat embarrassing. Apparently, workmen had left an outside door to the furnace room unlocked and nobody checked it.

Besides the lock, the door needs a  $3\frac{1}{2}$ " thick wooden bar across the inside to keep it from opening. Of course, when someone leaves the door unlocked and only puts in a standard  $2 \times 4$  ( $1\frac{3}{4}$ " thick) instead of the usual  $4 \times 4$ , the door can open almost 2". Guess what happens when someone pulls on the door from outside? An unlocked door is an embarrassing predicament.

Needless to say, I apologized profusely. It was a false alarm. If we'd

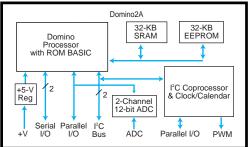

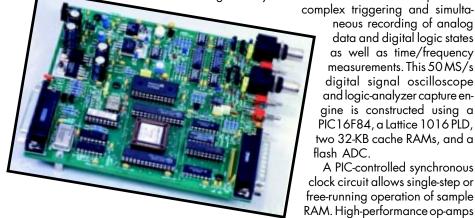

Figure 1—Domino2 is a small encapsulated controller with a built-in floating-point BASIC interpreter and 32 KB each of EEPROM and SRAM.

nabbed Charles Manson, wasting their time wouldn't be an issue. I probably could have even gotten away making police and donut-shop jokes. Under the circumstances, however, my only recourse was to thank them, tuck my tail, and return to the car.

I dialed the cell phone. When Jeannette answered, I said in a disgusted tone, "Someone left the damn door open! The only thing worse would be if they didn't set the alarm at all!"

"Well, Steve, I wasn't going to tell you, but I've had reports from the people who come in early that occasionally the alarm hasn't been on."

Next morning, I called everyone with alarm codes together and asked the pertinent who and when questions. I got back mostly blank stares, to

be interpreted as, "Not me, man." Given all the people with independent access to the building, that was hardly reassuring.

The obvious answer was the alarm company. We pay them \$30 a month to monitor the system and call the appropriate people if the alarm goes off. When it was first installed, we got a monthly opening/closing report that listed the date, time, and access code (these days I suppose we'd call it a PIN) for every alarm set or reset. This was the obvious answer.

Calling the alarm-monitoring service is an experience. They're contracted by your alarm installer and not typically selected by the alarm owner. And since they answer the phone "Monitoring station" and use the installer's name once you give them your account number, you might think they're just down the block. Only when you interrogate the autodialer or otherwise see where the call goes do you realize that your personal monitoring can be 2000 miles away.

Our monitoring company was at the other end of the state, but most large alarm companies deal with centralized service monitors that cover many states at the same time. Regardless of their location, aside from changes to the call list, they're like talking to a brick! Their pat response is that you should call your installer.

They usually charge the installer a flat rate based on a specific service level for all his customers. If he only contracts for alarm calling and none of the monthly printed reports, it's tantamount to bringing the mountain to Mohammed to get one from the monitoring company. Yes, I could get a report for a specific day—at \$20 each!

Calling the installer reminded me again why we designed our own homecontrol system. These people have no vision at all.

"What would it take to get daily entry/exit reports?" I asked. "I suggest you install a new alarm system," he answered matter-of-factly.

"Would a new system be better than our present ten-year-old hardwired system?"

"Well, sir," he continued. (Subconsciously, I noted that people generally called me "sir" when they were trying to sell me something. Sometime I'll have to test the financial limits of this theory. Do they start at \$100, \$500, \$1000...?) "It would have the latest technology and use wireless sensors."

"And after I replace the \$2 battery in every sensor each year, would it do more than provide a contact closure to an alarm horn and autodial a digital code to the monitoring station like the present one?" I already knew the answer.

"It would use the latest technology to close the contact and autodial the modem, sir...and we could get you one with a printer output." Finally, he mentioned something we wanted!

I continued, "Do you know if it's a standard serial printer port? Do you have a schematic?"

"Well, I'm not sure what it is, sir, but I can supply you with the printer (extra cost). There are never any sche-

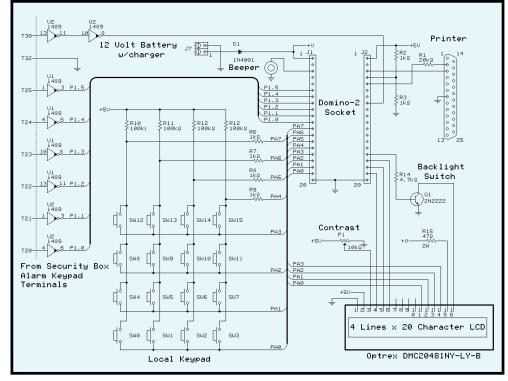

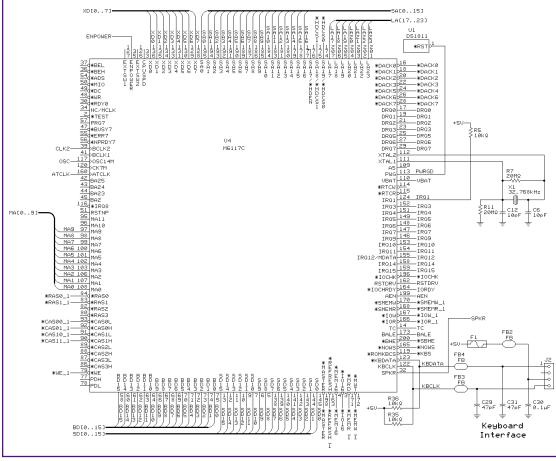

Figure 2—This schematic shows the ASDL system and how it connects to the alarm signals.

matics of any equipment, sir. I guess they're concerned about liability."

Liability, schmiliability. The only reason there are no schematics is that the alarm manufacturers don't want competition.

In the end, it's just a cost decision. "How much?"

"Well, sir, if we do just the same as your present system and add the printer, probably about \$3500–4000."

I knew this "sir" thing was going to cost me. "Thanks, I'll have to get back to you."

My next stop was Jeff's desk.

"Jeff, this alarm guy is nuts. You can't believe how much it costs for an alarm-code printout. Worse yet, it only records successful entries. It can't tell who punches in a bunch of numbers, never actually sets the alarm, and then just walks out without checking. That's the guy I want."

I knew telling Jeff about such a ridiculous obstruction would be a technical challenge he couldn't refuse. They may not know how to produce a daily event record, but somehow *we* would. We gathered up the 'scope and headed for the furnace room and the alarm-system controller box.

There was nothing surprising about the system. It was your standard tenyear-old Silent Knight alarm system. Documentation was strictly at the installer level. Motion detectors and sensors connect to these terminals, the alarm horn connects here, the phone line goes in here.

The PCB hardware included two microcontrollers that shared the control tasks. Because they had house numbers, Jeff and I concluded they were probably ROM-programmed 8051-family devices. And because it was ROM coded, we didn't have a prayer of changing any internal operation. The best we could hope to do was monitor the external signals.

It would have been great if the alarm designers had taken a traditional engineering approach. Even a *predictable* approach would have been welcomed. In the world of high-volume consumer-quality electronics however, nothing works the way you expect it to, and "cute" is a term frequently used to describe the design technique. The methodology is quite straightforward. Take a circuit that works the way you'd normally design it, throw away half the parts (or parts cost), and then make it do all the same control tasks. These are the guys who make a fine art of cycle-stealing, multiplexed operation, and hairy-edge qualification. Want them to design your next medical product?

This unit was no exception. The user interface consisted of a  $3 \times 4$  keypad with a green LED (ready), a red LED (armed), and a single 7-segment LED display (zone). The keypad labels were 0–9, Door, and On/Off. Pressing any button makes an internal beeper sound. Photo 1 shows a close up of the alarm's keypad.

Similar to the operation of most alarm systems, the user looks for a green light indicating the system has no open doors and punches in a fourdigit code followed by the on/off button. The alarm goes on, the red LED lights, and you have about 45 s to vacate the building. The process is reversed to shut off the alarm.

Jeff and I concluded the way for us to monitor entry and exit times and codes was to attach a circuit in parallel with this user interface and tap into its communication with the system box. Punch in 6637 and On, and we'd log it to a printer. The only sticky part was guessing where all these signals were so we could tell which key was pressed.

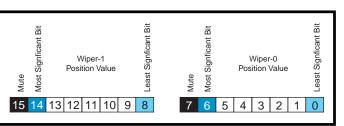

The keypad in the entryway connects to the system via an 11-wire parallel cable. The  $3 \times 4$  keypad has four rows labeled 1–3, 4–6, 7–9, and Door, 0, and On/Off.

Electrically, we determined that the keys are scanned in two separate groups of six. Two opposite and alternating signals drive the two groups. Pressing none of the keys results in a logic 0 on the three column inputs back at the system board.

Pressing a key diode ORs one of the phases with one or more of the column inputs, like this: 1 = 001, 2 = 010, 3 = 011. A 7 also creates the 001 combination but in step with the opposite phase. The system knows which key is pressed based on the column inputs and the phase of the input signal.

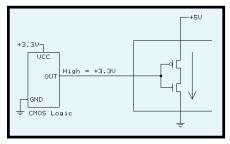

Other signals to the entry panel enable the red or green LEDs and drive a piezo beeper when any key is pressed. All signals are at the 12-V level.

#### PACKAGED SOLUTION

Jeff and I now knew there were some logical signals we could monitor. The next task was to decide what kind of data-acquisition system we had to configure. But unlike our lightning device ("Ground Zero," *INK* 90), this wasn't just an illustrative magazine project. I wanted to use this thing.

We could have used anything from a PIC to a full-blown PC as the hardware. Our logging system needed a processor board to acquire and analyze the data, a real-time clock/calendar to time stamp the entries, an LCD to view records, a keypad to direct the logger's activity, and a printer interface for making hardcopies on command.

Beyond the strict hardware necessity, system selection is always a tradeoff of competing ideals:

- time (getting this much software done quickly enough to meet a magazine deadline typically rules out assembly language)

- I/O capability (obviously, we needed a serial port and a lot of parallel I/O)

- speed (just how fast does this thing need to be anyway?)

- cost (are we making a few or is it a volume-production device?)

- political bias (some designers will jam in a PC even if it can be done on a PIC)

This analysis pretty much fits half the board ads in *INK*. Fortunately, I get to apply a little political bias of my own.

While there's a little fancy footwork in the interrupt routines, most of the software is a lot of text shuffling among the peripherals (it's easy for the guy who doesn't write the software to say stuff like this). When we looked at the requirements, it seemed like a perfect application for a Domino—or more precisely, a Domino2.

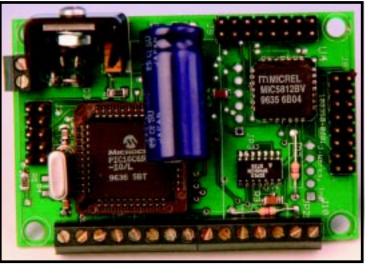

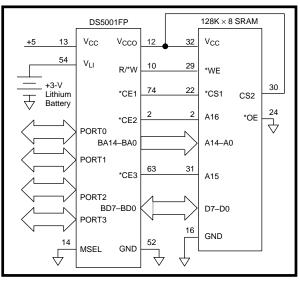

As Figure 1 shows, Domino2 is a small encapsulated controller

with a built-in floating-point BASIC interpreter and 32 KB each of EEPROM and SRAM. Best of all, it contains a serial port, lots of parallel I/O, and a real-time clock.

Even if you don't have a ten-yearold alarm, I'm sure you'll find that our method of solving the problem provides some interesting examples of using BASIC-52 in control applications.

#### ALARM-SYSTEM DATA LOGGER

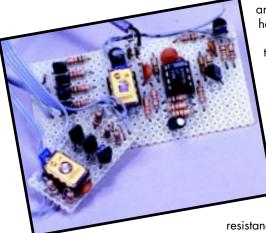

Figure 2 is the schematic of the alarm-system data logger (ASDL). The circuitry was added to Domino's proto1 board, as shown in Photo 2. The first task was mating the 12-V level alarm signals with Domino's TTL input levels.

There are lots of ways to do this, but one cute way is to use MC1489 RS-232 input level shifters. These inexpensive inverters can withstand  $\pm$  30-V inputs while interfacing directly with TTL on the output side. Six keypad lines connect to the processor.

The next detail is determining when a key is pressed. We had two alternatives. We could create a fallingedge key-press interrupt by NORing the three column inputs together. Or, we could take advantage of the fact that pressing any key caused the beeper to sound.

Ultimately, Jeff chose to use the signal applied to the beeper as a keypress interrupt. The three column

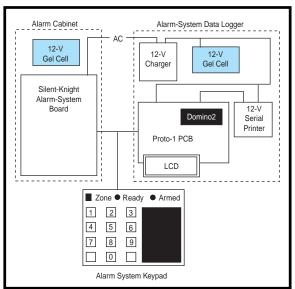

**Figure 3**—The ASDL attaches in parallel with the existing alarm keypad. The Domino2-based monitor program registers and records keypad activity and outputs the data to an LCD and printer on command.

lines, two phase outputs, and on/off button are read anytime there's an interrupt. Together, they determine the physical key combination.

Normal entry and exit profiles run a total of 10 key presses a day. This plus a 7-byte time and date stamp amounts to fewer than 20 bytes of data-logging space required per day.

Our plan isn't to check this thing daily but to have a record of events available when we need it. If we have a good chunk of data storage space available, how often we dump the records will never really be an issue. Six months of data fits easily in less than 5 KB of memory. We have about 24 KB available.

Program development started with writing the time and date to the LCD. Instead of using a couple I<sup>2</sup>C peripheral chips to connect the  $4 \times 20$  LCD and  $4 \times 6$  keypad as typically described for Domino, Jeff chose to minimize external hardware and scan the command keypad in software.

Using this number of I/O bits for the keypad necessitated using the LCD in 4-bit mode rather than the typical 8-bit parallel interface. The 4-bit mode requires two nibble writes to the LCD for each printed character, which entails eight physical operations for each character—set up the control register, raise the strobe line, set up the data register, drop the strobe line.

> The process repeats for the second data nibble.

The program executes a short initialization routine and then prints day of the week (DOW), month/day/year, and hour/minute/second on the LCD. Using the row and column positioning capability of the LCD (a control register routine), only new data needs to be updated. This makes a great idle screen that also indicates the system is running.

If the displayed time and date is incorrect, as it would be on initial powerup, the user enters the present DOW, month, day, year, hour, minute, and second. Maintaining the time during a power outage is a simple matter of adding a 4.5-V back-up battery to the real-time clock.

Since the alarm system is normally battery-backed and may be needed during a power outage, we decided to battery-back the whole Domino2 circuit. Besides keeping the RTC alive, it maintains any collected data that hasn't been printed yet. Figure 3 gives an overall view of how the complete system was integrated.

Photo 1—The alarm system PIN is entered via a keypad. The ASDL system monitors and records the time and date of all key presses.

#### FANCY FOOTWORK

As I mentioned, it's easy to say it's just a matter of software when you don't have to write it yourself. One of the more challenging aspects of the software was catching the key presses while doing all the other system functions.

This task was accomplished via the BASIC-52 ONEX1 command. This interrupt command temporarily redirects the normal program flow to a special subroutine.

ONEX1 is triggered by a high-to-low transition on Domino's INT1 input pin. Obviously, it should be reserved for a high-priority function. Listing 1 illustrates the high points.

The piezo beeper output connects to INT1. When ONEX1 is triggered, the routine samples the I/O port where all the row and column data is connected to the Domino. This beeper interrupt can occur during either phase of the row drivers.

To ensure the sample is valid, the program checks whether there is a high level on at least one column input line. If none of the first three bits are high, we assume it's the wrong phase and take another sample. Once there is a valid sample, the row driver levels (indicating the two phases) can be compared with the column inputs to determine which of the 12 keys was pressed.

Before leaving the interrupt routine, there are two more tasks. First, save the key-press code into the data-logging buffer and increment the buffer pointer. If the on/off key was pressed, a time/date stamp is added to the log.

Finally, we need to make sure the physical key-press action has ended (to prevent interrupt on the same key press). This is accomplished by repeatedly sampling the port and looking for invalid data (columns all low) on both phases of the row driver outputs. When RETI is executed, the program resumes where it left off.

#### **GETTING THE GOODS**

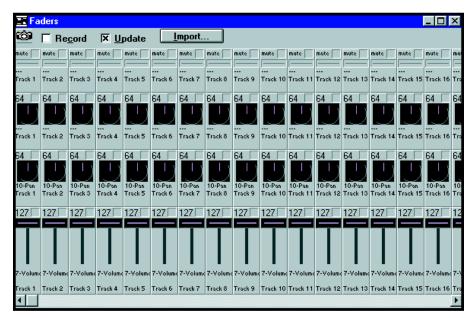

Displaying and dumping the stored data log is a secondary function chosen from the command menu. The ASDL LCD can show a command list, the time and date, or the data. The data is printed to the LCD in blocks.

When the log is dumped, all the blocks up to and including the present time and date are dumped. We didn't see the necessity for individual date interrogation.

You want the data log? *develo* Here's everything, a block at a time.

While the data is being sent to the LCD, it is also sent out the console serial port. Although this could be connected to a PC and logged to a file, Jeff mounted a plain-paper 12-VDC-powered serial printer (measures only

Photo 2—The prototype ASDL sytem is physically assembled using a Domino development board with an LCD and keypad attached.

$5'' \times 5'' \times 3''$ ) next to the Domino, so a hardcopy of the data could be printed and retained if necessary.

A short pause between each block lets the printer keep up with the data and provides time to study each block on the LCD before the next display. The final menu selections enable the user to clear all data from the data buffer and return from the menu screen to the idle screen (displaying time/date).

Since the capturing and logging of alarm codes is a security risk, it would be foolish not to try to prevent unauthorized use. Accessing the menu screen shouldn't be open to just anyone.

Any ASDL entry prompts the user for a PIN. An incorrect entry simply returns to the idle screen.

We also specifically chose to store the data log in SRAM rather than EEPROM. If the Domino is removed from

the system, the data log disappears.

#### GOTCHA

While solving the problem this way gave me the satisfaction of not having to buy more useless equipment from an alarm company, it turns out there was no better alternative.

The monitoring station and a commercial alarm printer could only give me a list of successful alarm operation. But, my major irritation was with people who didn't look for a green LED (indicating that the building was clear) before blindly punching in a code (that the alarm doesn't accept) and blowing out the door.

The ASDL stores every key pressed. It only adds the time/date stamp when the on/off key is pressed. If the alarm isn't set, a quick review of the record should show what code was being entered, even if unsuccessfully.

All of our work may have been in vain. We haven't had any false alarms, and interestingly, there haven't been any mornings with an unset alarm.

Either everyone has become educated by involvement in publishing this article, or seeing Jeff and me constantly playing with the alarm system has made them aware that something is going on.

Regardless, they seem to recognize the seriousness of it all. Jeff and I just have to be careful that we don't let on that we really have fun. Listing 1—The highest priority was given to the monitoring of the alarm keypad's key presses. The BASIC ONEX1 command branches to line 20000 to decode a key press and log it.

ONEX1 20000 : 120 REM CAPTURE ALARM KEY PRESSED 20000 REM INTERRUPT ROUTINE - EXTERNAL BUTTON PUSHED 20010 LED=PORT1.XOR.255 : REM INVERT DATA 20020 IF (LED.AND.07H)=0 THEN GOTO 20010 : REM CHECK FOR DATA 20025 LED=LED.AND.3FH 20026 BUT=LED.AND.37H : REM MASK OFF ALL BUT BUTTON INFO 20030 IF BUT=15H THEN GOTO 21000 : REM BUTTON 0 IF BUT=21H THEN GOTO 21100 : REM 20035 BUTTON 1 20040 IF BUT=22H THEN GOTO 21200 : REM BUTTON 2 : REM 20045 BUT=23H THEN GOTO 21300 ΤF BUTTON 3 20050 BUT=24H THEN GOTO 21400 : REM ΤF BUTTON 4 GOTO 21500 IF BUT=25H THEN 20055 : REM BUTTON 5 IF BUT=26H THEN GOTO 21600 20060 : RFM BUTTON 6 IF BUT=11H THEN GOTO 21700 20065 : REM BUTTON 7 20070 IF BUT=12H THEN GOTO 21800 : REM BUTTON 8 BUT=13H THEN : REM 20075 ΤF GOTO 21900 BUTTON 9 BUTTON DOOR 20080 ΤF BUT=14H THEN GOTO 22000 : REM 20085 IF BUT=16H THEN GOTO 22100 : REM BUTTON ARM/DISARM 20090 RFTI 20100 Z=Z+1 : XBY(Z)=OFFH : REM TAG END OF BLOCK 20110 LED=PORT1.XOR.255 IF (LED.AND.17H)<>10H THEN 20110 : REM WAIT FOR NO DATA 20120 20130 LED=PORT1.XOR.255 20140 IF (LED.AND.27H) <> 20H THEN 20130 : REM WAIT FOR NO DATA 20190 RETI 21000 XBY(Z)=30H 21010 GOTO 20100 22000 XBY(Z)=ASC(D) GOTO 20100 22010 22100 REM ARMED? 22101 IF (LED.AND.08H)=0 THEN GOTO 22200 22110 XBY(Z)=ASC(N) : REM NOT ARMED 22111 GOSUB 23000 22120 GOTO 20100 22200 XBY(Z)=ASC(A) : REM ARMED GOSUB 23000 22201 22220 GOTO 20100 23000 REM STICK IN TIME/DATE STAMP 23005 Z=Z+1 23006 XBY(Z)=0AAH 23010 Z=Z+1 23011 XBY(Z)=MTH 23060 Z=Z+1 23061 XBY(Z)=SEC 23080 RETURN

Steve Ciarcia is an electronics engineer and computer consultant with experience in process control, digital design, and product development. You may reach him at steve.ciarcia@ circuitcellar.com.

Jeff Bachiochi (pronounced"BAH-key-AH-key") is an electrical engineer on Circuit Cellar INK's engineering staff. His background includes product design and manufacturing. He may be reached at jeff.bachiochi@circuit cellar.com.

#### SOURCE

#### Domino2

Micromint, Inc. 4 Park St. Vernon, CT 06066 (860) 871-6170 Fax: (860) 872-2204 www.micromint.com

#### IRS

401 Very Useful 402 Moderately Useful 403 Not Useful

# FEATURE ARTICLE

#### **Steve Mann**

# WearCam: Personal Imaging System

WearCam is a personal imaging system that lets you capture events as if the camera sits behind your eyes. It can even manipulate its shots—zooming in and out. The real world gets equal footing with the virtual. achine vision and artificial intelligence (AI) are problems that have challenged research-

ers for decades. Many easy tasks for humans can only be done by computers in carefully controlled settings, if at all.

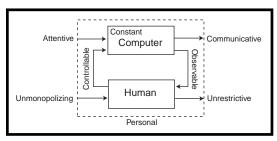

Rather than emulating human capabilities in a computer, an alternative framework, humanistic intelligence (HI), creates a synergy between human and machine in which the human is part of the feedback loop of a computational process, as illustrated in Figure 1.

Instead of implementing an imageprocessing neural network inside a computer, we need to realize we have a good neural network sitting on our shoulders—and it is already outfitted with two very good imaging devices.

#### **EMBODYING HI**

WearComp, which originated in the 1970s as a tool for exploring vision, offers a new form of human-computer interaction in which the computer exists within the user's personal space, is controlled by the wearer, and has both operational and interactional constancy (i.e., is always on, ready, and accessible).

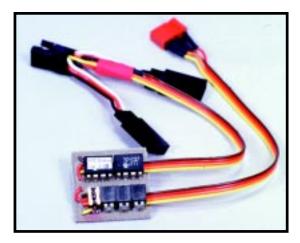

WearComp typically consists of a body-worn computer system, a visual display over one or both eyes with text and graphics display capability, and an input device with five or more pushbutton switches that may be operated by one hand. Other input devices may include microphones and one or more video cameras positioned to view the same subject matter the wearer sees.

Because the apparatus is worn on the body, input devices often include contacts that touch the body to determine skin conductivity or heart rate, as well as various transducers such as a respiration monitor.

To get a better feel for HI, consider this scenario: You're walking home wearing your WearCam. It's measuring your heart rate, respiration, footstep rate, and so on. (Dividing heart rate by footstep rate serves as a visual saliency index for controlling frame rate of video capture and transmission.)

Suddenly, an assailant wielding a sawed-off shotgun demands cash. You see him appear on the viewfinder concealed inside your glasses, and the computer, through intelligent signal processing, recognizes the increase in

**Photo 1—***Multiple push-button switches (e.g., microswitches in this data-entry device from the 1970s and early 1980s) are pressed in different combinations to issue different commands.*

heart rate and decrease in footsteps and sends high-resolution image data to remote locations at maximal frame rate. Friends and relatives are automatically summoned to see the situation.

Essentially, the computer presents the image on its viewfinder screen and measures the human's response to that image. No high-level machine vision or AI is used. Instead, the human brain and human visual system are inserted into the feedback loop of a process that determines whether or not the situation is dangerous.

#### **BUILDING WEARCOMP**

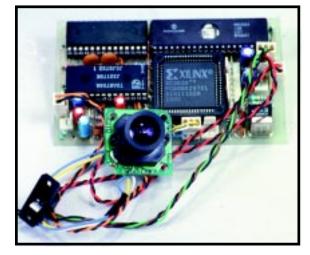

Most modern cameras contain some computational capability. The computational capability in WearCam—Wear-Comp—is more than just a micro for calculating exposure. WearComp is a complete Internet-connected multimedia computer system running a Unix-like operating system.

WearCam is for a technical breed that wants the challenge of becoming a camera and experiencing life through the screen of an image-processing computer. WearCam6/WearComp6 can be easily built from off-the-shelf components.

Obviously, since this system is in contact with your body, you need to take the utmost care to protect yourself from physical risk or danger by following careful engineering practices. As well, extensive wearing of the device could cause eye damage as well as damage from RF.

#### BRIEF HISTORY

Table 1 gives you a look at Wear-Comp's evolution, including the microprocessor used and its expanding text and graphics capabilities.

WearComp0 and WearComp1 were specifically designed for controlling experimental body-worn photographic lighting equipment. They certainly weren't general-purpose computers.

But WearComp2 was. It could execute a general instruction set, and it even had a BASIC interpreter, making it easy to write programs to edit ASCII text files, exchange messages (e.g., an E-mail of sorts), do floating-point calculations, and other things that go beyond the kind of functionality you'd expect in a camera system. WearComp3 was much less capable than WearComp2. However, it was smaller and could be better integrated into clothing (rather than being worn like a backpack).

It also marked the beginning of using the chest area as a display space others could see. This design choice arose out of the fact that WearComp3 put more emphasis on computer-supported collaborative photography than on the individual spirit WearComp2 had been based on.

WearComp4 returned to a fully functional general-purpose computer, as did WearComp5, which was a much more powerful image-processing workstation running the Linux OS with Xwindows (XFree86) and using a PCMCIA video-capture device.

In this article, I describe WearComp6 because it doesn't require any special nonstandard devices or custom ASICs. But, there's also a WearComp7, a covert version of wearable wireless webcam that was first completed in 1995, that looks like ordinary glasses and clothing.

And, a recently completed Wear-Comp8, a covert version of wearable wireless webcam, embodies a new kind of mediated-reality experience with enough visual acuity so you can engage in fast-action activities (e.g., playing sports) while looking through the viewfinder and recording the experience.

#### **BUILDING WEARCOMP6**

Most of the research issues including the mathematical framework for personal imaging and mediated reality (MR) are described at <wearcam.org/ research.html>. Here I simply describe how to build WearComp6. Go to the Web site for details on programming and integrating it into a WearCam6 system.

WearComp6 is built from standard PC/104 modules. The modularity of WearComp6 makes it easy to change the system's functionality quickly.

In a sense, you end up with a wearable image-processing lab, and you might want to add other boards such as an ADC board for an oscilloscope. I implemented an oscilloscope in Wear-Comp2 and found it useful for diagnos-

Figure 1—A camera that embodies humanistic intelligence (HI) uses the human operator for its intelligence rather than trying to emulate human intelligence directly. Within the HI framework, camera intelligence arises as a result of the existence of the human in the feedback loop of some computational process. In the case of WearCam, the camera ceases to be intelligent as soon as it is no longer being worn.

tic work. I could keep my eyes on the work while making measurements.

Isolation is important. You don't want high voltage going through your body when you display the signal on a highvoltage wire and the ground clip pops off.

#### BATTERIES

Early versions of WearComp used lead-acid batteries, whereas later (mid 1980s) versions used NiCd batteries.

For constant operation, I generally use at least two 12-V batteries. These batteries typically have lugs that connect to crimp-on connectors.

However, in wearable applications, the lugs are easily broken off or shorted by materials you might carry in a pocket with the batteries. To avoid fire and explosion hazards, I solder wires right to the lugs and insulate them well.

Be careful to place a fuse right next to one of the lugs of the battery, not in the cord going to the battery. Otherwise, if something wears through the insulation on the cord upstream of the fuse, you've got a problem.

The best fuses are the automotive type with solder lugs. I typically place a fuse right near the positive lug, as close as possible.

One lug of the fuse can be soldered to the positive lug of the battery, and a red wire soldered to the other end of the fuse. A black wire can go directly to the negative side of the battery.

I wrap both lugs in several layers of fiberglass tape and epoxy. You need to wrap all the way around both the positive lug and the fuse near it because general wear and tear on a wearable apparatus is much higher than for other embedded systems.

| Name                                                                                    | Completed                                                                                           | Processor                                                                                                           | Text and Graphics  | Where on Body                                                                                                                                          |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| WearComp0<br>WearComp1<br>WearComp3<br>WearComp4<br>WearComp5<br>WearComp6<br>WearComp7 | 1970s<br>1970s<br>1981<br>early 1980s<br>late 1980s<br>early 1990s<br>early 1990s<br>mid/late 1990s | electromechanical<br>SSI, MSI<br>6502<br>8085<br>80286<br>80486/33<br>PC/104,80x86<br>TMS320C3 <i>x</i> /4 <i>x</i> | $\begin{array}{c}$ | back<br>back + waist + shoulder<br>back + waist + shoulder<br>waist + chest<br>ordinary backpack<br>large waistbag<br>medium waistbag<br>underwearable |

| WearComp8                                                                               | late 1990s                                                                                          | Pentium                                                                                                             | RS170              | underwearable                                                                                                                                          |

Table 1—As you can see, WearComp has gone through quite an evolution on its way to becoming what it is today.

Alternatively, you can buy a battery vest for about \$600. You then have a ready-to-wear power supply with plenty of pockets for computational apparatus or additional components. These vests are designed for high-current output (e.g., video lights and large cameras), so it's a good idea to include an additional fuse of lower current rating, consistent with the use expected of WearCam.

#### LI-ION BATTERIES

In the early to mid 1990s, I began using lithium-ion (Li-Ion) batteries. Sony provided me with camcorder batteries before they were commercially available.

Now you can find Li-Ion camcorder batteries almost anywhere. You need a minimum of four batteries (two sets of two in series) for a constant-running 12-V supply.

My version of WearCam, for example, is a complete photographic studio and video editing facility, so it's not surprising that it needs more than just one camcorder battery. These batteries have built in minifemale banana connectors, so they're easy to connect to the system.

#### **BRIDGING THE POWER GAP**

Ordinarily, when you remove a battery from WearComp to insert a new one, there is a brief power gap. One or more large capacitors can keep power to the circuit during this time.

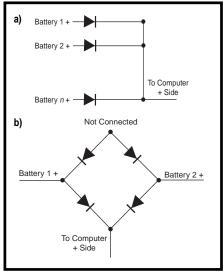

However, a better alternative is to put diodes in series with each set of battery terminals, as depicted in Figure 2. This power bridge has the following advantages over using a single battery:

- the new battery can be inserted before the old battery is removed, so the power gap is bridged

- multiple batteries may be bridged together for increased power capacity

- it protects against possible damage if battery polarity is incorrect

- mixed brands and types of batteries can be bridged together without damage resulting from one "charging" the other

In my typical usage, WearComp6 forms the basis of a complete Internetconnected multimedia video production facility, ham-radio television station, and various other things.

Because of the large amount of equipment I have powered up, the diodes dissipate some heat and must also carry the full current of the maximum anticipated load. I found that a bridge rectifier, by virtue of its larger surface area and the ease with which it may be heatsinked, dissipates the heat better and is easily sewn into my clothing.

#### **VOLTAGE REGULATORS**

The weight, for a given energy level, is much less for Li-Ion batteries compared to lead-acid and NiCd batteries. But, the output voltage of Li-Ion batteries varies widely and drops significantly with usage from a full charge.

Lead-acid batteries exhibit this inconstancy of output voltage to some degree (compared to NiCds, which are much more self-regulating). But, Li-Ion batteries are far worse, almost certainly needing a voltage regulator.

A single 12-V battery can power most of the apparatus, together with an integrated switching voltage regulator to bring the 12 V down to 5 V for powering the computational portion of the apparatus.

#### **POWER SUPPLY**

Isolation from any test probes to the rig is required, but I decided not to isolate the batteries from the rest of the rig. Therefore, I chose to use a nonisolated integrated switching regulator.

I selected the PowerTrends PT6302 (3-A ISR), which is much more efficient than the isolated regulators (e.g. Datel). This extends battery life and produces much less heat.

My WearComp6 is built around the Ampro Core-

Module, along with various other modules that I swapped in and out depending on my plans.

I connected the power to the Core-Module rather than using a power header connector. This enabled me to cut off all the pins on the bottom board, saving considerable space.

It's worth the extra money to get the CoreModule development system, especially if this is the first unit you build. This development system includes the power connector (e.g., MX40) with a 10 (or 8) pin female connector—2 rows of 5 (or 4) to mate with the header pins on the CoreModule. I generally cut off the large connector and 12-V wires, leaving just the small MX40 connector.

It's important to use all three pairs of redundant 5-V wires in parallel for system reliability, especially when you use video-capture cards because they often introduce current surges on startup. Otherwise, you may find that, when you issue a frame-capture command, the computer system reboots itself.

Originally, I built enclosures using sheet metal and a metal-bending machine. Here, however, I'm putting together a system using a commercial off-the-shelf enclosure.

A suitable choice is the so-called half cube enclosure. With it, you can easily keep the power cables 2" or less in length.

All three pairs of 5-V wires may connect to the various parallel pins of the PT6302 ISR. It is a nice coincidence that CoreModule's power connector and the ISR both have three redundant +5-V pins. Connect one of each red wire from the power cable to each of these pins.

The ISR has four redundant ground pins. Connect the three black wires from the CoreModule power cable to three of these, which leaves one ground connection for the 12-V input to the ISR (higher voltage and correspondingly less current).

Connect a single twisted pair of wires to the input (conductors don't need to be so thick owing to the lesser current, as well as the fact that the ISR makes up for line losses). Make sure the twisted pair has tough insulation because it's outside the enclosure and subject to wear and tear against your clothing.

Here, I used a  $100-\mu$ F output capacitor and a  $47-\mu$ F input capacitor with leads soldered to the appropriate pins of the ISR for additional filtering. I selected an input capacitor with a high enough voltage rating to match the range of input voltage that the PT6302 could handle so the rig could run on a wider range of input voltages. I found this useful in the field because I could run the rig from nearly any battery source I might encounter (e.g., a 24-V system).

Next, mount the ISR inside the enclosure. This prevents it from being jostled around where it may touch and short out other components or obstruct air flow. It also helps with heat dissipation (i.e., heatsinking it to the case). The PT6302 ISR comes in six variants, with and without mounting tabs (select the one with mounting tabs), and each of these comes in three variations—horizontal mount, surface mount, and vertical mount.

The vertical mount is preferable, but it's often out of stock. With surface mount, which is most readily available, the pins touch the case. But, if you use a small aluminum shim, the pins are kept sufficiently far away from the case.

Install the PT6302 ISR near the front of the enclosure, facing inwards. Locate it so that the power cable emanates from directly below where the power connector is located on the PC/104 CoreModule. Note that the ¼″ aluminum shim keeps the pins from touching the case.

Be careful not to locate objects near pin 12 (the sense pin) of the ISR. For example, if the disk cable comes too close to pin 12, stray emissions will affect the ISR or set up a feedback loop that makes the whole system unstable.

Touching pin 12 when the computer is running generally causes a spike of

sufficient strength to reboot the computer. If you don't need it, consider breaking it off or cutting it short so it doesn't act like a receive antenna.

Note the capacitors on the ISR as well as inline right near the MX40 connector. Sometimes I also insert series inductors, especially when using the ANDI-FG board, which seems to need them.

I brought the 12-V power leads out of the enclosure and threaded them through a ferrite bead (healthy paranoia). Then, I soldered on connectors for the battery.

#### HARD DRIVE

On the Ampro 100-MHz '486 Core-Module, it's best to put the hard drive on the bottom of the case, assuming you have three boards or fewer in the stack.

I normally cover the circuit-board side of the hard drive with cloth tape (thick gaffer's tape works best) as an precautionary measure. If you place the hard drive on the bottom of the case, put it upside down in the case and wire-tie it down.

With the hard drive underneath, you can make a straight run to the header

Figure 2a—A large number of batteries may be combined, and in this way, there is also protection from accidental polarity reversal. **b**—Where only two batteries are needed, a commercial bridge rectifier may be used. In this case, only two of the four internal diodes are used.

on the CoreModule. Therefore, you can shorten the ribbon cable appreciably, making the insides of the rig neater and resulting in greater reliability and improved air circulation.

#### ASSEMBLING WEARCOMP6

The Ampro VGA board doesn't properly support 24-bit true color, or at least the color fidelity was not as good as I needed. Having a full 24-bit color display was essential for photographic work because the display ultimately became the camera's viewfinder.

Therefore, I generally use a VGA board from another vendor. The Advantech board uses the Tseng4000 chip, which is fully supported in Linux. I use Linux in WearComp because Microsoft Windows isn't sufficiently reconfigurable to adapt to completely new paradigms in computing.

Traditional computing is a primary task, but WearComp makes it secondary. I frequently respond to an E-mail message, type a manuscript, and shoot a personal documentary video, while walking. Windows cannot be easily used through a teletype interface because it forces its GUI on the user.

The beeping speaker annoys others, so use an earphone jack instead. Alternatively, I use a step-up transformer (e.g., to generate a mild electric shock) or a silent vibrotactile device. I usually wear the computer in a waist bag or lumbar pack. The Mountainsmith daypack or tourpack is appropriate for the computer itself and leaves room for a good collection of other peripherals.

#### **KEYBOARD**

Data entry is typically through the camera (e.g., you can color mark each finger and track them using a PC/104 machine-vision system like Cognachrome ["Robots with a Vision," *INK* 92]). That way, you can use your finger to outline an object and select it by pinching two fingers together.

Alternatively, I use a collection of push-button switches. A few switches, appropriately arranged, may be connected to the parallel port of the computer and serve as a data-entry means (see Photo 1).

If you decide to use the switches as your keyboard, you need to write a small program that takes input this way. But if you write a device driver for both DOS and Linux, don't use LiLo (Linux Loader).

Use loadlin instead because there is no control of the computer at the LiLo prompt since your program or device driver which needs to accept input from the switches hasn't run yet. So, you can't use the keyboard to select operating systems at the LiLo prompt.

Photo 2 shows the completed Wear-Comp6 on my workbench, next to a VGA-to-NTSC scan converter.

#### TELEVEYES

By connecting WearComp to a headmounted display and plugging in some sort of keyboard, you have a complete computer system you can use while walking around doing other things.

The limited availability of reasonably priced, small, VGA head-mounted displays as well as their poor tonal range suggest NTSC as an alternative. Indeed, early versions of WearComp used NTSC, and there is a long history of availability of NTSC displays.

In particular, you can often salvage camcorder viewfinders and build them into eyeglasses. I usually find these units for under \$20, and it's clearly the lowest-cost solution. Larger tubes (like the ones I have from 15 or 20 years ago) last for years and provide good resolution and excellent tonal fidelity.

There is a common misconception (due to cheap game displays and consumer television) that NTSC resolution is significantly less than VGA.

However, good NTSC camera viewfinders often use CRTs with 1000 vertical lines of resolution that adequately display VGA-resolution images or text. Some experimentation is needed since text modes in VGA are often not 60 Hz, but many camcorder viewfinders will sync at 60 or 72 Hz.

If you choose to use a low-cost wearable television set (e.g., VirtualVision), you may want to run XFree86 with increased font size (e.g.,  $30 \times 12$ ).

#### NTSC OUTPUT

If you know Linux, you'll probably be able to rewrite the XF86Config file to output a signal that can drive an NTSC display directly. Unfortunately, such a display only works inside XFree86 and not in DOS or while booting to change the BIOS settings.

A simpler approach, which gives you a display that works outside XFree86, is to use a VGA-to-NTSC converter.

Begin by purchasing a Pocket Scan Converter from AITech. This unit, which costs about \$129, consumes a lot of power because of its inefficient regulator. However, you can roughly double its efficiency by replacing its regulator with a PowerTrends ST105VC integrated switching regulator.

Connectors on most devices, including the AITech scan converter, tend to be unreliable. So, I connected the red and black wires for 12-V input and a coaxial cable for video output directly to the circuit board. Routing these through the case, I installed locking inline connectors, which are much more reliable.

#### SET TO GO

Describing the full details of Wear-Cam is beyond the scope of this article. However, if you want more information about the algorithms and theory behind it, check the Internet sites listed in the References section.

Photo 2—The completed

WearComp6 is sitting on

workbench next to the

VGA-to-NTSC scan converter.

The pictures in this article were taken with another WearCam system I wore while building this unit. The visual record of this assembly is another example of the utility of personal imaging. Much of my work in this area is documented from the first-person perspective of the apparatus I wear.

Thanks to Kodak, Xybernaut, ViA, Kopin, DisplayTech, Liquid Image, HP labs, Thought Technologies, VirtualVision, Compaq, Sony, and Antonin Kimla, for making this work possible, and to Robert Kinney and Rich Landry of Natick for updating my ThinkTank/ VibraVest version of my personal imaging apparatus.

Steve Mann, is a faculty member at the University of Toronto, Department of Electrical and Computer Engineering. His present research interests include quantographic imaging, lightspace rendering, and wearable, tetherless computer-mediated reality. He is currently setting up a new Humanistic Intelligence lab to invent the camera of the future. Steve may be reached at mann@eecg.toronto.edu.

#### REFERENCES

genesis.eecg.toronto.edu/research.html www.hi.eecg.toronto.edu/hi/index. html

www.wearcam.org/historical/ index.html www.wearcomp.org/wearhow/ index.html www.pc104.org www.tapr.org www.radio.org

#### SOURCES

#### CoreModule

Ampro Computers, Inc. 4757 Hellyer Ave. San Jose, CA 95138 (408) 360-0200 Fax: (408) 360-0222 www.ampro.com

#### PT6302, ST105VC

Power Trends, Inc. 27715 Diehl Rd. Warrenville, IL 60555 (630) 393-6901 Fax: (630) 393-6902 www.powertrends.com

#### Enclosures

Tri-M Systems 1301 Ketch Ct., Ste. 6 Coquitlam, BC Canada V3K 6X7 (604) 527-1100 Fax: (604) 527-1110 www.tri-m.com

#### VGA board

Advantech America 750 E. Arques Ave. Sunnyvale, CA 94086 (408) 245-6678 Fax: (408) 245-5678 www.advantech-usa.com www.advantek.com.

#### **Pocket Scan Converter**

AITech 47971 Fremont Blvd. Fremont, CA 94538 (510) 226-8960 Fax: (510) 226-8996 www.aitech.com

#### **Battery vest**

NRG Research, Inc. 840 Rogue River Hwy., Ste. 144 Grants Pass, OR 97527 (541) 479-9433 Fax: (541) 471-6251 www.nrgresearch.com

#### IRS

404 Very Useful 405 Moderately Useful 406 Not Useful

# FEATURE ARTICLE

Brian Kurkoski

# Design Embedded Systems for Low Power

When it comes to battery management, conventional techniques don't always cut it. Brian shows how to get around traditional restrictions and still reduce power consumption. Find out how to get the most out of battery life. ou're ready to begin work on your latest design: a handheld measurement and data recorder. The unit must run off batteries for a reasonable length of time, so you want the design to use as little power as possible. A quick calculation shows that conventional techniques yield a battery life of only a few hours, but the system must run for several

times that on a single charge. By reducing the power consumption, however, you extend the battery life. In this article, I show you exactly that—how to reduce power consumption in embedded systems.

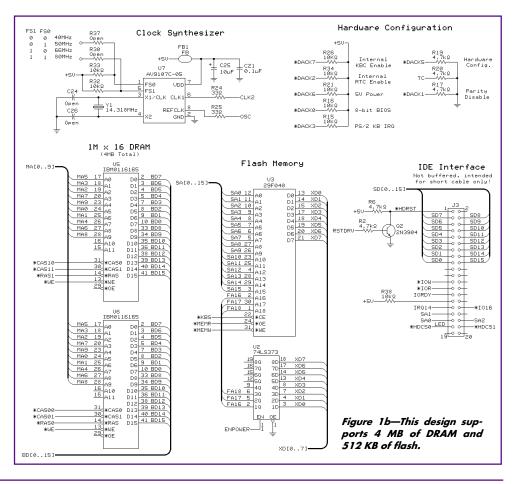

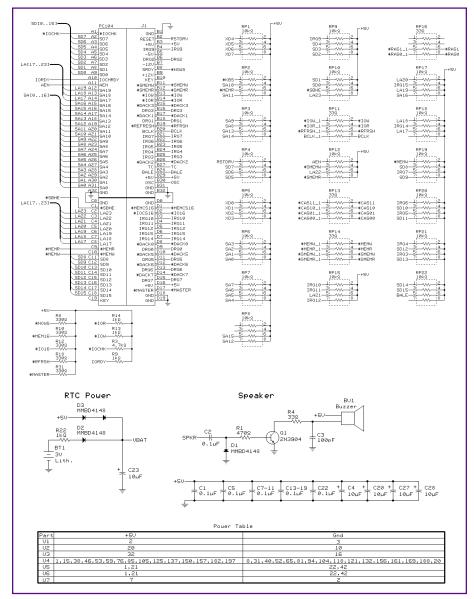

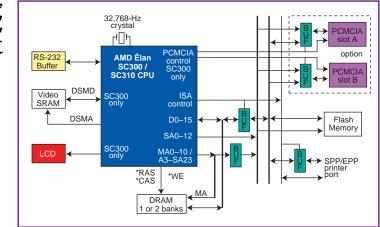

Advances in IC technology make it possible to create practical low-power designs with relative ease. The power your board consumes is determined mostly by the design's supply voltage and operating frequency. However, there are a number of other considerations for a successful low-power design.

#### THE POWER EQUATION

A reasonably accurate approximation of power consumption in an IC is:

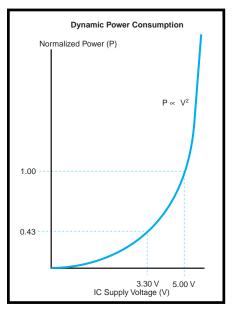

$$P = V^2 \times f \times C + P_{stati}$$

where  $V^2 \times f \times C$  is the dynamic power consumption and is largely under the designer's control.  $P_{static}$  is associated with the IC's quiescent current and depends on the characteristics of the die, temperature, and supply voltage. *V* is the supply voltage, *f* is the operating frequency, and *C* is the capacitive load.

#### REDUCING SUPPLY VOLTAGE

That the power consumption follows a square law is good news: great power savings are realized for small reductions in supply voltage.

Compare a system operating at 5-V supply versus 3.3 V. Reducing the voltage supply from 5 to 3.3 V reduces the dynamic power consumption to:

$$\frac{3.3^2}{5^2} = 43\%$$

of the original, which is a power savings of 57%. Figure 1 shows this graphical square relationship.

To reliably run a system at a reduced supply-voltage level, you must have ICs specified for operation at the level in question. A few years ago, your component selection may have been restricted because the part you wanted wasn't offered in a low-voltage version.

Today, many parts are available for  $3.3-V \pm 10\%$  power-supply operation. (3.3 V  $\pm 10\%$  is usually taken to be 3.0-3.6 V; in fact, this is a JEDEC standard for 3.3-V supply voltages.)

Figure 1—The dynamic power consumed by an IC is proportional to the square of the supply voltage, so reducing the supply 5.0 V to 3.3 V results in a 57% power savings.

You can also find  $3.0-V \pm 10\%$  parts (often referred to as 2.7-V parts; 3.0 V - 10%), but they're less common, which makes designing a 2.7-V system difficult.

#### FAST CLOCKS

Power consumption is proportional to operating frequency. As the operating frequency goes to zero, the dynamic portion of the power consumption also approaches zero. This situation leaves only the static power consumption, which typically is in the microwatt range for CMOS ICs.

Because power consumption depends heavily on clock speed, choose a processor speed as fast as your application needs, and no faster. Running the clock at a frequency higher than necessary wastes valuable battery power.

Also, substantial power savings can be realized from intelligently managing the CPU clock speed. If your CPU clock is fixed at a blazingly high speed to accommodate a compute-intensive task (e.g., data processing), then considerable battery power is lost when the system performs a less CPU-intensive task (e.g., acquiring data).

Enter a solution: the scalable clock. The microprocessor can program the frequency of its own clock to match the processing speed of the task being performed. Thus, for a minimal amount of additional hardware and software, the programmer can improve battery life by dynamically scaling the clock based on the computational load.

Simple on-chip scalable clocks, such as those found on Zilog's Z180, divide the crystal frequency to derive the CPU clock. Although this scalable clock is simple, the oscillator still operates at the nominal frequency, consuming a steady current.

Some larger microprocessors (e.g., Motorola's MC68328 DragonBall and