# CERTIFICATIONS JOURNAL #97 AUGUST 1998 DEBUGGING TECHNIQUES

### **PROM Programmer Construction**

**Capturing Mixed Signals**

Memory Management in Smart Cards

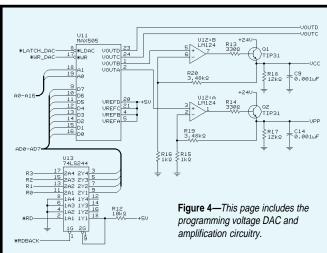

Debugging an Embedded PC Application

# TASK MANAGER

### Almost Made 100

few months ago, I wrote in this column about the beginnings *of Circuit Cellar INK* and described how I've been involved with the magazine in some capacity since the very first issue. I suppose that column could be viewed as a foreshadowing of what

was to come.

I've always been an engineer at heart. My parents like to tell tales of how, as a child, I had a see-through bulldozer that I took apart—at least a million pieces—and put back together without batting an eye. Through all the years I've been involved with editing *Circuit Cellar INK*, I've always kept a hand in the engineering side of things. It's been the therapy I could fall back on when the stresses of deadlines and printer mistakes became too much.

I've reached a point now that I've had to make a choice: engineering or editing? The answer has always been obvious, but not necessarily easy. As of this issue, I'm turning over the reins to my fellow editors on the *INK* staff and will be pursuing design activities full time. I'll continue to have a hand in the magazine's production on the side, so you'll continue to see my name from time to time. Maybe I'll actually have time to write an article or two. I'll also continue to be active in the Circuit Cellar newsgroups, so you haven't heard the last of me.

Thanks to the many of you who have become friends over the years, providing constructive feedback and encouragement. I trust we'll be able to maintain the relationships even though I've moved on.

I'd also like to take this opportunity to thank my colleagues at *INK* for all I've gained from them, whether it be Tom's enthusiasm and commitment on the West Coast, Elizabeth's exceptional attention to detail, KC's amazing Photoshop capabilities, or Janice's insistence on high editing standards in each and every issue. Such a strong team, along with Steve's determination to offer application-oriented, embedded-systems articles, will ensure *INK* readers the same level of editorial excellence. I pass my mantle on with confidence that the job will continue to be well done.

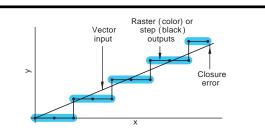

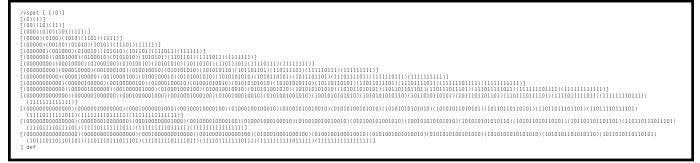

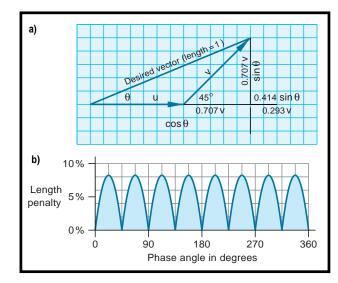

Now, before I start packing my files, let me show you the kind of editorial quality I'm talking about. We lead off with the first writeup of one of our Design98 contest winners. Norman Jackson took first place in the PIC16XXX category with BitScope, a mixed-signal capture engine. Mike Smith and Jason Wudkevich follow with a look at how to use virtual devices to test and debug your system and its peripherals. Bobby Crouch finishes the two-part series on smart cards by showing you how to juggle memory so that your smart-card design stays secure. Don Lancaster closes our feature section with an introductory look at how to keep vector-to-step conversions as fast and smooth as possible.

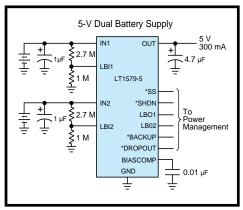

Stuart Ball launches a new MicroSeries on how to build a PROM programmer. His first article focuses on putting the hardware together. This month both Jeff and Tom are bent on power. Jeff is fed up with wall warts and is looking for transformerless power conversion, while Tom simply wants to check out the newer brawn. He takes a look at offerings from Linear Technology, Maxim, Motorola, and National Semiconductor.

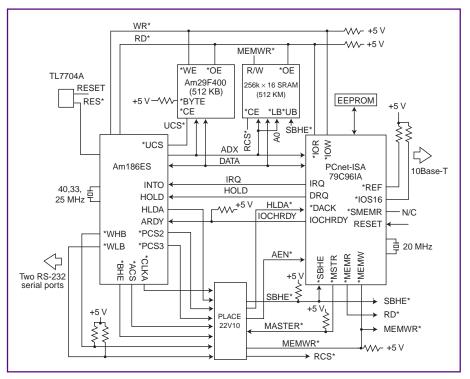

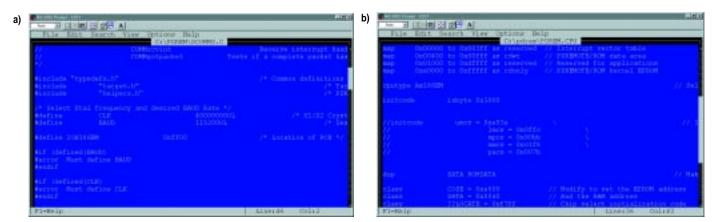

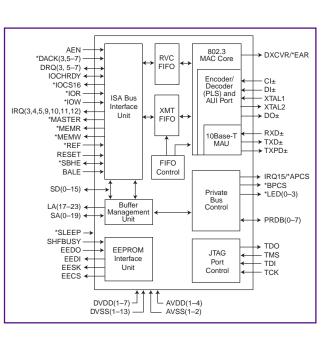

Ernie Deel starts off the *EPC* section by examining interprocess communication via anonymous pipes, and Edward Steinfeld checks out FAT32, a file system for data-intensive applications. In the columns, Ingo looks at real-time data acquisition and Fred checks out how to debug using the Net186.

ken.davidson@pobox.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia ASSOCIATE PUBLISHER Sue (Hodge) Skolnick

CIRCULATION MANAGER Rose Mansella BUSINESS MANAGER

Jeannette Walters

ART DIRECTOR

ENGINEERING STAFF

PRODUCTION STAFF Phil Champagne

James Soussounis

KC Zienka

Jeff Bachiochi

John Gorsky

MANAGING EDITOR Janice Hughes

EDITOR-IN-CHIEF

Ken Davidson

TECHNICAL EDITOR Elizabeth Laurençot

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ingo Cyliax Fred Eady Rick Lehrbaum

NEW PRODUCTS EDITOR Harv Weiner

> Cover photograph Ron Meadows—Meadows Marketing Many thanks to Alfred Baier of Manchester Center, VT, for sculpting the pipe on the front cover just for *INK*. **PRINTED IN THE UNITED STATES**

#### ADVERTISING

ADVERTISING SALES REPRESENTATIVE Bobbi Yush Fax: (860 (860) 872-3064 E-mail: b

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster (860) 875-2199

Fax: (860) 871-0411 E-mail: val.luster@circuitcellar.com

CONTACTING CIRCUIT CELLAR INK

SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 ENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066

UTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

> For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$88. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar INK<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, *Circuit Cellar INK<sup>®</sup>* disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in *Circuit Cellar INK<sup>®</sup>*.

Entire contents copyright © 1998 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

|                                                                          | 12                            | <b>BitScope</b><br>A Mixed-Signal Capture Engine<br><i>Norman Jackson</i>                          |                                                                                 |          |  |  |  |

|--------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------|--|--|--|

|                                                                          | 22                            | Simulating Micro-Controlled Systems<br>Mike Smith & Jason Wudkevich                                |                                                                                 |          |  |  |  |

|                                                                          | 60                            | <b>Designing for Smart Cards</b><br>Part 2: Practical Implementation<br><i>Bobby Crouch</i>        |                                                                                 |          |  |  |  |

|                                                                          | 66                            | <b>Vector-to-Step Conversions</b><br>An Introductory Tutorial<br><i>Don Lancaster</i>              |                                                                                 |          |  |  |  |

|                                                                          | 70                            | MicroSeries<br>Build a Serial Port PROM Programmer<br>Part 1: Hardware Construction<br>Stuart Ball |                                                                                 |          |  |  |  |

|                                                                          |                               | Stuart Ball                                                                                        | Task Manager                                                                    | 2        |  |  |  |

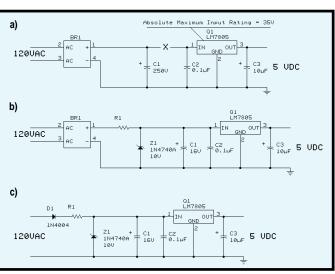

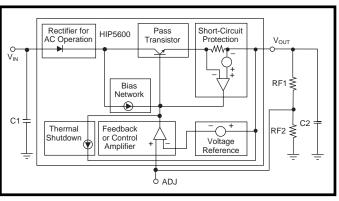

|                                                                          | 78                            | From the Bench<br>Transformerless Power Conversion<br>Jeff Bachiochi                               | Ken Davidson<br>Almost Made 100                                                 |          |  |  |  |

|                                                                          | 82                            | <ul> <li>Silicon Update</li> </ul>                                                                 | Reader I/O                                                                      | 6        |  |  |  |

|                                                                          | 0~                            | Power Trip                                                                                         | New Product News                                                                | 8        |  |  |  |

|                                                                          |                               | Tom Cantrell                                                                                       | edited by Harv Weiner                                                           | Ŭ        |  |  |  |

|                                                                          |                               | S                                                                                                  | Advertiser's Index/<br>September Preview<br>Priority Interrupt<br>Steve Ciarcia | 95<br>96 |  |  |  |

|                                                                          | When Boilerplates<br>Won't Do |                                                                                                    |                                                                                 |          |  |  |  |

|                                                                          | 3                             | 2 Nouveau PC                                                                                       | -                                                                               |          |  |  |  |

| edited by Harv Weiner                                                    |                               |                                                                                                    |                                                                                 |          |  |  |  |

| 36 Interprocess Communication<br>Using Anonymous Pipes<br>Ernie Deel     |                               |                                                                                                    |                                                                                 |          |  |  |  |

| 42 FAT32—File System for Data-Intensive Applications<br>Edward Steinfeld |                               |                                                                                                    |                                                                                 |          |  |  |  |

|                                                                          |                               | 9 RPC Real-Time PC<br>Data Acquisition<br>Ingo Cyliax                                              |                                                                                 |          |  |  |  |

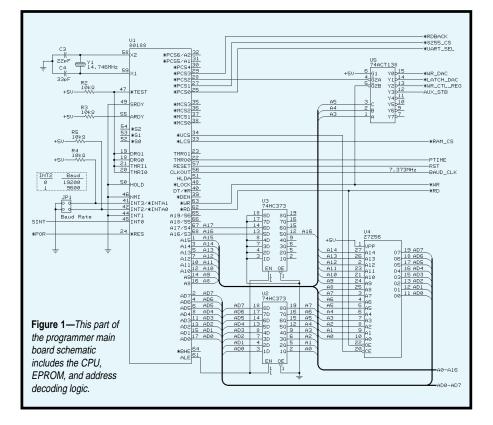

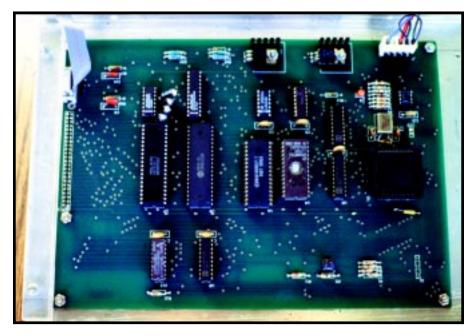

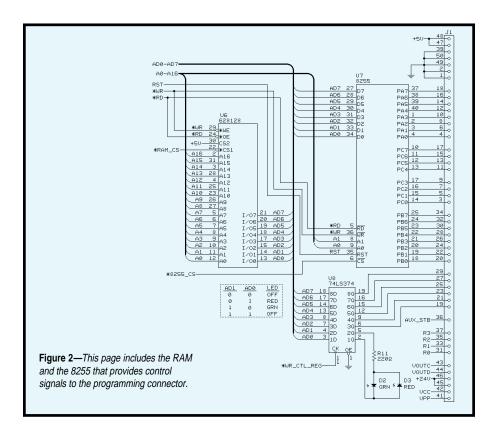

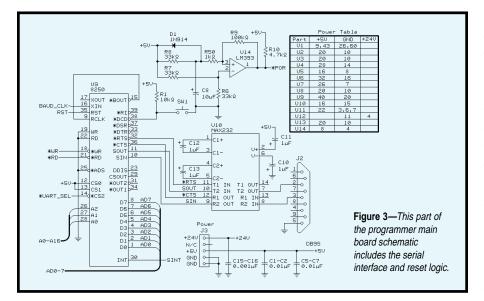

|                                                                          |                               | 5 APC Applied PCs<br>Debugging & the Net186<br>Fred Eady                                           | www.circuitcellar.com                                                           | *        |  |  |  |

# **READER** I/O

#### **CONSIDER THE ALTERNATIVES**

*INK* 96 came with a surprise. It included an article on FreeDOS, which complies to the GNU GPL and hence is totally free. But, freedom comes with a price: there's still no stable version (according to freedos.org).

What about using PTS-DOS? It is over 99.99% MS-DOS compatible, written in 80x86 assembly language, and comes with full sources. The makers restrict users to the extent that one user may not base a completely new OS on it, but you can overcome this by buying one CD with each version or by paying a fee to the makers.

PTS-DOS's native mode is "flat real mode." When I load a segment register with zero, I can use EBX as a 32-bit pointer in linear address mode. Now, I only have to load HiMem386.SYS and I'm off, with all the freedom of real mode but the addressing of protected mode.

PTS-DOS, with full sources, costs a mere \$50. Perhaps it's time to look at this software masterpiece that's been shipping, selling, and performing for over four years.

Jan Verhoeven

aklasse@tip.nl

#### AMAZING THE DIFFERENCE OF A MAGNITUDE!

After reading my article "Using the PC for Radiation Detection" in *INK* 96, one of my colleagues, Dr. Ed Webb, E-mailed me to point out a decimal error: 1 nCi of activity is equal to 37 disintegrations per second, not 0.37 as I said in the article.

Therefore, my basement should reach the EPA limit for radon in 0.388 days, not 38.8 days as I calculated. So, I should run my fan more often, about 2 hours every 12 hours, rather than once per month.

Dan Cross-Cole

crosscol@erols.com

#### WEARABLE COMPUTING—WHERE TO SHOP

The "WearCam" article (*INK* 95) neglected to mention that there's an entire community dedicated to wearable computing. For example, HandyKey's Twiddler keyboard provides an off-the-shelf method for one-handed typing and mousing at speeds up to 60 wpm. As well, there is a public mailing list for people building wearable computers maintained at wearhard@haven.org.

The annual conference for wearable computing, the IEEE International Symposium on Wearable Computers (ISWC), will meet this year October 19–20 in Pittsburgh, PA. Details may be found at <wearables.www.media.mit.edu/projects/wearables/>.

#### Thad Starner

testarne@media.mit.edu

#### CAN I SEE, TOO?

I was interested in Steve's Priority Interrupt editorial on "Design98—A Marketer's PICnic" (*INK* 94). If I am interpreting his comments correctly, he believes the Design98 contest was a huge success.

However, there's just not enough pages in *INK* to publish all those great design entries. Is there any chance that the rest of us will be able to share in these designs?

JR Morgan AQFRTSTR@aol.com

For more information on the projects submitted for Design98, be sure to check out the new Design Forum on the Circuit Cellar Web site—especially the section entitled PIC Abstractions.

#### **READERS, SPEAK UP!**

A lot of computing magazines used to publish articles by people who were deeply interested in how things work. A lot of us never built the exact projects shown in the articles, but we learned something from each one of them. Frequently, it's the case that we get our best ideas from looking at what others have done. We improve on what we have learned, twist it, and turn it to new purposes.

*Circuit Cellar INK* is great because it still has the right elements, and I'll continue subscribing as long as it does. Although there may be ways *INK* can increase its reader satisfaction level, I certainly think readers have a responsibility to make their interests known.

Tom McGahee

tom\_mcgahee@sigmais.com

## NEW PRODUCT NEWS Edited by Harv Weiner

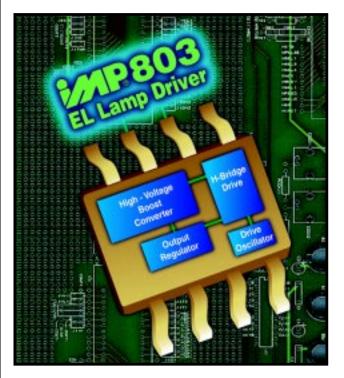

#### ELECTROLUMINESCENT LAMP DRIVER

The **IMP803** is a high-voltage, low-power electroluminescent (EL) lamp driver that generates the 180-Vp-p drive signal needed to excite an EL lamp from a lowvoltage DC source like a battery. EL lamps are used to backlight LCDs and keypads in low-power portable personal communications devices such as pagers, mobile phones, and personal digital assistants (PDAs).

The IMP803 incorporates four EL-lamp-driving functions on-chip: the switch-mode power supply, its high-frequency oscillator, the high-voltage H-bridge lamp driver, and its low-frequency oscillator. By boosting an input voltage of 2–6 V up to 180 Vp-p (maximum), EL lamps of 30-nF capacitance are driven to high brightness. If the lamp-drive voltage reaches 180 Vp-p, an internal circuit adjusts the boost converter to save energy.

Two external resistors permit the switching regulator frequency and lamp-drive frequency to be adjusted. Connecting these resistors to ground places the IMP803 into a powered-down mode.

The IMP803 is available in an eight-pin SO package or in die form for high-volume, low-cost chip-onboard applications. The 1000-quantity price of the IMP803LG is **\$0.96** each. An evaluation board, the **IM803EV1**, is available at an introductory price of **\$25**.

IMP, Inc. (800) 438-3722 • (408) 432-9100 Fax: (408) 434-0335 • www.impweb.com

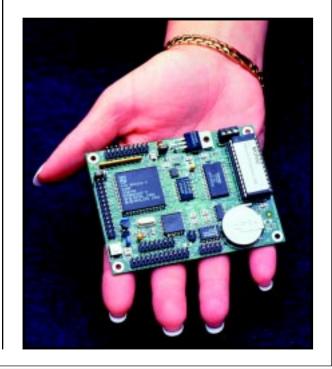

#### 8051-COMPATIBLE EMBEDDED CONTROLLER

The **RPC-220** is a compact, 8051-compatible embedded controller that's designed for monitoring or simple control applications. The  $3.85'' \times 2.85''$ form-factor board contains flash memory to enable remote program updates by modem or notebook, a year-2000-compliant real-time clock (which can wake up the card from low-power modes), and a battery backup of its 512 KB of RAM. Power inputs are 5.0/5.4 to 25 V, and a regulated 5 V is available to power user circuits.

Its 19 digital I/O lines can also be used for pulse output (two PWM and two square wave) and pulse width measurements. Analog I/O is accomplished through an eight-channel, 10-bit converter and a two-channel analog output. An LCD port enables display of current information, and hardware and software RS-232 ports are available.

The RPC-220 development system runs on Windows-based PCs. The development system includes an RPC-220 board, hardware and CPU manuals, cables, terminal boards, power supply, C compiler, and more than a dozen stand-alone application programs. Prices start at under **\$100** in quantity. A development system costs **\$435**.

Remote Processing (800) 642-9971 • (303) 690-1588 Fax: (303) 690-1875 www.remotep.com

# NEW PRODUCT NEWS

#### **TWO-AXIS SERVO CONTROLLER**

The **DC2-STN** is a stand-alone two-axis servo controller with two auxiliary outputs for stepper control. Its small footprint  $(9.5'' \times 4'' \times 5'')$ , back-panel mounting tabs, and removable/pluggable screw terminals make it well suited for OEM applications. It operates on universal AC voltage (100–240 VAC, 50/60 Hz) and has an integrated DC power supply.

Features include an RS-232 communication interface for programming and networking as well as 32 KB of nonvolatile memory to store macros, programs, and point information. It offers optoisolated I/O at industrial voltage levels, status LEDs, and a watchdog relay output.

The DC2-STN supports point-to-point positioning, velocity control, master/slave and gearing, joystick input for manual positioning, circular and linear interpolation, PID filter with velocity and acceleration feed forward, and the ability to change parameters and targets on thefly. The command set supports macros, sequencing, user data-registers, and more. Its multitasking capability permits four independent tasks or routines to run simultaneously without interrupting motion control.

The DC2-STN costs **\$995** in single quantities. OEM discounts are available.

Precision MicroControl Corp. (760) 930-0101 • Fax: (760) 930-0222 • www.pmccorp.com

# NEW PRODUCT NEWS

#### MULTICHANNEL DATA ACQUISITION

Point Six, an authorized software developer for Dallas Semiconductor, has developed an RS-232-powered multichannel analog interface card based on Dallas's onewire technology.

Features include eight channels of analog input on a credit-card-sized board. All eight channels are individually configurable as a 0–5-V 12-bit analog input. The **T8AH7BA** contains a built-in multidrop controller that provides a unique 64-bit registration number, assuring error-free selection and absolute identity of the device. No two parts are alike. The unique addressing enables inputs to be identified absolutely.

The T8AH7BA directly connects to 7B-series industrialstandard analog isolation back panels and modules. All necessary power is derived from the RS-232 port. The T8AH7BA has a built-in RS-232-to-one-wire interface, allowing network expansion to drive up to 200 one-wire devices (e.g., temperature, pressure, force, humidity, pH) over as much as 2000' of Cat-5 twisted-pair cable. All data transfers are CRC-16 error checked. A DDE driver permits effortless interface to most Windows applications. The T8AH7BA is priced at **\$99.95** in single quantities.

Point Six, Inc. (606) 271-1744 Fax: (606) 271-4695 www.pointsix.com

# **NEW PRODUCT NEWS**

#### COMPUTER-CONTROLLED PAN-TILT UNIT

The **PTU-46-70** offers high resolution at 0.771 arc minutes (less than <sup>3</sup>/<sub>4</sub>" at 100 yd.) with speeds at 60° per second and a load capacity of 6 lbs. Applications include

can make on-the-fly position and speed changes. Builtin RS-485 multidrop network capabilities mean a single host port can control up to 127 pan-tilt devices.

computer vision, security, test and measurement, and teleconferencing, as well as photography, video, and special effects. The **PTU-46-17.5** is a high-performance, low-cost, computer-controlled pan-tilt unit that moves over 300° per second with 3.086 arc-minute resolution at a load capacity of over 4 lbs.

The unit features plug-and-play using an RS-232 terminal, enabling the host computer to accurately control pan and tilt speed, acceleration, and position. Self-calibration on reset ensures reliable absolute positioning. Microprocessor control and constant current bipolar drives provide efficient high-speed movement, and the host

The  $3'' \times 5.11'' \times 4.25''$  unit has power-management controls and flexible input power requirements. Host commands control power consumption, which is 16 W peak at full power, 7.5 W peak at low power, and 1 W peak with motors off.

Single-quantity prices are **\$1800** for the PTU-46-17.5 and **\$2100** for the PTU-46-70. Options include international AC/DC power supply, joystick interface, nodal adapter, weatherizing, and C programmer's interface.

Directed Perception, Inc. (650) 342-9399 • Fax: (650) 342-9199 www.dperception.com

## FEATURES

| 12 | BitScope                                |

|----|-----------------------------------------|

| 22 | Simulating Micro-<br>Controlled Systems |

| 60 | Designing for Smart<br>Cards            |

| 66 | Vector-to-Step<br>Conversions           |

# BitScope

### FEATURE ARTICLE

### A Mixed-Signal Capture Engine

Has your office become so cluttered that you can't find your oscilloscope or logic analyzer? No problem, Norman will help you build a lowcost, mixed-signal capture engine that connects to your computer via the serial port. ome time ago, I had a bad experience with a bus—a logic bus. It had six rampaging DSP cards and a SCSI controller all trying to ride at the same time.

About once an hour, there was a sickening crash. After going through the usual stages of blaming the software, I relented, admitted possible culpability, and borrowed a mixedmode DSO.

This machine has a digital sampling oscilloscope and a logic analyzer effectively joined at the hip. They share a common trigger module that enables the user to identify a complex event and record the state of the target hardware before and after the trigger—in both the analog and digital domains.

In the case of my erratic bus logic, the culprit turned out to be a delinquent GAL with a ground bounce problem. The offending chip had its duties reassigned and the documentation police were alerted. Engineer triumphs over bug.

By employing a high-tech piece of test equipment, I could trigger on a complex digital event and correlate this event to an oscilloscope trace that showed what was really happening in the analog domain. I was saved in the nick of time, but despite having formed a deep attachment to the trusty 'scope, I had to give it back.

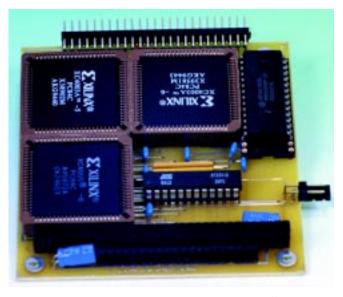

Following this adventure, I started musing about how to roll my own version of that useful electronic gadget. After some mental tinkering and with the added incentive of Design98, I was soon sketching electronic stuff on the grid pad. BitScope began to emerge (see Photo 1).

#### THE BIG PICTURE

The basic idea behind BitScope is that of a specialized piece of datacapture hardware that doesn't include any user interface other than an RS-232 plug. Most engineers have more computers, mice, and keyboards than they know what to do with. If I was going to build a cheap 'scope, I certainly didn't want any more of that stuff.

What I needed was an electronic drone that could capture and disgorge data on command. No more, no less. The commands had to be simple ASCII characters that are intuitive and easy to learn. The PC-based user interface can then synthesize functionality of arbitrary complexity by sending scripts of command characters and receiving the replies.

The answer: a virtual instrument where specialized hardware does the electronic test job and a PC lets the engineer drive it. One big advantage of this setup is that changing the way the virtual instrument works doesn't usually involve reprogramming chips (hard) but may be done by downloading a new program from the 'Net (easy).

As described in the sidebar "Virtual Machine Architecture," the microcontroller firmware is designed as a virtual machine (VM). The BitScope design is novel because it has an unusual arrangement of the VM program code. The

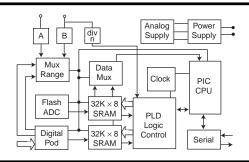

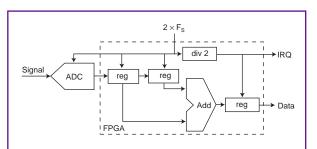

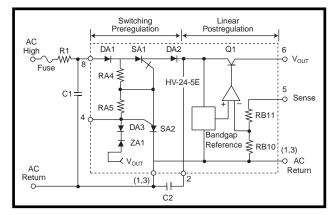

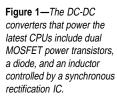

Figure 1—This block diagram of the mixed-signal capture engine shows basic design architecture.

instructions are not located in memory on the microcontroller but reside in the user interface and are executed atomically direct from the serial port.

If you study BitScope's virtual instruction set, you see that arranging things in this crazy way has its advantages. All instructions are atomic. In other words, there is no inherent syntax associated with any command byte.

#### Virtual-Machine Architecture

A virtual machine (VM) consists of a fully functional processor hosted on an unrelated substrate machine. VM design has advantages over conventional coding. Each instruction may be highly optimized for performance—unlike a general-purpose interpreter like BASIC, which can do anything but inefficiently. VM instructions are compact like assembly but perform extremely complex tasks. Once a register and command set are devised, you can add new instructions to enhance the machine. The original instructions remain the same, which promotes modularity. Since the operational definition of the VM is rigid, firmware changes tend to be straightforward, even to the point of hosting the target architecture on a completely new substrate.

In this design, the PIC16F84 is a substrate to implement a custom BitScope machine with its instruction set becoming microcode to implement the VM. So, the BitScope VM has instructions and registers but they're unrelated to the PIC native instruction set. The virtual registers are hosted by PIC memory registers but have meaning only to the BitScope. Similarly, BitScope has no use for XOR- or DECFSZ-type instructions. Instead, it has instructions for manipulating registers, starting sample RAM, and dumping captured data. BitScope registers may be option bits, timer constants, sample address, and so on. The exact function of the register set is detailed in Table i. Table ii shows the current command set.

Most interpreters run from a program stored in memory. BitScope is different because it executes directly from

| R0  | Puto Input Pog                     | Assemble input data bara                                      |

|-----|------------------------------------|---------------------------------------------------------------|

| R1  | Byte Input Reg<br>Register Pointer | Assemble input data here<br>Pointer to R(0–ff)                |

| R2  | Register Source                    | Pointer to R(0–ff)                                            |

| R3  | Sample Preload L                   | Low byte of RAM addr to load to Spock                         |

| -   |                                    | ,                                                             |

| R4  | Sample Preload H                   | High byte of RAM addr to load to Spock                        |

| R5  | TRIG Logic Byte                    | Logic levels for Spock to match, loaded<br>during Spock Init  |

| R6  | TRIG Mask Byte                     | Don't Care bits in trigger match, loaded<br>during Spock Init |

| R7  | Spock OPTION byte                  | TRIG and PG1 setup in Spock                                   |

| R8  | Trace Register                     | Trace Option controls Sample operation of BitScope            |

| R9  | Counter capture Lo                 | Counter low byte shifted out of Spock                         |

| R10 | Counter capture Hi                 | Counter high byte shifted out of Spock                        |

| R11 | DELAY-L                            | Post TRIG delay before halting                                |

| R12 | DELAY-H                            | Post TRIG delay before halting                                |

| R13 | TimeBase                           | TimeBase expander count                                       |

| R14 | Channel-A/B                        | Channel Range settings for Chop                               |

| R15 | Dump Length                        | Counter for number of samples trans-<br>mitted per request    |

| R16 | EEPROM Data                        | Data register for EEPROM                                      |

| R17 | EEPROM Address                     | Address register for EEPROM                                   |

| R18 | POD Transmit                       | Register holds byte for POD                                   |

| R19 | POD Receive                        | Register gets byte from POD                                   |

**Table i**—The BitScope virtual machine has a set of 20 registers. The operation of the machine and all its instructions refer to these registers.

the serial port. BitScope's instruction set is designed to have no syntax, so there can be a maximum of 256 instructions and each is stand alone—just like a RISC instruction set. An atomic protocol means the software at both ends of the serial line is simple and does not have to preserve state information. In a PIC with 1024 words of program, it's advisable to be economical with code, espe-

|              | Reset                           | Reset the machine and print its ID string                                                                                                | 54 T | Trace with TRIG stop   | Begin sample with Opt mode, until Trig then Delay, Halt Sample Clk, and                                               |

|--------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 23 #         | Load Source Reg                 | Store R0 into R2. Set up R2 which is a source reg. A reg-to-reg move may be done by pointing to a source (R2) and                        | 5b [ | Clear R0               | print sample add.<br>Reg R0 is cleared. This usually<br>precedes a nibble load                                        |

|              |                                 | destination (R1).                                                                                                                        | 5d ] | Nibble swap R0         | R0:(0–3) is swapped with R0:(4–7).                                                                                    |

| 2b +<br>2d - | Inc REG<br>Dec REG              | Incr the reg pointed to by R1<br>Decr the reg pointed to by R1                                                                           |      |                        | This command puts the entered<br>nibbles in the correct order.                                                        |

| 30 0         | Enter nibble 0                  | Incr R0 by 0 and nibble swap R0                                                                                                          | 61 a | Enter nibble 'a' hex   | Incr R0 by 10 and nibble swap R0                                                                                      |

| 31 1         | Enter nibble 1                  | Incr R0 by 1 and nibble swap R0                                                                                                          | 62 b | Enter nibble 'b' hex   | Incr R0 by 11 and nibble swap R0                                                                                      |

| 32 2         | Enter nibble 2                  | Incr R0 by 2 and nibble swap R0                                                                                                          | 63 c | Enter nibble 'c' hex   | Incr R0 by 12 and nibble swap R0                                                                                      |

| 33 3         | Enter nibble 3                  | Incr R0 by 3 and nibble swap R0                                                                                                          | 64 d | Enter nibble 'd' hex   | Incr R0 by 13 and nibble swap R0                                                                                      |

| 34 4         | Enter nibble 4                  | Incr R0 by 4 and nibble swap R0                                                                                                          | 65 e | Enter nibble 'e' hex   | Incr R0 by 14 and nibble swap R0                                                                                      |

| 35 5         | Enter nibble 5                  | Incr R0 by 5 and nibble swap R0                                                                                                          | 66 f | Enter nibble 'f' hex   | Incr R0 by 15 and nibble swap R0                                                                                      |

| 36 6         | Enter nibble 6                  | Incr R0 by 6 and nibble swap R0                                                                                                          | 6c   | Load R0 from @R2       | Copy contents of reg pointed to by R2                                                                                 |

| 37 7         | Enter nibble 7                  | Incr R0 by 7 and nibble swap R0                                                                                                          |      |                        | toR0                                                                                                                  |

| 38 8         | Enter nibble 8                  | Incr R0 by 8 and nibble swap R0                                                                                                          | 6e n | Next Address           | Incr addr reg R1                                                                                                      |

| 39 9         | Enter nibble 9                  | Incr R0 by 9 and nibble swap R0                                                                                                          | 70 p | Print REG value @R1    | Print <cr>ASCII,ASCII<cr></cr></cr>                                                                                   |

| 3c <         | Get ctr value<br>from Spock     | Shift the current 16 bit ctr value from<br>Spock into R9, R10                                                                            | 73 s | Store R0 to @R1        | Copy contents of R0 to reg pointed to<br>by R1                                                                        |

| 3e >         | Program Spock<br>from Registers | Load 5 bytes of data from R3–R7 into<br>Spock. Previous contents of ctr are<br>destroyed                                                 | 75 u | Update RAM pointers    | Copy contents of R3,4 to R9,10.<br>Updates sample addr value from<br>sample preload reg.                              |

| 3f ?         | Print Machine ID                | Print <cr>CHAR8–CHAR1<cr><br/>where CHAR<i>n</i> is part of a string<br/>identifying the type and revision of this<br/>device.</cr></cr> | 78 x | Exchange byte with POD | Transmit byte in POD_TX to POD<br>IO-0. Wait for reply byte on IO-1<br>and put it inPOD_RX then return it to<br>host. |

| 40 @         | Load Address Reg                | Store R0 into R1. Use to set up reg ptr.                                                                                                 | 7c   | Pass Through byte      | Transmit byte in POD_TX to POD IO-0.                                                                                  |

| 53 S         |                                 | Dump lines of 16 Sample RAM                                                                                                              |      | to POD                 | Connect IO-1 to Serial Out for host.                                                                                  |

|              | RAM (CSV)                       | values (digital and analog)                                                                                                              |      |                        |                                                                                                                       |

Table ii—The command set for the BitScope virtual machine is a subset of the byte values between 0 and 255. Active commands are confined to the ASCII range from 0 to 127.

cially given the importance of reliably transmitting packets over a serial link.

I decided the BitScope command set should use common printable ASCII commands. Since the assignment of byte codes is arbitrary, any value could mean "enter hex nibble 3," but obviously 3 is a good choice. The general scheme for allocating byte-code values and their ASCII symbol is:

- numerals—data entry

- operators—manipulation of register values

- lower case—general machine operation

- upper case—major machine functions

- nonprintables—reserved for future commands

An example script for loading R6 with 0x5a is [6]@[5a]s. It may seem obscure, but if you study it, it should make sense. Ultimately, a user interface will debug scripts and writing scripts will only be necessary if a user develops a new mode of operation or drives it directly from a terminal.

All BitScope operations, including wait on trigger, may be interrupted by any serial command. The first part of the software UART ensures that the sample clock is halted. When a serial byte is assembled and echoed, the UART turns on and, once activated, aborts all previous operation. In this sense, BitScope's command protocol is truly atomic. Each command ends in a halt, if not prematurely aborted. ASCII code 00 is the reset vector, so it can get the PIC's attention with a <break>.

Inevitably, a VM like this will get enhanced firmware. Microchip has devices that potentially double the number of byte codes implemented. To cope with the potential of other feature sets, ? returns a 32-bit ID code. User-interface software may keep a register of feature sets supported by each byte-code revision.

All instruction bytes are echoed to provide a simple handshake mechanism. And, all instructions are preemptive, so you can always abort the previous command and regain control simply by sending a new command.

#### SERIAL CONNECTION

While a serial interface may seem a bottleneck for a capture engine that can potentially store 64 KB of data, this is not a problem. Thanks to the Internet and 56k modems, most PCs now have fast, buffered UARTs.

The transmission speed of the BitScope serial link can be scaled to 115 kbps using a fast microcontroller. At this rate, you can transfer enough samples to draw a  $640 \times 480$  screen—at most 640 bytes—in about 55 ms, or 18 screens per second.

For lower frequency data or simple sine waves, it's necessary to only send a handful of samples to the host and have the user interface do some curve fitting. Small bursts of contiguous sample data may be used to enhance a waveform display to show high-frequency noise.

Logic analyzers don't need to rapidly update their display at all. After a trigger event, the data may stay in the sample RAM and be downloaded only when the host needs it. At 115 kbps, the total contents of a 16-KB buffer can download in less than 2 s. The user interface may then draw logic state or timing diagrams and manipulate them as necessary.

#### **USER INTERFACE**

Don't think shrink-wrapped monolithic Windows software for this design. Think more about the Linux model where the engineering community builds its own tools and can customize them as needs arise.

Because BitScope uses simple ASCII commands, in a pinch, you can use a terminal program and spreadsheet to display waveforms. For complex applications, you need more advanced software based on C, Delphi, or Visual Basic.

A BitScope user interface can run under many possible environments, including Windows, MAC, Unix, WinCE, Palm Pilot, Psion, DOS, or Amiga. Basically, it can work on any machine with a serial port.

No single person could write all that software. Instead, I made the BitScope design open and documented so you could create what you need.

On *INK*'s Web site, you'll find some user-interface software with source listings to start the ball rolling. Via the Internet, you can also find existing programs that already simulate oscilloscopes, logic circuits, and data displays.

#### **DESIGN PHILOSOPHY**

A good place to start designing is with a functional specification. For BitScope, the main issue was sample rate. While it seemed clear that a 200-MHz sample rate was out of reach, I could easily get to about 50 MS/s and still be ahead on the price/performance curve.

For the engineer dealing with microcontroller circuits, it's unlikely that frequencies of interest will exceed 20 MHz—at least for the time being. Later on, when 3-V logic becomes more prevalent, that 50-MS/s rate can probably stretch to 100 MS/s in an SMT version of the design.

To make BitScope as useful as possible, I was determined that it should physically stand alone. It needed to be unconstrained to a particular machine or bus standard, and I wanted it to communicate with any computer using the ubiquitous RS-232 interface.

From my experience, the most commonly required features of this type of test equipment are two analog input channels and eight digital logic inputs. Combine those features with a flexible trigger capability, and you get a pretty useful instrument. I set a design goal of about \$100 for the cost of required components, all of which should be readily available.

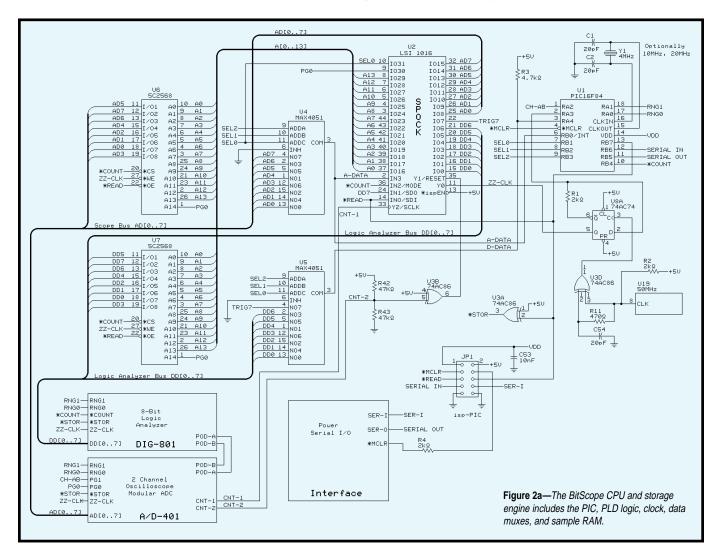

For the core of BitScope, I selected a PIC16F84 micro tightly coupled with a Lattice 1016 PLD. The PIC controls the serial port and implements a VM architecture. The Lattice counts RAM addresses and waits for a trigger.

These chips are cheap and solid performers. Both are flash-memory based for easy upgrades, and they have excellent entry-level development software. Sample RAM is provided by two 32-KB 15-ns cache memories.

These devices will take the design to 50 MS/s and have the great advantage that about eight of them are perched on every '486 motherboard ever built. That should put their head count at about one billion, so don't tell me you can't find any!

Every DSO must be built around a flash ADC. These chips were exotic until a few years ago when digital manipulation of video became popular.

Now, several companies have devices that can provide 40 MS/s or better for

less than \$10. Even an older device like Motorola's MC10319P can sample from DC to 25 MS/s and is available in a DIP package.

In fact, I used this device for BitScope. By selecting a 600-mil DIP package, I could accommodate any of the new SMD devices as a plug-in module and avoid the need for multiple PCB versions.

For vertical amplifiers that process analog signals to the ADC, the video industry again provides a solution. Maxim and Ana-

log Devices both have cheap, stable 300-MHz op-amps that make wide-band amplifier design easy.

Using these devices lets the vertical-amplifier bandwidth get close to 100 MHz, matching the input specs on the new flash ADC chips from Analog Devices and TI. For an insight into why we need such wide-bandwidth vertical amplifiers, see the sidebar "Subsampling—Bending Nyquist."

Photo 1—BitScope was prototyped on a two-layer PCB. Notice that the components are arranged to separate analog and digital sections of the circuit.

#### WALKING THRU SCHEMATICS

Before delving into the schematics, take a look at Figure 1, which overviews the functionality of the BitScope design.

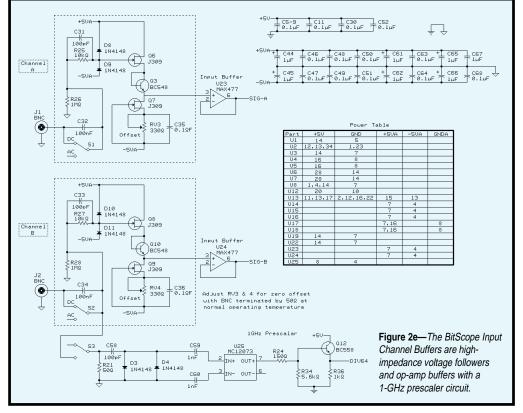

The PIC, the Lattice PLD, and the SRAMs are shown in Figure 2a. These chips are closely coupled to form the sample capture functions at the core of this design.

By using a synchronous tristate clocking circuit, the PIC is able to stop,

start, and preload the Lattice PLD using just a handful of signals. Notice that it's necessary to read in data from the RAM chips one bit at a time because there are no spare eight-bit ports available.

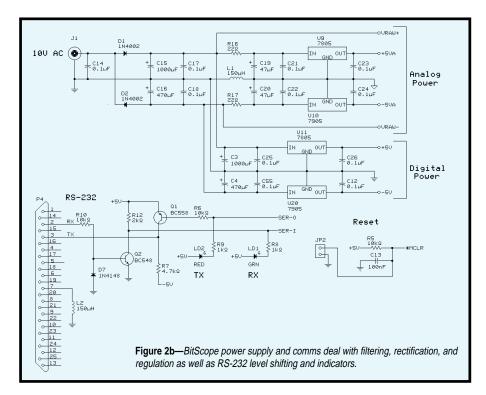

One fundamental rule in mixing analog and digital circuits is to avoid contamination of the analog grounds. Figure 2b shows that great care was taken to isolate the analog and digital sections of this circuit at high frequencies.

Similarly with the RS-232 port, it's best not to allow PC noise to have any path to a test circuit.

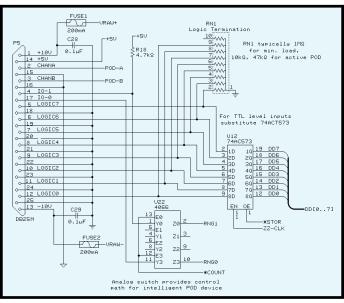

Digital test signals and two spare analog signals are shown on Figure 2c connecting to the DB25M pod connector. Logic levels are latched and conditioned ready for storage in the digital sample RAM.

You might guess from the extra signals on the pod that it's not just

eight logic levels in. As well as fused balanced power supplies, there is a digital I/O communication port. Everything you need is there to connect an active, programmable extension module.

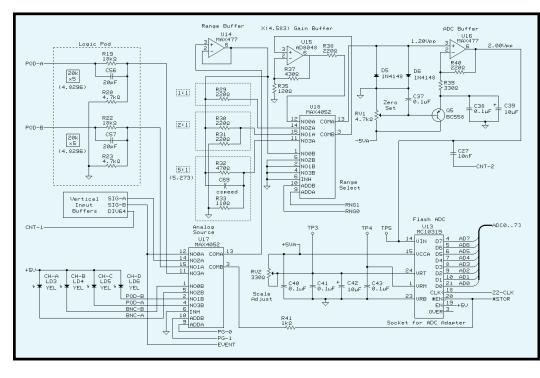

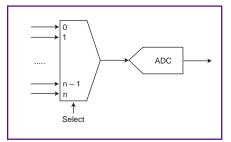

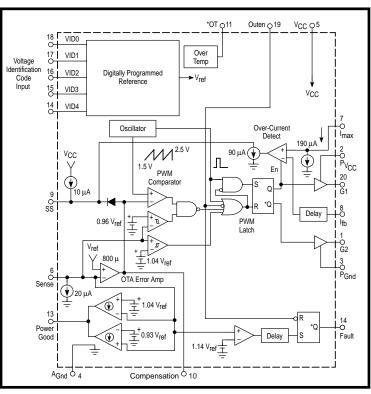

Most of the analog conditioning circuits and the flash ADC are shown in Figure 2d. The circuit consists of an amplifier chain driving through a pair of 4:1 analog mux devices.

Modern video op-amps help here. They give you high input impedance, low output impedance, and unity gain stability.

The PIC controls the mux sources that allow

implementation of range switching and channel chop functions. To accommodate different ADC chips, there are adjustment pots for both the range

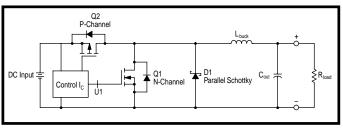

Figure 2c—The BitScope digital capture unit has a logic pod circuit with latching buffer and pod I/O switches.

and offset voltages as required by the manufacturers.

Figure 2e shows the final part of the analog conditioning circuit. Channels

A and B are standard 1-MB input impedance AC/DC BNC connectors. A classic source follower tree driving a unity gain buffer for each channel completes the vertical-amplifier section.

For engineers who like to measure high frequencies, I added a small 1-GHz prescaler circuit, which includes a switchable 50- $\Omega$  terminator hanging off the Channel B input circuit. Note that BitScope has a couple of ways to measure the frequencies of applied signals. I explain the motivation behind this in the sidebar "Subsampling—Bending Nyquist."

#### THAT IS LOGICAL, CAPTAIN

PLDs such as the Lattice 1016 can swallow a whole swag of logic func-

#### Subsampling—Bending Nyquist

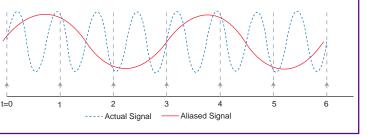

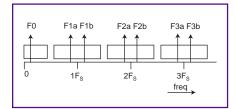

In data-acquisition applications, there is often some confusion about the relationship between bandwidth and sample rate. The Nyquist rate of half of the sampling frequency ( $F_s$ ) is well known to be the maximum frequency that can be captured by periodic sampling at  $F_s$ . Given that mathematical constraint, why would we want an instrument that has a bandwidth of 100 MHz and yet samples at a maximum rate of only 50 MS/s? The answer lies with subsampling.

The Nyquist rate applies to continuous time varying signals. In that general case, the highest-frequency component should be less than half of  $F_s$  (25 MHz at 50 MS/s) to avoid aliasing. Repetitive waveforms are a different matter. They're the only high-frequency waveforms you ever see on an analog CRO. The same waveform is redrawn each sweep, and the eye sees a solid trace. Subsampling is similar. You use multiple samples and overlay them to build an image. Providing that your ADC has a wide bandwidth and a small aperture, it is possible to sample a repetitive waveform over many cycles and build up a snapshot of the exact waveform, limited only by the bandwidth of the signal path. This technique, known as subsampling, is just an example of the RF mixer in the digital world.

Subsampling has a few constraints. It isn't possible to subsample a waveform that's harmonically related to the sampling frequency. Practically, this means that if the waveform of interest is related to the sample frequency, the sample points always fall at the same relative position on the waveform and the regions between will forever remain a mystery.

Another concern has to do with resolving the ambiguous period of the subsampled waveform. Let's say you have a signal of 28 MHz and are sampling at 40 MS/s. In the sample buffer, you'll see a sequence of values with components at 12 and 68 MHz. How can these be plotted to build up a profile of the original 28-MHz signal? Well, if you can measure the fundamental frequency of the sampled wave, that will imply period. Since you know the sample rate accurately, you can fractionally chop the sample buffer up into segments of *n* wave periods and then plot them overlaid. You will have traded the freedom for those *n* waveforms to vary in exchange for *n* different points on the waveform. It may now be apparent why the BitScope design has provision to measure the frequency of any signal presented to the ADC.

Even if you can't measure the frequency of a subsampled waveform directly, all is not lost. DSP engineers have some fancy autocorrelation algorithms that can be let loose on a chunk of acquired data to pull a waveform out of meaningless numbers. It is important to note, however, that for resolving single event (such as high-frequency pulses like logic glitches), there is only one solution: oversample by at least a factor of 10. This performance is exclusively in the domain of specialized test equipment using state-of-the-art circuit techniques to resolve samples to 1 ns or better.

tions. In this case, about 18 medium TTL devices with all their wiring disappear into a 44-pin PLCC device.

Radial PLDs like the Lattice are like eight PALs in a circle surrounding a big breadboard. This architecture favors the tight timing requirements of counters and glue logic.

Mostly, this PLD is a 16-bit shift register and counter with a configurable comparator for triggering. The PIC can load a five-byte configuration word that sets the operation of the chip, after which it may be clocked at full speed.

#### THRU THE LENS MEASURING

The SLR lens-mount system from the photographic world is a great design that has stood the test of time. You start with a camera body with a general-purpose 50-mm lens, and for specialized work, you screw in any of a hundred matching lens types. From fisheye to telescopic, as long as the mounts match, you have a new camera.

I tried to use the same SLR principle in the BitScope design. The device on its own is an extremely useful DSO and logic analyzer, but it is not everything.

The pod connector provides an electronic lens mount for test equipment. Think of the sample RAM in BitScope as a roll of 35-mm film, and the data you store there may come from either built-in connectors or any weird and Figure 2d—The BitScope analog capture features the vertical channel muxes, attenuation switch, ADC buffer, and ADC.

wonderful "data lens" you care to attach via the data pod. Because the pod architecture and protocol is open and documented, anyone may design a specialized data lens for BitScope.

#### VOLTAGE RANGES

The BitScope DSO includes four internal attenuation ranges and four channel inputs. Channel A and B are BNC

connectors that may have ×1 or ×10 probes connected. Channel C and D (pod inputs) have a fixed attenuator, and possibly, there's some extra circuitry in the pod.

Table 1 details the range sensitivities. The ranges aren't nearly as comprehensive as a bench CRO, but it covers

| Range | BNCx1   | BNCx10   | POD      |

|-------|---------|----------|----------|

| 00    | ±130 mV | ±1.30 V  | ±632 mV  |

| 01    | ±600 mV | ±6.00 V  | ±2.90 V  |

| 10    | ±1.20 V | ±12.00 V | ±5.80 V  |

| 11    | ±3.16 V | ±31.60 V | ±15.28 V |

Table 1—Here are the BitScope input ranges for an ADC span of 2 V. Resistor attenuators can be found in the schematic.

those most useful to digital and analog circuits. As well, I intended for the pod connector to deal with unusual or high voltage signals by way of an active pod adapter.

It's also possible to alter the gain of some ranges. Since the ADC output is an eight-bit number that ranges from 00 to FF, the final interface just needs to ratiometrically apply this hex value to the voltage range of each stage.

A little thought reveals that for a digital oscilloscope, volts per division and microseconds per division are quite arbitrary notions. Provided that the signal under consideration is within the ADC range and the sample-buffer size, a display can be of any size and grid spacing. Similarly, the notion of *y* offset

becomes a display function, which has nothing to do with the sample engine.

#### IN YOUR HANDS

With this design, I hope to have presented a low-cost solution to the engineer's needs for sophisticated test equipment. I have heeded the call for more open designs and liberation from the single-platform juggernaut.

In the coming months, I look forward to hearing from any of you who can think of applications for this device that I haven't even dreamed of.

Norman Jackson is principal hardware design engineer for Discrete Time Systems P/L in Sydney, Australia. He designs DSP-based digital audio systems for use in film and TV postproduction. You may reach Norman at normj@ discrete.net.

#### SOFTWARE

The Circuit Cellar Web site has downloadable software listings, technical documents, programmable binaries, and PCB overlays. Information about BitScope is available at www.discrete.net or via bitscope@ discrete.net.

#### SOURCES

#### PIC16F84

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 786-7277 www.microchip.com

#### 1016 PLD

Lattice Semiconductor Corp. (503) 681-0118 Fax: (503) 681-3037 www.latticesemi.com

#### MC10319P ADC

Motorola SPS (800) 521-6274 Fax: (602) 897-5725 www.mot-sps.com

#### Preprogrammed PIC, 1016 PLD,

MC10319P ADC, and PCB Discrete Time Systems +612 9212 3469 Fax: +612 9212 3470 bitscope@discrete.net www.discrete.net

# Simulating Micro-Controlled Systems

### FEATURE ARTICLE

Mike Smith & Jason Wudkevich

When you're short of cash, you're always looking for less expensive ways to build embedded systems. If you're like Mike and Jason, you'll use virtual devices to test and debug your system and its peripherals. re you wanting to use some hardware you don't have (or can't afford)? Many useful embedded-system ideas wither on the vine at the development stage for lack of resources.

Virtual devices, however, provide an avenue to the leading edge in the embedded-system market. They let you test how the embedded system controls all its peripherals, even if every peripheral isn't physically available.

In recent years, at least two tutorials on generating such hardware emulators have appeared—Mike's "Developing a Virtual Hardware Device" (*INK* 64) and an article by Larry Mittag [1].

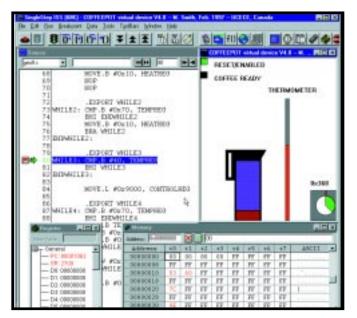

These tutorials produced usable virtual devices. But, the concepts now appear outdated when compared to devices that can be developed with newer commercial virtual-device construction packages like the microprocessor simulators and debugging environments from Software Development Systems (SDS).

SDS's GUI packages can be used to debug embedded systems based on the PowerPC and 68k processor families. ColdFire 5102 and Z80 processor support is present on the most recent release (V.7.11).

The Single Step Peripheral API development diskette option in SDS's

full 68k development system enables a software engineer to quickly create realistic and sophisticated virtual devices. The sophistication available is easiest to demonstrate using an SDS UART virtual device which can be controlled as a peripheral from within any SDS microprocessor simulator.

The lowest two levels of virtual devices that can be generated with the Peripheral API interface roughly correspond to the capabilities of the virtual devices developed by Smith and Mittag [1].

Basic read and write operations change the values of the virtual UART registers. Information from a file or a keyboard dynamically changes the device registers to represent the UART's interaction with the outside world. Writing to a virtual UART register places the transmitted characters into a GUI window or file.

The API's third sophistication level enables simulation of time-dependent hardware register changes in a straightforward fashion not possible with the Smith and Mittag approaches. You can use a time specification file to produce UART-driven interrupts and update registers (e.g., timer registers) on-the-fly.

We particularly liked the Peripheral API system's ability to handle the fourth level of virtual-device sophistication.

Imagine running an SDS processor simulation on a PC. At the flick of a software switch, the virtual UART takes control of the PC's UART to send information into the real world from within the simulation. You can emulate communication with a networked embedded system or control a physical device over a real serial interface.

All the functionality required to produce a sophisticated virtual device is in the C++ classes provided with the SDS Peripheral Interface. So, why are we writing this article?

Unfortunately, this clever development interface is poorly documented. And to complicate matters, there was a hidden defect in the concepts for developing virtual devices using the approaches of both Smith and Mittag which makes it difficult to transfer the knowledge gained from building these devices into constructing an SDS virtual device.

#### DEVICE CONCEPT

Suppose you see a market for the McVASH—a microprocessor-controlled, voiceactivated shower head. It synchronizes the water pulse rate to the voice of a person singing in the shower and even offers a prerecorded beat of solemn music stored in EEPROM for those Monday morning blues.

For safety, the microprocessor is solar powered and communicates to the shower head over an IR link driven from a serial port. A small water impeller provides power for the shower head.

Before seeking venture capital, you want to get a feel for the associated software size and required hardware control. A virtual device seems to fit the bill.

Table 1 shows a simplified programmer's model of the hardware registers. To make the problem a little more realistic, not all the registers have the same byte size. Offsets from the base address (0x20000) are given.

#### **OPERATIONAL DEMONSTRATION**

This virtual device should simulate the operations expressed by the pseudocode in Listing 1. In the code, the device is reset, and the waterstream turns on and off in synchrony with the peaks and valleys of the notes in the bather's voice.

Most embedded-processor development environments on the market can directly debug code using information from the original C source file. So, you may be tempted to build a virtual device using a direct C-code approach.

| Register                     | Size            | Offset from<br>Base Address | Action                                                                                                                       |

|------------------------------|-----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Water Valve Control<br>Timer | 8 bit<br>32 bit | 0x00<br>0x04                | Turns waterstream on and off<br>Indicates number of milliseconds since system startup                                        |

| Period                       | 16 bit          | 0x08                        | Gives period of bather's current vocal rendition                                                                             |

| Infrared Receive             | 8 bit           | 0x0C                        | Permits communication between solar-powered<br>microprocessor (on bathroom window) and<br>water-impeller-powered shower head |

| Infrared Transmit            | 8 bit           | 0x10                        | (Same)                                                                                                                       |

| Shampoo                      | 8 bit           | 0x14                        | Puts shampoo and conditioner into waterstream at the<br>command of voice-recognition circuit (patent pending)                |

| DSP 1                        | 32 bit          | 0x18                        | Example of available DSP register                                                                                            |

| DSP 2                        | 32 bit          | 0x1C                        | Example of available DSP register                                                                                            |

Table 1—The McVASH device registers offer a wide range of functionality and bit sizes.

Listing 2a illustrates this approach for function ResetMcVASH() which initializes the virtual device's 8- and 32-bit registers. We represent the virtual device registers using the array device\_reg[].

All read and write operations are handled via #define statements. This technique is more natural than directly manipulating device\_reg[].

But, this approach only simulates the most basic reads and writes. For example, problems occur with simulating a simple while loop. This loop never exits since TIMER\_REGISTER never changes! These operations must be translated by the tester as in Listing 2b.

#### ADDING SOPHISTICATION

Listing 3 shows a more sophisticated virtual device that handles time-dependent register operations with a realistic addressing mode. With the peripheral access function—paccess()—this virtual device can differentiate between memory-mapped accesses to itself or to other system devices.

Managing the required time-dependent register changes (e.g., incrementing TIMER\_REG) as part of paccess() is straightforward. The different sizes of

Listing 1—This pseudocode for the McVASH device demonstrates initializing the device registers and controlling the water flow according to period of the note being sung.

memory operations (byte, word, and long word) are also handled in a manner reflecting the real device registers' structure.

Such an implementation works with any processor—simulated or real—and any debugging system that handles C code. Changing the #define statements into macros that place parameters on the stack before calling subroutines lets the virtual device be manipulated directly from assembly-language code.

This simple approach is usable with code running on an evaluation board or in a processor simulator, providing a device with the sophistication level of the Mittag virtual device [1].

However, the programmer is still open to many fundamental errors if the simulation code has significant length. How long before the developer attempts to access the virtual-device registers using the same format as any other C variable (e.g., \*device\_reg = value) when a contrived form (e.g., WriteByte(device\_reg,value)) is needed?

A successful simulation implies that accessing any virtual-device register should occur transparently!

#### VIRTUAL-DEVICE COMPLEXITY

Minimal virtual-device sophistication should let us code the use of the device directly in C. Direct manipulation of the virtual device in assembly code should also be possible—at least at the level of the 68k section in Listing 4.

This higher level of sophistication is available with the Smith virtual device, which runs by producing exceptions produced when the processor accesses the virtual-device registers.

#### **REGISTER ACCESSES**

It's necessary for the processor, rather than the programmer, to recognize that virtual-device register accesses are occurring.

Table 2 shows a simplified (but typical) memory map for an embedded processor system running in real life or from within a simulation. Some address ranges are associated with physical memory chips, while others aren't.

Memory accesses to the RAM associated with the user program and variable space (0x30000–0x3FFFF) are handled properly by the processor. But, memory accesses in the 0x20000– 0x2FFFF range attempt to read nonexistent memory locations, triggering a BUS ERROR exception and a jump to the system exception handler.

You can use this exception-handling capability to create a more sophisticated virtual device that manages standard coding practices in a userfriendly way. The new virtual device captures all BUS ERRORs produced by memory access in the 0x20000–0x2001F range. **Listing 2a**—The ResetMcVASH() function is simulated with an unsophisticated virtual device. However, even the simplest while loop (**b**) from Listing 1 will fail.

```

a)

// Array to represent device registers

long int device_reg[8];

#define WATER_REG 0

// Pointers to device registers

#define TIMER_REG 1

// Functions handle op on registers

#define ReadByte(reg_name) {device_reg[reg_name] & 0xFF}

#define WriteByte(reg_name, value) {device_reg[reg_name] = value&0xFF}

#define ReadLong(reg_name){device_reg[reg_name]}

#define WriteLong(reg_name, value){device_reg[reg_name] = value}

void ResetMcVASH(void)

// Reset device registers

WriteByte(WATER_REG, 0); // *water_reg = 0;

WriteLong(TIMER_REG, 0); // *timer_reg = 0;

}

b)

while (initial_time + ReadWord(VOICE_REGISTER) >

ReadLong(TIMER_REGISTER))

WriteLong(TRANSMIT_REG, ON);

```

In *INK* 64, Mike explains how a virtual device can run on RISC (AMD 29200) and CISC (Motorola 68332) microcontroller evaluation boards. Obviously, such implementations require detailed processor-dependent knowledge, but Listing 5 captures the main concepts.

#### **RISC VS. CISC**

Developing a sophisticated virtual device using the bus-exception approach is straightforward for the simple load/ store architecture of a RISC processor (e.g., the AMD 29k family). Values needed during exception handling

Photo 1—Water levels, water and heater temperature, and an elapsed time clock are all animated. It was no small feat to develop a virtual device with this level of animation.

were available from dedicated registers rather than stored on an external memory stack.

The regular format of the 29k RISC instructions, together with special "indirect register" registers, enabled simple recognition of the source and destination registers involved in the virtual-device operation. We generated virtual devices that ran directly on the AMD evaluation boards and within AMD debugging simulators [2].

Generating a virtual device for a CISC processor (e.g., Motorola 68k) using the bus-exception approach was more problematic. One major difficulty was the different stack frames for BUS ERROR exceptions across a processor family (compare those from the Motorola 68332 and 68020 processors) and for a given processor (e.g., Motorola 68020).

Also, some processors move onto the next instruction after an exception is handled. Others expect the addresses on the stack frame and data values to be corrected so the instruction execution can continue on return from the exception.

Such complexity means several BUS ERROR exceptions can be triggered in one instruction. An example is the 68k instruction MOVE.L OFFSET1(A0), OFFSET2(A0).

Other problems arise with any processor pipeline occurring when the exception is forced. Take the following instructions: MOVE.L DO, OFFSET1(AO) MOVEQ.L #5, DO

The second instruction will have completed loading register D0 before the processor handles the BUS ERROR associated with storing the original D0 register value from the first instruction.

In theory, these different cases must be handled in the virtual-device code. In principle, you must construct a complete CISC-processor simulator as part of the exception handler. But in practice, the situation wasn't too problematic for virtual-device write operations.

Most C compilers don't produce a wide range of instructions when accessing a fixed memory location that may represent the absolute address associated with a peripheral. Since such instructions aren't produced by the compiler, you don't need a virtual device that handles them.

By contrast, even the simplest CISC reads on the virtual device proved troublesome. Without significant decoding, it's hard to determine the instruction's destination register.

Despite this fact, we developed some useful virtual devices that only respond to reads sending values to one specific register, as in:

MOVE.L (address\_reg), DO MOVE.L OFFSET(address\_reg), DO

Of course, this approach works if you write assembler code where you can specify the D0 register. Surprisingly, it also typically works with automated code generation since typical C compilers reuse D0 as a temporary or volatile register.

#### **EXCEPTION-HANDLER PROBLEMS**

The exception-handling approach to virtual-device development works user-transparently. We've produced several virtual devices that work with Motorola 68020 and 68322 CISC processors running in the SDS simulation and on evaluation boards.

However, some serious problems remain. For one, you need to develop different virtual-device code for each processor your company plans to use.

Also given how time-dependent register operations are implemented, no register changes occur unless the device is being accessed by the programmer's code. So, it's difficult to ensure that the timing of device operations has a proper relationship to the processor clock.

It's also hard to debug virtual devices unless you know where the array representing device-register values is located. Direct access to the "physical" device-register locations doesn't work because many debuggers modify the processor's exception handling, blocking virtual-device operation.

Complicating the issue is the fact that some processor simulators don't properly handle all processor exceptions. The appropriate exception stack frame is constructed, but you can't recover from the interrupted instruction. So, operation becomes more complicated because you need to modify the stack frame to represent an exception handled by the debugging environment.

Finally, an unsophisticated virtual device can't simulate real-time operations. An instruction that should interact with the real peripheral over

| Listing 3—A more sophisticated virtual device can handle memory-mapped I/O and time-dependent register operations in a realistic manner.                                                                                                                                                                                                                |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <pre>char device_reg[32];</pre>                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| <pre>long int paccess(long address, long data, short operation, short</pre>                                                                                                                                                                                                                                                                             |  |  |  |  |

| <pre>else {     accessed = address - BASE_ADDRESS;     if (operation = = READ)         switch(data_size) {             case BYTE: value = device_reg[accessed]; break;             case WORD: value = device_reg[accessed];             value = (value * 0x100) + device_reg[accessed +1]; break;             }     else if (operation = = WRITE)</pre> |  |  |  |  |

| <pre> Handle_Time_Dependent_Register_Operations(); return(value);</pre>                                                                                                                                                                                                                                                                                 |  |  |  |  |

| }<br>} // Return reg value as required                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| <pre>void Handle_Time_Dependent_Register_Operations(void) {     device_register[TIMER_REGISTER - BASE_ADDRESS]++;</pre>                                                                                                                                                                                                                                 |  |  |  |  |

| // Increment device TIMER_REGISTER                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

several processor clock cycles takes several *thousand* cycles due to the exception-handler code needed to cause the virtual device to function.

#### DLL VIRTUAL DEVICE ADVANTAGES

These problems pale in comparison with the fact that you can never be completely sure that you, or the compiler, haven't used processor instructions your virtual device can't handle. This snag becomes more likely as the project code size and optimization level increase.

A virtual device generated using the SDS Peripheral API offers a good solution. This device takes the form of a DLL, so one virtual device can be used in conjunction with simulators from any processor family.

The DLL acts in conjunction with the SDS processor simulation rather than being parachuted on top of it. So, access to the device registers occurs user-transparently.

Time-dependent operations, including complex concepts like triggering the virtual-device interrupts at specific times, are easily linked to the processor clock because the DLL becomes part of the processor simulation.

Since operations on the virtualdevice registers are handled identically to other memory operations, any instruction sequence the compiler can generate from your product code is guaranteed to work.

The virtual-device DLL is developed using C++ peripheral classes provided by SDS. Through the DLL interface, the virtual device can access any physical peripheral belonging to the PC the simulation is running on.

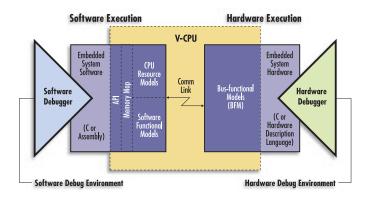

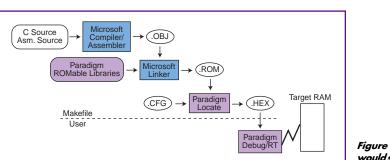

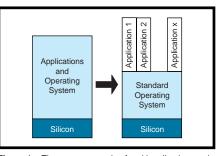

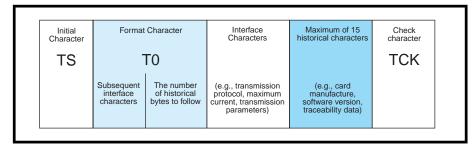

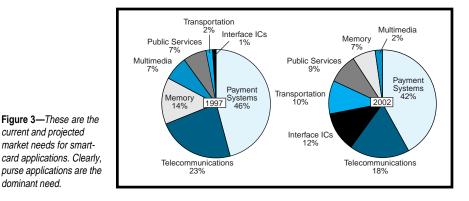

A UART virtual-device demonstration illustrates the power of this DLL approach. Connect the UART to the processor simulation at memory location 0x20000 by adding mem 0x20000 periph=c:\sds\periph\xuart.dll to the simulation start-up file.