# COMPUTER APPLICATIONS JOURNAL #98 SEPTEMBER 1998

# **EMBEDDED APPLICATIONS**

Data Acquisition Goes Ballistic– Recording Rocket Acceleration

Audio Spectrum Analyzer

MicroMonitor Your Car's Performance

DeviceNet— Fundamental FAQs

> \$3.95 U.S. \$4.95 Canada

# TASK MANAGER

# **The Final Rendition**

ike any kid, when I studied music, I had my favorite pieces and those I practiced so many times that the rest of the family had strains of "Happy Birthday" or "Three Blind Mice" intermingling with recipe ingredients, calculus assignments, crop-rotation decisions, and so on. My mother, an accomplished pianist and organist for

one of the larger congregations in the nearby city, however, knew the real secret to success, "Janice, let's hear your scales." She was equally fond of those inane Hannon exercises, not to mention arpeggios, triads, chords, harmony, history, etc. She had quite a list.

Surprise, surprise, with time, a little patience, and some good oldfashioned parental supervision, I actually got to be not too bad at churning out a little Bach, Chopin, Kabalevsky, and many Hannon exercises. In preparation for my last music exam, I had pushed my way up to five hours of practice a day (now there's a new definition of tedium, eh?!).

Probably the most nerve-racking experience was preparing for recitals. In a sense, exams weren't quite so bad. Yeah, you could fail and spend several more months repreparing. But, a recital happened once a year, in front of many people, people you knew...you flub up then, that's it!

In the weeks before a recital, I protected my fingers—no knives, no door jams, no volleyball. As a result, I would arrive at my recital with my hands intact, but really it did no good. At that point, nerves would strike. My hands would be so cold that I could barely move them and they'd sweat so profusely that I'd lose my grip and slip all over the keys.

I suppose the final product sounded good, but it was always a hairraising experience. I finished the concert, people congratulated me, but I was still in some kind of echo-chamber reality. So worn out from the rigors of preparation and recital that everything sounded a little hollow and undone.

As I talk to engineers, it seems to me that embedded applications is just about the same. There are all those years of engineering studies, then the first few years of getting your feet wet in some lackey first-time job, and then design, development, debugging, testing, and production. After a product is on the market and ready to sell, many company owners have that same exhausted, hollow look that I had following each recital. One part of them can't believe they actually got it finished, while another is deathly afraid that someone, somewhere will find that fatal timing error in the seventh measure, or perhaps I should say, module.

And, in many ways, the final product—the concert, the invention—is the crowning glory. It shows how well you learned all the bits and pieces that go into the final product. You know, how well you learned your scales.

This month's feature articles are real concert winners. Tom Consi and Jim Bales, researchers at MIT, launch the issue with a look at acquiring acceleration data from rockets. Robert Lacoste, the first-place winner for the PIC17XXX family in Design98, then unveils his audio spectrum analyzer. And, Robert Priestley is back with a car performance monitor—just what you need for your next high-speed, high-tech car rally.

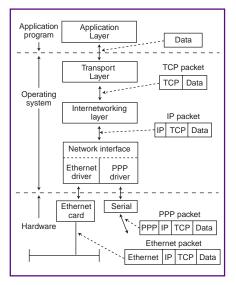

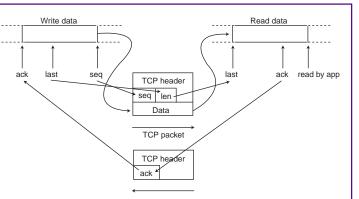

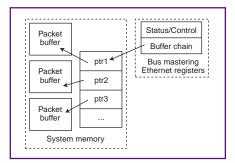

In *EPC*, Jim Brady introduces us to DeviceNet, a new automation network, while Ingo checks out what we need to know about TCP/IP to design real-time applications, and Fred shows us how to solve RF problems, even if we're not RF experts.

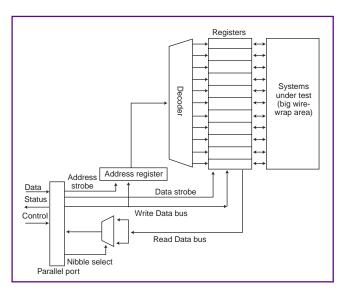

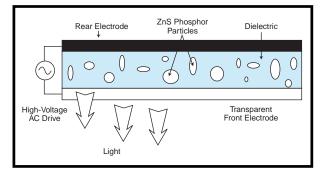

Stuart Ball wraps up his two-part MicroSeries on building a PROM programmer, Jeff pokes about in the nether-world of phosphorus, while Tom tells us about his latest and greatest finds at Sensors Expo.

All in all, it's a high-quality recital from engineers determined to keep delivering what they're the best at. I, on the other hand, having completed my last piano exam, changed from music to English, moved from that campus and haven't lived with a piano since. Now when I play, my ears know what to expect, but my fingers can no longer deliver. My many years of training are now put to work picking out fine compositions and recordings.

janice.hughes@circuitcellar.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Janice Hughes

SENIOR TECHNICAL EDITOR Elizabeth Laurençot

TECHNICAL EDITOR Michael Palumbo

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ken Davidson Fred Eady

NEW PRODUCTS EDITOR Harv Weiner ASSOCIATE PUBLISHER Sue (Hodge) Skolnick

CIRCULATION MANAGER Rose Mansella

> BUSINESS MANAGER Jeannette Walters

> > ART DIRECTOR KC Zienka

ENGINEERING STAFF Jeff Bachiochi

PRODUCTION STAFF Phil Champagne John Gorsky James Soussounis

### EDITORIAL ADVISORY BOARD Ingo Cyliax Norman Jackson

David Prutchi

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

# ADVERTISING

ADVERTISING SALES REPRESENTATIVE Bobbi Yush Fax: (860 (860) 872-3064 E-mail: b

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster (860) 875-2199

Fax: (860) 871-0411 E-mail: val.luster@circuitcellar.com

## CONTACTING CIRCUIT CELLAR INK

SUBSCRIPTIONS: INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199

TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION: TELEPHONE: (860) 875-2199 FAX: ((

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066 THOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

CIRCUIT CELLAR INK<sup>®</sup>, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$88. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar INK<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK<sup>®</sup> disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK<sup>®</sup>.

Entire contents copyright © 1998 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# **READER I/O**

# **BEFORE YOU SPEAK, WE LISTEN**

I enjoy the articles on RTOSs, but I'm surprised that Ingo hasn't mentioned RealTime Linux. RT-Linux offers sub-100-ms real-time response, Posix soft-realtime tasks, a tremendous development environment with free compilers, RTOS, and debuggers, and remote logging, monitoring, and debugging via a PPP link.

# James Linder

jam@woozle.dialix.oz.au

Keep an eye out for upcoming articles on Linux in Embedded PC, especially in Real-Time PC, where Ingo will be presenting a series of applications using RT-Linux.

# WITH JUST A LITTLE MORE HARDWARE...

Thanks for Dan Cross-Cole's article about turning your PC into a multichannel analyzer ("Using a PC for Radiation Detection," *INK* 96). The calculations to determine the percentage of radon in a poured concrete basement were enlightening. Working from counts to U-235 to U-238 to radon to concentrations to flow rates to a muffin fan is a lot more interesting than sending a canister off to be measured by a lab.

However, a couple of significant calibration issues weren't addressed because there wasn't enough hardware applied to the project.

First, any pulse amplitude spectra measured by the analyzer will be biased toward higher energy pulses. The sample-and-hold circuit is really a peak-hold circuit, so what's measured is the largest pulse that has occurred since the circuit was reset. This wouldn't be a problem if all the pulses were from the 185-keV gamma emission of U-235, but as Dan notes, higher energy pulses come from the decay chain of U-238. For example, Bismuth 214 emits 609 keV, 1120 keV, and 1764 keV gammas. These pulses mask many of the gammas produced by U-235.

The second issue—dead time—relates to the amount of time the analyzer is unable to detect a pulse and the average number of pulses per second. For example, if the C++ program portdata takes 10  $\mu$ s to acquire and store a pulse in its array and the radioactive source is producing 6000 pulses per second, the analyzer is dead for 6000  $\times$  0.0000010 = 0.06 s per second, so 6% of the pulses are lost. As Dan demonstrates, this dead time can be compensated for by calibrating the analyzer with a radioactive source of a known activity.

This only works if the multichannel analyzer PC does nothing else. Anything that increases the amount

of time portdata takes to handle the data (e.g., interrupts) substantially changes the dead-time and, consequently, the measured pulse rate. In other words, don't expect good results if you run this task on Windows NT.

Minimize the first issue by using a gated peak-hold where the gate is turned off shortly after a pulse is detected. The second issue can be handled by using the pulse detector to generate an interrupt and a timer to track the amount of time between pulse detection and ISR data collection.

Stephen Lloyd slick@lanl.gov

# **MICROCHIP TAKES ON MOTOROLA**

Tom Cantrell's hint of a looming 8-bit OTP MCU war in "The Micro Price is Right" (*INK* 96) was on target. Three weeks after Motorola introduced the 49¢ 8-bit MCU, Microchip Technology fired back with an 8-bit MCU priced at 40¢ for a ROM and 49¢ for an OTP in large quantities.

The PIC16C505 OTP microcontroller provides design engineers with a higher value solution by offering  $1024 \times$ 12 words of program memory, 2:1 code compaction over competitive solutions,  $72 \times 8$  bytes of user RAM, 12 I/O pins with 25-mA sink and source capability, wakeup on I/O change, and 4-MHz internal clock oscillator.

According to Dataquest, Microchip now ranks number two in worldwide 8-bit MCU shipments—thanks largely to *INK* readers. In turn, these leading designers can rest assured that Microchip will respond to future industry battle cries and deliver the most appropriate 8-bit MCUs for their design needs.

# Eric Sells

eric.sells@microchip.com

# BACK TO SCHOOL

I was struck at how well thought out Ken's recent editorial was ("A Mind is a Terrible Thing...," *INK* 95). It gives good tips and directions for helping students.

This past year, I was very pleased to have directed my focus on one agent useful towards lymphoma. This small success reminded me to set my goals carefully, and I am happy to incorporate your method for reaching students.

# Marc McGary

mcgama8@elwha.evergreen.edu

USB JOYSTICK CONTROLLER The FT8U24AM USB Game-Port Joystick Controller IC incorporates a four-channel ratiometric measuring circuit for determining the position of the analog controls. Traditional low-cost analog joysticks track position with an RC time constant, using low-tolerance compo-

# **Edited by Harv Weiner**

nents (i.e., a potentiometer and a capacitor). Resulting threshold values vary with temperature and voltage, producing inaccurate joysticks that need frequent recalibration. Digital joysticks use optical sensors and electronics to eliminate these inaccuracies, but they can be more expensive.

The FT8U24AM measures the angle of the potentiometer rather than its resistance to eliminate the tolerance effect and provide a typical accuracy of  $\pm 1\%$ . It features an integral EMCU microcontroller with preprogrammed mask ROM, 128-byte data memory and 12 I/O pins. The four ratiometric analog channels measure *x* and *y* movements as well as throttle and rudder functions. The IC supports a wide range of configurations with up to four analog controls, four stick and four base buttons, as well as support for a POV hat switch. The IC is packaged in a 24-pin PDIP.

The FT8U24AM sells for less than **\$2** in quantity.

Saelig Co. (716) 425-3753 Fax: (716) 425-3835 www.saelig.com

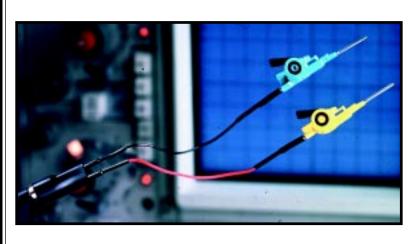

# **OSCILLOSCOPE PROBE ADAPTER**

The **MicroGripper Oscilloscope Kits** from Emulation Technology provide easy probing of fine-pitched devices. They are uniquely designed to provide testing of PQFP and SOIC packages from 0.8- to 0.3-mm lead pitch. Combined with a dual-lead adapter, the MicroGripper enables hands-free testing. The devices work with all popular oscilloscope probes. The MicroGripper tip is insulated to prevent shorting out when attached side-by-side and features a wire-tip diameter of 0.08 mm. It is constructed of steel or stainless steel wire, nickel plated with an ABS plastic finish. It is rated at 500 WVDC. The kit is intended for use with voltages up to  $\pm 40$  V. The probe capacitance is less than 2 pF between adjacent grippers and its inductance is

> less than 1 mH (both measured at 1 kHz). The 3-dB bandwidth is greater than 100 MHz.

Three separate kits are available, depending on the lead pitch. Each kit contains parts for use with two probes, including four MicroGrippers and two dual-lead adapters.

Pricing ranges from \$145 to \$199.

Emulation Technology, Inc. (800) ADAPTER (408) 982-0660 Fax: (408) 982-0664 www.emulation.com

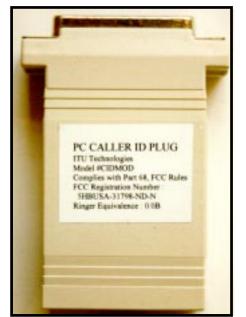

# CALLER-ID PLUG FOR PC

The **PC Caller ID** plug decodes caller-ID data sent over a telephone line and delivers the name, number, date, and time to a computer. Enhanced services, like voice-mail notification and caller ID with call waiting, are also supported. The PC Caller ID Plug, which measures only  $2.25'' \times 3''$ , plugs directly into any spare PC serial port and requires no external power.

Included software (with source code) enables the user to transform a PC into an advanced caller-ID box and to integrate caller ID into other applications. The software has DOS- and Windows-based programs. Windows software source code is supplied in Visual Basic, and DOS software source code is supplied in C. The Windows software supports Windows 3.11, 95, 98, and NT.

The unit is FCC Part 68 certified and can supply caller-ID information to microcontrollers, SBCs, and other embedded systems. Full documentation, including the data format and a schematic diagram for interfacing to other hardware, is included.

The ITU PC Caller ID Plug is available for **\$34.95**. A 30-day money-back guarantee and a 90-day warranty are supplied with each unit.

ITU Technologies (888) 448-8832 • (513) 661-7523 Fax: (513) 661-7534 • www.itutech.com

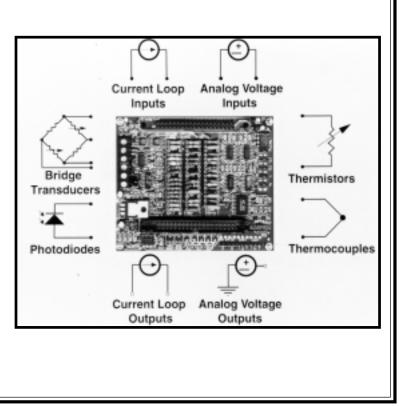

# ANALOG SIGNAL CONDITIONING BOARD

The **QED Analog Conditioning Board** enables direct monitoring and control of 16 analog inputs and 8 analog outputs from thermocouples, RTDs, strain gauges, pressure sensors, photodiodes, bridge sensors, analog actuators, and 4– 20-mA transmitters. Onboard amplification, attenuation, and filtering can be easily customized with plug-in components to provide flexible signal conditioning. Analog outputs range from 0 to 10 V.

Typically controlled via a direct cable interface to the C-programmable QED board controller, the QED Analog Conditioning Board also features built-in thermocouple cold-junction compensation to simplify temperature measurement and control.

The QED Analog Conditioning Board sells for **\$249**.

Mosaic Industries, Inc. (510) 790-1255 • Fax: (510) 790-0925 www.mosaic-industries.com

# FEATURES12Smart Rockets24PIC'Spectrum62Automotive Travel<br/>Computer

# Smart Rockets

# FEATURE ARTICLE

Tom Consi & Jim Bales

# Data Acquisition in Model Rocketry

Model rockets have always served as ideal vehicles for teaching physics and engineering basics. With this new dataacquisition device, Tom and Jim show how to trace the rocket's acceleration and store the entire flight and its data. odel rockets have inspired generations of students to pursue careers in

engineering and science. Indeed, many of you probably went through a rocket phase in your formative years.

Model rockets are popular with aspiring engineers for good reason. They're exciting, they're fun to build and launch, and they offer a number of significant engineering challenges that can be tackled with simple tools and small budgets.

From an educational perspective, model rockets introduce a number of fundamental concepts in physics such as Newton's laws, lift, and drag. Inexpensive microcontrollers and solid-state sensors add an exciting new dimension to model rocketry.

It's now possible to build tiny devices that can measure and record the performance of a model rocket in flight. This article describes just such a device that we designed, built, and flew as part of our "Smart Rockets" seminar at MIT.

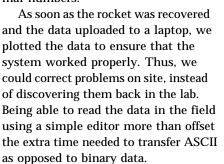

Our system measures just one flight characteristic—acceleration—although it could be easily modified to measure other aspects of a rocket's flight. We designed the system to fly in a small, single-staged, model rocket that could be launched in a relatively small area. The entire system, including battery, is 4¼" long, slightly under an inch wide, and weighs about 1 oz. (32 g). Photo 1 shows a picture of the system mounted in the rocket.

Inside the payload compartment is a small circuit board that contains an acceleration sensor, power supply, microcontroller, and nonvolatile memory chip. A pair of leads brought out of the payload run down to the tips of two fins and touch corresponding contacts on the launch pad. The launchpad contacts attach to a cable that leads to the launch control box.

When the launch button on the control box is pressed, two things happen. First, the leads brought out to the fins are shorted together, triggering the data-acquisition system. Second (and electrically isolated from the first), a current passes through the igniter, starting the rocket's engine and setting the vehicle into flight.

# INTRODUCTION TO MODEL ROCKETRY

Model rockets are lightweight, lowcost, solid-fuel rockets designed to permit safe experimentation with the principles of rocketry. Factory-made, single-use, solid-fuel engines are a key feature in model-rocket safety.

A model-rocket engine consists of, from bottom to top, a nozzle, propellant, delay charge, ejection charge, and an end cap. This design governs the overall flight characteristics of the model.

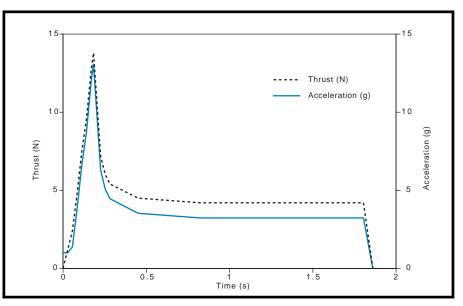

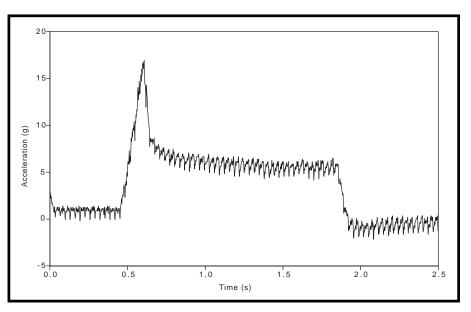

The acceleration phase (i.e., when the propellant burns) lasts from a fraction of a second to up to 2 s for typical rocket engines (see Figure 1). It is followed by a longer (several seconds) tracking phase when the rocket coasts up to maximum altitude. The model is not powered during this phase, as the delay charge that generates smoke for visibility has negligible thrust.

At the end of the tracking phase, the ejection charge ignites at the peak altitude, when the velocity of the rocket is near zero. The ejection charge blows forward, bursting the end cap, and pressurizing the interior of the model, which pushes the nose cone/payload section out of the rocket body.

Both pieces, connected by an elastic shock cord, then drift safely back to

**Figure 1**—This graph shows the predicted performance of the rocket. The thrust data was extracted from a performance curve of the Estes C6-5 engine provided by the National Association of Rocketry. The acceleration curve for the rocket is calculated. Note that at t = 0, the system experiences Earth's gravity, which is equivalent to a rocket accelerating upward at 1 g in free space.

earth via a parachute. During this recovery phase, the rocket is at the mercy of the wind which can blow it onto rooftops, into trees or power lines, or, in our case, dump the model in the middle of the Charles River! If all goes well, however, the rocket is recovered, the engine is replaced, and the model can be flown again.

Model-rocket engines are designated by a letter and two numbers. The letter indicates the total impulse of the engine, which is just the integral of the thrust versus time curve of the engine (the dashed line in Figure 1).

We used A-, B-, and C-sized engines with total impulses of 2.5, 5, and 10 N, respectively. The first number of the engine designation is the average thrust in newtons, and the second number is the period of the tracking phase in seconds.

Our rocket—the Estes Nova Payloader—is a typical single-stage model rocket. It's about 21" long, 1" in diameter, and weighs 1.8 oz. (50 g) without a payload or engine.

The rocket consists of a paper tube, balsa wood fins, and a 4¾"-long plastic payload section topped by a nose cone. The wood and paper parts are assembled with wood glue, and the plastic parts with model cement. The rocket body and the nose cone/payload section are connected by an elastic rubber shock cord, which attaches to the 12" diameter parachute.

Prior to launch, an engine is inserted into the rear of the rocket and held in place with a spring clip. A piece of recovery wadding (fireproof tissue) is placed in the rocket body just forward of the engine to protect the plastic parachute and shock cord from hot gasses during ejection.

Next, the parachute and shock cord are coiled up and inserted into the rocket. The nose cone/payload section is inserted into the forward end of the body, and the model is placed on the launch pad, ready for flight.

Our launch platform—an Estes Porta-Pad II—consists of a plastic tripod, a steel blast deflector, and a meter-long launch rod. The rocket has a small tube attached to its side, the launching lug, that holds the model to the launch rod during the initial phase of powered flight.

Model-rocket engines are fired electrically using an igniter that typically consists of a piece of nichrome wire coated with a flammable material. A current passed through the wire ignites this material, which then ignites the propellant.

The igniter connects to a long pair of wires that lead to the launch control box at a safe distance (~20') from the rocket on the pad. The launch control

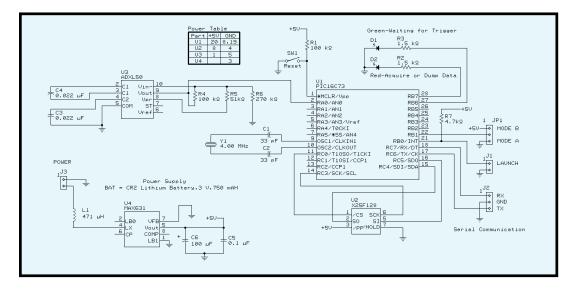

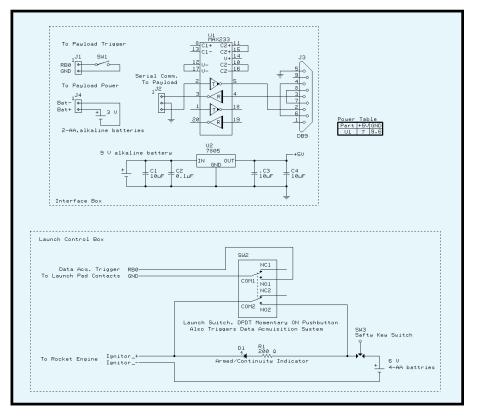

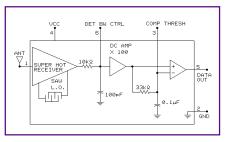

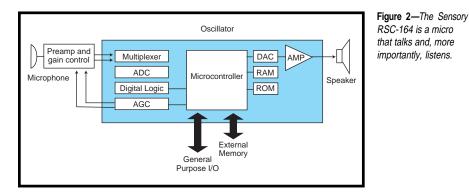

Figure 2—Here's the schematic for the model-rocket dataacquisition system. During the rocket's flight, the PIC16C73 microcontroller reads the ADXL50 accelerometer and stores the data in the X25F128 serial flash memory.

box has a switch (the launch button) that connects the igniter to the 6-V battery (four alkaline AA cells). We discuss the details of the launch control box later.

# **ROCKET SCIENCE 101**

Newton's First Law, F = ma, contains all the physics you need to predict the accelerations that the system will record. All we need is the mass of the rocket (*m*) and the applied force (*F*), right?

The force exerted by a rocket engine is not constant as you see in the thrust versus time curve for an Estes C6-5 engine (the dashed line in Figure 1). We assume the rocket moves straight up while the thrust is applied, so the total force is the engine thrust minus the gravitational force (mg,  $g = 9.8 \text{ m/s}^2$ ).

If the mass of the rocket were fixed, then the acceleration is the dashed line scaled by the mass. However, as the propellant burns, the mass of the rocket decreases.

How important is this effect? For NASA, it's critical—85% of the space shuttle's take-off weight is fuel!

In our case, only 12 g of the 105-g take-off weight is fuel (11%). So, we can treat the rocket mass as a constant, which gives us the expected acceleration curve shown as the solid line in Figure 1.

Our students made this calculation on the first day of class. Their task for the semester was to determine, by direct measurement, if Figure 1 is correct.

# CONTROL AND DATA LOGGING

We chose the Microchip PIC16C73 microcontroller as our data-logging engine (see Figure 2). This chip has all the I/O functions we need: DIO pins, a five-channel eight-bit ADC, a USART, and an SPI synchronous serial port.

Its 4 K words of data space (we used the reprogrammable windowed EPROM version) and 192 bytes of RAM easily accommodate our application code as well as provide some head-room for future expansion.

Size was a key factor in determining what microcontroller to use. The PIC-16C73 comes in a 28-pin skinny-DIP package that fits our space constraints.

The only thing the '16C73 lacks is nonvolatile data storage. This is provided by a Xicor 25F128 serial flashmemory chip that contains 16 KB of memory in an 8-pin DIP package.

The Xicor chip communicates with the '16C73 via the PIC's SPI serial interface. A 4-MHz crystal (Y1) was chosen so each of the PIC instructions executes in 1  $\mu$ s, which is convenient for calculating code-execution times. The reset button (SW1) is a tiny SPST momentary On push button which grounds the MCLR pin of the PIC.

We considered two methods of triggering data collection by the PIC. One is to have the PIC continually read the ADC and use the flash memory as a ring buffer. The PIC waits for the accelerometer output to exceed a threshold and stops writing to the buffer just before completing the next loop around the ring. The drawbacks are the added software complexity (a concern for students just learning PIC programming) and the finite number of write cycles allowed by the flash chip. Also, for the first launch, we would have to set the threshold based on our predicted acceleration curve, a golden opportunity for Murphy to intervene!

Instead, we chose to supply an external electrical signal when the launch switch is pressed. This technique removes all the objections listed above and also provides us with data on the lag between pressing the launch button and the liftoff.

However, it presents a new challenge: how to make a reliable electrical connection that can be broken with very little force. We need this type of connection in two places—between the launch pad and the rocket and between the rocket body and the nose cone/ payload section (which must separate during ejection). Our solution is in the "System Construction" section.

Two digital input pins control the system operation. When grounded, the trigger input (RB0) starts the program running.

On triggering, the program enters one of two modes, determined by the jumper on digital input pin RB1. Mode A (RB1 low) causes the PIC to acquire accelerometer data. In mode B (RB1 high), the PIC immediately dumps its stored data to a host computer though its USART.

As Photo 1 shows, the trigger lines (RB0 and ground) are brought out of

the payload section and down the rocket body to the fin tips where they contact two plates on the launch pad, which are, in turn, connected to the launch control box (see Figure 3). The launch button (SW2) shorts these contacts together, triggering the system to start acquiring data (if it is in mode A).

Green and red status LEDs connect to digital outputs RB6 and RB7, respectively. The green LED indicates that the system is on and waiting for a trigger signal. The red LED means the system is either acquiring data (mode A) or dumping data through its USART (mode B).

Four other digital outputs (RB2–5) were used for debugging purposes.

To get the data onto a PC, we built a small interface box that has a push button to trigger RB0 while in mode B. This interface box contains a MAX-233 TTL to RS-232 level shifting chip that eliminates this chip from the payload's circuit board. The box also has its own battery so the payload's battery isn't drained during retrieval of data (see Figure 3).

# THE ACCELEROMETER

We chose Analog Devices' ADXL50 accelerometer, which requires a regulated +5-VDC supply and has an on-chip amplifier. The gain of this inverting final stage can be set by external resistors, which enables us to trade off range for sensitivity.

We selected the ADXL50's external resistors to condition the sensor output to have a zero-g bias level of about 2.5 V. Since the maximum acceleration is expected to be 14 g, we selected the gain resistors R4–R6 to create an inverting amplifier with a range of  $\pm 20$  g.

An internal voltage reference makes the output insensitive to variations in the supply voltage. The output of the accelerometer connects directly to the PIC's 8-bit ADC (pin RA0), giving a resolution of approximately 0.2 g.

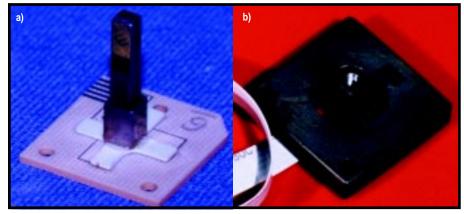

Photo 1a—Here's our smart rocket on the launch pad. Note the clear payload compartment containing the data-acquisition system and the copper contacts beneath the fins. The brown streak down the right side of the rocket is one of the two lines of conductive paint that bring the trigger signal to the payload. **b**—In this view of the data-acquisition system, you see the modifications made to the payload compartment. The brown patch on the rear bulkhead connector is conductive paint that forms a sliding electrical connection with the rocket body. To the left of the circuit board is a model-rocket engine.

One potential source of error is fluctuations in the regulated power supply, which serves as the reference voltage ( $V_{REF}$ ) for the PIC's ADC. A better design would be to use a voltage reference chip for  $V_{REF}$ , although that would, of course, consume precious circuit board space.

Another potential source of error is misalignment of the sensor with respect to the rocket's thrust axis. This error is small: one minus the cosine of the misalignment. So, for a misalignment of  $5^{\circ}$ , the error is less than 0.5%.

# SOFTWARE

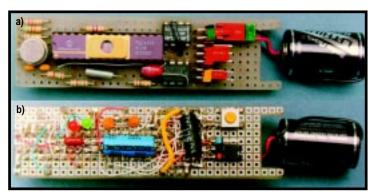

The code was written in PIC assembly language. We used Microchip's MPASM assembler and PICStart 16C programmer as development tools. A block diagram of the software is shown in Figure 4. On powerup or after coming out of a reset, the software initializes the I/O facilities and internal resources of the PIC (DIO, ADC, SPI interface, USART, and Timer 0). The USART operates at 9600 bps, and the SPI clock runs at 1 MHz.

The program then polls RB0, which is normally high. A trigger signal pulls RB0 low and causes the program to check the mode and execute the appropriate code. After the selected mode executes, the program loops back to polling RB0 for another trigger signal (see Figure 4a).

Mode A is the real-time data-acquisition portion of the program. It is entered if pin RB0 is jumpered low. The ADC is read during an interrupt service routine that is governed by Timer 0, which provides an interrupt every millisecond, thus setting the data-acquisition rate (see Figure 4b).

How data is acquired is dictated by the behavior of the Xicor 25F128 serial flashmemory chip. It receives data in 256-bit packets via

its SPI interface and stores it in one 32-byte sector of its flash memory.

Transferring 256 bits takes only about a quarter of a millisecond at an SPI clock rate of 1 MHz. The programming operation, however, takes 10 ms. Fortunately, this occurs automatically after the bits are received and it requires no further intervention of the PIC.

The program in mode A reads the ADC 32 times at a 1-kHz rate, storing these values in 32 bytes of buffer RAM on the PIC chip. Between the thirtysecond and thirty-third A/D conversions, it shoots the contents of the buffer to the Xicor chip through the SPI.

It then proceeds to fill the buffer RAM again. During the 32 ms that the buffer is being refilled, the Xicor chip has plenty of time to write the data it just received into its flash memory. In addition to sending acceleration data, the PIC sends the sector address that indicates where to store the data in the Xicor chip. The sector address is incremented after every SPI transfer.

This cycle repeats itself 256 times until 8 KB of data are stored on the Xicor chip. The program then ends mode A and goes back to polling the trigger pin.

The Xicor chip holds up to 16 KB of data. But, we found that 8 KB of data, corresponding to 8 s of time, was enough to capture a rocket flight from launch to recovery phase.

Triggering the system in mode B presumes that a host computer is connected to the USART of the PIC via the interface box. The PIC reads a single byte from the Xicor chip, converts it to a three-byte ASCII decimal number, and transmits it to the host computer (see Figure 4a).

Each transmitted number is appended with the ASCII codes for carriage return (\$0D) and line feed (\$0A). This cycle repeats itself until all 8 KB of data are transmitted to the host.

Figure 3—In the ground equipment, the interface box connects the payload to a host computer for data transfer. Pressing the ignition switch on the launch control box (SW2) simultaneously ignites the rocket engine and triggers the payload to record data. The user must set the host computer to accept this ASCII stream before the PIC is triggered into mode B. There is no handshaking between the PIC and the host. As with mode A, on termination of mode B, the program loops back to polling the trigger input.

In the field, we used a laptop, running a terminal emulator set in screen-capture mode, as the host computer. The captured file is a 1-column  $\times$  8192-row matrix of ASCII decimal numbers.

Photo 2a—The accelerometer is in the TO-100 can at the forward end of the board. Its axis of sensitivity is along the diameter of the can that crosses the tab. The connectors are for the trigger signal (yellow), serial communication (central three-pin connector), and power (green), which is shown connected to the lithium battery. **b**—The red and green status LEDs, the large black inductor, the mode jumper, and the reset button are visible on the wire side of the board.

# POWER

The power system, consisting of a battery and a voltage regulator, was one of the more difficult portions of the design because it operates under several constraints. First, the battery must source 30 mA at 3 V.

Second, the regulated 5-V rail is critical because it is the reference for the PIC's ADC. Any change in this voltage translates into a proportional error in the recorded acceleration.

Third, the power system must be compact and lightweight because 50 g is the rocket's maximum payload. Finally, it must be reasonably efficient because small batteries have limited energy.

We started by looking at high-energy batteries. The two obvious choices were alkaline cells and lithium primary cells. Lithium cells have, on average, three times

more energy per unit mass than alkaline cells.

We settled on a CR2-style lithium battery designed for high-current applications. It provides 750 mAh at 3 V and weighs 11 g.

We selected Maxim's MAX631A step-up switching regulator because of its low part count (one inductor and two capacitors) and small quiescent current. The selection of the inductor is critical because its resistance must be low (0.5  $\Omega$  or less) and it must not saturate when the current through it peaks. The power supply is shown in Figure 2.

# SYSTEM CONSTRUCTION

The data-acquisition system was point-to-point wired on a  ${}^{15}\!/_{16}$ "  $\times 3\frac{1}{2}$ " piece of pad-per-hole perf board. The PIC chip was mounted in a socket so it could be removed for reprogramming. All other components were soldered directly to the board.

As you see in Photo 2 and Figure 2, three connectors were mounted on the board—two 2-pin connectors to connect to the battery (J3) and to link the trigger lines to the rocket body (J1), and one 3-pin connector for the USART connection (J2).

The big challenge in laying out this board was minimizing the component heights at the edges to accommodate the cylindrical shape of the payload compartment. Thus the PIC chip, accelerometer, and the large capacitor and inductor of the power supply had to be mounted centrally on the board.

We mounted components on both sides of the board, which had the added bonus of balancing the weight of the payload. Photo 2 shows both sides of the payload circuit board.

A slot was cut in the rear end of the plastic nose cone that acts as a guide to hold the circuit board in the payload section (see Photo 1b). Some material was removed from the plastic bulkhead that forms the bottom of the payload compartment to make a crude battery holder.

Pieces of foam wedged between the battery and the wall of the payload compartment help hold everything in place. The forward nose cone and rear bulkhead connector are taped to the payload tube to prevent the electronics from falling out during recovery. We soldered wires onto the terminals of the battery and brought them out to a connector on the circuit board. Beware! This is the most dangerous part of building the system.

There is a lot of energy in the lithium cell, and excessive heat can cause it to catch fire or explode! Use a cell that has integral solder tabs, and don't linger on them with the soldering iron.

One of the more difficult aspects of the design was bringing the trigger lines (RB0 and ground) out of the payload compartment, down the rocket body, and out onto the fin tips. For this we used conductive paint, the kind used to repair windshield defrosters.

An electrical connection was established between the payload compartment and the rocket body by applying two patches of paint on the outside surface of the payload bulkhead connector where it slips into the rocket body, and two corresponding patches of paint inside of the forward end of the body (see Photo 1a).

Conductive lines were painted from these forward patches around the edge of the tube and down the exterior of the rocket to patches of paint at the tips of two of the three fins. These patches contact copper plates on the launch pad that connect to the launch control box (see Photo 1).

The paint patches on the bulkhead connector and the rocket body provide electrical continuity between the payload and the rocket while the model is on the launch pad. This connection is easily broken by the ejection charge.

Figure 4a—Data is acquired by an interrupt-driven routine that runs during the time indicated by the shaded diamond. Note that the code between the points labeled A and B must execute in less than 1 ms to maintain the 1-kHz data-acquisition rate. b—In this flowchart of the interrupt-driven data acquisition routine, timer 0 sets the sampling period. Each time the routine is called, one A/D conversion is performed and the data byte is stored in the RAM buffer.

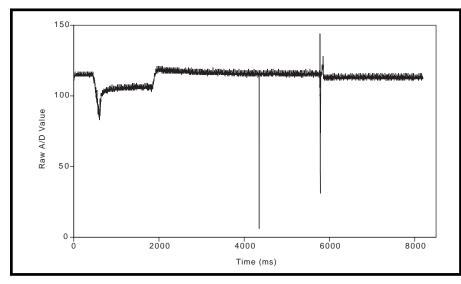

**Figure 5**—Here's the raw data from an actual rocket mission using a C6-5 engine. Because this is the output of an inverting amplifier, upward acceleration causes decreased output voltage. This curve was plotted in the field, and it shows that the system functioned correctly. The spike around 4500 ms is spurious, while the structure just before 6000 ms indicates the ejection charge firing.

Connector J1 brings the trigger lines to the paint patches on the bulkhead connector. It isn't possible to solder wires to the conductive paint, so we essentially pasted the stripped end of each wire to its patch with a thick coating of the conductive paint. Clearly, conductive paint is not going to hold the wire. To provide strain relief, we glued the insulated portion of the wires to the bulkhead connector using model cement. Still, these connections proved quite delicate and sometimes broke in the field.

# LAUNCH CONTROL BOX

The launch control box shown in Figure 3 has many of the features of the standard Estes Electron Beam launch controller. Between the batteries and the nichrome igniter are the safety key and the armed indicator (LED D1). The launch switch is in parallel with the LED.

The igniter is connected with the safety key removed, so the clips to the igniter are not hot. Inserting the safety key applies the battery voltage across the series combination of the armed indicator and the igniter, which enables enough current to flow to light the indicator but not enough to ignite the igniter's black powder coating. A nice feature of this design is that any break in the wiring prevents the armed indicator from lighting.

Our major modification to the Estes design was to replace their SPST launch switch with a DPDT momentary push-button switch (SW2). The second channel of this switch shorts together the two contacts brought out to the fins of the rocket. A 20' fourconductor cable brings the igniter current and the payload-trigger signal to the launch pad.

Three small blocks of wood epoxied to the blast deflector of the launch pad (see Photo 1a) support the rocket, while electrically isolating the fins from the steel blast deflector.

Copper plates are attached to each block of wood, and two of the plates are connected by leads to the trigger signal lines of the launch cable. The two rocket fins with conductive-paint contacts are positioned over these blocks, and the third fin rests on the unconnected block to balance the model on the pad.

# RESULTS

Before leaving the lab, we went through every step in the sequence of the setup, launch (with no engine), data recovery, and data visualization. We even shook the rocket up and down a few times after pressing the launch key, just to generate acceleration data. Once the procedure was perfected, we moved outside.

The raw data from a launch with an Estes C6-5 engine is shown in

Figure 5. The acceleration appears to be negative, but that's because the onchip buffer of the ADXL50 is an inverting amplifier.

The initial kick and the sustained thrust are easily seen, as is the ejection charge (around 6000 ms). There is also a spurious data point (around 4500 ms). While the accelerometer output has not been converted into acceleration yet, this plot still tells us that the system worked.

Turning Figure 5 into the desired acceleration plot requires a few steps:

- removing the spurious data points

- smoothing the curve with a three-

- point sliding-window average

converting the 0–255 A/D readings to 0–5 V

- converting the voltage to acceleration, exploiting the fact that the system saw 1 g just before ignition

The first three steps are straightforward. For the final step, we used the published response curve of the sensor as well as the calculated transfer function for the amplifier, given the values of resistors R4–R6.

We know that, just before ignition, the rocket was experiencing the 1-g gravitational force, so we defined the observed DC offset to be 1 g. Figure 6, shows the final acceleration curve for our system.

Compare Figure 6 to the solid line in Figure 1. The general shape of the curves agree, although the measured curve is compressed in time. The maximum measured acceleration was 17 g, while the maximum acceleration predicted from the mass of the rocket and the characteristics of the C6-5 engine was 14 g.

The correspondence between theory and experiment isn't bad, and it shows our system works as designed. There are several ways to improve the quality of the data.

First is to perform a careful calibration of the accelerometer. Calibration procedures for the ADXL50 are discussed in the datasheet. We calculated gains using the nominal values of our 5% resistors. Using 1% resistors in the accelerometer circuit would give better results.

Figure 6—Here's the processed acceleration data for the launch shown in Figure 5. The shape compares favorably to the predicted acceleration curve in Figure 1.

Also, a more stable voltage source can be used as the reference for the PIC's ADC. Other questions can be addressed as well: What causes the spurious data? What is the source of the ripple seen even when the rocket is on the pad?

# FUTURE DEVELOPMENTS

There are many ways to improve and expand this system. It could be miniaturized further by using a PCB with surface-mount components.

Earlier, we mentioned our decision to use a wire link to the rocket to

trigger the data acquisition as opposed to using a threshold acceleration to trigger the system. Two of our students managed to implement this idea and got it to work quite nicely. Other triggering schemes could use optical or radio signals as wireless triggers.

Also, more sensors could be added. An old model-rocket trick for measuring roll rate is to install a photosensor in the side of the model. As long as the model doesn't fly directly into the sun, there will be asymmetric illumination around the vehicle, causing a periodic signal from the photosensor as the rocket rolls. The PIC could easily measure the frequency of this signal.

A number of other sensors could be added—thermistors, pressure sensors, and even tiny gyroscopes. Another class of sensors consists of devices that indicate when critical events occur during the flight of the model.

For example, a fine wire could be placed across the nozzle of the rocket engine. When the engine ignites, the wire burns through and signals the PIC, which logs the exact time of ignition. You can imagine similar sensors that indicate when the rocket leaves the pad, when it clears the launch rod, and when the ejection charge occurs.

Additional sensor data could easily exceed our system's capacity. Greater memory can be obtained via highcapacity serial flash-memory modules (discussed by Tom Cantrell in "Serial Flash Busts Bit Barrier," *INK* 85).

We've only scratched the surface of the many possibilities for smart model rockets. We hope to explore some of these avenues in another course. This time we were more than satisfied that all of the students got to fly their rockets and collect real data.

This effort was supported by the MIT Sea Grant College Program and the MIT Department of Ocean Engineering. At MIT we were helped by the Undergraduate Seminar Office, The Safety Office, the Campus Police, and the Athletics Department. Analog Devices, Maxim, Microchip, and Xicor all donated ICs for the course. Microchip (through S-J New England Inc.) also provided PIC programmers and databooks. Finally, thanks to our students, whose interest and dedication were inspirational and who were just a lot of fun to be around!

Tom Consi is a research engineer and lecturer in the MIT Ocean Engineering department, where he develops biologically inspired marine robots. He received his Ph.D. in biology from Columbia University in 1987. You may reach him at consi@mit.edu.

Jim Bales is a research engineer with the MIT Sea Grant College Program. He received his Ph.D. in solid-state physics from MIT in 1991. His research interests include sensors for underwater robotics and power systems for autonomous platforms. You may reach him at bales@mit.edu.

# SOFTWARE

Complete source code for this article is available via the Circuit Cellar Web site.

# SOURCES

## ADXL50

Analog Devices, Inc. (617) 329-4700 Fax: (617) 326-8703 www.analog.com

## Model rockets and rocket equipment

Estes Industries 1295 H St. Penrose, CO 81240

# **MAX631**

Maxim Integrated Products (408) 737-7600 www.maxim-ic.com

# PIC16C73

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 786-7277 www.microchip.com

### **Rocket-engine performance curves**

National Assn. of Rocketry P.O. Box 177 Altoona, WI 54720 www.nar.org

### X25F128

Xicor, Inc. (408) 432-8888 Fax: (408) 432-0640 www.xicor.com

# FEATURE ARTICLE

# **PIC'Spectrum**

# Audio Spectrum Analyzer

Sure, a DSP can make the calculations and generate the pixel bitmap for an audio spectrum analyzer, but at what cost? Robert gets the same result from a single PIC processor with a design so good he walked away with a Design98 first prize. remember being quite astonished when one of my professors explained the basics of frequency domain analysis, "Every periodic signal is the sum of pure sinusoidal signals, with given frequencies, amplitudes, and phases."

Hmm...every signal. That includes the light coming from the sun, the vibrations of my old car, even the tears of my two-month-old baby!

And, I bet that 99% of *INK* readers are like me. You want to understand, and you understand it better if you make it yourself.

So, years ago, I quickly wire-wrapped an analog acquisition board and wrote a small BASIC program on my old Apple II to display the frequency decomposition of an incoming audio signal. It was my first audio spectrum analyzer. Later, I did the same on my PCs, and the '*x*86s were soon powerful enough to get real-time performance.

Using a PC is OK, but how about an autonomous device? Something small enough to bring along anywhere but that has a VGA video output with a decent quality image and real-time refreshes.

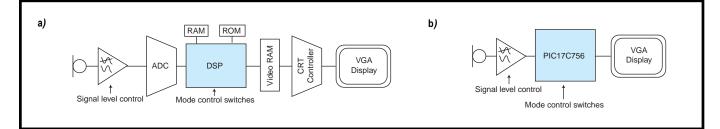

My first idea was something like the block diagram in Figure 1a. An amplifier and low-pass filter suppress out-of-the-band signals before the signal goes to an ADC, which transforms it into numerical samples.

A DSP can calculate the frequency decomposition of this signal with the classic Fast Fourier Transform (FFT) algorithm and generate the pixel bitmap in video RAM, which is displayed by a CRT controller chip.

You'd need a fair amount of computing power, but is it possible to do the same with a simpler design? How about a high-end microcontroller? *INK*'s Design98 contest presented a great opportunity to try it with one of the newer Microchip devices—the PIC17C756.

This chip has enough horsepower not only to do an FFT in real time but also to eliminate the CRT controller. The video output can be made with some general-purpose parallel output lines, and the software toggles the corresponding bits to generate the video synchronization and color signals in real time.

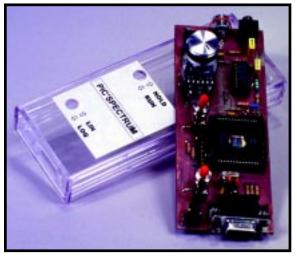

With this controller, the block diagram of my logic analyzer (shown in Figure 1b) is, well, as simple as possible. PIC'Spectrum is born!

# YOU SAY PIC17C756?

Before getting into more details about PIC'Spectrum (see Photo 1), let's have a look at the PIC17C756 and its stripped-down version, the PIC17C752. These new fully static CMOS chips are an enhancement of the existing PIC17C4X family.

The microcontroller core runs up to 33 MHz, giving a 121-ns instruction cycle. These chips are pure RISC design, and thanks to the two-stage pipeline, each instruction executes in only one cycle, except program branches and table reads/writes, which are two cycles long. That makes it near 8 MIPS—not bad for a microcontroller.

The 58 single-word instructions (coded on 16 bits) are easy to learn for any user of Microchip's smaller controllers. Direct, indirect, and relative addressing modes are supported. External interrupts are present, as is a 16-level hardware stack.

One interesting feature for compute-intensive applications: there is an integrated  $8 \times 8$  bit hardware mul-

tiplier, working in only one instruction cycle. This multiplier offers a performance boost of more than three times (compared to a software-only version) for a complete FFT calculation.

The internal memory is impressive as well. The PIC17C756 has 16 K words of EPROM program memory as well as 902 bytes of general-purpose RAM, which accommodates quite large projects without the need of external memories, even if extended modes are available and support up to 64 K words of program memory.

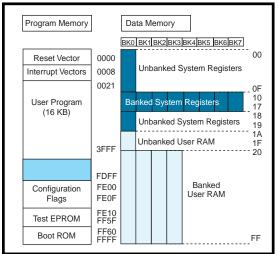

The smaller PIC17C752 has only 8 K words of EPROM and 454 bytes of RAM. Microchip has also announced flash-memory versions (PIC17F75X). The memory map is shown in Figure 2.

One piece of bad news: the RAM and registers are still banked, and the working page is selected by some bits in the BSR register. Even if some specific assembler instructions help, this is a major headache for the programmer and a major source of bugs. I hope that Microchip switches to a linear address mode in the near future.

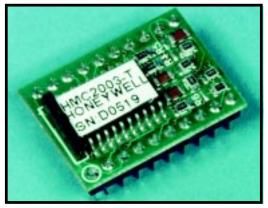

Hosted in 64- (DIP) or 68-pin packages (PLCC and TQFP), the PIC17C75X **Photo 1**—The PIC'Spectrum prototype is built on a  $1^{\prime\prime} \times 3^{\prime\prime}$  PCB. A good ground plate is mandatory on a mixed digital/analog design like this one. I used a transparent box to prove that there are very few components inside.

provides 50 I/O pins with individual direction control. As usual, each pin may be used for general-

purpose I/O or dedicated to some onchip peripherals.

Have a look of the pinout of the PLCC version in Figure 3 and you'll understand that this chip is quite flexible. Both OTP and windowed versions exist, even if they aren't so easy to find.

On the peripheral feature list, there are four timers (two 16 bits wide and two 8 bits wide, TMR0 having an internal 8-bit programmable prescaler), four capture input pins, and three PWM outputs with a 10-bit resolution.

Need more? Perhaps two asynchronous and one synchronous serial port, the latter configurable both in SPI and I<sup>2</sup>C modes, master or slave? Or a 12channel 10-bit ADC? Or an RC-clocked watchdog timer?

How about an integrated supplyvoltage supervision? Or a configurable RC/crystal/ceramic clock system with an oscillator start-up timer? Name it, and it's probably there.

The PIC17C756X also has in-circuit programming hardware. By pulling the TEST and MCLR/ $V_{pp}$  pins to a 13-V programming voltage before powering up the chip, a specific ROM

bootstrap code is launched and waits for orders coming from a dedicated serial synchronous interface (RA1/ RA4/RA5 pins).

With a small interface connected to the LPT port of your favorite computer, you can read or write the internal EPROM without any specific programmer and without having to extract the chip from its socket.

I developed my own PC-based incircuit programmer based on Microchip's programming specifications [2].

Electrically, the standard-grade PIC17C756 needs a supply voltage from 4.5 to 6.0 V, while a special extended device (PIC17LC756) accepts anything from 3.0 to 6.0 V. In both cases, the minimum RAM retention voltage is 1.5 V.

The supply current is 6 mA at 4 MHz but climbs to 50 mA at 33 MHz. Of course, sleep modes reduce consumption down to 1  $\mu$ A, depending on the selected peripherals, but high performances and low consumption are still difficult to conciliate.

# PIC'SPECTRUM HARDWARE

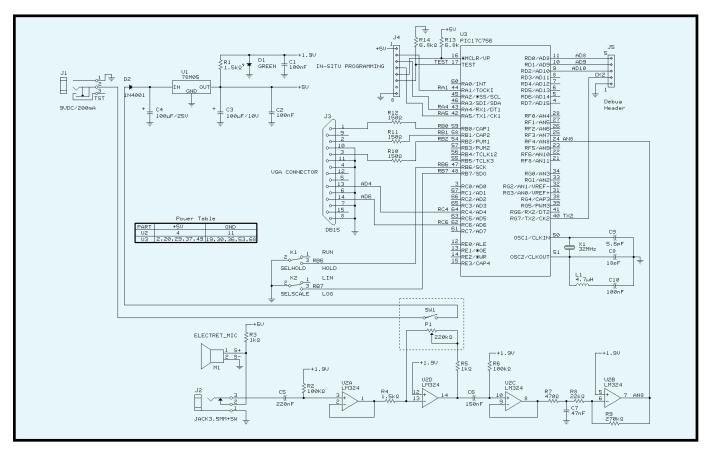

Now that we have a good microcontroller, let's look at the PIC'Spectrum hardware shown in Figure 4.

A small power supply, which is built around U1 (78M05), generates a clean 5 V from a standard 9-VDC power supply (the total power consumption is around 100 mA, which is mainly 50 mA for the PIC and 50 mA for driving the three 75- $\Omega$  video outputs). The LED D1 indicates powerup and generates a pseudoground 1.9-V level used by the analog section.

The analog input signal (from an onboard electret measurement microphone or a line input jack) is amplified and low-pass filtered down to 10 kHz

Figure 1a—Here's a classic block diagram for a spectrum analyzer. The signal is amplified and low-pass filtered before going to an ADC. A DSP calculates the FFT and drives the VGA screen through a video controller. b—The PIC'Spectrum block diagram is much simpler. The microphone signal is amplified and low-pass filtered and goes directly to the PIC, which calculates the FFT and directly generates the video. It's all in the software.

Figure 2—From this memory map of the PIC17C756, you see that the program and data areas are separated, as usual on a Harvard architecture. The '17C752 has the same memory map, except that there is only 8 KB of user program memory and two user RAM banks.

these frequencies, this crystal is a  $3 \times$  overtone model.

I needed a damper circuit (L1/C8) to select the correct resonant frequency. Without it, the crystal would oscillate

on its fundamental frequency, and I'd end up with a 10.66-MHz clock!

Two switches (K1 and K2) control the current mode (run or hold) and the scaling of the display (linear or logarithmic). They connect directly to RB6 and RB7 because the PIC has selectable internal pullups.

The VGA-compatible video-output connector is directly driven by the PIC. The horizontal and vertical synchronization signals are TTL compatible, so there's no problem there. For the R, G, and B lines (0–2 V/75  $\Omega$ ), a 150- $\Omega$  series resistor does an adequate 5-V to 2-V/75- $\Omega$  adaptation, thanks to the high power capacity of the PIC outputs (20 mA/line, 100 mA total for ports A and B).

The 8-pin header J4 handles in-circuit serial programming. Four additional output pins (including one UART output) are connected to a debug header. This provision is useful during the debug phase because it enables you to send debug information to a serial terminal to find out what's happening inside the box when you don't have an in-circuit emulator.

# **ON THE SOFTWARE FRONT**

Of course, when you choose the simplest possible hardware, the software has more to do. Here, the software must:

• do the acquisition of a burst of the analog signal (typically 256 samples at a sampling frequency of 16 kHz)

by four operational amplifiers (U2, LM324). A potentiometer lets you adapt the amplifier gain to the ambient sound level and serves as an on-off switch. The output signal, centered on the 1.9-V pseudoground level, connects directly to one of the PIC's analog inputs.

The PIC processor is clocked by a 32-MHz crystal (I wasn't able to find a 33-MHz crystal in time). As usual for

Figure 4—Around the PIC, there is only a quad operational amplifier, a regulator, and some discrete components.

- calculate the FFT of these 256 samples, giving an amplitude for each of the 128 frequencies

- calculate the power of each frequency and scale it (depending on the position of the log/lin switch)

- manage the run/hold switch

- do the generation of the VGA video signal in parallel

To do all these tasks while keeping real-time requirements, PIC'Spectrum software is divided into two tasks. The main program is in charge of initialization, device control, and numerical algorithms. The interrupt routine, executed each

31.77 µs (corresponding to the VGA horizontal video synchronization period), is in charge of analog signal acquisition and video generation.

These two tasks dialog through three RAM shared structures:

- FFT buffer (256 words, 16 bits each), filled by the interrupt routine with analog samples and used by the main program for FFT calculation

- display buffer (128 bytes), filled by the main program with the length (in pixels) of each of the 128 horizontal frequency bars, and used by the interrupt routine for video generation

- synchronization variables

Figure 5 illustrates the information flow. Since you can get the complete source code from the Circuit Cellar

Web site, I'll focus here under on the more specific codes, like FFT calculation and software video generation.

A standard FFT algorithm works on complex numbers (real plus imaginary parts). It takes as an input an array of *n* complex samples and gives an array of *n* complex frequency amplitudes. Here, the input signal is of course only real numbers.

The immediate solution to get its FFT is to add a zero imaginary part to each sample and to use the standard complex numbers algorithm. If you do that, only half of the *n* frequencies in the result are useful (in fact, each value is found twice).

This is a consequence of the wellknown Nyquist rule. If you sample your signal at a period of 1/n, you can only analyze frequencies with periods

Figure 6—The top part shows the timings of the video and horizontal synchronization signals, while the bottom part shows the conversion of these timings in number of instructions as well as what the PIC is doing during this time. above 2/*n*. More problematic, this simple approach uses twice as much memory as is useful and we have only 902 bytes of RAM.

Fortunately, you can use a more sophisticated algorithm, known as real-mode FFT. The idea is to pack two real samples in each complex input value, do a standard complex FFT, and decrypt the resulting complex values to find back the good real figures. You can get the details from *Numerical Recipes in C: The Art of Scientific Computing* [3].

To implement this FFT algorithm on the PIC, I developed a fixed-point mathematical library (source file is fixed.inc). It implements a virtual fixed-point machine operating on two 16-bit

floating-point registers (RA and RB).

Routines are available for addition, subtraction, multiplication, division, sine, and logarithm, as well as access to the banked RAM. The fixed-point format used is S/2/13 (one sign bit, 2 bits for the integer part, and 13 bits for the fractional part). In fact, writing sinus and logarithm calculation routines in assembler is quite an interesting experience.

# **OPTIMIZING VIDEO INTERRUPTS**

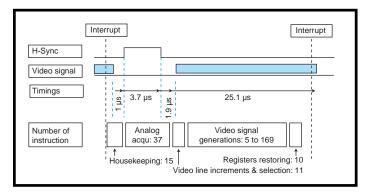

Writing the interrupt routine was another interesting exercise. One interrupt is generated by timer 0 each  $31.77 \mu$ s. This period equals the horizontal refresh period of a VGA signal in mode 7 (640 × 350).

Because  $31.77 \mu s$  translates into 254 instructions only (even at 32 MHz), the number of instructions used to do the analog signal acquisition and the video generation must be carefully optimized.

Figure 6 shows the VGA horizontal timing specifications, the corresponding number of instructions that the PIC17C756 could execute at 32 MHz, and the operations done by the interrupt routine in the corresponding time frame (more information on VGA timings is available on the Web [4]). The interrupt routine starts with housekeeping (register saving, timer reload, etc.) and switches on the horizontal synchronization signal. During the 3.7  $\mu$ s needed by this synchronization, the software manages the acquisition of an analog sample (one signal sample is taken every two interrupts, giving a 15.7-kHz digitization rate).

The current video line number is then incremented and used as an index into a table, giving the address of the routine to use for displaying each scan line (vertical synchronization virtual lines, blank lines, frequency display line, scale or title display, etc.). Each routine manages the switching on and off of the three RGB video signals with good timing.

This brute-force programming method is needed to achieve the result in Photo 2. The longer the program takes between the interrupt and the start of the video display, the more black areas you have onscreen.

Real-time requirements have to be managed very carefully. In particular, the execution time from the interrupt to the start of the video display must be rigorously constant, whatever the results of the if/then tests are.

If it isn't, the video lines do not align. I was forced to add NOPs everywhere—in particular, in the analog acquisition routines—to ensure that the same number of instructions is executed whatever the situation is.

To get the best result, I implemented some strange programming practices. For example, to get a specific delay with 125-ns resolution, I do a calculated jump in the middle of a long sequence of NOPs. It's the only solution I've found, because managing a loop consumes several instructions.

# DEVELOPMENT AND DEBUG

Debugging a signal-processing embedded application isn't easy. And, I don't have access to an adequate ICE. Since it might be useful for similar projects, let me briefly explain my methodology (which must not be too bad: PIC'Spectrum actually works!).

After some timing calculations to ensure the feasibility of the concept, I started with a prototyping phase on a PC using a PC sound board as input. I used floating-point calculations, with everything in C (see Listing 1). I then translated the software to use exclusively integer numbers and debugged it.

The third step was to develop a fixed-point library (still on the PC) that prefigures the future PIC-based fixed-point library. I also modified the FFT code to do all calculations exclusively through this library. It was quite easy to write this fixed-point library in PIC assembler, debug it on Microchip's simulator, and translate the FFT routine from C to assembler.

Using the simulator is useful for numerical-calculation software. In fact,

it was possible to open two windows on my PC, the first being a standard PC debugger with my C-code FFT, and the second the PIC simulator with the manually translated assembler code. Single stepping between the two codes with a test signal as an input helped me quickly find the more tricky bugs.

When the signal-processing part was completed and debugged, I wrote the real-time part (signal acquisition and video generation) and debugged it as much as I could on the simulator.

This phase was helpful for correcting timing issues related to video synchronization. For example, with a

```

Listing 1—Here you see my step-by-step process from traditional float C code on a PC down to integer

assembler code on a PIC.

Step 1: C code on PC, float numbers:

float data[NMAX],h1r;

data[j]=(data[i]-h1r)/2;

/* calculation step of FFT routine */

Step 2: C code on PC, integer numbers:

word data[NMAX], h1r;

data[j]=(data[i]-h1r)/2;

Step 3: C code on PC, use of pseudoregister based on fixed-point

library:

fixed.h:

word ra, rb;

/* pseudoregisters A and B */

m_sub ()

/* subtraction function a-b->a */

{ra=ra-rb;};

main program:

/* data[j]=(data[i]-h1r)/2 */

m_ldai(i); /* load data[i] in A register */

m_ldb(h1r); /* load h1r in B register */

/* A = A-B */

m_sub();

/* A = A/2 */

m_div2();

m_stai(j); /* store A in data[j] */

Step 4: Last, translation in PIC assembler

Fixed.inc:

; m_sub :

subtract B to A (A = A-B)

m_sub

macro

movfp rb+1,WREG ; low byte first

subwf ra+1.1

movfp rb.WREG

; and high byte with borrow

subwfb ra,1

endm

main program:

; data[j]=(data[i]-h1r)/2

m_ldai i

; m_ldai(i)

m_ldb h1r

; m_ldb(h1r)

m_sub

; m_sub()

; m_div2()

m_div2

; m_stai (j)

m_stai j

```

breakpoint set on each access to the horizontal synchronization pin, it's easy to verify if the timings on this pin meet the VGA specification.

I waited until this phase was successful before cabling the prototype. The first EPROM I burned didn't work 100%, but I got a working video image and something resembling a spectrum display.

Thanks to the in-circuit programming and some debug pins, the software was working soon. In fact, 90% of the bugs found in this last step were related to banking register issues, which are tough to simulate because hardware ports are involved.

# WRAP UP

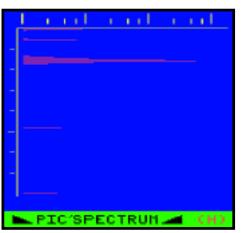

I got the display looking quite good, with an interrupt routine taking ~50% of the available CPU time for video generation. The main program has time to do more than 10 FFT calculations per second, giving a true real-time display.

With my technique, the time spent in the video-generation code depends greatly on the image being displayed. If the screen is full of information, the time left for the main program is near zero. So, you can't use this technique for all video-based projects.

To get satisfactory results with the video-display code, I sacrificed maintainability. Changes to the display may require tremendous efforts in keeping the real-time constraints unchanged. However, it works, and the basic principles may be used to get cheap video display devices like PIC'Spectrum.

For your next video-based project, try to do it with a software video only. If you have strict maintainability requirements, add a CRT controller chip or select a microcontroller with one built in. On the other hand, the FFT implementation is easily reused.

A final note: I'm sure this project wouldn't be possible without a good

simulator or an ICE. Thanks to Microchip for providing a good simulator for free on the Web!

Robert Lacoste lives in France, near Paris. He works in the telecommunication industry as senior project manager for GSM wireless base stations development. Robert has 10 years' experience in real-time software and embedded-system development. You may reach him at rlacoste@nortel.com.

# SOFTWARE

Complete source code for this article and freeware for the PIC-17C756 in-circuit programmer is available via the Circuit Cellar Web site.

# REFERENCES

- Microchip Technology, *PIC17C-75X Datasheet*, DS30264A, 1997.

Microchip Technology, *PIC17C-*

- XXX EPROM Memory Programming Specification, DS30274A, 1997.

- [3] S.A. Teukolsky, W.T. Vetterling, and B.P. Flannery, *Numerical Recipes in C: The Art of Scientific Computing*, Cambridge University Press, New York, NY, 1992.

- [4] "VGA Timing Information," www.hut.fi/Misc/Electronics/ docs/old/vga\_timing.html.

# SOURCE

# PIC17C756

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 786-7277 www.microchip.com 34 Nouveau PC edited by Harv Weiner

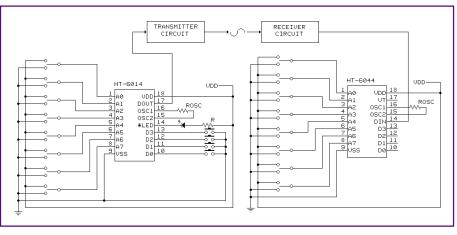

38 Networking with DeviceNet Part 1: How DeviceNet Stacks Up Jim Brady

46 Real-Time PC TCP/IP Networking Ingo Cyliax

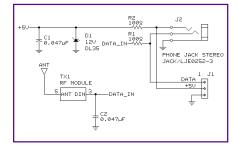

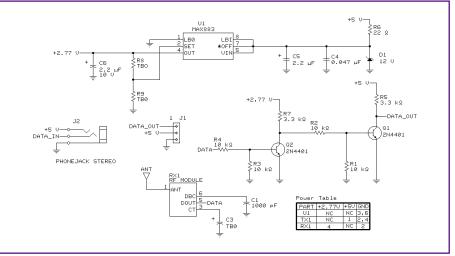

55 Applied PCs Radio Frequency and Micros Part 1: Transmitter and Receiver Modules Fred Eady

and the same

0101 0100 0001 1001 0000 0010 0000

$\infty$

T

23

1

SOLUTIONS

L1002 D3597

RX433AT

hoto courtesy of DVP

# **MULTIFUNCTION SBC**

The Élan104 has been designed for a wide range of embedded control applications with functions specific to the implementation of PC-based, lowcost, medium-scale man-machine-interfaces (MMIs).

Its Eurocard-format board features the AMD 100-MHz Élan486 microprocessor (full power management) with fully licensed ROM-DOS running in flash memory, 4–16 MB of EDO DRAM, 4–8 MB of flash memory, and 128 KB of battery-backed SRAM.

Other features of the board include dual DMA controllers, interval timers, real-time clock, clock generation circuitry, DRAM controller, and ROM interface. Also included are a bidirectional IEPP/ECP parallel port, 16550-compatible serial port, ISA-bus interface, speaker interface, and JTAG test access port.

Interfaces typically suited to MMI design include matrix keyboard interface, mono LCD graphics (with  $\frac{1}{4}$  VGA,  $320 \times 200$  to  $640 \times 480$  pixel resolution) interface, and SVGA CRT/ LCD for interfacing to CRT monitors or color flat-panel displays.

Standard peripheral I/O ports include 16-bit PC/104 expansion interface, floppy and hard disk drive interfaces, two RS-232 serial ports, one RS-485 port for multidrop serial applications, and a single LPT parallel printer port. Standard PC-type mouse and keyboard ports are supplied via PS/2 mini-DIN connectors.

Arcom Control Systems, Inc. (816) 941-7025 Fax: (816) 941-0343 www.arcom.co.uk

# **SOLID-STATE DISK**

The **FCLite** is a small form-factor, add-in, solid-state flash-memory–based disk emulator that uses an IDE interface. The drives are compatible with any operating system, without requiring special software drivers or onboard BIOS ROM sockets. The drives aren't mapped into any BIOS or extended memory space. They are currently available in capacities from 2 to 32 MB and have MTBFs exceeding one million operating hours.

The FCLite drives plug into either a PCI or ISA slot from which they derive power. They consume 3 mA in sleep mode and less than 100 mA when writing or erasing. The data transfer rate is 4.0 MBps reading, 2.5 MBps writing/burst, and 50 kbps writing/cont. Flash-memory write endurance is in excess of 300,000 write/erase cycles. The FCLite drives

can withstand operating shock of 500 G, temperature range of 0–700°C and 5–95% noncondensing humidity environments. Board dimensions are  $4.3'' \times 1.7''$ .

List prices for the FCLite drives range from **\$129** to **\$599**.

Curtis, Inc. (612) 404-9081 Fax: (612) 404-9175 www.mncurtis.com

edited by Harv Weiner

# SINGLE-BOARD COMPUTER

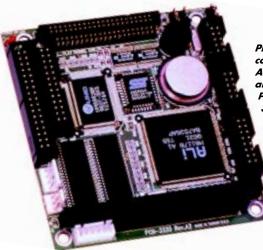

The **CMi586DX133 cpuModule** is an ultracompact, high-speed, fully integrated PC/104compliant CPU. The cpuModule features a highperformance 133-MHz Am5x86 processor, internal math coprocessor and cache, 8 MB of 32-bit wide surface-mounted DRAM, IDE, and floppy controllers.

Also included are two software-configurable RS-232/-422/-485 serial ports, Extended Capabilities Parallel (ECP) port, keyboard and speaker port, and a watchdog timer. A 32-pin solid-state disk socket supports 1-MB EPROM or 512-KB flash memory, SRAM, NVRAM, or MSystems' Disk-OnChip.

The services and functions provided by its Embedded BIOS ensures PC/AT compatibility. BIOS enhancements include quick boot, virtual devices, and solid-state disk support with flash file system. A virtual device mode allows the operator to use the keyboard, video, floppy, and/or hard disk on another PC-compatible computer through the serial port. A nonvolatile configuration EEPROM stores the system setup without needing a battery.

The CMi586DX133 sells for \$598.

Real Time Devices USA, Inc. (814) 234-8087 Fax: (814) 234-5218 www.rtdusa.com

# PC/104-COMPATIBLE AUDIO MODULE

WinSystems' **PCM-AUDIO-DLX** offers 16-bit stereo audio functions that can simultaneously record and playback (full duplex) voice, sound, and music on a PC/104-compatible module. Based on the ESS Technology ES1888 AudioDrive chip, this module supports PC audio that is AdLib and SoundBlaster Pro compatible.

A four-channel record mixer blends three 16-bit stereo and one microphone input under software control. An independent seven-channel mixer supports playback. Stereo output from the playback is up to 2 W per channel. The volume can be adjusted by software, an external 64-step pushbutton audio control, or onboard potentiometers. Two joystick inputs provide more input and control options.

The ES1888 chip operates at sample rates of up to 44.1 kHz to provide CD-quality sound. It has a 20-voice, 72-operator music synthesizer. The FM synthesis is backward compatible to the OPL-3 mode. An MPU401 serial port can be used to interface with external wave table synthesizers and MIDI devices.

Special drivers are not needed for newer OSs like Windows 95 and Windows NT. Windows 3.x is supported through supplied drivers. WinSystems offers a utility that allows record and playback of audio or voice with control of sample speed, volume, and compression for use with DOS or non-DOS applications. It also supports playback of Windows .WAV audio

files in a non-Windows environment.

An optional KIT-PCM-AUDIO-DLX consists of a PCM-AUDIO-DLX board, microphone, two speakers, PC Bus Sound Blastercompatible board, Windows audio-applications user guide, and DOS/ embedded-systems tools and drivers. This kit enables the designer to develop and debug the application code on either a desktop PC or the target embedded CPU running in a Windows or DOS environment.

The PCM-AUDIO-DLX sells for **\$250**.

WinSystems, Inc. (817) 274-7553 • Fax: (817) 548-1358 www.winsystems.com

PC/104 PERIPHERAL MODULE

The **MM686** is a PC/104 form-factor board featuring two PCMCIA slots, four A/D video input channels, 5-W SoundBlaster–compatible stereo sound, and support for optional PCMCIA-based Zoom Video MPEG decoding. It also accommodates two joysticks or a MIDI input. The video inputs support PAL, NTSC, and SECAM decoding and real-time video capture ability. The YUV video output plugs into the YUV connector on 686LCD/S or 686LCD/MG SBCs, allowing for extremely high frame rate video display and capture handled directly by the video controller.

The PCMCIA interface is PCMCIA-2.1 and JEIDA-4.1 compliant and supports all common PCMCIA cards (e.g., modems, ATA flash cards, MPEG decoders, and hard drives).

The SoundBlaster–compatible port has stereo-line and headphone output as well as a direct output from the onboard 5-W amplifier. The MM686 supports a microphone input, analog line input, and direct input from CD playback devices via the Zoom Video port. Volume control is supported in software or via the builtin up-down-mute plug. This PC/104 board is fully scalable for applications that don't require all of its features. It can be provided as just a SoundBlaster board, just a dual-slot PCMCIA interface, just a video/image processing board, or in any combination.

Inside Technology USA, Inc. (972) 390-8593 Fax (972) 390-8609 www.inside-usa.com

# Networking with DeviceNet

Part 1: How DeviceNet Stacks Up

With all the debate on networks these days, it's easy to get confused about the differences between networks, buses, and field buses, particularly when a new technology comes along. Join Jim for the lowdown on DeviceNet.

Reading articles on networks raises a lot of questions—like whether to call Device-Net a network, a bus, a fieldbus, or what?

The term "bus" is used for industrial networks that control things, as opposed to general office networks that move data. I decided to forget about impressive terms and stick to basics. I want to cover the meat and potatoes of what a developer needs to

know to implement a Device-Net network.

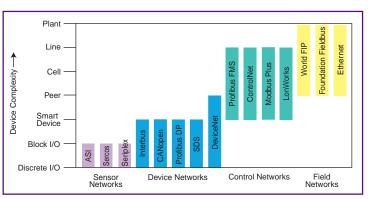

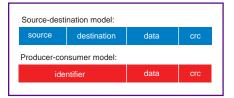

Why are there so many network protocols? Figure 1 shows 15 of them. Why not just use Ethernet?

In the beginning, I didn't ask. I developed DeviceNet interfaces because customers requested them. Then Profibus, then others. However, with time, I wondered: is there an ideal network for a given application?