# CERTIFICATIONS JOURNAL #99 OCTOBER 1998 DIGITAL SIGNAL PROCESSING

AND A DE LA DE

### Getting Around the Nyquist Limit

**Doing Filters in Software**

**Signal Conversion Basics**

PIC-Based Graphing Data Logger

oration

Constant of the Short Sh

# TASK MANAGER

### Not Exactly a Binary World

verybody's got their own way of looking at things. Fortunately—yes, fortunately—we don't all have exactly the same view of the world. It's also pretty clear that *INK* caters to a select audience. Not everybody, nor even every engineer, you meet designs or works with embedded computer systems for a living. But here's my point: Even within our narrow slice of the engineering universe, there are plenty of different perspectives. It's not all black and white, ones and zeros.

Over ten years ago, when Steve started *INK*, he was crafting a publication for hands-on engineers. And while a significant percentage of readers have been there since Day 1 (and among them will be those who call themselves experimenters as well as others who will vilify me for even suggesting it), *INK* has offered such an excellent range of editorial material over the years that its appeal now runs from systems designers in multimillion-dollar companies, to EE university students, to the engineering entrepreneur starting a brand-new company (that one day may in fact become one of those multimillion-dollar powerhouses), and beyond.

*INK* finds itself in a unique position, and faced with a unique problem: how to meet the needs of such a varied group. And I do mean *needs*. Nobody here is interested in putting together a magazine that gets tossed in the Freebies-To-Be-Read-Someday (yeah, right) pile. You pay for *INK*; you should get a magazine you want to read.

But, of course, there's only so much that can fit in a print magazine each month. That's why Design Forum is on *INK*'s web site. It's still in its infancy, but you know, sometimes, the more you give, the more you get. *INK* gives you Internet access to design hints, feature articles, abstracts submitted to *INK*'s design contests (most recently, Design98, cosponsored by Microchip), as well as monthly columns—and when you get inspired, you give back. Becoming an active part of the larger community that *INK* is fostering guarantees you'll find what you're looking for.

Design Forum is just one aspect of the growth here at *INK*. A new editorial advisory board has started, with three experienced engineering professionals—Ingo Cyliax, Norman Jackson, and David Prutchi—keeping their eyes and ears open for the kinds of editorial you're interested in. And although Ken moved on a couple months ago, he didn't go all that far: he still proofreads every article and helps with Design Forum editorial. Janice, too, has shifted roles. After doing a stellar management job for the past two years, she is now our Project Editor, helping with Internet editorial, as well as serving as a resource for special projects.

So, while *INK* is committed to its focus on providing high-quality engineering editorial, it's clear that we are determined to offer you a wider range of opportunities to experience it. No question: in the computing world, ones and zeros are a big part of the picture, but there's a lot of value lurking in the middle. Take advantage of it.

elizabeth.laurencot@circuitcellar.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot

TECHNICAL EDITOR Michael Palumbo

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ken Davidson Fred Fady

NEW PRODUCTS EDITOR Harv Weiner

Ingo Cyliax

PROJECT EDITOR Janice Hughes ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella

> BUSINESS MANAGER Jeannette Walters

> > ART DIRECTOR KC Zienka

ENGINEERING STAFF Jeff Bachiochi

PRODUCTION STAFF Phil Champagne John Gorsky James Soussounis

#### EDITORIAL ADVISORY BOARD x Norman Jackson

David Prutchi

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

#### ADVERTISING

ADVERTISING SALES REPRESENTATIVE Bobbi Yush Fax: (860 (860) 872-3064 E-mail: b

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster (860) 875-2199

Fax: (860) 871-0411 E-mail: val.luster@circuitcellar.com

#### CONTACTING CIRCUIT CELLAR INK

SUBSCRIPTIONS: INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066 AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles, contact Jeannette Walters (860) 875-2199.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Mo-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK®.

Entire contents copyright © 1998 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar INK is a registered trademark of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# **READER** I/O

#### AN ANALOG EYE ON DIGITAL DESIGN

I am an analog-oriented EE, and Mike Smith's article ("Unplanned Calibration Errors in Embedded Systems," *INK* 96) gave me an appreciation of the design considerations for a software program for a digital instrument. One would design an analog instrument to handle failsafe conditions for all potential situations. The software code, its syntax, and the compilers used to mechanize code handling add layers of potential ambiguity.

In analog design, the simplest approach is usually the best, and I expect that it's likewise in digital design. I think your examples were picked to be a demonstration for your article, and it worked.

As an analog guy, I would be more likely to enter the correction factor/calibration error for the transducer at a summing junction, with the reference trip level for the fail safe at the low/high trip, to generate a signal to be subsequently summed with that of the conditioned transducer signal to generate a trip alarm.

I would think that, in a software design review, the software would be simpler, more reliable, and faster if the static correction factor were applied as the digital sum of the static trip point, and then the correction factor, calculated on bootup, and the resulting static digital reference stored for comparison with the digitized transducer data?

I'm sure you agree that when the failure of a design could mean jail, or the poorhouse, the redundancy level for each catastrophic failure mode would be doubled or tripled, or pass the job. I'm not denigrating digital design, but I want to point that it has peculiarities to be considered.

#### Tom Callahan

tpcal@iu.net

Editor's note: A corrected version of Figure 1 from "Automotive Travel Computer" (INK 98, p. 67) is available as a downloadable PDF file on the Circuit Cellar web site at ftp://ftp.circuitcellar.com/CCINK/ 1998/Issue\_98/correction.zip.

October Design Forum password:

Filter

INK ON-LINE

Your magazine enjoyment doesn't have to stop on the printed page. Visit *Circuit Cellar INK*'s Design Forum each month for more great online technical columns and applications. Here are some of the great new on-line articles:

#### Columns

#### Silicon Update Online: Microchip on the March— Tom Cantrell

**Lessons from the Trenches:** Get an Embedded Micro and C Compiler off the Ground—George Martin

#### **Forum Feature Articles**

One More Wireless Trick to Stuff Up Your Sleeve— Hank Wallace

Lost at C? Forth may be the Answer—Tom Napier

#### **PIC Abstractions**

**Design Abstracts from our Design98 Contest** X-10 Temperature Sensor—Donald Blake Compact Optical Image Scanner—John Luo Heating Control System—Mark R. Wheeler

#### **Missing the Circuit Cellar BBS?**

Then don't forget to join the *Circuit Cellar INK* newsgroups! The cci newsserver is the engineer's place to be on-line for questions and advice on embedded control, announcements about the magazine, or to let us know your thoughts about *INK*. Just visit our home page for directions to become part of the BBS experience.

## www.circuitcellar.com

#### **GPS ANTENNA**

Tri-M Systems' **Mighty-Mouse** GPS integrates a highperformance patch antenna and a state-of-the-art, low-noise, low-power consumption amplifier into a compact waterproof enclosure. Ideally suited for deployment as an external antenna for hand-held or vehicle-based GPS receivers, the antenna consumes less than 12 mA while producing 25 dB of signal gain.

#### **Edited by Harv Weiner**

An innovative universal adapter system enables Mighty-Mouse antennas to mate with GPS receivers from different manufacturers. Supported connectors include SMB, SMA, BNC, TNC, and MCX. The Mighty-Mouse comes standard with a 5-m RG174/U cable and features magnetic and permanent mounting. The unit measures 58 mm × 48 mm × 15 mm and weighs 65 g.

The GPS antenna is hermetically sealed and completely waterproof. It is manufactured with a die-cast metal baseplate, which acts as a ground plane, so you can mount the antenna anywhere without sacrificing signal-reception performance. A polycarbonate radome protects the antenna element, low-noise amplifier, band-pass filter, and buffer stage at operating temperatures from -30° to +85°C.

Tri-M's Mighty-Mouse antenna comes with everything needed to attach to the user's GPS receiver. Pricing starts at **\$59** in OEM quantities, with a suggested list price **\$79**.

Tri-M Systems, Inc. (800) 665-5600 • (604) 527-1100 Fax: (604) 527-1110 www.tri-m.com

#### REAL-TIME VIDEO IMAGE PROCESSING

BittWare has announced a new video I/O mezzanine that interfaces NTSC/PAL video signals with SHARC processors in real time. The **bitsi-VIDEO** captures and displays composite and S-video signals, making it ideal for real-time image-processing applications requiring rapid scanning and peak I/O performance.

The bitsi-VIDEO mounts to SHARC-based host boards and uses a tightly integrated interface to transmit video signals to the processor on the host. Using square pixel or CCIR601 data formatting, the device encodes from, and decodes to, 8-bit YCrCb-format digital data. It delivers the signals to the SHARC processor on the host board for immediate processing or frame storage. Two link ports return processed video data to the bitsi-VIDEO for conversion back to analog video.

The bitsi I/O mezzanine standard is optimized to match the SHARC DSP's sophisticated I/O capabilities. A variety of off-the-shelf bitsi I/O mezzanines, including audio, control, video, and telephony interfaces, are available. The interface consists of 32 data bits, 26 address bits, 10 control signals, two DMA channels, four SHARC link ports, and three serial ports.

Pricing for the bitsi-VIDEO starts at \$1495.

BittWare (800) 848-0436 • (603) 226-0404 Fax: (603) 226-6667 www.bittware.com

#### HARDWARE SIMULATOR

The **SIMICE** hardware simulator provides low-cost system debugging for the Microchip Technology PIC-12C5*xx*, '12CE5*xx*, and '16C5*x* eight-bit RISC microcontrollers. It works in conjunction with Microchip's MPLAB-SIM software simulator to provide non-realtime I/O port emulation.

SIMICE enables a developer to run simulator code for driving the target system. The target system can also provide input to the simulator code, enabling simple and interactive debugging. SIMICE features unlimited software breakpoints and PC communication via serial interface at speeds up to 57 kbps. It also supports source-level debugging.

The MPLAB Integrated Development Environment (IDE) gives users the flexibility to edit, compile, emulate, and program devices from a single-user interface. MPLAB software offers a project manager and program text editor, a user-configurable toolbar containing four predefined sets, and a status bar, which communicates editing and debugging information. A dynamic error capability creates rapid application development. MPLAB is available at no cost by downloading the software program from Microchip's Web site.

The complete SIMICE hardware-simulator system features a hardware I/O port emulator board, RS-232 cable, PICmicro target probe cables, and MPLAB IDE software. SIMICE is priced at **\$129**.

Microchip Technology, Inc. (602) 786-7668 (602) 786-7200 Fax: (602) 899-9210 www.microchip.com

#### **VERSATILE SINGLE-BOARD COMPUTER**

The **SBC2000-074** single-board computer is a compact, low-power unit that features a Microchip Technology PIC16C74 running at 20 MHz. It is equipped with two RS-232 serial ports that run to 19.2 kbps, a real-time clock, watchdog timer, an 8-KB EEPROM, and five 8-bit A/D inputs. It also includes five programmable DIO lines, a low-power sleep mode, a PWM generator, an LCD port, and a keypad port. All this comes on a  $2.8'' \times 1.3''$  board. Expansion of the SBC2000-074's hardware is facilitated by the board's VAST (Vesta Addressable Synchronous Transfer) network connector, which lets the user select from over 20 peripherals.

The SBC2000-074 includes Vesta Basic V.2, which is a Windows-based, IDE-driven compiled BASIC. The single-tasking software features floating-point calculations with 16-bit precision. The unit operates at temperatures between -40°C and +85°C and consumes 15 mA at 5 VDC. A low-dropout onboard voltage regulator creates optional direct connection to unregulated supplies ranging from 5.5 V to 24 VDC.

The SBC2000-074 sells for \$64.

Vesta Technology, Inc. (303) 422-8088 Fax: (303) 422-9800 www.sbc2000.com

#### LCD MICROTERMINAL

The **ILM-216L** is an LCD module with a built-in serial interface. It works like a terminal, receiving text via RS-232 at 1200–9600 bps (8N1) and displaying it in large 5.9-mm (0.23") characters on a supertwist 2-line × 16-character LCD. text, which is ideal for updating numeric fields with minimal programming overhead.

A unique feature of the ILM-216L is its nonvolatile configuration memory (EEPROM). Users can set the ILM-216L to perform any of the following tasks at startup—display a custom splash screen, define custom characters, and turn on the backlight.

The ILM-216L draws only 5 mA with the backlight off and 40 mA with it on. The device measures  $80 \times 50$  mm (3.15"  $\times$  1.97"), so it

fits into most standard  $2 \times 16$  LCD mounting locations with a small overhang at the bottom.

Pricing for the ILM-216L ranges from **\$49** in single quantities to **\$29** in 100+ quantities.

Scott Edwards Electronics, Inc. (520) 459-4802 Fax: (520) 459-0623 www.seetron.com

Formatting text for the display is a simple matter of using familiar terminal-control characters such as carriage returns, linefeeds, tabs, and so forth. Additional instructions control the backlight, position the cursor, define custom characters, and read four switch contacts. The ILM-216L automatically right-aligns selected

#### THICK-FILM SMART FORCE SENSOR

The **DX-300** is an all-metal, thick-film sensor designed for high-precision, multiaxis force sensing in harsh environments. Typical applications include coordinate measurement and robotics feedback controls, as well as precise multiaxis force measurement and fly-by-wire motion control.

The DX-300 has a network of conductive thickfilm strain-sensitive elements (on a steel substrate) to measure microscopic strain. This network creates a force-measurement device that produces many times the output of even the best ceramic-based sensors.

Advantages of this construction include thermal stability, ESD protective design, high output, rotational accuracy, chemical stability with different cap chemistries, and no crack-propagation problems. So, the sensor circuitry will never fatigue or change output with time. The DX-300 features noncompliant palmor finger-activated motion and force-sensing capabilities in a high-output, precise smart-sensor design.

The sensors are offered in two smart-sensor systems the cursor control Integrated Block system that provides an RS-232 or a PS/2 sensor output for precise cursor control, and the force measurement/motion

control package that provides a 0–5-V output in all three distinct axes of input.

The DX-300 costs **\$165** in quantities of 500, and it is available with full signal-conditioning electronics for a slightly higher price.

Bokam Engineering (714) 513-2200 • Fax: (714) 513-2204 www.bokam.com

### FEATURES

| 12 | X-Y Graphing Data<br>Logger                 |  |  |

|----|---------------------------------------------|--|--|

| 24 | Time-Domain Filter<br>Simulations Using C++ |  |  |

| 30 | Breaking Nyquist                            |  |  |

| 36 | Digital Frequency<br>Synthesis              |  |  |

### FEATURE ARTICLE

# X-Y Graphing Data Logger

With more data than he can handle (and always in some inconvenient place), Alberto constructed a powerful, handheld, programmable data logger from his Casio pocket calculator. And as a reward, Design98 judges made it their "first PIC." ike any other designer, I have to cope with lots of data everyday. Raw data in need of analysis comes from every design phase and from all related sites. From writing specifications to development, from production tests to on-site verification, we end up with tons of measurements.

A graph is often the best way to point out the key features of what you measure. It's useful for instantaneous communications and easy to document for later reference. It's accepted for corporate quality system records, too.

PCs are powerful graphing tools, and maybe that's why almost all recent instruments have some kind of PC interface. So, you just take out your dazzling new computer-interfaceable meter, connect it to nearest PC, and start measuring. Right?

Wrong. Sometimes you want to take measurements in the field, and you can't take the instruments out of the lab. Something other than the PC can collect the data, but it's fooled by grounding problems.

Other times you need a batteryoperated instrument, but a laptop is too expensive, or it has to be used elsewhere, or the batteries don't last long enough. And don't forget that you have to convert data to spreadsheet format to get the graphics.

What if you need to collect data for a whole week? Can your precious equipment be locked for such a long time?

My solution: a simple yet powerful graphical data-acquisition unit built from a pocket calculator. I applied a component-oriented approach that resulted in a shortened development cycle and overall quality improvement.

The unit doesn't just collect data. It also displays it for further investigation, and it offers plenty of analytical and statistical built-in functions.

I applied low-power techniques and components to squeeze all the power out of a 9-V battery. By the way, I'll also tell you how I found the communication protocol used by the calculator.

While this design doesn't pretend to solve all your measurement problems at once, it's simple, cheap, and powerful enough to be useful in the situations I described above.

Its flexibility makes it ideal for acquisition in the lab, on the production line, in the field, or wherever you need a clear, graphical, and immediate (yet sophisticated) data display.

#### MACHINE MUSCLE

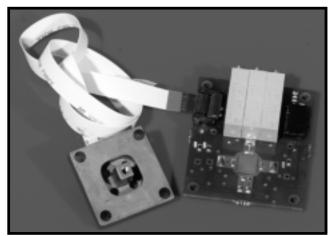

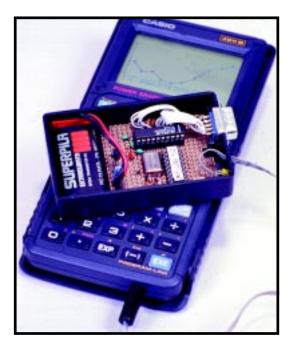

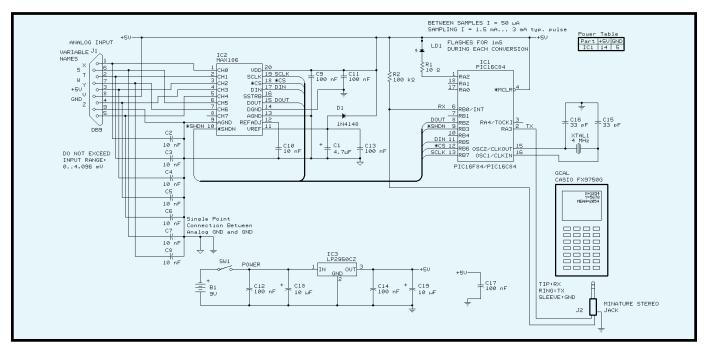

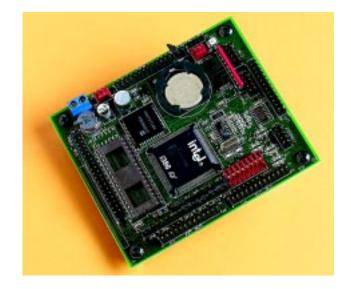

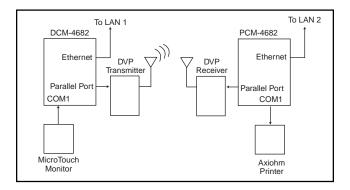

The data logger consists of the graphic calculator—with its  $64 \times 128$  LCD screen and keyboard—and the analog interface. I left the calculator untouched, and the analog interface fits in a small, separate plastic box (see Photo 1). They are joined only by the umbilical serial data connection.

The interface enables me to read the voltage at up to eight inputs with 1-mV resolution in the 0–4096-mV range, thanks to a 12-bit ADC. The data is converted to the right protocol by a PIC microcontroller and sent to the calculator for display and storage.

Once the data is received by the graphing calculator, it's immediately available for graphing, viewing, zooming, panning, or listing. You can apply all the calculator's functions to your

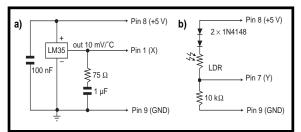

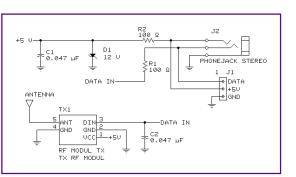

**Figure 1**—The unit can accommodate a variety of sensors. Up to eight sensors can be read at the at the same time with 1-mV steps from 0 to 4096 mV. **a**—This setup reads temperatures ranging 0–100°C with a resolution of 0.1°C. **b**—The light sensor is placed in front of an LED to nonintrusively monitor a device's on/off status. The diodes reduce the maximum output to a safe 3.6 V.

data set, either by hand or through simple programs.

Statistical (e.g., linear, exponential, polynomial regressions, mean, or deviation) and mathematical (e.g., integration, derivation) analyses are only a few keystrokes away. All of this can be done in the field with no other hardware except the logger itself—a capability not found in the most expensive data loggers available today.

The unit is battery powered and works for more than 200 h on standard batteries while retaining more than 20 KB of data for at least one year. I use separate batteries for the calculator and analog interface. Batteries make this device suitable for mobile use, as well as eliminating ground loops, which is a common nuisance for PC users.

#### USING COMPONENTWARE

Componentware is a popular buzzword in the IT community. It stands for software entities (sometimes as big as a full-featured word processor) that you can reuse as building blocks for other programs without having to know too many details.

What does componentware have to do with hardware design? A lot. A  $16 \times 2$  LCD, an RF tuner, and a stamp-sized controller (e.g., Basic Stamp, Domino, PicStic, or Basic Tiger) comprise the hardware counterpart of componentware techniques.

Once upon a time, we had libraries of subcircuits that worked well. But today, we have fat, white-box components. The list goes on to include DC-to-DC converters, modem on a chip, LCD voltmeters, wall-wart power supplies, and even a whole PC!

Is the componentware a good design technique? I think so. When you have a  $16 \times 2$  LCD, you don't need to know the details about LCD polarizers or backlighting problems. Just leave these problems to LCD specialists, and concentrate on your specific application.

Adding components together increases the abstraction level and, consequently, the designer's

freedom and power. With so many problems already solved, you can concentrate on solutions to new problems.

All of this comes at no extra cost. Most white-box components are derived from high-volume consumer devices. Everyone benefits from the optimized price, industrial quality, uniformity, and reduced time to market.

In this design, I go a step further and use a graphic calculator as a white-box component to build a data logger. Admittedly, thinking of a pocket calculator as a component is a little wild, and we may never see such a component as a standard.

Nevertheless, the general approach is effective, and the benefits can apply to a number of designs. For one thing, it increases designer power, putting a graphical LCD, a programming language, lots of memory, and PC connectivity at your disposal.

Using a calculator also cuts development time, so it takes just days (not weeks or even months, if you include

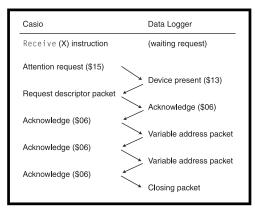

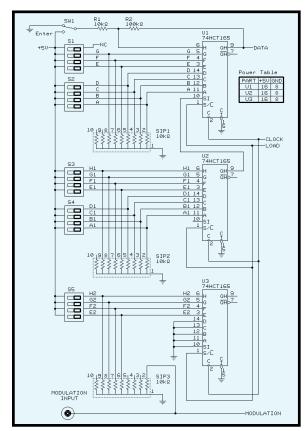

Figure 2—Here is the main flow of the Casio communication protocol. Apart from reversed-TTL logic levels, it's a familiar half-duplex with 9600 bps, no parity, eight data bits, and two stop bits. A level converter and inverter like the MAX232 is all that's needed to interface the Casio to a PC serial port.

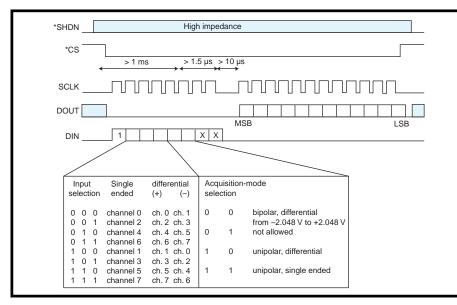

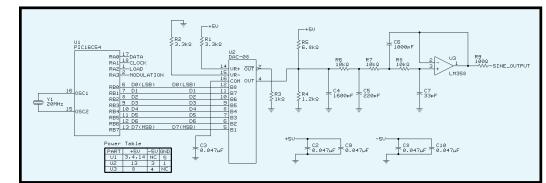

**Figure 3**—The analog inputs of the MAX186 can be switched to bipolar and pseudodifferential mode by changing the control word. In bipolar mode, the input spans between ±2.048 V instead of the usual 0–4.096 V. The last two bits in the control word select the power-down mode. Here, they are overridden, forcing the shutdown pin (\*SHDN) low.

the calculator math) to go from ideas to prototype. This technique also simplifies the problem-solving path: a simple concept, simple electronics, and simple software yield a complex result.

You also get lower power consumption (at least 200 h on standard batteries), which is more than 20 times a comparable PC-based solution.

Also, using the calculator cuts cost. Just one, off quantity, sells for the price of an LCD alone. Overall costs are more than 20 times less than any PC-based solution of comparable power.

You get increased flexibility, low cost, and an easily replaceable flashreprogrammable input board, enabling you to retain the calculator. Plus, only data acquisition and transmission need to be tested, and you save on production costs because you don't need complicated plastics and electronics.

Documentation is simpler, too. Just add a "Capturing data" chapter to the calculator's manual.

Size and weight are also reduced. Even prototypes are handheld, weighing only 290 g (including batteries), and series production sizes can be reduced further.

#### LOW-POWER GUYS

Every successful project relies on component selection, especially batteryoperated designs. Maxim's MAX186 is a low-power 12-bit ADC. It needs minimal external hardware and features a nice internal 4.096-V reference that sizes each step to a handy 1 mV.

The MAX186 sports eight singleended inputs, which is more than enough for most applications. The same inputs can be reconfigured as four bipolar and pseudodifferential inputs by simply changing the command word. It's suitable for reading data directly from a large variety of sensors (see Figure 1).

The MAX186 generates its clock internally, and the entire operation is controlled through a four-wire SPI, QSPI, or Microwire serial interface. The device is put in standby mode via a three-level input pin or with a software command word.

It consumes 1.5 mA typical while operating, which drops to a mere 2  $\mu$ A in full power-down mode. There is also an interesting fast power-down mode (not used in this design) that consumes 30  $\mu$ A with a wake-up time as short as 5  $\mu$ s.

If 10 bits are enough for your taste, you can replace the MAX186 with the MAX192. It's fully pin- and softwarecompatible with the MAX186. Price aside, the only difference resides in the precision of the two lower bits, which aren't guaranteed for the MAX192.

The chip needs a single 5-V power supply. With such a low power requirement, the drain of the power regulator itself becomes important. Ordinary regulators such as the 78L05 can easily drain more current than the whole circuit.

You need specific low-dropout regulators like the LM2936 to get maximum battery life. The LM2936 has a quiescent current of only 9  $\mu$ A, and it's internally protected from reverse battery connection.

#### FLASH RISC GLUE

An eight-bit RISC microcontroller glues the ADC to the Casio serial input. Because my goals included rapid development time and low cost, I focused on small flash- or EEPROMbased RISC microcontrollers.

The simplified RISC architecture is easy to learn, and erasable parts let you concentrate on the problem instead of the UV eraser. As a bonus, these parts usually have simple, ultracheap PC-port-based programmers.

I chose the PIC16C84 (an EEPROM part) and the newer PIC16F84 (an improved flash version) from Microchip. A useful characteristic of the PIC architecture is its support of data tables that are as long as the program memory. This characteristic is a result of the RETLW instruction.

These PICs are powerful enough to handle serial communications entirely in software with a 4-MHz clock. A faster part (you can find 50-MHz PIC clones) is unnecessary.

The PIC draws only a few microamps when sleeping (even with the watchdog timer enabled), and best of all, it's cheap and available. MPLAB, a professional grade assembler and simulator, is distributed for free by Microchip, along with lots of useful libraries.

#### THE GRAPHIC ENGINE

The Casio FX-9750G graphing calculator has 32 KB of RAM for data or programs and a  $64 \times 128$  black and white LCD. The FX-9750G is a member of a larger family that includes models with color LCDs and up to 64 KB of memory. It's a powerful and enjoyable math tool, but it costs about the same as a graphic LCD module alone.

It runs on four LR03 batteries for 200 h, and sensitive data and programs are maintained for up to one year by a Photo 1—The circuit fits inside a small plastic box just as large as the calculator. The micro jack connector hangs out, connecting to the calculator serial port. The box is stuck to the bottom of the calculator for operating. This arrangement gives the calculator a stable and comfortable slope.

separate lithium battery. I'm glad the Casio folks elected to use a standard miniature stereo jack as the serial port connector for external peripherals.

The data protocol is built around a standard 9600-bps half-duplex serial stream, with one start bit, two stop bits, and eight data bits with no parity.

Interfacing the FX-9750G to a PC is a matter of adapting TTL-to-RS-232 levels. A MAX232 can do the job. I built one of the dozens of similar circuits I found on the Internet, coupled with the FA-122 Windows backup software.

I haven't tested the compatibility with other calculators (besides the FX9750G), but I don't expect any differences in the protocol between similar models.

#### CASIO PROTOCOL

The Internet is now an invaluable resource for designers. After a night of browsing, I found some commented programs for loading calculator pro-

grams to and from a PC. I found only partial information about how to transmit or receive single variables instead of programs, but it served as a good starting point.

I assumed that the variable transfer format probably wasn't so different from the program transfer format. Notably, even the official Casio FA-122 backup software can be found online.

I knew that the communication was a 9600-bps half-duplex TTL serial stream, and I knew communications should start with ACK/NACK-style, single-character messages. Packets follow, starting with colons (\$3A) and terminating with checksums.

I also had PIC samples, some good ready-made serial and BCD routines,

| Senf cade: 128 106 111                                                                                            | 115 IE -                                 | padult                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COM settings 0000.0.2 17 auto-in                                                                                  | privita de la selación de la selación de | \$15 Chartene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ("Received) target by faile"/<br>18 ("ready to set4? () set the<br>12 ("yet, ready")                              | eren)*/                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PERSONAL MEANING VALUES AND                                                                                       |                                          | 123 of Wassedness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 17 17 17 17 17 17 17 17 17 17 17 17 17<br>17 17 17 17 17 17 17 17 17 17 17 17<br>17 18 17 17 17 17 17 17 17 17 17 |                                          | adara a peter a bela a la bela a la bela de |

| 06<br>28 /"variable descriptor follow                                                                             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 04, 56 41 40 00 86 40 00 01 00 0<br>FF FF FF 56 61 72 69 61 62 62 6<br>FX F5 77 77 77 77 77 77 77 77 77 77        | 5 62 04 99 99 99                         | Vil Winneddran<br>mei TariablaDeann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17 30<br>Se /?value &-12340670908800 fall                                                                         |                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DA BO OI DO DE OI 23 45 47 89 O                                                                                   | 0 80 00 01 09 90                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 33, 45 42 44 70 77 77 77 77 77 77 77<br>77 77 77 77 77 77                                                         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10000                                                                                                             |                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Photo 2-I used Visual Basic to discover the inner secrets of the Casio protocol. With VB5 it's easy to set up a quick and dirty serial protocol debugger. Tasks responding automatically to a control character, trying various serial speeds, or sending packet strings are left to a simple program loop. Thanks to Visual Basic's interpretative nature, you can stop the program, issue any other command manually, then continue execution. This way you avoid writing lots of code. Here, the characters sent by the Casio are in red, and the analog interface response is in black.

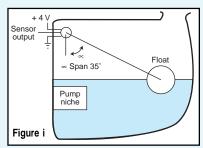

#### Straightening Curves—Linearizing a Tank-Level Sensor

Most sensors' outputs are nonlinear. To use them practically, they must be straightened using interpolation tables or analytical models.

Regression models are popular analytical tools for substituting data tables with clean, continuous functions that are elegant and practical. During calibration, function substitutes require only three or four points to be measured, as compared to the many more points that tables require.

The volume of liquid in the 25-l tank in Figure i is measured using a float and potentiometer. The output is proportional to the angle. The tank's irregular shape makes an analytical approach im-

practical. It's better to measure the sensor output at known liquid quantities.

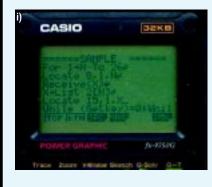

**Photo i**—The output is connected to the *x* input, and the program in Listing 1 is run. Each cycle, exactly 1 l of liquid is added until the tank is full. At the end, List1 stores the liters of liquid, and List2 stores the sensor's output level. Successive data manipulation is done manually.

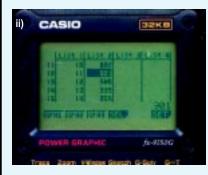

**Photo ii**—Selecting STAT gives you the sampled data in its raw form, as it appears on the default entry page. Here, editing and sorting can take place. GPH1 lets you view data graphically, and SET lets you check the current graphing preferences.

**Photo iii**—The preferences for GPH1 are set as a scatter graph with small box markers. I want to plot the liters over the sensor's output, so I select List2 for x and List1 for y. Showing the inverse function is simply a matter of exchanging coordinates here. Exit goes to the previous menu.

**Photo iv**—The display scales automatically to fit all the data, but you can zoom in or pan in each direction. The dotted grid is shown every 50 mV for x and 5 l for y. Note the gap at about 5 l (after the fifth marker), which is due to the pump niche.

**Photo v**—To draw the first-order regression line, just press X. Other regression models (e.g., median-median, second- to fourth-order polynomials, logarithmic, and exponential) are obtained the same way.

**Photo vi**—The first-order regression is too coarse for reliable measurements, but it's easy to try other curves. The secondorder one, shown here, fits the data nicely.

**Photo vii**—Zooming shows that the error at the pump niche gap is negligible.

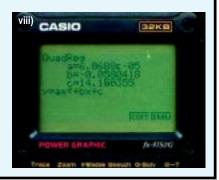

**Photo viii**—Pressing  $X^2$  brings up the coefficients and the regression formula, ready to be used for linearizing the sensor's output. Thanks to the second-order characteristic, a full data table is no longer necessary. I can do the calibration with only three points.

and a microjack plug. That's all I needed to start experimenting.

Using a TTL-to-RS-232 level converter, I connected the calculator to the PC serial port so I could monitor what's going on.

After I issued the Receive(X) command on the Casio, it sent out a \$15 character and, after 1 s, it aborted (a \$22 character sent to the PC prior to interrupt communications).

I made a Visual Basic program to issue various characters after that attention request (see Photo 2). I quickly discovered that the calculator was waiting for a \$13 character.

A request packet from the calculator follows this vital sign from the PC (50 bytes, starting with : REQ), where the calculator defines the variable to be sent. As expected, all nontrivial packets start with a colon character and are terminated by a simple negated checksum. With the exception of the last packet, all require an acknowledgement message from the recipient (\$06).

Since I didn't know how a value packet is made, I reversed the situation, making the Visual Basic program act as a Casio calculator issuing the Receive(X) command that was just received. At the same time, the real Casio calculator issued Send(X). In this reversed setup, the calculator issued a 50-byte variable-address packet, starting with : VAR.

I reiterated this process, continuously reversing the sender with the receiver, sometimes simulating Send(X) and sometimes simulating Receive(X). Packet after packet, the whole protocol was discovered, as depicted in Figure 2.

#### MAIN CODE

The software copes with communication protocols over a serial line, combining sleep mode and watchdog techniques to achieve minimal power consumption, low-power ADC driving, and data conversion to the Casio format.

Complete packet templates are stored in data tables in program memory. At this point, I found RETLW invaluable.

Only segments with variable values are replaced by real data read from the ADC in real time. Most parts of the input packet are ignored, and only the variable name is stored to select the right ADC input. When issuing Receive(X), you can specify any other variable name to select a different input.

Even the simpler communication protocol must deal with errors and interruptions. To keep program overhead low, I set up the watchdog timer to reset the device if it waits for an answer from the calculator for more than 2 s. Once reset (and for most of the time), the device is left in sleep mode. It's awakened by another WDT timeout or by receiving a character.

In the former case, the device goes back into sleep mode. In the latter case, the LED flashes, the ADC awakens, and the communication flow restarts.

When the micro sleeps, the ADC is left in full power-down mode. The shutdown pin is a three-level selection input, and the MAX186 sleeps with that pin at 0.

It is awakened by putting the pin in a high impedance state, which is done long before the conversion starts to let the voltage reference capacitor charge completely.

The MAX186 input can be reconfigured to bipolar input mode (with input spanning from  $-V_{ref}/2$  to  $+V_{ref}/2$ ) or pseudodifferential input mode by changing the command word that is ORed in the ReadADC code segment. Figure 3 shows the signals involved and how the control word is made.

The Casio needs variables in BCD format with separated exponent digits. The most significant digits come first. The BCD conversion and the bitbanging serial-port routines are derived from public-domain Microchip libraries.

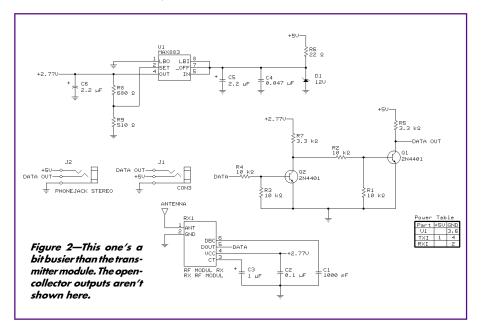

Figure 4—Using a graphing calculator as the output and processing device results in a simplified circuit diagram. The 5-V power rail is brought to the input connector to feed external sensors. If the quiescent current does not concern you, then the popular 78L05 can replace the LP2950CZ.

#### **INSIDE THE BOX**

The final circuit diagram is shown in Figure 4. Since this is a low-power, unshielded, mixed A/D circuit, the overall result depends on the quality of the layout.

Even though we're all accustomed to 12-bit converters, you must take great care to correct grounding so you have stable readings of the least significant bits. The analog and digital grounds must be kept separate. They have to be joined only at one point (as near as possible to the regulator ground). Bypass capacitors are mandatory, and capacitors on the inputs are equally necessary.

The MAX186 has a good pin layout, which helps separate input lines from data lines, and a stable readout is easily obtainable. But in noisy environments, consider averaging in software to further reduce uncertainty.

The eighth analog input is left unconnected on the prototype. This arrangement enabled me to bring the power out to the nine-pin input connector, thus powering external sensors. However, it's fully supported by software, so if you need it, simply add an input capacitor and feel free to use it.

Of course, power supply is critical in every battery-operated device. Power-up rise times must be short because there is no external reset circuitry for the micro. The MCLR pin is tied directly to  $V_{CC}$ .

The low-power regulator is more delicate than a regular 78L05. It requires an output electrolytic capacitor—better if it's tantalum.

The required current is impulsive, consisting of a 50- $\mu$ A offset (sleeping micro and ADC), 1.5 mA during serial communication with the calculator, a single pulse of 1.5 mA for a few milliseconds (A/D conversion), and a 1-ms peak for LED flashing (current given by the LED series resistor).

The LED flashes once per conversion. I recommend a red LED because it produces more light with the same current.

I brought the power supply to input pin 8 in case some sensor needs it. Be sure to take sensor power requirements into account when estimating battery life. If the sensor sinks a significant amount of current, consider powering it through one of the free PIC I/O pins, which will power off when not in use.

I assembled the whole circuit using a prototyping board, and it fits inside a small plastic box that's only the size of the calculator. The box contains all the circuits and the battery. Only the micro jack connector (connecting to the calculator serial port) hangs out.

As you see from Photo 1, there's a lot of space left on the board. If possible, use a 90° jack to keep the unit even more compact and rugged.

#### SETTING UP THE CASIO

While operating, the analog interface box is stuck to the bottom of the calculator, below the LCD, with TESA removable biadhesive strips. This arrangement gives the calculator a stable and comfortable slope, and it leaves the input connector in a handy place, free from obstacles.

To reveal the micro jack socket, remove the rubber cover that comes with the calculator. If the jack is left unconnected or the unit is powered off, a Com error message is displayed.

You don't need any particular programming skill to use the acquisition unit. One instruction does it all.

Issuing Receive(X) directly (Recv softkey in the PRGM I/0 menu) displays the value read from channel x. You can manipulate the x variable like any other ordinary variable, exactly the same way you would if you entered it manually. Value is expressed in millivolts, and ranges from 0 to 4095.

Receive(X) is usually issued under program control, as in Listing 1. But, I like to manipulate graphs manually. It's an instructive, highly interactive way.

Nevertheless, every keystroke can be replaced by a matching keyword to be issued under program control. From the programming standpoint, complex tasks (e.g., displaying a whole graph or computing a fourthorder regression) count as only a single instruction.

You can specify other variable names instead of *x*. Each variable

selects a different input. Variables supported are *x*, *y*, *v*, *w*, *z*, *s*, *t*, and *u*. Other names are seen as aliases and won't cause errors.

#### **FIRST GRAPH**

Look at the real-world example in the sidebar "Straightening curves— Linearizing a Tank-Level Sensor." Here, a float drives a potentiometer sensing the liquid level in a 25-l, irregularly shaped tank.

I want to figure out the relationship between the sensor output and the quantity of liquid left in the tank and to gather enough data to build a model for the control processor.

The complex relationship between angle, height, and volume makes an analytical approach impractical. It would be better to measure the sensor output at known liquid quantities.

The potentiometer output is brought to input *x*. It's powered at 4 V to avoid damaging the inputs.

In Listing 1, you see the simple control program that's required. List is the equivalent of an array in the Casio world. Seq allocates the memory space for a list and initializes it. Here, two lists—one for the liquid quantity and one for the sensor output are created and filled with data in a simple for-next loop.

At each cycle, 1 l of liquid is added and a measurement is taken. This process continues until the tank is full. When the program ends, the two lists hold the quantity of liquid as well as the sensor's output level.

Even if data visualization commands could be included in the program, it is convenient to look at nonrepetitive tasks manually.

The STAT menu lets you examine the data tables. If you select the GRPH submenu and GPH1, Graph1 is then displayed as an *x*-*y* scatter graph of List1 (liters) over List2 (sensor output).

Although nonlinear, it's immediately clear that the sensor output is suitable for measurements. An anomaly at about 5 l, due to the presence of a pump niche that reduces the available volume, is equally evident.

#### **MODELING DATA**

By means of regression, the measured data can be shaped into a function that fits into a nice formula. Formulas are not only easy to implement, they also give us a better understanding of the data and can significantly reduce the number of points needed for calibration.

In this example, the original data set is made of 26 points. Knowing that a sensor's output is a secondorder function enables a three-pointonly calibration without appreciable degradation. The calibration procedure can then be reduced to reading the output at three convenient positions (empty, full, and halfway).

On the Casio, complex regressions are a single keystroke away. When a graph is displayed, as in Photos v, vi, and vii in the sidebar, the softkey line lists a variety of popular regression functions to choose from. Pressing xbrings out the coefficients for first-order regression line. DRAW puts a graph over the sampled data.

As you see from Photo vi, a simple straight line leaves a lot to be desired. The shift-zoom combination brings up the zoom menu, while pressing one of the arrow keys pans the whole display in the indicated direction.

The  $X^2$  softkey switches to the second-order regression. This time, the graph is very near to almost all the samples. The overall result doesn't vary appreciably regardless of the regression order (e.g.,  $x^3$ ,  $x^4$ ). Other regression models (e.g., logarithmic, exponential) don't give significantly better results.

You can interact with your data and try out as many functions as you like, exploring the possibilities without having to write a single line of code. It is impossible to list here all the functions in the 425-page Casio FX9750G user guide. There's also a full set of statistical tools—useful when monitoring production sample parameters, weather data, pollution, and so on.

#### A BROADER VISION

Since this design was announced in *INK* 95, I've received lots of E-mail from interested readers. Each one had a different vision of what this little design can be used for—from tracking the accuracy of a GPS-locked PLL and

**Listing 1**—This simple program makes 25 samples and places them in List2. Another list is filled with ascending numbers used as x-axis values on an x-y graph. List is the equivalent of an array in the Casio world.

```

Seq(N,N,0,25,1) --> List1

Seq(0,N,0,25,1) --> List2

For 1--> N To 26

Receive(X)

X --> List2[N]

Locate 1,1, N

Locate 10,1, X

While (Getkey): WhileEnd

Next

```

plotting weather data, to shoving a waveform from an instrument and monitoring a central heater's operation, or counting people coming in a door.

The number of possible applications exploded. Built-in display and the capability of being programmed, combined with very low cost, are the key factors.

I encourage you to expand the capabilities of the data logger. The code is fully commented, and the PIC program memory is only half full.

I do have a couple suggestions. As a first step, try adding a pulse-counter mode. There are lots of things worth counting, and many sensors (e.g., Steve and Jeff's lightning sensor [*INK* 90]) have pulse outputs.

Secondly, drive outputs by implementing the Casio command Send(X)to make the interface bidirectional. The Casio is slow but powerful enough to read in the input, make some computations, and send output to the outside world. In this way, it would migrate from the world of monitoring and displaying events to the broader world of (pocket) computer control.

Alberto Ricci Bitti is a software designer at Eptar, an industrial-controller firm. He has written software for systems such as meteorological equipment, specialized TV sets, professional satellite devices, industrial machinery controllers, and energymanagement devices. You may reach Alberto at a.riccibitti@ra.nettuno.it.

#### SOFTWARE

Source code in official Microchip mnemonics is available via the Circuit Cellar web site.

#### REFERENCES

- MPLAB IDE free assembler and simulator software, 1997 technical library, www.microchip.com.

- Casio, FA-122 software and PC link schematics, members.tripod.com/ ~carolino/.

- Casio, FX9750G User Guide, A340606-27.

- Maxim Integrated Products, MAX186– MAX188 low-power, 8-channel, serial 12-bit ADC, Datasheet 19-0123, August, 1996.

- Maxim Integrated Products, *MAX192 low-power*, *8-channel*, *serial 10-bit ADC*, Datasheet 190123, March, 1994.

- Microchip Technology, *PICmicro mid-range MCU family reference manual*, Datasheet DS33023A, December 1997.

#### SOURCES

#### PIC16C84, PIC16F84

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 786-7277 www.microchip.com

#### **MAX186**

Maxim Integrated Products (408) 737-7600 www.maxim-ic.com

#### FX9750G

Casio Electronics Co., Ltd. www.casio-usa.com

### LM2936, MAX186, PIC16C84, PIC16F84

Digi-Key Corp. (218) 681-6674 Fax: (218) 681-3380 www.digi-key.com

### FEATURE ARTICLE

**Glenn Parker**

# Time-Domain Filter Simulations Using C++

When you have to work with filters and what hardware engineer doesn't at some point?—you'll want to try out Glenn's complete C++ FILTER class. He's ready to prove how easy it is to integrate this class into embedded apps. early every hardware engineer (analog or otherwise) deals with frequency selective circuits, or filters, at some point in his or her career. Filters are everywhere, and most electronic systems can't function without them.

Circuit simulation is fairly straightforward today, especially with readily available simulation software. But, some engineers still write software (for speed or to handle aspects of their application not addressed by commercial software).

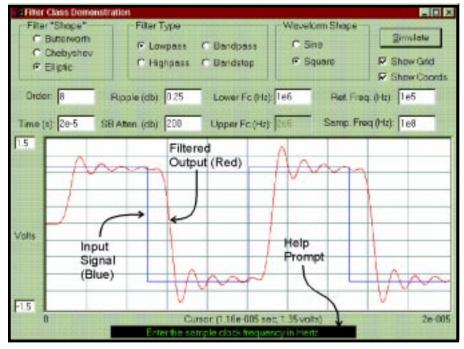

This article presents a complete C++ class for simulating electronic filters. If you need a refresher course, check out the sidebar "Analog Filter Basics."

The source code is implemented for analog filtering, but you can easily adapt it to handle digital filters or any analog system that can be characterized by a transfer function in the frequency domain. A Windows executable complete with source code is also available which uses the class to simulate various analog filters, including elliptic types.

Digital or discrete-time filters are implemented in software or through dedicated DSP hardware. Analog or continuous-time filters are generated by designing a network whose input impedance changes with frequency to realize a desired response curve. For this reason, analog-filter specifications are typically given in the frequency domain. Still, it's important to consider the time-domain characteristics of analog filters whenever waveform distortion (e.g., in digital demodulation systems) or signal delay is critical.

#### TRANSFER FUNCTIONS

Analog-filter designers are undoubtedly familiar with how the Laplace Transform relates continuous-time with the frequency domain. There is a parallel relation between discrete time and frequency via the *z*-transform.

The coefficients of a function in the *z*-domain can be used to construct a constant-coefficient difference equation, which provides a direct method for time-domain simulation:

y[n] = 2x[n] + x[n - 1] - 3y[n - 1]

where y[n] is the output at time  $\Delta tn$ , and x[n] is the input at time  $\Delta tn$ . By iterating n, this system's time-domain response to a changing input can be calculated. The constant  $\Delta t$  is simply the time interval between n - 1 and n.

Once the difference equation coefficients are found, a real-world signal can be sampled with an ADC and filtered by hardware with dedicated DSP devices or microcontrollers or by some other method implementing the difference equation. The same idea lies behind digital filters as well.

The difference equation coefficients can be tweaked to realize nearly any magnitude and phase requirement. Or, you can take the coefficients and funnel them through a simulation engine like the one presented here to see what the original analog filter looks like in the time domain.

The only missing link is how the *s*-domain function gets into the *z*-domain. There are several acceptable methods for accomplishing this, each with benefits and pitfalls. The class I present here uses the bilinear transform.

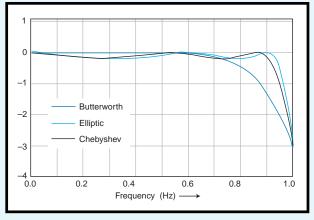

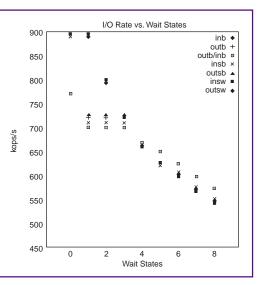

The nonlinear mapping inherent in this transform compresses the frequency response. The critical filter frequencies can be moved slightly to compensate for the magnitude response compression, but in most cases, the phase response is noticeably distorted. Figure 1 shows a linear-phase filter response before and after the bilinear transformation. Because of its inevitable phase distortion, this transform is not suitable for modeling linear-phase or flat group-delay filters.

Predistortion or prewarping is often applied to the original filter so the transformed filter's magnitude response looks like the original. Prewarping is done by shifting the *s*-domain cutoff frequency before transformation to force the transformed filter's cutoff to occur at the correct frequency.

The new cutoff frequency is given by:

$\omega = 2 f_{sample} \times tan \left( \frac{1}{2} \times \frac{\Omega}{f_{sample}} \right)$

where  $\Omega$  is the discrete-time frequency and  $\omega$  is the corresponding continuous-time frequency.

#### QUANTIZATION ERRORS

Although a single section can be used to realize any filter order, coefficient quantization is an important consideration. In a single-section filter, each pole or zero contributes significantly to the coefficients of the difference equation.