# CERCENCE APPLICATIONS JOURNAL

# #102 JANUARY 1999 EMBEDDED PROCESSORS

Custom Processors: The Price/Performance Tradeoff

Communication Between Multiple Processors

Timing Functions with a TPU Coprocessor

Embedded Java Made Easy

# TASK MANAGER

# Everything Old is New Again

ut with the old, in with the new-isn't that what we tend to say at the beginning of a brand new year? But this time 'round, it gives me pause. It's true that we're starting a brand-new year, but it's the last one of the century, last one of the millenium, and that's an odd feeling.

OK, OK, Yes, I'm educated. Yes, I've heard that the new millenium doesn't really start until January 1, 2001. But give me a break. Most people don't think that way. Twelve months from now, everyone's either going to be wildly singing, "We're gonna party like it's 1999," or huddling under their mattresses with their savings and flipping out over the Y2k bug. We're not going to be thinking too seriously about pronouncements from all those prescriptivists who are so determined that we say things 100% accurately.

Well, at least I'm not going to. I'm more determined to celebrate this special, once-in-a-lifetime event. It's the event I've been waiting for since I was a child. The event I've been waiting for since I could add up how many years old I was going to be when the calendar did its cartwheel into 2000. So, with the clock ticking down and only 12 months to go, my question is, how to prepare for it?

In one respect, we (the publishing, editorial types) prepare for these things way ahead of time. For example, the Circuit Cellar 1999 Editorial Calendar has been set for many months already. But it's only now that you, the reader, are starting to see it in action. It's only now that you are starting to see how Circuit Cellar is going to celebrate this special year.

We start off with this issue on embedded processors, and when next month arrives, we'll see some real-world applications of fuzzy logic. And following that, it's a spring whirlwind of informative issues on automation and control, DSP, measurement and sensors, and communications.

As we get into summer, you'll be sitting in the sun, seeing what's cool in the robotics field as well as the latest techniques and tools for development and debugging. September brings the embedded apps issue (just right for heading back to school), and in October, we'll be hearing more about software algorithms. Getting back to dealing with the bumps and hassles of the real world, November deals with analog problems. And, in the last issue of 1999, the focus will be on embedded interfacing.

Hey, wait a sec! All this doesn't sound so new, does it?! Uh-oh. Do you mean to tell me that for all this talk of brand-new year and a special way of celebrating the century, we've scheduled more of what we've been doing all along? Hmm... Well, on second thought, that's probably the best possible way for us to pay tribute to the years that have treated us so well. And, it's a good way for us to remind you that we're committed to providing the same quality of editorial in the future.

I hope you enjoy a productive 1999, and I wish you a happy new year!

R THE COMPUTER APPLICATIONS JOURNAL

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot

ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella CHIEF FINANCIAL OFFICER

**TECHNICAL EDITORS** Michael Palumbo Rob Walker

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ingo Cyliax Ken Davidson

Fred Eady NEW PRODUCTS EDITOR Harv Weiner

Ingo Cyliax

Jeannette Ciarcia ART DIRECTOR KC Zienka

**ENGINEERING STAFF** Jeff Bachiochi

**PRODUCTION STAFF** Phil Champagne John Gorsky James Soussounis

> PROJECT EDITOR Janice Hughes

EDITORIAL ADVISORY BOARD

Norman Jackson David Prutchi

Cover photograph Ron Meadows-Meadows Marketing PRINTED IN THE UNITED STATES

ADVERTISING ADVERTISING SALES MANAGER Bobbi Yush (860) 872-3064 ADVERTISING COORDINATOR

Valerie Luster

(860) 875-2199

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

FAX: (860) 871-0411

Fax: (860) 871-0411 F-mail: val.luster@circuitcellar.com

### CONTACTING CIRCUIT CELLAR INK

SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION

TELEPHONE: (860) 875-2199 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com

EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066 THOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions.

P.O. Box 698. Holmes. PA 19043-9613 or call (800) 269-6301. Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK®.

Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

| 14 | Multiprocessor Communications           Part 1: Methods for Communicating           Stuart Ball |                                                                                                                                       |                                                                    |    |

|----|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----|

| 20 | Ana                                                                                             | <b>Developing a Custom Integrated Processor</b><br>Analyzing the Price/Performance Tradeoff<br><i>Joe Circello and Sylvia Thirtle</i> |                                                                    |    |

| 26 |                                                                                                 | <b>Using Java in Embedded Systems</b><br>Vladimir Ivanovic and Mike Mahar                                                             |                                                                    |    |

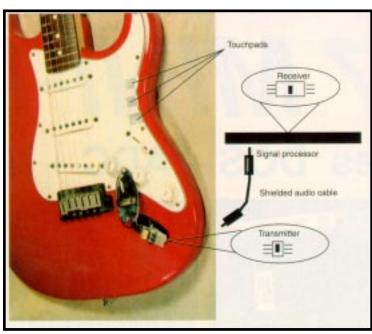

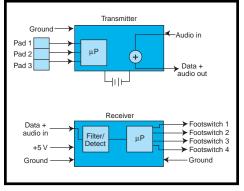

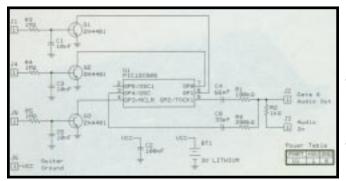

| 36 | Gu                                                                                              | <b>Music at Your Fingertips</b><br>Guitar Effects via Remote Control<br><i>Hank Wallace</i>                                           |                                                                    |    |

| 62 | The<br>Goi                                                                                      | e <b>PCL3013 Step/Servo Motor Controller in Action</b><br>rdon Dick                                                                   |                                                                    |    |

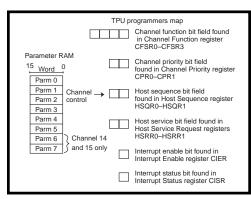

| 68 | <b>±</b>                                                                                        | <b>MicroSeries</b><br>TPU<br>Part 1: A Coprocessor for Timing Functions<br><i>Joe DiBartolomeo</i>                                    | Task Manager<br>Elizabeth Laurençot<br>Everyhting Old is New Again | 2  |

| 76 | <u></u>                                                                                         | <b>From the Bench</b><br>Can You Feel the Beat?<br><i>Jeff Bachiochi</i>                                                              | Reader I/O                                                         | 6  |

| 80 | <u>الم</u>                                                                                      | <b>Silicon Update</b><br>Wires, Wires Everywhere<br>The RF Solution                                                                   | New Product News<br>edited by Harv Weiner                          | 8  |

|    |                                                                                                 | Tom Cantrell                                                                                                                          | INK On-line                                                        | 12 |

|    |                                                                                                 |                                                                                                                                       | Advertiser's Index/<br>February Preview                            | 95 |

|    | S                                                                                               | SUET                                                                                                                                  | Priority Interrupt<br>Steve Ciarcia<br>'Net Worth                  | 96 |

|    | 42 Nouveau PC<br>edited by Harv Weiner                                                          |                                                                                                                                       |                                                                    |    |

|    | 17 RP                                                                                           | Embedded RT-Linux<br>Part 4: Developing Under Linux gcc/gdb<br><i>Ingo Cyliax</i>                                                     |                                                                    |    |

|    | 56 AP                                                                                           | C <b>Applied PCs</b><br>In the Face of Medusa<br>Part 2: A Whole New Solution<br><i>Fred Eady</i>                                     |                                                                    |    |

# **READER** I/O

# COULD I SEE YOUR LICENSE, PLEASE?

For some years now I've followed Linux and considered its use in embedded systems. I found the Embedded RT-Linux (*INK* 100) article to be both timely and informative.

However, an unfortunate error occurred where BSD versus GNU GPL licensing was discussed. Although the BSD kernels follow a different licensing scheme, the Linux kernel *is* GNU GPL protected.

Aside from the brief mention that components developed for a GNU GPL-protected system don't fall under the GNU GPL license, the problem concerns the use of the GNU C library in embedded (especially ROMed) applications.

This problem has received a lot of attention recently because the GNU C library is protected under a modified license, the GNU LGPL (Library General Public License). The GNU LGPL states that if you distribute binaries that are linked with the GNU C library, you must make available linkable objects (or the source) to your binaries so any downstream users can recompile and/or relink your code with any updated GNU C libraries that are available. This way, downstream users aren't locked into a particular revision of the GNU C library that was linked into a vendor's closed-source application.

Linking with a library was seen as producing a derivative work. This would have forced GNU GPL licensing issues on the original code, making the GNU C library almost useless for most commercial developers.

So that the FSF software would get some use, the GNU LGPL was created. Object code generated by the GNU C compiler from your source isn't considered a derivative work. Therefore, using the gcc compiler to generate code doesn't place you under the GNU GPL.

GNU LGPL was designed to deal with desktop workstation situations where the GNU toolset is installed by default, enabling end users to relink an application (given the linkable objects) or use dynamic linking with distribution-supplied shared libraries. But, an embedded system that boots from read-only media immediately runs afoul of the GNU LGPL. Choosing an alternative library and runtime enables you to ROM an application without violating the FSF licenses.

In the case of an embedded system that includes enough facilities (writable filesystems, and a console interface or remote network attachment), supplying linkable application objects and the tools and instructions necessary to relink the application (or use the shared libraries) should be sufficient to be compliant with the GNU LGPL. This isn't meant to scare anyone away from freely available software, but a little time spent reading and understanding licenses is time well spent.

# Dave New

newd@esi.com

You're right about the GPL issue. Because I'm not a lawyer, I wanted to concentrate on the technical issues and just mention that, in contrast to Net/ FreeBSD, Linux is GPL licensed. Also, Pat Villani discusses some of the issues in INK 95–96.

Anyone developing commercial products should consult a lawyer for advice on legal issues about GPL licensed code or license agreements of other codes. Because the situation may be different for each project, this is the best way to make sure the intellectual properties of the project are protected. Unfortunately, that's the way it is in this business.

Ingo Cyliax

# **IS THAT ALL I GET?**

I enjoyed the article by Alberto Ricci Bitti about the Graphing Data Logger (*INK* 99), but it left me wanting more—more description of the protocol that the FX9750G uses. Does the Casio FX7400G share the same protocol? What links are available for describing Casio features? What links did Alberto find? What kinds of projects are Circuit Cellar readers undertaking with respect to the Casio/PIC combination?

# Gus Calabrese

wft@frii.com

Editor's note: Any thoughts on the topic? We'd love to hear from you. Send any correspondence to editor@circuitcellar.com.

Editor's note: Thanks to James Horton for noticing that the www.res.gatech.edu/~bdixon/rtlinux and www.r52h146.res.gatech.edu/~bdixon/rtlinux URLs mentioned at the close of "Embedded RT-Linux" (INK 100) didn't work. Although they were current when Ingo wrote the article, it doesn't take long for things to get outdated. Now, there's an official RT-Linux site (www.rtlinux.org) with links to projects, documentation, and downloadable modules for different Linux distributions.

# NEW PRODUCT NEWS Edited by Harv Weiner

# **MULTIPLE TAPE BACKUP UNIT**

Ultera Systems has announced plug-and-play mirroring controllers for producing two or more backup tapes as quickly as one. The **Imager** series of controllers appears to have a single drive or autoloader but actually mirrors the data being backed up onto two drives or two autoloaders, running them at their maximum recording speed. By cascading the devices, a user can produce four, six, or more copies simultaneously without a sacrifice in speed.

The Imager series includes two models. Imager 1 operates at up to 20-MBps burst rate over a SCSI I or SCSI 2 host channel, and records at up to 10 MBps onto two individual drives or two autoloaders. Imager 2 runs at up to 40 MBps from the host and to the drives and also supports the robotics for controlling tape libraries. Any SCSI tape drive and any backup software can be used with either system.

Imagers can be managed on-line through a GUI that is compatible with Windows 95, 98, and NT and with DOS. Imagers can also be operated off-line through their own control panel for tape copying, comparing or verifying. Internal half-height 5.25", desktop, and rack-mount units are available.

Pricing for the Imagers begins at \$2445.

Ultera Systems (949) 367-8800 Fax: (949) 367-0758 www.ultera.com

# BATTERY MONITOR IC

The **DS2436** battery identification chip provides a convenient method of tagging and identifying battery packs by manufacturer, chemistry, or other identifying parameters. The chip enables the battery pack to be coded with a unique two-byte identification number, and it stores information about battery life and charge/discharge characteristics in its nonvolatile memory. Applications include cell phones, audio/video equipment, data loggers, scanners, and other hand-held instruments.

The DS2436 integrates a 10-bit voltage ADC and 13-bit temperature-sensing circuitry that monitors battery temperature without requiring a thermistor in the battery pack. A cycle counter manages battery maintenance intervals and helps the user to determine the remaining cycle life of the battery.

The DS2436 also measures battery voltage and sends the measured value to a host CPU. This feature is useful for end-of-charge or end-of-discharge determination or for basic fuel-gauge operation. Information is sent to and from the DS2436 over a one-wire interface, so the battery packs need only have three output connectors: power, ground, and the one-wire interface.

The DS2436 sells for \$4.10 in quantities of 1000.

Dallas Semiconductor (972) 371-4448 Fax: (972) 371-3715 www.dalsemi.com

# PC DATA INTERFACE ADAPTERS

A PC can now be used to log data from GPS satellites, depth sounders, radar, and other marine navigational devices with the latest data interface adapters from B&B Electronics. The plug-in connectors convert NMEA (National Marine Electronics Assn.) standard data signals so they can communicate with any RS-232/-422/-485 device, such as a PC or printer.

Two adapter models are provided to suit either the older NMEA or the latest NMEA specs. Model 183COR converts the data signal from the older version of the specifications (NMEA0183 V.1.x) to EIA RS-232/ -422/-485 signals. Model 183V2C is for NMEA0183 V.2.x, which is the latest version of the NMEA specification. The 183V2C converts one data signal in each direction between NMEA0183 and EIA RS-232.

The adapter model sells for \$99.95 each.

**B&B Electronics Mfg. Co.** (815) 433-5100 Fax: (815) 434-7094 www.bb-elec.com

# PORTABLE EMBEDDED GUI

The PEG (Portable Embedded GUI) library is a professional-quality graphical user interface library created for embedded-systems developers. It is small, fast, and easily ported to virtually any hardware configuration capable of supporting graphical output. The default appearance of PEG objects is almost identical to common desktop graphical environments.

The PEG library is written in C++ and implements an event-driven programming paradigm at the application level. Each control type is built incrementally on its pre-

decessor, enabling users to select and use only objects that meet their requirements. The PEG library provides an intuitive and robust object heirarchy. Objects may be used as provided or enhanced through user derivation.

PEG provides a

1.00

ament Fund: 57 Paint Shoper

set of hardware and OS encapsulation classes, so the PEG user interface can run as a standard 32-bit Windows application.

PEG includes two PC executable utility programs. PEG Font Capture enables users to convert standard

font files into a format required by PEG, and PEG Image Convert converts standard .pcx, .bmp, and .tga images into a compressed format supported by the PEG bitmap functions.

PEG is designed to work with any compiler/debugger combination. There are no internal restrictions on CPU type or hardware configuration. It currently supports standard EGA/VGA, SVGA, and LCD (320 ×  $240 \times 4$  color grayscale) video controller/display resolutions. PEG is designed to work with any combination of mouse, touchscreen, or keyboard input.

PEG is licensed on a per-developed-product basis, eliminating royalty fees. It is delivered with full source code, several example application programs, hardware

14

interface objects for several common video configurations and input devices, and thorough documen-

tation.

The cost of \$5000 includes six months of free support.

Micro Digital, Inc. (800) 366-2491 (714) 373-6862 Fax: (714) 891-2363 www.smxinfo.com

# GLOBAL COMMUNICATION DEVELOPMENT SYSTEM

The **GC1100** developmentsystem integrates an embedded controller, GPS receiver, communications modem, and a user-command interface to enable the rapid design of tracking systems for a wide variety of GPS applications. The GC1100 is ideal for GPS-based fleet management, AVL, or asset-tracking systems.

The GC1100 contains a motherboard, an Ashtech G8 receiver, a Motorola 505SD modem that allows ARDIS Packet Data, an operator display interface, 32 digital user I/O lines, eight analog user inputs, and an active GPS antenna (15–30-dB gain). Also, prewritten software provides instant communication among all of the components.

The GC1100's high I/O count provides many options for user-specific applications. Digital and analog I/O enable monitoring several aspects of vehicle status, ranging from engine performance, cargo integrity and temperature, to fuel stops and door openings. Also, messages to and from the dispatcher and driver can be sent and displayed as text. The variety of I/O enables easy interfacing as well as connecting and monitoring digital and analog sensors.

The development system is available without a receiver or modem and can accomodate a variety of receivers.

The individual package includes a modem and receiver and sells for **\$1895.**

# Z-World (530) 757-3737 Fax: (530) 753-5141 www.zworld.com

# SINGLE-CHIP DATA LOGGER

The **EDE702** serial LCD interface IC permits almost any text-based liquid crystal display screen to be controlled via a one-wire serial link. The chip, from E-Lab Digital Engineering, is ideal for embedded microcontroller applications where minimal I/O pin usage is desired.

The EDE702 enables full LCD control, including the creation of custom characters, scrolling text, cursor on/off, and so forth. With transfer rates of 2400 and 9600 bps as well as selectable data polarity, the chip can interface to almost any microcontroller that is capable of sending asynchronous serial data.

Another plus for designers is that this microcontroller connection can be made without any type of voltage-level conversion hardware.

With the EDE702, circuit designers can easily add an LCD screen to their design without being concerned with the increased software overhead or I/O requirements that typically accom-

pany an 11-pin LCD interface. A serially controlled digital output pin makes the one-pin serial interface effectively a zero-pin interface.

The EDE702 is available in 18-pin DIP or SOIC packages, and it sells for **\$4.50** in quantities of 1000.

E-Lab Digital Engineering (816) 257-9954 Fax: (816) 257-9945 www.elabinc.com

# UNIVERSAL SECURITY DEVICE

The **Safety Claw** is a universal lock for any drive on a PC or workstation. This device enables disk drives to be protected whether they're on a desktop or tower PC. All other drives, including CD drives, streamers, Zip drives, MO, or Syquest, can be reliably secured against unauthorized use whether they're installed in a PC or as an external drive.

The Safety-Claw's security plate is affixed to the PC or external drive casing, and its bar is inserted to block the drive. The Safety-Claw protects the PC or external drive from robbery if the user inserts a steel cable through the loop in the bar and attaches the protected device to another firm object.

Additional uses of the Safety-Claw include preventing a scanner or copier lid from being opened or avoiding the unauthorized use of an interface and/or removal of the cable on any device.

There are 200 different keys available for the Safety-Claw, and keyed-alike systems can be ordered. The steel bar of Safety-Claw is 6 mm in diameter, so it is extremely difficult to cut.

The Safety-Claw sells for \$29.95.

Interface Security Solutions Corp. (800) 254-4392 (203) 743-1228 Fax: (203) 743-1458 www.crocodile.de

# FEATURES

# FEATURE ARTICLE

# **Stuart Ball**

# Microprocessor Communications

Part 1: Methods for Communicating

Communication is tricky no matter what, right? But when you have several processors involved, well, it just gets worse. Stuart begins this two-part series by looking at ways to get the messages between processors on a single backplane. lthough most embedded applications can be handled with a single processor, every now and then, you find a job requiring a system with two or more

processors. Nearly every multiprocessor design needs a way for the processors to communicate. In this series, I look at the different methods for communicating between processors and the various

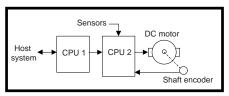

tradeoffs involved. To start off, I'll look at useful approaches when two processors share the same PC board or backplane. Let's say the processor communicates with a higher-level system, like a PC, and distributes commands to a lower-level processor that controls a DC motor (see Figure 1).

CPU 1 talks to the host system, and CPU 2 controls a DC motor, under the

Figure 1—Although it's rather simple, this block diagram is representative of a typical multiprocessor application

Figure 2—Note that CPU 1 performs two writes to the register for every bite transferred. The first write clocks the data in, and the second one toggles the most significant bit as a strobe.

control of CPU 1. CPU 2 senses the motor position via a shaft encoder and gets other sensor inputs as well.

In a typical real-world scenario, you might find this arrangement if CPU 1 needs to execute slow, complex tasks in response to the host, and CPU 2 has to execute fast, simple tasks to control the motor speed or position. You may find CPU 1 controlling multiple processors like CPU 2.

Clearly, CPU 1 must communicate with CPU 2 to get this job done. This requires commands like turn motor on, turn motor off, set motor speed to *x*, and start motor when sensor *y* goes active.

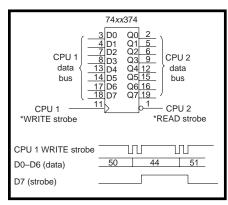

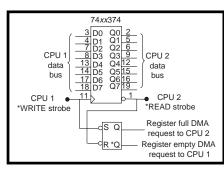

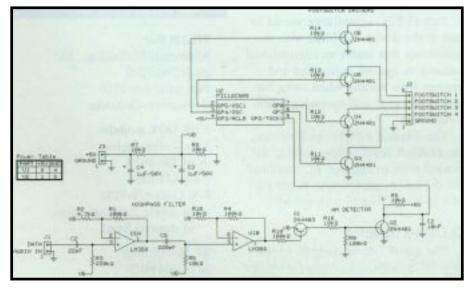

Figure 2 shows one method of communicating between processors. The circuit is an 8-bit register written by CPU 1 and read by CPU 2. The register is a 74xx374 (xx = LS, HC, ACT, etc.), but this scheme can be implemented in programmable logic or with any register that has tristate outputs.

The D inputs to the register connect to the data bus of CPU 1 (or to the lower 8 bits if CPU 1 is a 16- or 32-bit processor). The clock input (pin 11) connects to a write strobe from CPU 1. The write strobe is the same type you'd use to clock data into any register or a peripheral IC, and it goes low when CPU 1 writes to the specific address where the communication register is located.

The register's Q outputs connect to CPU 2's data bus. When CPU 2 wants to read the register, it generates a low-going read strobe (a decoded address strobe) at the register's Output Enable (pin 1). This strobe enables the tristate outputs, so CPU 2 to read the register data. As Figure 1 shows, only seven bits of the register are used for transferring data. The eighth bit (D7/Q7) is a strobe that indicates when data is available.

The strobe bit is needed because CPU 2 may read the register anytime, including the exact instant when CPU 1 is writing to it. As you see from the timing diagram, when CPU 1 wants to change the register, it executes two write operations. The first write sets the lower 7 bits (D0–D6), and the second write toggles the strobe bit, D7, without changing D0–D6 again.

CPU 2 only reads data when it sees the strobe bit change state. So, if CPU 2 happens to be reading the register when CPU 1 is updating the data bits, CPU 2 won't see a change on the strobe bit and will ignore the data. If CPU 2 reads the register at the exact instant that CPU 1 is changing the strobe bit, it won't matter if CPU 2 sees the change, because the data bits are already stable.

Let's say you defined some commands for the control system as in Table 1. As Figure 2 shows, CPU 1 previously sent a Motor On command. This command is followed by a command to set the speed to 4, followed by a Motor Off command. Each new command changes the state of the strobe bit.

The advantage to this scheme is simplicity. A single 8-bit register is used and may be embedded in an FPGA or ASIC, or it may be implemented with a multibit parallel I/O IC. Of course, 16- or 32-bit processors can use wider registers.

A simple system may not even need a command structure. Instead, it can assign a separate bit to each function. Two-way communication can be implemented with a second register, written by CPU 2 and read by CPU 1.

Unfortunately there's no feedback to tell CPU 1 when CPU 2 has read the data. This drawback has serious implications for the system's throughput.

Say CPU 2 checks the register every 10 ms in response to a timer interrupt. CPU 1 can't send data any faster than this or CPU 2 may miss a byte.

If CPU 2 polls the register on an irregular basis, such as in a background loop, then the fastest thatCPU 1 can send data is the longest time it takes

|   | Code<br>(hex) | Command                                      |  |

|---|---------------|----------------------------------------------|--|

| - | 4 <i>x</i>    | Set motor speed to x $(x = 0 \text{ to } F)$ |  |

|   | 50<br>51      | Turn motor on<br>Turn motor off              |  |

Table 1—These are some examples codes for various control commands.

CPU 2 to execute the loop.

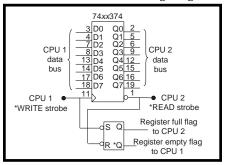

# **REGISTER WITH FLAG**

To achieve faster throughput, the circuit in Figure 3 adds a set/reset flip-flop to the basic register circuit. The flip-flop is set when CPU 1 writes to the data register and reset when CPU 2 reads the register. The flip-flop can be constructed from a pair of NAND gates, or it can be half of a 74xx74 with the clock and D inputs grounded.

The flip-flop's output is provided to both processors so it can be read as an empty/full flag for the data register. It can connect to a status register or to a microcontroller port bit.

To use this scheme, CPU 1 writes something to the register. CPU 2 sees the data available (because the flip-flop was set) and reads it. CPU 1, polling the flip-flop output, sees it go low and knows that the register is empty and ready for another byte of data.

Now, the basic register circuit is morecomplex but the potential throughput is greatly increased . The maximum throughput is still limited, though, because both CPUs must poll the empty/full bit.

For example, if CPU 2 still polls for data once each pass through a background loop, the worst-case transfer rate is the same as in the single-register

Figure 3—Adding a set/reset flip-flop improves the efficiency and speed of the register-based communication method by providing an empty/full status to the two CPU's

Figure 4—A FIFO provides a very fast interface

implementation. The maximum rate at which data can be transferred increases because CPU 1 can transfer data at the actual polling rate instead of at the slowest possible rate. The price is that both CPUs must have an available port bit or status input to read the empty/full flag.

# **INTERRUPT-DRIVEN SYSTEM**

You can improve performance by connecting the outputs of the set/reset flip-flop of figure 3 to an interrupt on each CPU (instead of to status bits). CPU 2 gets an interrupt when the register is full, and CPU 1 gets an interrupt when the register is empty. Be sure you get the polarity of the interrupts correct if you make this change.

This scheme greatly increases the potential data throughput. The maximum data rate becomes the sum of the interrupt latency and processing time for both processors. The price for this approach is the need for one free interrupt on each CPU (two if a reverse path is also implemented).

There's also the potential for CPU 2 to get hammered with constant interrupts if CPU 1 has a lot of data to send. One way around this is to have CPU 2 turn off the communication interrupt

Figure 6—If the processors support it, adding DMA to the register-based scheme provides extremely fast, lowoverhead communication.

during critical processing. However, this approach decreases the overall throughput.

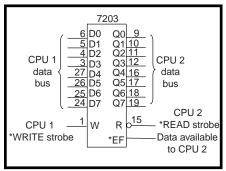

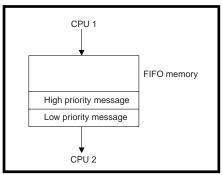

# FIFO

Figure 4 shows a FIFO interface. This example uses a 7203, which is a  $2 \times 9$ -KB FIFO. The 7203 is an industrystandard part from a family of parts available in 512 × 9-KB, 1 × 9-KB, 2 × 9-KB, and up. This example circuit doesn't show all the 7203 pins, just those we're interested in here.

The 72*xx* family of FIFOs contains an internal SRAM and logic to control access to the RAM. Data written to the FIFO input by CPU 1 is placed in the internal FIFO memory. Any time the FIFO is empty, the Empty Flag (EF) output is low. If the FIFO is not empty, EF is high.

The incoming data is stored so that CPU 2 reads it out in the same order it was written. So, the FIFO acts as a deep register that allows CPU 1 to write multiple bytes without worrying about how fast CPU 2 is reading them.

To use this method, CPU 1 typically writes a complete, multibyte message to the FIFO. When EF goes high (not empty), CPU 2 reads the data. This type of interface requires very little overhead from the processors. The rate at which CPU 1 sends data is not limited to the rate at which CPU 2 reads it.

The first drawback to this system is a throughput limitation. Although CPU 1 can send a message without worrying about how fast CPU 2 can read it, the average transfer rate can't exceed the capacity of CPU 2. If it does, the FIFO fills up and data is lost. So, the FIFO doesn't really increase the overall data throughput, it just decreases the overhead of transferring the data.

A second problem with the FIFO interface is time delays. If CPU 1 sends a command, such as Motor Off, there may be a delay before CPU 1 reads the message and acts on it. With registerbased approaches, CPU 1 always knew CPU 2 was reading data as it was sent. But with the FIFO design, that's no longer the case.

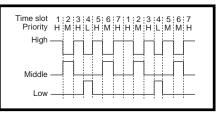

The third problem is relates to the second and involves message priorities. Suppose this hypothetical system had messages of differing priorities. The normal Motor Off command may allow the motor to coast to a stop, but there's an Emergency Stop command that brakes the motor instantly.

If Emergency Stop is received, you presumably want to service it immediately. If the interface uses a FIFO, there's the possibility that commands can stack up in it, as shown in Figure 5. A low-priority command, like a speed change, can be in front of a command such as Emergency Stop.

Suppose that your command set consists of long, multibyte messages and that the software in CPU 2 reads the first byte of each command to see what kind of command it is. If the command is low priority, like a speed change, the software may decide to read and process the command later. This decision leaves the possibility that Emergency Stop won't be acted

Figure 5—It's possible for a high priority message to stack up behind lower priority messages in a FIFO This situation can cause thehigh-priority message to be serviced later than expected.

on right away if it's behind a lowpriority command in the FIFO.

The solution to this priority problem is for CPU 2 to read all messages as soon as they are received. Lower priority messages can be stored for later execution, and high-priority messages can be executed immediately. The drawback is that all messages must be treated as high priority because any message could have a highpriority message stacked behind it.

# DMA-BASED INTERFACE

Some microprocessors, such as the '186 and '386EX, have built-in direct memory access (DMA) controllers. For these applications, the circuit in Figure 6 eliminates nearly all of the disadvantages I've described so far. This circuit goes back to the register-andflip-flop approach, but with a twist.

Figure7a—If CPU 2 is much faster than CPU 1, CPU 2 may detect the register full condition and read the data while CPU 2 is still performing a write cycle. This results in the register full condition remaining active and CPU 2 reading two bytes instead of one. **b**—By connecting the CPU 1 write strobe to the clock input of the status flip-flop (instead of the SET input), the status flip-flop is not set until the end of the write cycle. **c**—The change prevents the race condition from occurring, regardless of the relative CPU speeds.

In Figure 6, the flip-flop outputs do not connect to status bits or to interrupt inputs. They connect to the DMA request signals on both processors. CPU 1 receives a DMA request when the data register is empty and CPU 2 gets one when the register is full.

Let's look at three ways to implement this interface in software. First, all messages have a predefined length (16 bits, 32 bits, etc.). Shorter messages are padded out to this length. CPU 2 sets up its DMA controller to transfer one complete message. When CPU 1 wants to transfer data, it tells its DMA controller to send the block of memory to the data register. As each byte is sent, the DMA request to CPU 1 goes inactive and the DMA request to CPU 2 goes active. When CPU 2's DMA controller reads the byte, the DMA requests swap states again and CPU 1's DMA controller sends the next byte.

After the entire message is received, CPU 2 gets an interrupt from its DMA controller and processes the received data. The entire transfer is accomplished in a few tens of microseconds, although the processing may take longer.

If your application requires variablelength messages, you can define each message so the first byte defines the length. As before, CPU 1 sets up its DMA controller to send the entire message. CPU 2 has already set up its DMA controller to transfer a single byte.

When the first byte of the message is sent, CPU 2 gets an interrupt (from its DMA controller) and reads the byte. CPU 2 then sets up its DMA controller to transfer the rest of the message based on the length byte. This method enables variable-length messages to be sent, but CPU 2 now has to service two interrupts for each message and the maximum transfer rate is slower.

The third method is for CPU 2 to set its DMA controller to transfer more data than the longest possible message. When CPU 1 sends data, it gets an interrupt (from its DMA controller) indicating that the transfer is complete.

CPU 1 notifies CPU 2, via another interrupt path, that a message is available. CPU 2 then reads the length from its DMA controller pointer registers and processes the message normally.

In a DMA scheme, CPU 2 sets up a block of memory as a buffer for the DMA data. For example, if each message is 16 bytes in length, CPU 2 can set up a 256-byte block of memory that contains 16 message buffers.

Using DMA also avoids the FIFO priority issue in two ways. First, the transfers are executed directly to memory in hardware, making the process of reading the data less of a bottleneck. Second, if CPU 2 uses multiple buffers, lower priority messages can be left in their buffers until they are acted on, whereas high-priority commands can be executed immediately.

Even if only one of your CPUs has built-in DMA, you can take advantage of this approach. The CPU with DMA can transfer messages using DMA, eliminating the overhead of polling or servicing one interrupt per byte. While you won't get the throughput of a dual-DMA design, sometimes you get simpler software with this approach.

With any DMA-based approach, make sure the timing of setting and resetting the flip-flop meets the requirements for the DMA controller. The primary drawback to this approach is that one or both processors must have DMA capability.

The primary advantage is extremely fast data throughput, and although it's probably not worth changing processors just to use this technique, it can provide a fast communication path if the processors support it.

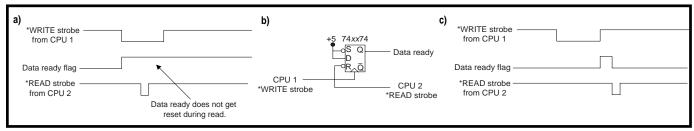

# RACE CONDITION

All the variations of the register-andflip-flop design are susceptible to a race condition if one processor is considerably faster than the other. In Figure 7a, CPU 2 is much faster than CPU 1, so CPU 2 sees the flip-flop get set and reads the data while CPU1 is still writing to the register. As a result, the flip-flop doesn't get reset properly.

A typical scenario where this might occur is if CPU 2 is a very fast DSP

communicating with a slower generalpurpose microprocessor.

The solution: use a synchronous design (where evrything is referenced to one of the CPU clocks) or use a clocked flip-flop. Figure 7b shows how a flip-flop like the 74xx74 would be connected to fix the timing problem.

Figure 7c shows the new timing. Because the write strobe from CPU 1 is connected to the clock input of the 74xx74, the data ready flag doesn't get set until the end of the write cycle, eliminating any timing conflict.

# **DUAL-PORT RAM**

I also want to mention dual-port RAM (i.e., RAM that can be accessed by either processor). One option is to use an off-the -shelf dual-port RAM IC with two addresses and data buses. You can get controller IC's that convert standard RAM devices to dual port.

The second method is to use the existing RAM associated with one of the processors. This approach is simpler than an external RAM, but it can affect the throughput of both processors. All of these approaches can be mixed and matched. For instance, if your application has a CPU 1-to-CPU 2 interface that requires long data messages at high rates, you might implement a DMA controlled register for that interface. The return path, from CPU 2 back to CPU 1, might carry only infrequent status bytes, so it may be a simple polled register interface.

Next time, I'll look at methods you can use if your processors must communicate over a greater distance.

Stuart Ball works at Organon Teknika, a manufacturer of medical instruments. He has been a design engineer for 18 years, working on projects as diverse as GPS and single-chip microcontroller designs. He has also written two books on embedded-system design. You may reach Stuart at sball85964@aol.com.

# REFERENCE

S. Ball, Embedded Microprocessor Systems, Real World Design, Butterworth-Heinemann, Newton, MA, 1996.

# Developing a Custom Integrated Processor

Joe Circello & Sylvia Thirtle

# Analyzing the Price/Performance Tradeoff

If standard processor configurations aren't quite what you need, consider a processorindependent core. Joe and Sylvia bring to your doorstep a customizable core, so you can manipulate valuable variables in the price/performance equation ew uses for advanced embedded microprocessors are emerging everywhere, especially in the highly competitive, fast-paced market of consumer electronics. Thanks to cooperative efforts with silicon vendors, embedded-system developers can manipulate powerful variables in the price/performance equation that were previously beyond their control.

Optimizing an embedded processor presents an earnest challenge and it requires the system designer to perform a delicate balancing act between performance and cost. Ultimately, this approach produces an embedded-processor solution that is fine-tuned for a given system and/or application.

# **DESIGN MODELS**

With the traditional system design model, the engineer remains at the mercy of standard product offerings from the semiconductor vendor. A chipmaker's catalog of standard processor configurations may or may not include precisely what's required for a given application.

With a standard product, system designers may have to pay for functions

(and silicon) they'll never use. Additionally, the device may lack certain functions that could significantly enhance the system performance of a given application if integrated on-chip.

But, a new system design model is emerging, brought on by the availability of modular, fully synthesizable, process-independent microprocessor cores. For the first time, design engineers have unprecedented control over defining and configuring embedded processors.

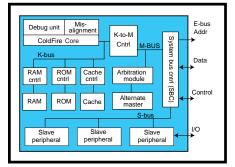

Customizable cores, like the Motorola ColdFire family, can be cost-effectively tailored to meet the demands of specific applications. The ColdFire architecture was developed to address this class of applications.

Based on variable-length RISC technology, ColdFire combines the architectural simplicity of conventional 32-bit RISC with a memory-saving, variable-length instruction set. In defining the ColdFire architecture, Motorola incorporated a RISC-based processor design and a simplified version of the variable-length instruction set found in the 68k family.

The result is a family of 32-bit microprocessors suited for those embedded applications requiring high performance in a small core size. The ColdFire family provides balanced system solutions to a variety of embedded markets. Here are some of the basic philosophies that have guided all ColdFire designs.

When it comes to small, fully synthesizable processor cores, developments are on track with a publicly announced performance roadmap reaching 300 MIPS by the year 2001. Using compiled memory arrays and 100% synthesizable designs enables

Figure 1—This generalized block diagram shows a custom integrated processor using a ColdFire core.

system designers to easily define CPU configurations.

Figure 1 depicts the standard ColdFire microprocessor configuration. The hierarchical bus structure and the modular architecture are apparent. You can add other logic, in the form of predefined macros, from Motorola's library or synthesize your own proprietary circuits.

# MAXIMUM ARCHITECTURE

Fine-tuning a custom embedded processor for optimal price and performance requires some insight into the specific architecture's variables. The difficulty of this process is influenced by the sophistication of the silicon vendor's development environment as well as the system designer's ability to provide accurate, real-world application data for the target system.

For example, the system OEM may be able to provide information from a previous-generation system. The data can be a key piece of software that represents a critical execution path of the given application. If possible, the ability to extract the key software routines and recompile them for the target system makes the process much easier.

As an alternative, trace data captured from a previous-generation system can also provide critical information for sizing the processor's local memories (e.g., cache, RAM, ROM). These dynamic traces, whether captured from an earlier design or created by the application code running on a software simulator of the target system, are crucial for the price and performance optimization analysis.

# PREDICTING PERFORMANCE

Although ratings for microprocessors are expressed in MIPS, this number often fails to accurately predict the performance of an embedded microprocessor system for a given application. Many times, these ratings need a "mileage you get may vary" disclaimer. Unless the effects of the memory subsystems are taken into

| a) base CPI [cycles/inst] = summation {F(i) × ET(i)} +<br>sequence-related pipeline stalls                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>b) effective CPI [cycles/inst] = base CPI</li> <li>+ summation of memory factors</li> <li>+ summation of system factors</li> </ul>                                                                                                                                                                                                                                                                      |

| c) effective CPI [cycles/inst] = base CPI<br>+ IC_miss × IF × IF_stall<br>+ OC_miss × REF × OP_stall                                                                                                                                                                                                                                                                                                             |

| where the cache memory degradation factors include:                                                                                                                                                                                                                                                                                                                                                              |

| IC_Miss = Cache miss rate on instruction fetches (Miss/fetch)<br>IF = Instruction fetches per instruction<br>IF_stall = Time [cycles] the processor core is installed servicing<br>an instruction fetch miss<br>OC_Miss = Cache miss rate on operand fetches (Miss/OPFetch)<br>REF = Operand references per instruction<br>OP_stall = Time [cycles] the processor core is installed servicing<br>an operand miss |

| <pre>d) effective CPI = base CPI     + {(IC_Miss × IF) + (OC_Miss × REF)}     x {2 + 11 + 0.6 × (12 + 13 + 14)}</pre>                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                  |

Figure 2a—Here's the simplified expression for the processor's performance measured by effective CPI. b—This generic expression defines performance as measured by effective CPI. c—This more detailed equation defines effective CPI performance for a processor with cache memory. d—And, this is the effective CPI equation for the ColdFir2 V.2 and V.3 processors.

account, these simplistic ratings can't accurately indicate performance.

Today, more precise performance estimates of a hypothetical or actual processor core can be made. By taking specific system and memory subsystem variables into account, this methodology provides a more accurate representation of completely different CPU configurations and architectures.

The predicted performance of a processor can be developed using an average-instruction-time methodology. In its simplest form, this cycles per instruction (CPI) metric represents the number of machine cycles per instruction and is calculated for a single-issue architecture as:

$$CPI\left[\frac{cycles}{inst}\right] = summation\left\{F(i) \times ET(i)\right\}$$

where *CPI* is the average instruction time expressed in cycles per instruction, F(i) represents the dynamic frequency of occurrence per instruction, and ET(i)is the execution time for a given instruction *i*. By summing the product of relative frequency and execution time for each instruction type, the average instruction time for a processor executing any given instruction mix can be calculated. Consider the definition of a base average instruction time (base CPI). Let the base CPI represent maximum processor performance strictly as a function of the instruction mix. Stated differently, this metric represents the processor's performance assuming the rest of the system (caches, memory modules, etc.) is ideal.

Figure 2a shows the base CPI where the summation product was previously defined and the sequence-related pipeline stalls include all pipeline breaks caused by the instruction sequence. You can calculate the base CPI by summing the product of the relative frequency of occurrence and execution time for each instruction type plus the sequencerelated holds.

This base CPI provides a parameter to quantify the performance of a given processor microarchitecture. To convert this value into a more realistic measure of predicted system performance, you have to consider a series of degradation factors.

Let the effective average instruction time (effective CPI) represent this more realistic measure of performance. By quantifying the degradation factors associated with these other system components, the effective CPI can be calculated. As an example, the processor stalls resulting from cache misses typically represent the largest degradation factor in the effective CPI equation.

In Figure 2b, the calculated effective CPI is reached by summing the individual degradation factors. Let's

Figure 3—This diagram gives you an overview of the ColdFire performance-analysis methodology.

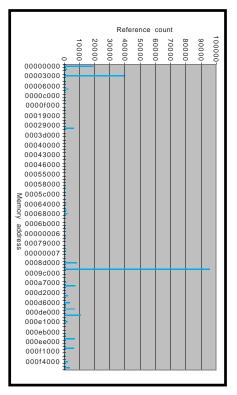

**Figure 4**—The operand address histogram is taken from a set-top box application.

define the memory subsystem factors as those associated with a cache memory, and assume the remaining system factors are negligible.

The effective CPI equation can then be rewritten as in Figure 2c. The first degradation term quantifies the CPI contribution due to instruction fetch cache misses, and the second term quantifies the operand reference cache misses.

The relative performance between two systems, *x* and *y*, can be expressed as:

### x performance

$\overline{y \text{ performance}}$  $\underline{y \text{ eff CPI}}_{x \text{ eff CPI}} \times \frac{y \text{ cycle time}}{x \text{ cycle time}} \times \frac{y \text{ executed insts}}{x \text{ executed insts}}$

where the first ratio defines the architectural factor, the second ratio is the technology factor, and the third ratio is the instruction set/compiler factor.

Using the system performance equation, you can analyze the relative performance of different generations of a microprocessor family, or compare different architectures. For benchmarks where the same binary code image is executed on different designs, the relative performance equation reduces to the product of the architectural and technology factors.

# MODELING TOOLS

Given CPI methodology, a number of tools have been developed to assist in this kind of performance analysis for the ColdFire architecture.

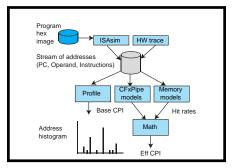

You can use a number of architectural models to analyze various factors within the effective CPI performance equation. These tools are typically high-level C language models of certain functions within the design and are driven with information from the ColdFire ISA simulator or trace data.

The ISA model is a C-language program that defines the expected results of execution of the instruction set architecture. By inputting a memory image file, the ISA model executes the program on an instruction-byinstruction basis, updating all programvisible machine registers and memory as required. This ISA model is instrumented to optionally output information on instruction fetch, operand addresses, and program counter values.

By executing the target application on the ISA simulator with the appropriate outputs enabled, a stream of data from the executing application can be input to one of the architectural models. This input data provides the required stimulus to the architectural models.

Processor pipeline models are used for base CPI analysis. There's also a program that gathers detailed statistics about dynamic opcode usage. Recalling the base CPI equation, this program provides the F(i) factors associated with the various opcodes for the application.

# ADDITIONAL ANALYSIS MODELS

The ColdFire cache model quantifies numerous performance parameters for various cache sizes, associativity, and organizations. It uses the stream of reference addresses generated by the simulator as input, and models the behavior of Harvard and unified caches of sizes from 512 bytes to 32 KB.

Additionally, the associativity can vary between two-way and four-way, and the operands can be mapped into copyback or store-through space. This model can also include a RAM, mapped to a specific region, for heavily-referenced operands or code segments. Mapping the active region of the stack frame to this type of RAM is often effective.

A second model provides information for memory address profiling. Using the stream of reference addresses as input, this model profiles the memory access patterns to identify critical functions and/or heavily referenced operand locations. For some systems, such profiling helps you understand the required amount of RAM as well as which variables to map into this space to maximize performance.

Of prime importance is verification of the architectural models. So, at various times throughout the analysis process, the accuracy of the architectural models is validated.

The V.2 processor pipeline architectural model was initially verified by comparing predicted base-CPI values versus those directly measured from silicon. Reviewing measured base-CPI values versus those predicted by the pipeline model, the error was less than a 0.5% difference across a large set of embedded benchmarks.

The cache architectural models were validated against the design descriptions for several ColdFire MPU designs.

Another area of interest is the modeling of the {IF,OP}\_stall times. These degradation factors represent the pipeline stall that occurs on a cache miss. For the nonblocking streaming cache designs of the V.2 and V.3 cores, these terms are modeled as:

{IF, OP}\_stall =  $(1 + t1) + 1.0 + 0.6 \times (t2 + t3 + t4)$

| Memory        | Relative    | Relative |

|---------------|-------------|----------|

| Configuration | performance | area     |

| 2-KB cache    | 1.00        | 1.00     |

| Z-ND Cache    | 1.00        | 1.00     |

| +4-KB RAM     | 1.05        | 1.19     |

| 4-KB cache    | 1.19        | 1.11     |

| +4-KB RAM     | 1.27        | 1.31     |

| 8-KB cache    | 1.52        | 1.32     |

| +4-KB RAM     | 1.61        | 1.52     |

| 16-KB cache   | 1.98        | 1.79     |

| +4-KB RAM     | 2.06        | 1.98     |

| 32-KB cache   | 2.71        | 2.71     |

| +4-KB RAM     | 2.91        | 2.91     |

Table 1—Here's the relative performance and area for various ColdFire configurations executing a set-top box application

where the response time of the external memory for a linesized fetch is specified as t1 - t2 - t3 - t4 when viewed from the microprocessor pins.

Using the equation in Figure 2d for the V.2 and V.3 designs, the relative error between the predicted and measured effective CPI

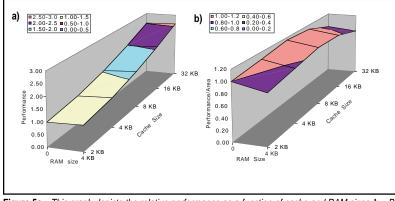

**Figure 5a**—This graph depicts the relative performance as a function of cache and RAM sizes. **b**—By contrast, this graph shows the relative performance per area as a function of cache and RAM sizes.

was less than 2% across a wide suite of embedded benchmarks.

Figure 3 summarizes the process. The architectural models are driven by trace data captured from existing hardware or from a compiled application executed on the instruction set simulator. The resulting streams of addresses and instructions are then input to the specific models.

The profiling tool determines any hot spots in the code or data areas that might be considered for placement in local RAMs or ROMs. The pipeline model produces the base CPI performance metric for a given version of the ColdFire microarchitecture.

The local-memory models determine all the performance parameters associated with the cache, RAM, and ROM modules. The miss ratios are based on size, organization, and the dynamic stream of reference addresses. The base CPI and memory parameters are combined to produce an effective CPI value that provides an accurate measure of predicted performance for a given configuration.

# OPTIMAZATION EXAMPLES

To see how the performance analysis procedure works, consider the following realworld examples.

To begin, let's say you are implementing a digital set-top box. By instrumenting an exist-

ing 68k system, trace data is captured for two critical execution paths.

The challenge is to determine the appropriate amount of local processor memories (cache and possibly RAM) to optimize price and performance for a V.3 ColdFire design. When implemented in 0.35-µm process technology, the V.3 core provides 70-Dhrystone, 2.1-MIPS performance when operating at 90 MHz.

The trace data is profiled to identify any potential hot spots that might benefit from placement in a RAM. The profile in Figure 4 shows several spikes representing heavily referenced operand areas.

The largest reference area is generally the system stack and the first candidate for mapping into a local RAM. Using the architectural models, the relative performance and area calculations across a range of cache and RAM configurations are given in Table 1. The reference design is a V.3 core with 2 KB of cache memory.

In Table 1, the relative performance ranges from  $1.0 \times$  to  $2.6 \times$  as a function of local memory configurations with a corresponding relative area of  $1.0-2.9 \times$ . Depending on system requirements, the appropriate configuration can be selected, as shown in Figure 5.

In the second example, a customer provides a C-language benchmark that represented four execution paths in a servo control application. In this realtime application targeted for a V.2 core, absolute performance in response to certain interrupts was critical.

There was a fixed amount of time to service the interrupt and the algorithm implemented a number of digital

| Configuration                                      | Relative performance |

|----------------------------------------------------|----------------------|

| CF2, no MAC<br>CF2 + MAC with compiler-            | 1.00x<br>1.45x       |

| generated MAC instructions<br>CF2 + MAC with hand- | 1.69x                |

| optimized MAC instructions                         | 1.00X                |

**Table 2**—Depending on the servo control application,

the relative ColdFire performance will vary.

filters. Given the signal-processing nature of the application, this analysis attempted to quantify the impact of the ColdFire multiply-accumulate unit (MAC). The optional MAC is tightly coupled to the basic execution pipeline and is designed to accelerate signal-processing algorithms.

Initial analysis indicated that the dynamic frequency of occurrence for multiply instructions (i.e., F(mul)) was ~10%. Applying the MAC provides faster execution time for multiply instructions, reducing ET(mul).

Many implementations of digital filters can be optimized using MAC instructions directly. First, the benchmark code was compiled and executed on a V.2 core and its performance measured. This value provided the reference.

The code was recompiled using Clanguage macros to use MAC instructions for arithmetic calculations. The compiler-generated MAC assemblylanguage code was optimized by hand to provide an upper bound of performance. Table 2 shows the results.

The baseline core configuration included the processor complex with 8 KB of RAM. Including the MAC unit increased this area by only 11% but increased performance by  $1.5-1.7\times$ .

# WHICH MEANS...

This analysis methodology provides a powerful tool, now system designers can balance processor performance, clock speed, and relative die size.

Given a highly configurable architecture, system designers now have access to the key silicon variables needed to create embedded processor solutions optimized for a given application. And, the result? Smart, intuitive, and user-friendly products. Joe Circello works as an advanced microprocessor architect for Motorola's Semiconductor Products Sector and was the chief architect for the MC68060 and the ColdFire family of microprocessors. With 23 years of experience, he is a veteran designer specializing in pipeline organization, control structures, and performance analysis. You may reach Joe at Joe\_Ciecello-rzsx90@email.sps.mot.com.

Sylvia Thirtle is a principal staff engineer for Motorola's Semiconductor Products Sector, specializing in high-speed digital ASIC design. In her five years at Motorola, she's been involved in various design activities with ColdFire and is currently leading the design of the debug module for the next-generation development. You may reach Sylvia at Sylvia\_ Thirtle-r24495@email.sps.mot.com.

# SOURCE

**ColdFire** Motorola, Inc. (512) 895-2134 Fax: (512) 895-8688 www.mot.com/ColdFire

# Using Java in Embedded Systems

# FEATURE ARTICLE

Vladimir Ivanovic & Mike Mahar

If you're set on putting some desktop-Java functionality into an embeded system, chances are that you've had some sleepless nights. No more! That's what Vladimir and Mike Promise if you'll consider the available alternatives. Ithough Java has properties that would be useful for embedded-system design, the versions of Java used in desktop systems just aren't suitable for embedded systems. There are some alternatives, but they do have drawbacks.

When considering the alternatives, it's important to consider issues like multithreading and debugging support. Regardless of whichever option emerges as the preferred form, two key issues must still be addressed by any embedded Java programming environment: how to provide determinism and how to interface to hardware.

# JAVA IS GOOD

One of Java's strengths is its reasonably clean sytax that is strongly reminiscent of C or C++. So although it's a new language, it's familiar. Getting up to speed with Java is easy.

More importantly, Java is both object-oriented and strongly typed. Everything in Java is an object and there are no loopholes to circumvent Java's strong typing. Since the advent of C++, these features are considred essential in a programming language because they contribute enormously to the correctness of programs.

Aneccdotal evidence bandied about in Java newsgroups and mailing lists

suggests thatdevelopers take less time to produce a working Java program than a program in C or C++. Debugging is also easier because Java has removed a prolific source of hard-to-find bugs, including those related to the incorrect use of pointers.

Example bugs include memory leaks and memory access errors (wild pointers, referencing freed memory, returning a pointer to a local variable, etc.). Java doesn't allow its pointer equivalent (i.e., object references) to be manipulated in the same way as pointers are in C or C++, and it provides automatic garbage collection.

Another strength of Java is its large reusable code base. In the standard distribution, Java supports threads, TCP/IP networking, and remote invocation. It even has a full set of classes for building GUI's.

Additional API's support a variety of needs, such as database access, communication, multimedia, a way to use GUI components, and security.

With Java's strengths as a language, a development environment, and a reusable code base, it's easy to see why developers—and not just embedded-system developers—are eager to put it to use.

# DESKTOP JAVA DRAWBACKS

Unfortunately, as I mentioned, desktop Java has some drawbacks when used in embedded systems. Although Javawas originally intended for use in set-top boxes, it was first used in a web browser, which is a desktop application.

First, desktop Java is too big for embedded applications. Not only must the entire Java virtual machine (JVM) be present, but a Java interpreter or a just-in-time (JIT) compiler must be present as well.

On top of that, all the standard classes must be present. These take up to 8 MB on disk, more when loaded. Fonts take even more space.

The bottom line is that desktop Java needs on the order of 16 MB just to run, and the application needs are additional. Very few embedded systems have that kind of memory available.

Also, Java is too slow. Sun's first releases were usually more than 30x

slower than equivalent C code. Subsequent releases, which use JIT compilers, are significantly faster but still perhaps 5x slower than equivalent C. If you're used to squeezing out the last few cycles out of a processor, this is a heavy penalty to pay just to use Java.

But, the most omportant drawback of desktop Java is that it doesn't meet the constraints of most embedded systems. One such constraint is the requirement for real-time behavior (i.e., execution that's both predictable and bounded in duration).

Many embedded systems have severe real-time requirements. For instance, the collision-detection system on a jetliner has seconds in which to respond. Computation must finish in a certain amount of time, so execution has to be predictable.

Another constraint of embedded systems is their limited resources. Consumer devices, which may be manufactured in the millions, are very sensitive to cost, so designers tend to use the smallest processor and the smallest amount of memory possible to do the job. A programming language that's slow and uses up a lot of memory just isn't competitive with existing alternatives.

More importantly, Java doesn't possess the notion of an address. Embedded systems, almost by definition, are required to access hardware. Most often, that hardware is accessed by referring to a specific address. Because addresses aren't part of Java, you have to go outside the language to overcome this constraint.

Finally, desktop Java has some attributes that get in the way of successful use in embedded systems. These attributes may be useful and even necessary in desktop systems, but not in embedded systems. For instance, Java is interpreted (the source of much of its slowness) an dit is dynamic because it supports the down loading of new classes on-thefly. Java is portable across many different systems because its source code is compiled, not to native code, but to bytecodes, an architecture-neutral format. Also, Java supports a comprehensive security model designed to prefent many kinds of attacks.

However, for embedded sysems, which frequently exist in completely closed environments, portability and security aren't issues. Unless an embeded system is connected to a network, the ability to load new classes dynamically is useless.

These attributes of desktop Java prevent its use in embedded systems. And, the issues of performance, memory consumption, and poor real-time behavior make it hard to retarget the desktop version to an embedded system.

# EMBEDDED ALTERNATIVES

What are the alternatives? How can an embedded-systems developer use the great features of Java without quadrupling the system's cost or writing piles of non-Java code?

Essentially, there are only three options: use a special-purpose JVM, use a JVM with a JIT compiler, or use compiled Java instead of some form of interpreted Java.

Many vendors have come up with specially tailored versions of Java that are a better fit for the needs of embedded developers. For instance, Sun offers PersonalJava for systems with 2-4 MB of memory and EmbeddedJava for smaller systems (Mentor Graphics' Microtec Division is a licensee of PersonalJava). Hewlett-Packard, NSI Com, Insignia Solutions, NewMonics, and others have similar offerings.

Listing 1—Since a compiler knows about every write to memory, it inserts a write barrier automatically.

```

object_a->next = object_c;

if(object_c != NULL)

if(object_c->garbage_flags == WHITE){

object_c->garbage_flags = GRAY;

gc_make_gray(object_c);

}

```

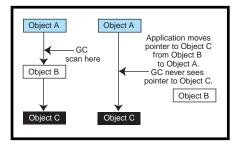

**Figure 1**—*Object C is lost if the application changes pointers between garbage-collection scans.*

Another approach, even in versions tailored for embedded use, is to use a dynamic compilation technique, typically a JIT compiler, to increase performance. But there are several tradeoffs involved.

First, JVMs with JITs have potentially longer start-up times because the JIT compiler has to compile Java bytecodes into native amchine language before executing. Secondly, it's difficult to do a good job of optimizing native code while keeping memory consumption low. The more optimizations that are done, the larger and slower the JIT compiler becomes.

Several vendors provide knobs to tune the dynamic compilation process so you can choose on a case-by case basis exactly what the performanse, memory consumption, and start-uptime tradeoffs are going to be.

But, for some embedded applications, even a JVM with dynamic compilation is too slow and takes up too much memory. One option that is increasingly being considered is compiling Java directly to a native machine language, thereby eliminating both the JVM and either the interpreter or the JIT compiler.

Of course, the resulting application is no longer portable, but embedded developers typically don't care about portability. For a given design, their application needs to run on a single well-known hardware configuration.

The other attribute that compiled Java forces a developer to give up is the ability to load new classes on-thefly. Because all the code is precompiled, there's no facility for dynamic loading of classes. Again, this issue probably isn't too serious for embedded-system developers, most of whom don't want random classes downloaded onto their system. If you're willing to tolerate the lack of portability and the lack of dynamic class loading, you can still reap all the benefits of Java as a great language and keep the system small and fast—that is, if you can resolve the issues of determinism and lowlevel programming.

# **RESOLVING THE ISSUES**

Any version of Java for embedded systems must first be deterministic and predictable. It also has to be able to access memory directly.

One bugaboo of embedded systems is ensuring real-time response. In the case of Java-based systems, the primary cause of nondeterminism is the garbege collector.

In desktop systems, it doesn't matter much that the JVM stops for several seconds to collect unused memory. But in an embedded system, several seconds can be the difference between correct operation andthe loss of human life.

The biggest threat to an embedded operation is that most garbage collectors work in what's called stop-theworld mode. Usually, the collector is called only when an allocation fails because memory is exhausted. Therefore, allocation time is impossible to predict, and when the collector is running, no other processing is being done. This situation is unacceptable in a real-time system.

An obvious solution is to have the garbage collector run concurrently with the application so that the impact of garbage collection is spread around more evenly. This way, timecritical events are processed in a timely manner.

Ensuring real-time reponse still isn't enough to make Java useful for developing embedded systems. Because the added value of embedded systems is their specialized hardware, the embedded software must always be able access or control the hardware, which requires an extension to the Java through a Java Native Interface (JNI) with several possible options or through a nonstandard extension of the Java language.

Sun's JNI permits portability across different JVMs on a particular processor

```

Listing 2— This code gives you an example of how the Phys package can be used.

import COM.mentorg.microtec.phys.*;

class m68561 {

PhysByte this_uart;

PhysByte Tsr, Tdr, Rsr, Rdr;

int baseAddr;

m68561(int base_addr)

{

baseAddr = base_addr;

this_uart = new PhysByte(baseAddr);

Tsr = new PhysByte(baseAddr + 0x8 * 4));

Tdr = new PhysByte(baseAddr + 0xa * 4));

Rsr = new PhysByte(baseAddr + 0x0 * 4));

Rsd = new PhysBYte(baseAddr + 0x2 * 4));

// Initialize UART. Reuse this_uart object because registers

are only used once or twice

11

this_uart.setAddress(baseAddr + (0x1 * 4));

//RCR

this_uart.set(1);

// Reset receiver

this_uart.setAddress(baseAddr + (0x9 * 4));

//TCR

this_uart.set(1);

// Reset transmitter

this_uart.setAddress(baseAddr + (0x19 * 4));

//PSR2

this_uart.set(0x1e);

// 1 stop, 8 bit

this_uart.setAddress(baseAddr + (0x1c * 4));

//BRDR1

this_uart.set(0x8c);

// 9600 bps

this_uart.setAddress(baseAddr + (0x1d * 4));

//BRDR2

this_uart.set(0);

11

this_uart.setAddress(baseAddr + (0x1e * 4));

//CLKCR

// Divide by 3, TCS out, TXC in

this_uart.set(0x1c);

this_uart.setAddress(baseAddr + (0x1f * 4));

//FCR

this_uart.set(0);

// No parity, no error check

this_uart.setAddress(baseAddr + (0xd * 4));

//TIER

this_uart.set(0);

// No transmitter interrupt

this_uart.setAddress(baseAddr + (0x15 * 4));

//SIER

this_uart.set(0);

// No serial

interrupt

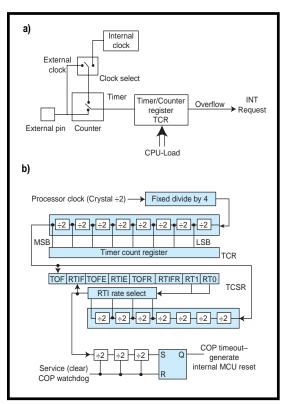

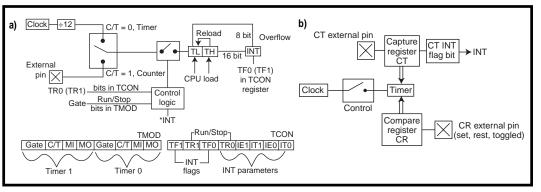

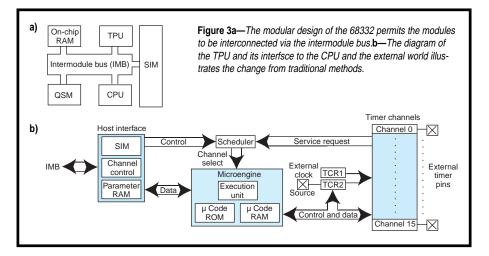

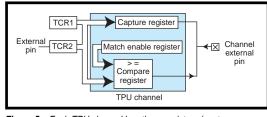

this_uart.setAddress(baseAddr + (0x05 * 4));