# THE COMPUTER APPLICATIONS JOURNAL #103 FEBRUARY 1999 **REAL-WORLD PROGRAMMING**

SPEED

INA

**Getting Down to Speed** with Practical Control

**Step into Pressure Sensing**

**Real-Time Linux Development Tools**

C++ Embedded and Efficient

### TASK MANAGER

#### Avoiding the Fuzzy Faux Pas

or several years, I've edited issues focusing on fuzzy logic for *Circuit Cellar INK*. But this is the first time that "Fuzzy Logic" hasn't been the theme even though three articles in this issue use this approach. As many people suggest, there's a stigma associated with the word "fuzzy." Perhaps for some of the hardboiled hardware types out there, it's just too cute. I can appreciate that.

In fact, I'll let you in on a little behind-the-scenes action. During the recent holiday season, we were pondering cover photo concepts for this issue. And if you were in the States this past year, you know what every kid wanted for their holiday gift, right? Furby, of course!

For those of you who haven't made his acquaintance, this little bug-eyed furry creature "acquires" language by being talked to, or so the ads say. (I won't even start a tirade on what it means to acquire language, although if you see me at the Embedded Systems Conference next month and ask my opinion, I'll be happy to give you the benefit of ten years of graduate study in linguistics!) By the way, if you want to learn about some of the hardware truths beneath Furby's furry exterior, check out www.phobe.com/furby.

Anyway, as I was saying, Furby was on our minds and someone said, "Wouldn't it be funny to put Furby on a Fuzzy Logic cover?" Sure, but we knew it was going to be next to impossible to get our hands on one of these popular toys. Besides, I'm not sure it uses fuzzy logic. So, that idea went out the window.

We had to come up with something else, but with the words "Fuzzy Logic" on the cover, it just wasn't working. All we could envision were fuzzy animals, fuzzy houseslippers,.... Those cuddly images would just get us into trouble with people who seem to believe that fuzzy logic is imprecise and unprofessional simply because it uses *that* word.

To get beyond the fur fest, we started thinking about what fuzzy logic is: balancing, weighing variables, a certain way of evaluating parameters. But since the last two Fuzzy Logic covers have embodied the "different way of looking at the situation" concept, that now-stale idea went out the window along with Furby.

Clearly, putting "Fuzzy Logic" on the cover wasn't going to happen. By now, I was getting really frustrated and started walking around the office growling, "What's wrong with 'fuzzy' anyway? Do you mean to tell me that more people would appreciate fuzzy logic if we called it something pompous like 'multiparameter weighting analysis'?"

Fortunately, once we thought about how Walter Banks and Constantin von Altrock discuss this approach in their articles, we realized that fuzzy logic is just a practical way of using embedded computers to handle realworld problems. And that's when it hit us: Real-World Programming.

Although we changed the name of the theme, I hope you'll look past any biases that "fuzzy" brings up as you read the fuzzy-logic articles. Don't let words get in the way of a helpful solution.

80

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella CHIEF FINANCIAL OFFICER

TECHNICAL EDITORS Michael Palumbo Rob Walker

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ingo Cyliax Ken Davidson

Fred Eady **NEW PRODUCTS EDITOR** Harv Weiner

Ingo Cyliax

Jeannette Ciarcia ART DIRECTOR KC Zienka

ENGINEERING STAFF Jeff Bachiochi

PRODUCTION STAFF Phil Champagne John Gorsky James Soussounis

> PROJECT EDITOR Janice Hughes

EDITORIAL ADVISORY BOARD

Norman Jackson David Prutchi

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

ADVERTISING ADVERTISING SALES MANAGER Bobbi Yush Fax: (860) 871 (860) 872-3064 E-mail: bobbi. ADVERTISING COORDINATOR

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

FAX: (860) 871-0411

R Fax: (860) 871-0411 F-mail: val.luster@circuitcellar.com

CONTACTING CIRCUIT CELLAR INK

#### SUBSCRIPTIONS:

Valerie Luster

(860) 875-2199

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION:

TELEPHONE: (860) 875-2199

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar INK, 4 Park St., Vernon, CT 06066 UTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613. Circuit Cellar INK<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK<sup>®</sup> disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK<sup>®</sup>.

Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

| 12 | <b>Fuzzy L</b> o<br>Walter I                                                                  | ogic Becomes Velvet Programming<br>Banks                                                             |                                                                    |    |

|----|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----|

| 16 | <b>Truck Speed Limiter Control</b><br>Constantin von Altrock                                  |                                                                                                      |                                                                    |    |

| 20 | <b>Fuzzy Footfalls</b><br>Pressure Sensing in a Medical Shoe<br><i>Constantin von Altrock</i> |                                                                                                      |                                                                    |    |

| 26 | C++ Lite<br>A C++ Dialect for Embedded Systems<br>John Carbone                                |                                                                                                      |                                                                    |    |

| 34 | Stuart Ball                                                                                   |                                                                                                      |                                                                    |    |

| 66 | TP<br>Par<br><i>Joe</i>                                                                       | r <b>oSeries</b><br>U<br>t 2: Freeing the CPU<br><i>DiBartolomeo</i>                                 | Task Manager<br>Elizabeth Laurençot<br>Avoiding the Fuzzy Faux Pas | 2  |

| 74 | JTA                                                                                           | <b>m the Bench</b><br>AG Testability<br><i>F Bachiochi</i>                                           | Reader I/O/<br>Circuit Cellar On-line                              | 6  |

| 78 | Car<br>A I                                                                                    | <b>con Update</b><br>2 1451, Where are You?<br>Look at the IEEE 1451 Standard<br><i>m Cantrell</i>   | New Product News<br>edited by Harv Weiner                          | 8  |

|    |                                                                                               |                                                                                                      | Advertiser's Index/<br>March Preview                               | 95 |

|    |                                                                                               | DE                                                                                                   | Priority Interrupt<br>Steve Ciarcia<br>Survey 101                  | 96 |

|    | 2 Nouver<br>edited                                                                            | <b>nu PC</b><br>by Harv Weiner                                                                       | 1195                                                               |    |

|    |                                                                                               | for Test and Measurement<br>as Wall and Mike Bauer                                                   |                                                                    |    |

| 5  | 51 RPC                                                                                        | <b>Real-Time PC</b><br>Embedded RT-Linux<br>Part 4: Developing Under Linux gco<br><i>Ingo Cyliax</i> | c/gdb                                                              |    |

|    | <b>9</b> APC                                                                                  | <b>Applied PCs</b><br>In the Face of Medusa<br>Part 2: A Whole New Solution<br><i>Fred Eady</i>      |                                                                    |    |

### **READER** I/O

#### HARVARD VS. VON NEUMANN APPEALED

In their article "In-System Programming" (*INK* 101), Craig Pataky and Bill Maggs imply that all embedded micros use Harvard architecture rather than Von Neumann. In fact, the Motorola 68HC05 and 68HC11 families employ the Von Neumann architecture.

Their statement, "The main reason microcontrollers have clung to the Harvard architecture is because by keeping data and code memory separate, it's impossible for the machine to inadvertently corrupt its own code and go insane" (p. 15) implies that code memory in a Von Neumann system is always volatile.

Also, the statements "Von Neumann designs are flexible but inherently unstable. Harvard designs are rock-solid but immutable" (p. 15) are extremely misleading. If my code is in EPROM or some other firm memory area, I doubt a misguided program could overwrite the code and cause the system to go insane.

A corrupted program counter register in a Harvard design is no safer than one in a Von Neumann design.

Calvin Krusen

ckrusen@meeco.com

The point of our article was to address the flexibility and cutting-edge technology of in-circuit programming in flash-based designs. Our reference to Von Neumann versus Harvard design was based more on historical implementation than technical definition.

You are correct, not all micros use the Harvard architecture. But, our statement that microcontrollers which keep code and data memory separate cannot corrupt their own code is factual. And, yes, a corrupted program register could happen to any micro, but that's generally what watchdog timers are for.

Aside from being inexpensive, the Von Neumann design permits dynamic creation and destruction of programs on-the-fly—only the minimum code required for basic operation is fixed. On the other hand, Harvard designs have almost always been ROMed.

We agree that if the micro is Von Neumann and an address region was set aside for ROMed code, the code is every bit as secure as a Harvard design. Unfortunately, this gives rise to the same problems that the article was trying to solve in the first place.

Craig Pataky and Bill Maggs

#### Circuit Cellar ONLINE

#### Newsgroups

If you miss the Circuit Cellar BBS, then the cci newsserver is the place to go for on-line questions and advice on embedded control, announcements about the magazine, or to let us know your thoughts about Circuit Cellar. Just visit our home page for directions to become part of the newsgroup experience.

> The February Design Forum password is:

> > Fuzzy

www.circuitcellar.com

- Circuit Cellar Online is hosting the proceedings from the First Annual 1998 **Embedded Internet Workshop**. Visit our homepage to find the workshop proceedings including slide presentations, lecture notes, and complete papers.

- All aboard the INFO Express! Loaded with the latest news and information about Circuit Cellar INK as well as any additions or changes to our web site, the INFO Express stops right at your e-mail address. Visit our homepage to sign up for this new service from Circuit Cellar.

- While you're working on your entry for Design99, don't forget to check the Design99 Rules Update section for the latest updates on the contest guidlines.

Be sure to visit the Circuit Cellar Design Forum this month for more great online technical columns and applications. February's Design Forum password is your key to great new columns, monthly features, and PIC Abstracts.

Silicon Update Online: Zilog Lives?!—Tom Cantrell

Lessons from the Trenches: Getting a Head Start on Software Development— Linking Embedded Code—George Martin

A 68HC11 S-Record Disassembler: Frank Kuechmann

#### DATA ACQUISITION MODULE

The **ADR2000** is a serial data acquisition and control interface that features a host of peripherals. The board includes eight 12-bit analog inputs with a 0–5- or ±5-V input range (software selectable), two analog outputs (either 12-bit analog [V.A] or 10-bit PWM [V.B]), and a 16-bit event counter. Eight digital I/O lines with 20-mA sink and source current capability are available.

The ADR2000 can be programmed using simple yet versatile ASCII commands, and host software can be written in virtually any programming language or with most graphical instrumentation software packages. An onboard RS-232-to-RS-485 converter permits the use of hosts with either port type and facilitates daisy-chaining via RS-485. The converter on each daisy-chained unit enables other vendors' RS-232 devices to be connected to any node on the chain.

Power is applied via standard 9-V wall adapter. An auxiliary, regulated 5-VDC output is available to power external circuitry.

Pricing for the ADR2000 ranges from **\$225** to **\$265**.

Ontrak Control Systems, Inc. (705) 671-2652 Fax: (705) 671-6127 www.ontrak.net

#### VIDEO TEXT DISPLAY MODULE

A video text display module that lets a PC or microcontroller display up to 11 lines of 28 characters (308 total) on standard NTSC or PAL composite video systems has been announced by Decade Engineering. Applications include remote video inspection, robotics, recreational vehicles, home automation, security and surveillance, remotely piloted vehicles, amateur TV, and industrial process monitoring.

**BOB-II** generates matte background video onboard or genlocks to an external video source and superimposes its text over the image. Video mode switching is fully automatic. The video output contains a small positive DC bias, which is common to many video sources and well tolerated at the inputs of most video BOB-II's character patterns are  $12 \times 18$  pixels. Basic character graphics and Euro-language support are provided. Character transparency and brightness are variable using external pots. Character-blinking or background-display options draw attention to important messages.

Programmed control is effected by simple commands and text sent as plain ASCII codes through a 9600-bps serial data link. Direct control from the PC keyboard is possible with any standard ASCII terminal program.

BOB-II uses a 30-pin SIMM form factor and snaps into a common 30-pin SIMM socket. It requires 65 mA from an unregulated l2-VDC source and offers a regulated +5-V output to power associated equipment.

BOB-II (NTSC) sells for \$79.95. The PAL version

equipment. Internal video background signal is automatically generated if video is not supplied to the input pin. Composite sync output (separated from input video) is provided.

costs slightly more. Application code is available at the company's web site.

Decade Engineering (503) 743-3194 Fax: (503) 743-2095 www.decadenet.com

#### SERIAL REAL-TIME CLOCK MODULE

The **Pocket Watch B** contains a real-time clock, a calendar, and advanced timing features. The clock module keeps track of seconds, minutes, hours, days, months, and years. Adjustments for leap year are automatic, and the module is year-2000 compliant.

The Pocket Watch B communicates via an asynchronous, one- or two-wire, serial communications interface. Data-transfer rates of 2400, 4800, and 9600 bps are supported with autobaud detect. The module is packaged in a SIP format that measures  $1'' \times 1''$  and operates on standard TTL levels.

The Pocket Watch B contains four advanced timing features that are accessible with the alarm command. There is a standard-level alarm, a single-shot alarm with a duration of up to 18 h, an astable alarm pulse with pulse lengths of up to 4 min. and repetition rates of up to 4 h, and an astable alarm pulse with pulse lengths of up to 4 h and repetition rates of up to 10 days.

The Pocket Watch B sells for **\$24.95**. Complete datasheets and application notes are available at the company's web site.

Solutions Cubed (530) 891-8045 Fax: (530) 891-1643 www.solutions-cubed.com

#### UNIVERSAL MEMORY EMULATOR

The **I-Series Universal Memory Emulator** enables a user to debug embedded systems with the same level of features as a microprocessor ICE. The emulator provides real-time access to memory devices in embedded systems, enabling the user to monitor and change target data and bus information. Complex triggers can be set on any combination of data values, address values, and external inputs from other units. These trigger events can be set to signal the host PC or external equipment and/or to force an interrupt on the target system.

The I-Series emulates virtually all types of memory chips, including EPROM, flash memory, EEPROM, and DRAM. These emulators have capacities up to 32 Mb, and support is provided for devices from 8 to 56 pins with dual 8- and 16-bit capability. Full support for flash memory command registers is provided. The emulators offer fast access times (70 ns) and ultra-fast downloading capabilities (over 400 kbps).

Reconfigurable memory resources enable the internal memory to be used in a variety of emulation and debugging applications simultaneously. Transferring file data to and from the emulator is easily achieved with any mix of file formats. The open software structure means that the user can build the display form from predefined values or from more complex user-defined structures.

Advanced debugging capabilities integrated into the design enable developers to use whatever debugging approach they desire, including a virtual serial port and live memory display and editing.

On all models, 3- and 5-V support is standard. Advanced powermanagement features and a low-power design facilitate reliable data backup and limit target power-supply loading.

Pricing for the I-Series emulators starts at \$349.

Scanlon Design, Inc. (902) 425-3938 Fax: (902) 425-4098 www.scanlondesign.com

#### VOICE PLAYBACK MODULE

The **VM-1608** is an EPROMbased digital voice module that plays back up to 128 preprogrammed messages via two independent channels with up to 64 messages per channel. This self-contained module requires only a power supply, a speaker, and a few trigger signals to operate. Applications include verbal industrial control, talking displays, exhibit sound effects, and vending-machine voice output.

Desired messages are preprogrammed into the module with the Quikvoice development system. A user-friendly interface provides random access to messages as well as separate or mixed audio output for the two channels. The total combined message time is 8.5 min. maximum. Operation requires a single 12–24-VDC power supply. Two EPROM sockets provide a memory capacity from 2 to 16 Mb. Each audio channel uses half of the EPROM capacity. Each has its own power amplifier, but the amplified output may be mixed together on the board. If line-level output is selected, onboard mixing is not possible.

When the board is playing a message, it ignores any further triggering until the playback is over. To stop the playback prematurely, pulse the RESET pin high momentarily.

The VM-1608 sells for **\$68** in quantities of 50.

Eletech Electronics, Inc. (626) 333-6394 Fax: (626) 333-6494 www.eletech.com

#### 8051 SINGLE-BOARD COMPUTER

The **Micro Lab-51** is an 8051-based SBC that works well in educational and product development settings. In an academic environment, instructors can demonstrate real-world applications and students can implement projects. In the development lab, design engineers can create and test prototypes of their 8051-based products.

The computer uses the 8051-compatible 89S8252 microcontroller, which runs at

microcontroller, which runs at up to 24 MHz. The chip has 8 KB of flash memory for program storage, and its flash memory can be programmed serially, so no programmer is needed.

The board also contains two 28-pin memory sockets—the first supports 32 KB of RAM, and the second supports 28 KB of EEPROM, EPROM, or batterybacked RAM. Other board features include RS-232 serial port buffering (RS-485 is optional), processor supervisory circuit with

manual reset switch, and a  $3.5'' \times 1.5''$  prototyping area. Data, address, and control lines are brought out on connectors next to the prototype area to facilitate the adding of custom user circuitry.

In its standard configuration, the Micro Lab-51 has a full-featured BASIC interpreter that sup-

ports floating-point math and most BASIC commands. An advanced version comes with system monitor debugger software and an optional 8051 cross assembler. This configuration is suited to 8051-based product development because the engineer can write assembly-language code and run it in real time under monitor control.

> Prices range from **\$99 to \$139**. Options and projects are also available.

Allen Systems (614) 488-7122 members.aol.com/allensys

#### FEATURES

| 12 | Fuzzy Logic Becomes<br>Velvet Programming |

|----|-------------------------------------------|

| 16 | Truck Speed<br>Limiter Control            |

| 20 | Fuzzy Footfalls                           |

| 26 | C++ Lite                                  |

| 34 | Multiprocessor<br>Communications          |

#### We don't hear too much about fuzzy logic anymore. And, Walter wondered why. But once he started looking at the applications around him, it became clear that there's a reason for all the hush-hush. Fuzzy logic has hit the mainstream.

#### FEATURE ARTICLE

Walter Banks

### Fuzzy Logic Becomes Velvet Programming

he real mark of a mature technology is when it is used and no one notices. Let me explain what I mean.

Just a few months ago, I was at dinner with a Japanese friend of mine and I noted that the products they developed and sold no longer advertised that they used fuzzy logic. I wanted to know why.

He responded that they use fuzzy logic now more than ever, but these days, it wasn't a feature that advertising hype found useful. He pointed out that the product still used fuzzy logic in its implementation and that, in fact, the rule base had been extended and reimplemented.

Looking back over our own fuzzylogic experiences, I can see how it went through all the stages of a new technology from its initial idea and early users to hard evaluation by reputable scientists and finally engineering acceptance.

It took us a long time to find an application that could actually be implemented with fuzzy logic as a Listing 1—This small snippet of code is part of the fuzzy function for a rice-cooker temperature-control system.

```

FUZZY cooker_temperature;

{

IF bowl IS cold THEN

heat is ON

IF bowl IS too_hot THEN

heat IS OFF

IF bowl IS boiling THEN

heat IS OFF

}

```

suitable engineering choice. Over time, however, engineers in various countries have found several classes of applications that are well served by fuzzy-logic technology.

Rice cookers in Japan were one of the first commercial products that proclaimed fuzzy logic as an advantage to the consumer. This mainstream commercial product is used for every meal in almost every Japanese household. It also represents one of the application areas where fuzzy logic is a particularly good solution.

Practical fuzzy-logic applications are divided into four general types—fuzzy control systems, knowledge bases, imprecise comparisons and application scaling. In this article, I want to briefly address each of those areas.

#### FUZZY CONTROL SYSTEMS

Fuzzy control systems are voting systems that evaluate a number of

strategies to solve a particular problem. They then weigh those options to find the solution that best fits the current requirements. The Japanese rice cooker fits into this category.

This simple control problem has many variables. Temperature, time, volume, and mix all affect the outcome. For example, as the rice cooks, some of the properties of the mix change (e.g., the boiling point).

Fuzzy logic is one of the few solutions in which it is simple to implement nonlinear control systems that depend on finding a workable solution for many different circumstances.

Consider this classic fuzzy control system. The controller software consists of a fuzzy function and consequence functions for each of the controlled variables.

Listing 1 shows part of the temperature control system for a rice cooker. The present state of the cooking bowl

Listing 2—The fuzzy comparison for equality is implemented with a small C function called ABOUT.

is tested against several fuzzy functions and the consequence (i.e., heat position) is controlled as a result of these tests. As in most fuzzy-logic control systems, each fuzzy rule represents a simple common-sense statement about the application.

Such control systems are regularly implemented with very small embedded processors, especially in consumer products. Other good examples of fuzzy control systems include camera focus and household environmental control.

#### IMPRECISE COMPARISONS

Because we use the term "fuzzy," fuzzy-logic systems are often thought of as having imprecise comparisons. But the truth is that, unlike conventional binary comparisons, a fuzzy comparison returns a result that is scaled between 0 and 1. In other words, these systems are more—not less precise.

Listing 2 shows an industrial weighscale C-code fragment of just such a fuzzy comparison. The main line call (i.e., x = ABOUT(bag, 200, 10)) checks the bag weight of 200 g within 10 g and returns a value between 0 and 255 to indicate the degree of truth.

A bag value of 200 returns 255, and a bag value of 195 or 205 returns 128. If the bag is outside the range 190–210, then the returned value is 0.

The required code for imprecise comparisons is easily implemented on most embedded processors.

#### APPLICATION SCALING

The concept of application scaling is a big win in embedded systems applications. Consequently, it is a common practice.

If the significant variables in an application are all scaled to a standard range of fuzzy 0 to fuzzy 1 with outof-range values limited by the value of either fuzzy 0 or fuzzy 1, then the amount of application code needed to make decisions with these variables is significantly reduced. In all the applications I've seen (with one exception), the variables have been scaled to be within a single-byte range.

Fuzzy-logical operators—fuzzy AND, OR, and NOT—can manipulate and combine the variable data. This **Listing 3**—Many applications may be simplified by scaling the +Scaling significant variables.

```

#define F_OR(a,b) ((a) > (b)) ? (a) : (b)

char Ftemp,Fhumidity,swelter;

int temp,humidity;

unsigned char Scale(int v, int lower, int upper)

{

if (v > upper ) return (F_one);

if (v < lower) return (F_zero);

return (((v - lower)/(upper-lower) ) * (F_one - F_zero));

}

void main (void)

{

…

Ftemp = Scale(temp, 50,90);

Fhumidity = Scale(humidity, 60,100)

Swelter = F_OR(ftemp, Fhumidity);

}</pre>

```

approach to application implementation has kept low-cost processors in many high-volume consumer products.

The code fragment in Listing 3 shows how application scaling can be implemented. In this example, humidity and temperature are scaled over the significant range of interest. A new fuzzy variable, Swelter, is set based on the discomfort level that the temperature or humidity produces.

The F\_OR function referenced is the minimum of two variables. This function takes very little embedded system resources in an application.

#### **KNOWLEDGE BASES**

Fuzzy-logic rules carry with them information about a problem. It is common, for example, to say that if the room is hot then turn down the heat. "Hot" is an abstract value that becomes important when it's associated with an action.

Fuzzy control systems decide actions based on a database for fuzzy functions, each competing for resources. Information databases use fuzzy logic to weigh facts and arrive at conclusions.

There are some obvious uses for this approach to knowledge bases. Determining the potential causes of an illness is a good example.

One novel example of a fuzzy knowledge database uses fuzzy-logic tools to create a computer player in a role-playing game. The behavior of a fictitious alien race is described with a fuzzy function.

The current circumstances are sent to several different alien descriptions, producing consequences for each simulated character. It takes surprisingly few rules to create new alien species that are recognizable by their behavior.

#### TOO CLOSE TO SEE

My point: fuzzy-logic tools and technology have matured to the point that they've become mainstream tools. The underlying principles have survived the validity tests of science and the usefulness tests of time.

Fuzzy logic enables you to encapsulate a large problem in a form that can be solved by a very small processor. These days, it helps build huge databases of important information as well as solve many of the tricky problems associated with nonlinear control systems.

My Japanese friend was right. We don't talk about fuzzy logic much anymore. We just use it. ■

Walter Banks is president of Byte Craft Limited, a company specializing in software tools for embedded microprocessors. His interests include highly reliable system design, codegeneration technology, programminglanguage development, and formal code-verification tools. You may reach him at walter@bytecraft.com.

#### FEATURE ARTICLE

#### **Constantin von Altrock**

### Truck Speed Limiter Control

Is your teen learning to drive? Are you worried? If you think they lack logic, maybe you should consider fuzzy logic. Constantin uses fuzzy rules to consistently limit the speed of commercial trucks, despite weight variables and truck type. n Europe, commercial trucks with a maximum load of over 12 tons are legally required to be equipped with a device that limits their maximum speed to 53.3 mph (86 km/h). Designing an algorithm for this control problem was no easy task.

The speed-limiter device needed to be compatible with a variety of trucks, all of which exhibit different behaviors. Additionally, the dynamic behavior of a truck varies depending on whether it is fully loaded or empty.

Conventional control algorithms, like PID controls, assume a linear model of the process under control, so they couldn't be used. A mathematical model of the truck would be tough to build and would require too much computational effort from an 8-bit micro. So, the designers turned to fuzzy logic.

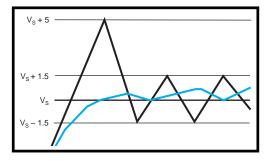

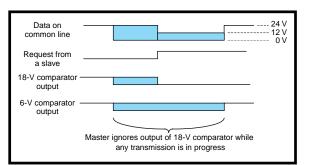

Figure 1—By law, the speed limiter is allowed a +5-km/h overshoot when reaching maximum speed. Thereafter, it must control the speed within a ±1.5-km/h band. The blue line shows that the fuzzy-logic controller provides much smoother performance compared to the conventional controller (black line). The overshoot is eliminated, and the fluctuations are only about one-fourth of the allowed maximum. This article focuses on the electropneumatic design of the speed limiter. The pneumatic cylinder mechanically limits the throttle-opening angle of the fuel-pump arm, and a pulse-proportional electromechanical valve controls the cylinder pressure. The electromechanical valve connects to an electronic control unit that uses a microcontroller to drive the valve according to the speed of the truck.

#### **CONTROL REQUIREMENTS**

When the truck approaches the maximum velocity, the pneumatic valve reduces the throttle-opening angle of the fuel-pump arm so the maximum velocity ( $V_S$ ) is not surpassed. Even if the driver continues to push the accelerator, the speed limiter has to ensure a smooth ride at the maximum velocity.

However, because of the dead time and nonlinearities involved with this control action, an actual overshoot and hunting occur when using a proportional or on/off controller. Adding a differential and integral part yields a PID controller model.

A PID controller generates the command value as a linear combination of the error (P), the derivative of the error with respect to time (D), and the integral of the error with respect to time (I). To tune a PID controller, the combined weights of these three components must be chosen so they approximate the nonlinear behavior of the process under control at its operating point.

Although this technique works with processes that are at only one operating point, it fails when the operating point moves. With the truck-speed limiter, the operating point moves because of different load situations such as driving uphill or downhill, as well as driving empty or with a full load. Additionally, the characteristics of the pneumatic valve and the fuel

injection are highly nonlinear and vary from one truck to another.

If a PID control algorithm is used in a truck-speed limiter, it can only be tuned accurately for one operation point and one type of truck. For other operation points and different truck types, overshoot and hunting occur.

To compensate for this, European legislation permits speed limiters to operate within a certain tolerance, as shown in Figure 1. Once the maximum speed is reached, an initial overshoot of 5 km/h is tolerated. Afterward, the speed is kept constant within an interval of  $\pm 1.5$  km/h. But, the overshoot and hunting tolerated by the legislation result in annoying speed fluctuations.

#### MECHANICAL DESIGN

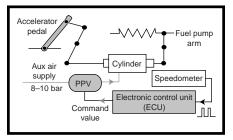

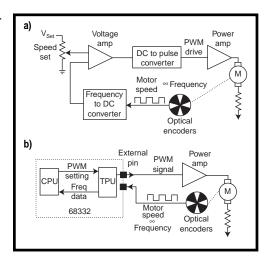

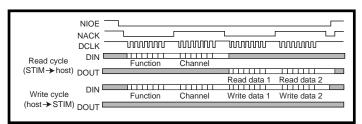

Figure 2 shows the outline of the mechanical design for the speed limiter. An electronic control unit (ECU) compares the digital pulse signal from the speedometer with the maximum speed value preset in the device.

Based on this comparison, the ECU computes the command value for the pulse-proportional valve (PPV) that controls the air pressure in the cylinder. The air stems from the vehicle's pressured-air system. In a nonlinear but proportional ratio, the cylinder shortens the arm linking the accelerator pedal to the fuel pump, thereby throttling the fuel pump. The ECU is designed as a mixed digital and analog circuit. Speedometer signal processing, diagnosis functions, and the fuzzy-logic control algorithm are all computed by an 8-bit PIC. The MCU uses an external EE-PROM to store parameters of the truck and speedometer such as the maximum velocity and diagnosis variables.

The MCU generates

a PWM signal that is amplified by a power stage to drive the PPV. The analog part is responsible for preprocessing and filtering the speedometer signal.

#### FUZZY-LOGIC CONTROLLER

Fuzzy logic is an innovative technology for solving multiparameter and nonlinear control problems. It uses human experience and experimental results rather than a mathematical model to define a control strategy.

As a result, fuzzy logic often delivers solutions faster than conventional control techniques. As well, fuzzy-logic implementations on microcontrollers are very efficient when it comes to code space and execution speed [1, 2].

The entire fuzzy-logic algorithm was developed, tested, and optimized

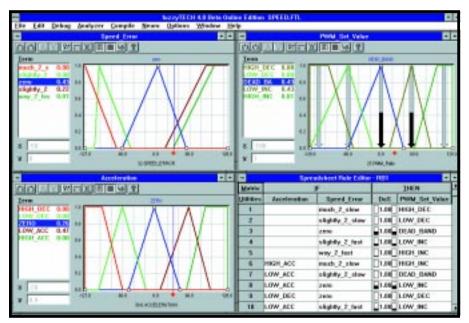

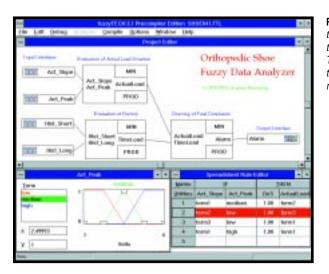

**Photo 2**—The fuzzy-logic system is designed graphically using the fuzzy TECH software development system. Linguistic membership functions are drawn with the mouse, and control rules are represented as tables.

Photo 1—The fuzzy-logic controller for the speed limiter uses acceleration and speed error as inputs to determine the set value for the pressure valve.

using Inform's *fuzzy*TECH software tool. This integrated design environment features automatic assembly code generation on all PIC families [3, 4].

Photo 1 shows the Project Editor featuring the structure of the fuzzylogic system. On the left side, two input interfaces fuzzify the two input variables Acceleration and Speed\_ Error.

The rule block in the middle contains all the fuzzy-logic rules that represent the system's control strategy. On the right side, the output variable PMV\_Set\_Value is defuzzified in an output interface.

The linguistic variables are displayed in a variable-editor window, and the rules are shown in the Spreadsheet Rule Editor window (see Photo 2). Each linguistic variable contains five terms and membership functions (standard type) that are connected by a total of 12 fuzzy-logic rules. As a defuzzification method, the Center-of-Maximum (CoM) method is used [1].

All rules in the fuzzy-logic system let the designer define the best reaction (output variable value) for a situation. The situations are described by the combination of the input variables.

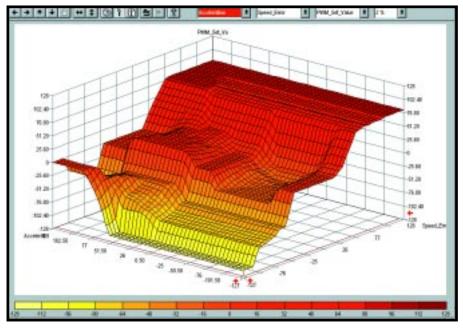

A number of different analyzer tools are used to verify the system's performance. In the 3-D plot in Photo 3, the two horizontal axes show the two input variables, Acceleration and Speed\_ Error. The vertical axis plots the output variable (PWM\_Set\_Value), which is the set value for the PWM unit on the microcontroller.

Rule 1, as shown in Photo 2, states that if Speed\_Error = much\_2\_slow,

Photo 3—The 3-D analyzer of fuzzy TECH plots the transfer characteristics of the fuzzy-logic controller. This type of controller approximates the nonlinear characteristics of the truck much better than a linear PID-type controller.

then PWM\_Set\_Value = HIGH\_DEC. This rule represents the engineering knowledge that if the truck is under the speed limit, no pressure should be applied to the cylinder. The membership function of the term much\_2\_slow is also shown in the respective variable editor in Photo 3.

The 3-D analyzer plots the transfer characteristic as a result of rule 1. In

the front part of the curve, the value of the output variable is very low (color of surface light). As you proceed to the left along the Acceleration axis, the output variable value increases, which is a result of rule 6.

Rule 6 states that if Acceleration = HIGH\_ACC and Speed\_Error = much\_2\_slow, then PWM\_Set\_Value = HIGH\_INC. This rule represents the engineering knowledge that in the case of a high acceleration, the result is medium pressure on the cylinder. This action ensures that the cylinder already contains some pressure in case the truck reaches the limit quickly. Without this rule, a speed overshoot would occur.

#### IMPLEMENTATION

Because *fuzzy*TECH can simulate the fuzzy-logic system without the target hardware, a fair amount of optimization was accomplished off-line on the PC. Final optimization and verification of the system were conducted on real trucks.

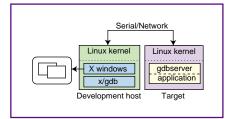

The target system and the MCU for the electronic control unit is mounted in the truck and connected to the development PC (a laptop in the truck's cabin) by a serial cable. Serial connection enables modification of the running fuzzy-logic controller on-the-fly.

This development technique is efficient because it lets the developer analyze how a certain behavior of the fuzzy-logic controller is caused by the membership-function definition and the rules. And because modifications can be done in real time, the effects can be felt on the truck instantly.

One way to enable on-the-fly debugging is to link the *fuzzy*/TECH real-time remote cross-debugger (RTRCD) module to the fuzzy-logic controller that runs on the MCU and connect it to a serial driver. The RTRCD module consumes about half a kilobyte of ROM, a few bytes of RAM, and some computing resources to serve the serial communication on the MCU.

Because the PIC used in this application can't provide such resources, the serial debug mode of *fuzzy*TECH is used rather than the RTRCD module. In serial debug mode, the values of the input variables are sent from

Figure 2—The speed limiter consists of an electronic control unit (ECU) that reads in the speedometer signal and controls the pulse proportional valve (PPV). The PPV manipulates the air pressure in the cylinder connecting the accelerator pedal and fuel-pump arm.

the MCU to *fuzzy*TECH running on the development PC via the serial cable and the results are sent back.

*fuzzy*TECH shows the entire fuzzylogic computation in its editor and analyzer windows and enables on-thefly modifications. To support serial communication, a piggyback board containing a MAX232 driver IC is mounted on the speed-limiter board.

Using *fuzzy*TECH's serial debug mode rather than the RTRCD module means that the code size and computation effort previously required for the fuzzy-logic computation on the MCU can be saved and used for the serial communication.

The disadvantage of the serial debug mode is that it computes the system's results on the PC, where real-time response cannot be guaranteed. Also, unlike the RTRCD module, any crash of Windows, the PC, or the serial communication will halt computation in serial debug mode.

#### RESULTS

After optimizing the fuzzy-logic rule strategy on different trucks and various load conditions, the speed limiter demonstrated the response curve shown in Figure 1 (blue line). The fuzzy-logic controller achieves a much smoother response, doesn't show overshoot behavior, and provides a higher accuracy of keeping the speed limit compared to a conventional controller.

The final fuzzy-logic system was compiled to PIC assembly code by *fuzzy*/TECH and required 417 words of ROM space and 32 bytes of RAM. The RAM space can be used for other computation tasks such as preprocessing and filtering while the fuzzy-logic system isn't running. The entire fuzzylogic system needs less than 2 ms to compute on the PIC16 MCU.

I've demonstrated that, with a little bit of fuzzy logic, you can solve difficult control problems using conventional design techniques and by putting your own engineering experience to work.

Not only that, but you can design a solution using visual software tools and generate highly optimized assembly code for most microcontrollers at the push of a button. Now you're on the way to significantly reducing design time.

Constantin von Altrock began research on fuzzy logic with Hewlett-Packard in 1984. In 1989, he founded and still manages the Fuzzy Technologies Division of Inform Software Corp., a market leader in fuzzy-logic development tools and turn-key applications. You may reach him at cva@inform-ac.com.

#### REFERENCES

[1] C. von Altrock, Fuzzy Logic and NeuroFuzzy Applications Ex*plained*, Prentice-Hall, Englewood Cliffs, NJ, 1995.

- [2] H.J. Zimmermann, Fuzzy Set Theory—and its Applications, Boston, MA, 1991.

- [3] Inform Software Corp., fuzzy-TECH 5.2 Edition Manual, 1998.

- [4] Microchip Technology, fuzzy-TECH fuzzyLAB Manual, 1998.

#### SOURCES

#### **PIC microcontroller**

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 899-9210 www.microchip.com

#### *fuzzy*TECH

Inform Software Corp. (630) 268-7550 Fax: (630) 268-7554 www.fuzzytech.com

#### **MAX232**

Maxim Integrated Products (800) 998-8800 (408) 737-7600 Fax: (408) 737-7194 www.maxim-ic.com

### Fuzzy Footfalls

#### FEATURE ARTICLE

#### **Constantin von Altrock**

#### Pressure Sensing in a Medical Shoe

If you've ever had knee surgery, you know how long it takes to recover. Imagine a pressure sensor that enables you to monitor the pressure you're putting on a bad knee. Fuzzy logic and a tension sensor make it all possible. nalyzing complex data sets often requires human-like evaluations or decisions that are severely limited if mathematical models are used. In many applications, the data material is noisy or contains artifacts. Under such conditions, it doesn't take long for conventional data-analysis methods to reach their limits.

Most data-analysis methods derive structural information from given data sets. This structural information represents the system that produced the data sets. The goal is to identify internal parameters of the system that can't be directly measured.

There are many different methods and algorithms for data analysis, but most have difficulties coping with noisy data and data containing artifacts. These applications have to use very robust data-analysis techniques that cope with the errors and artifacts.

Take a look at Figure 1 to see how fuzzy logic can help. To the human eye, this graphic looks like a nonsensical collection of gray squares. The human eye is a precise sensor that can distinguish about 100 shades of gray, but even so, Figure 1 remains a collection of gray squares. Only by squeezing your eyelids so tight that the entire picture becomes fuzzy can you see that the collection of gray squares is actually a picture of Abraham Lincoln.

The lesson? Even the most precise methods can't reveal the picture. If you modify the grayness of some of the squares, the most accurate picture still comes from the fuzzy look.

Employing fuzzy logic can be just as successful in data-analysis applications to provide solutions for everyday problems. For example, after knee surgery the doctor tells you to limit the strain on your knee. But what constitutes too much strain? And how do you know when you're approaching the limit?

The solution is really quite fuzzy, but I'll get to that in a moment. Using fuzzy logic for data analysis, whether for medical or practical purposes, can be accomplished with many different combinations of fuzzy logic and conventional techniques.

Of course, choosing the best combination of techniques depends on the application. The most common combinations are fuzzy cluster analysis, fuzzy rule-based methods, and adaptive fuzzy rule-based methods. Let's review these before getting into the application.

#### **CLUSTER ANALYSIS**

Fuzzy cluster analysis maps objects to predefined classes [1, 2, 3, 4]. In a quality-control system, for example, the classes could be either good or bad. For this mapping, a vector of parameters describes each object, and each parameter denotes a certain property of the objects.

**Figure 1**—Only by squeezing your eyelids so the picture becomes "fuzzy" can you recognize Abraham Lincoln.

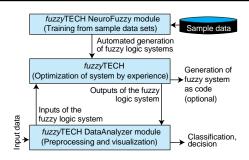

Figure 2—Linking the DataAnalyzer module with the NeuroFuzzy module and fuzzy TECH creates an integrated development environment for fuzzy data-analysis systems.

These parameters for classifying acoustic signals can be the result of a Fourier transform. Most cluster-analysis algorithms use training algorithms to configure themselves from given sample data sets.

Using fuzzy logic in cluster analysis enables fuzzy classes to be defined. So, even when a unique classification of some parameters isn't possible, a good final solution can still be derived.

Cluster analysis derives all necessary structural information by training from given sample data sets. This situation demands very high-quality sample data sets. Also, there are no explicit modifications of the resulting system, so optimization and verification are difficult tasks.

#### **RULE-BASED METHODS**

With fuzzy rule-based methods, ifthen rules represent the entire classification. This method is similar to the application of fuzzy logic in intelligent control. But in contrast to fuzzy logic in control applications, fuzzy-logic classification uses different inference and defuzzification methods.

The benefit of rule-based methods over cluster analysis is that the information flow in the system is completely transparent. Because fuzzy-logic systems are self-explanatory, explicit optimization and verification are easy.

But rule-based methods have a disadvantage as well. The entire system has to be built up manually, and unlike cluster analysis, no automated training exists. Despite these problems, however, fuzzy rule-based methods are the basis of many successful applications for data analysis and signal classifications [5].

#### ADAPTIVE RULE-BASED METHODS

The advantage of cluster analysis lies in its trainability, and the advan-

tage of rule-based methods lies in the inherent transparency of the system. But, some applications need trainability and transparency at the same time.

Combining a training algorithm with a fuzzy rule-based method makes for a successful solution. Because the training algorithm adapts the fuzzy rules and membership functions, and the behavior represents the sample data sets, this combination is called the adaptive fuzzy rule-based method.

Although there are many ways to adapt a fuzzy-logic system, the most widely used approach in industrial applications is the neurofuzzy technique. With this technique, learning algorithms developed for neural nets are modified so that they can also train a fuzzy-logic system [5].

This method learns from given sample data sets, and the learned result can be further enhanced by hand. For applications where only partial information for the solution stems from sample data, adaptive fuzzy rule-based systems are best. Another advantage of this method is a pure fuzzy-logic system that can be implemented even on inexpensive hardware platforms. You'll see more on this later.

#### SOFTWARE TOOLS

In most fuzzy data-analysis systems, the input data needs extensive preprocessing before reaching the fuzzy-logic system. Preprocessing can include filtering, linearizations, or Fourier transforms. These functions aren't part of most fuzzy-logic applications in industrial control and aren't usually part of fuzzy-logic software development tools.

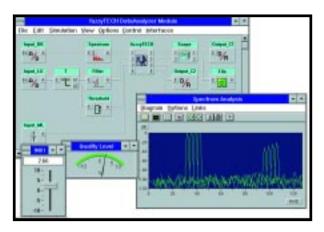

For the *fuzzy*TECH development system [6], data-analysis functionality is provided by an add-on tool called the DataAnalyzer module [7]. Figure 2 shows how *fuzzy*TECH and the Data-Analyzer and NeuroFuzzy modules can be linked to form an integrated design environment.

Linking these components enables the design of adaptive fuzzy rule-based solutions. If the NeuroFuzzy module is left out, only fuzzy rule-based solutions are possible.

Photo 1 shows a fuzzy data-analyzer solution that supervises the wear of a machinery tool during operation. The two upper-left function blocks drive A/D channels on a standard PC plug-in board. The upper channel links to a pressure-stripe sensor that acts as a microphone. The lower one links to a temperature sensor mounted at the tool.

The acoustic signal is preprocessed by a spectrum block (i.e., FFT) and input to the fuzzy-logic function block. The second input is the temperature signal filtered by a low-pass filter.

The third input is the direct temperature signal after a threshold function block. And the fourth comes from a visual inspection and is input by a slide in a separate window.

Meter and spectrum scopes display the outputs of the fuzzy-logic function block. If an overload occurs, a D/A channel sends the machine a speed override signal to avoid destroying the tool.

A file function block writes the evaluation result on disk. The Neuro-Fuzzy module sits on top of *fuzzy*TECH (see Figure 2), which is why you don't see it in Photo 1.

#### **FUZZY SHOE**

Now that you understand fuzzy-logic methods, let's look at the knee-surgery recovery problem I mentioned. Patients have to limit the strain on the knee during recovery. But, the knee has no

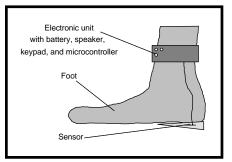

Figure 3—The orthopedic shoe consists of an electronic unit attached by Velcro over the ankle and a sensor in a silicone inlay.

strain sensor. By the time pain occurs, the knee has already suffered damage.

To solve this problem, I used a pressure sensor and fuzzy-logic dataanalysis system to design a biofeedback shoe inlay. The silicone inlay contains a pressure sensor made of conducting polymer and is wired to an electronic unit in a belt that attaches to the ankle by Velcro (see Figure 3).

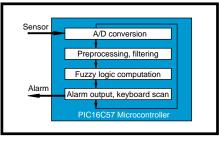

The electronic unit contains the microcontroller, battery, speaker, and keypad. The speaker warns the user when the strain limit is reached, and the 8-bit micro runs the A/D conversion, signal preprocessing, and fuzzy data-analysis system.

The objective for the fuzzy dataanalysis system is to estimate the internal strain in the knee from the pressure signal. If 80% of the maximum acceptable load is reached, a beep warns the user to take it easy.

If the 90% level is reached, a repeating beep tells the user not to use the leg for a while. And, if the strain is over the maximum threshold set by the doctor, the beep sounds continuously.

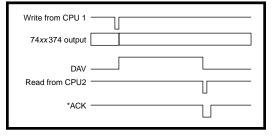

Figure 4—The complete control loop, reading in sensor data, preprocessing, fuzzy-logic computation, and data output, is all implemented on one microcontroller.

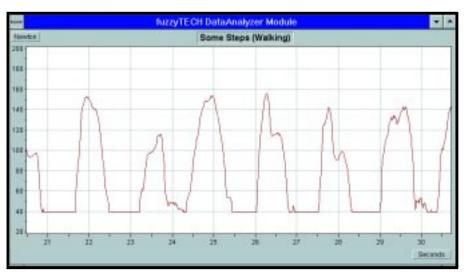

The difficulty in this situation is estimating the internal strain in the knee from just the pressure signal. Photo 2 displays the pressure sensor signal for a typical sequence of steps. In order to get more information from this signal, preprocessing derives additional inputs to the fuzzy data-analysis system.

In total, there are four inputs to the fuzzy-logic function block:

- Act\_Peak—peak pressure of the current step

- Act\_Slope—slope of the pressure signal of the current step

- Hist\_Short—feedback of the average output signal from the fuzzy-logic function block for the last 5 min. and an indicator of the current strain on the knee

- Hist\_Long—feedback of the average output signal of the fuzzy-logic function block of the last 48 h and an indicator of long-term strain on the knee

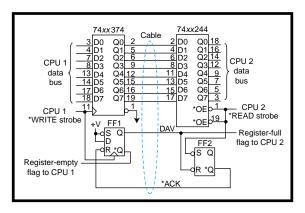

Photo 3 shows the fuzzy-logic system in the data analyzer, with the upper window showing the system structure. The output variable Alarm stems from a rule block with the input variables ActualLoad and TimeLoad, which are outputs of other rule blocks.

ActualLoad computes from the two input variables (Act\_Slope and Act\_Peak) that are input variables of the fuzzy-logic function block. The dataanalyzer module computes these variables from the pressure sensor signal.

TimeLoad computes from the inputs Hist\_Short and Hist\_Long. The data-analyzer module computes these inputs using low-pass filtering from the system's output signal. Photo 1—Developing a fuzzy dataanalyzer solution is completely graphical. Configuring predefined function blocks integrates conventional signal-analysis techniques and fuzzy logic. Fuzzy logic is also represented as a function block.

The lower-left window shows a membership-function definition. Most linguistic variables use two or three membership functions of standard MBF type. The lower-right window shows four rules of the upper rule block. The 39 rules in the system were derived in close cooperation with orthopedists.

Because no good sample data for the strain estimation in a knee exists, the NeuroFuzzy module wasn't used. Under the nomenclature I discussed earlier, this application uses fuzzy rule-based methods.

Using fuzzy logic here means that the rule set is easy to modify. As an example, by designing a rule set that evaluates steps and their fit to an optimal curve, runners can improve their running style with this intelligent biofeedback technique.

Figure 4 shows the total implementation on a PIC16C57 microcontroller. The ADC transforms the resistance of the pressure sensor into a digital 10-bit value. Preprocessing and filtering get the four input variables for the fuzzylogic computation shown in Photo 3.

Depending on the strain rating, the speaker outputs the alarm and the keypad is scanned. The fuzzy-logic system requires ~20 bytes of RAM and 590 words of ROM on the PIC16C57 [8]. The code was generated by the *fuzzy*-TECH Edition that generates fuzzylogic systems as assembly code for standard microcontrollers.

This case study demonstrates how you can use innovative software design techniques like fuzzy logic to implement even complex functions within the limits of a low-cost microcontroller.

With graphical software development tools, you can focus on solving your problem. Turning your solution to highly optimized assembly code for microcontrollers becomes a matter of a mouse click.

The fuzzy shoe is a good example of how intelligent software design techniques lead to innovative products.

Photo 2—A walking sequence shows the amount of pressure placed on the sensor with each step.

Photo 3—Here's the structure of the fuzzy-logic function block for the fuzzy data-analysis system. The four inputs are compared to the set rules, and the appropriate response is generated.

Just imagine shoes and other devices that enable you to improve your exercise and avoid damaging your body!

Constantin von Altrock began research on fuzzy logic with Hewlett-Packard in 1984. In 1989, he founded and still manages the Fuzzy Technologies Division of Inform Software Corp., a market leader in fuzzy-logic development tools and turn-key applications. You may reach him at cva@inform-ac.com.

#### REFERENCES

- J. Bezdek, E. C-K. Tsao, and N. Pal. "Fuzzy Kohonen Clustering Networks," FUZZ-IEEE Conference, 1992, 1035–1043.

- [2] A. Kandel, Fuzzy Techniques in Pattern Recognition, New York, NY, 1982.

- [3] V. Watada, "Methods for Fuzzy Classification," *Japanese Journal* of Fuzzy Theory and Systems, 4, 149–163, 1992.

- [4] H.J. Zimmermann, *Fuzzy Set Theory—and its Applications*, Boston, MA, 1991.

- [5] C. von Altrock, Fuzzy Logic and NeuroFuzzy Applications Explained, Prentice Hall, Englewood Cliffs, NJ, 1995.

- [6] Microchip Technoloy, *fuzzy-TECH MP Edition Manual*, 1994.

- [7] Inform Software Corp., fuzzy-TECH 5.2 DataAnalyzer Module Manual, 1998.

- [8] Inform Software Corp., Fuzzy Logic Benchmarks for Standard MCUs, www.fuzzytech.com, 1994.

#### RESOURCES

- C. von Altrock, B. Krause, and H.J. Zimmermann, "Advanced fuzzy logic control of a model car in extreme situations," *Fuzzy Sets and Systems*, **48:1**, 41–52, 1992.

- C. von Altrock and B. Krause, "On-Line-Development Tools for Fuzzy Knowledge-Base Systems of Higher Order," Proceedings of the 2nd Int'l Conference on Fuzzy Logic and Neural Networks, 1992.

- C. von Altrock, B. Krause, and H.J. Zimmermann, "Advanced Fuzzy Logic Control Technologies in Automotive Applications," IEEE Conference on Fuzzy Systems, 831–842, 1992.

- C. von Altrock, "NeuroFuzzy Technologies," *Computer Design Magazine*, June 1994.

- C. von Altrock, H.O. Arend, B. Krause, C. Steffens, and E. Behrens-Rommler, "Customer-Adaptive Fuzzy Control of Home Heating System," IEEE Conference on Fuzzy Systems, 1994.

#### SOURCES

#### PIC16C57

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 899-9210 www.microchip.com

#### *fuzzy*TECH

Inform Software Corp. (630) 268-7550 Fax: (630) 268-7554 www.fuzzytech.com

### C++ Lite

#### FEATURE ARTICLE

John Carbone

### A C++ Dialect for Embedded Systems

Want to be able to maintain valuable C++ concepts while eliminating those responsible for boosting memory requirements and reducing efficiency? John shows us how with EC++, a new dialect that targets embedded systems. n many embedded system designs, programmers can leverage all the features of C++, such as classes, templates, exception handling, and class inheritance, that have proven so useful for mainstream computer applications. But, some of these features bloat the compiled code, significantly increasing memory requirements while reducing execution speed.

A new C++ dialect, Embedded C++ (EC++), has been developed by an industry-standards committee to address the limitations of C++ in embedded applications, where memory is limited and 32-bit processors are prevalent.

EC++ maintains the most valuable C++ concepts while eliminating those most responsible for boosting memory requirements and reducing efficiency. Ideally, designers will be able to choose whether to use EC++, C++, or a hybrid of the two to match their application requirements.

The object-oriented features of C++ simplify source code and the development process by reusing code modules and placing burdensome housekeeping functions (e.g., memory allocation and range checking) in the class definitions and away from the main application. Although C++ code is typically more readable than standard C code, compiled C++ code can swell by a factor of five or more relative to a standard C implementation. This increase caused a group of companies, led primarily by Japanese microprocessor vendors, to develop the EC++ specification and to prompt the development of the first EC++ compiler.

EC++ is a proper subset of C++. Among the C++ features it omits are multiple inheritance, virtual base classes, templates, exceptions, runtime type identification, virtual function tables, and mutable specifiers (see sidebar "EC++ Excludes Problematic Features" for details).

Although each of these features is useful in its own right, none is compelling enough for a sufficiently broad range of embedded applications. Support for some of the features tends to bloat the generated code, whether or not the features are used in an application.

Exception handling proves to be one of the worst offenders and can adversely affect the deterministic response to external events required in real-time systems. Eliminating support for a number of C++ features substantially reduces the size of the compiled code and improves run-time efficiency.

To understand the range of features that differentiate standard C, EC++, and C++, consider two examples of EC++ and C++ constructs. Listing 1 illustrates some of the key advantages that EC++ offers over straight C.

The concept of classes is probably the single most important concept brought about by C++ and one that is supported in EC++. Classes build on the data structures found in standard C.

Besides allocating memory for a number of variables of mixed types, classes can initialize variables, dynamically allocate additional memory for variables and arrays, perform range checking, and perform other useful duties. In C programs, these tasks were typically scattered throughout the main code.

#### **CLASSES AND OBJECT DEFINITION**

An embedded application such as a data-acquisition system might use such a class to create arrays for storing data **Listing 1**—This embedded C++ example of a simple Array class does range checking on the creation of an array and on array subscripting operations.

```

#include <iostream>

using namespace std;

extern "C" void exit(int);

// Deal with run-time error. A real embedded application would

// probably choose a different error-handling strategy.

void die(const char *msg, int n)

{

cout << msg << n << endl:

exit(1);

}

class Array{

// the integer array class

private:

int *elements;

// array elements

// array size

int element_cnt;

public:

Array(int n) : element_cnt(n) { // construct new array

if (n > 0)

elements = new int[element_cnt];

else

die("Bad Array size ", element_cnt);

3

int & operator [](int indx) const {

// overloaded subscripting operator

if (indx < 0 || indx >= element_cnt)

die("Bad Array index ", indx);

return elements[indx];

int size() { return element_cnt; } // return size of array

};

main()

{

Array a(6);

for (int i=0; i<a.size(); i++)</pre>

a[i] = i;

for (int i=0; i<a.size()+1; i++) // error on a[7]</pre>

cout << i << ". " << a[i] << endl;

};

```

Listing 2—Templates are a powerful feature but should be used carefully in space-sensitive applications.

```

template <class T>

class Array{

private:

T *elements;

// array elements

// array size

int element_cnt;

public:

Array(int n) : element_cnt(n){ // construct new array

if (n > 0)

elements = new T[element_cnt];

else

die("Bad Array size ", element_cnt);

T & operator [](int indx) const{

// overloaded subscripting operator

if (indx < 0 || indx >= element_cnt)

die("Bad Array index ", indx);

return elements[indx];

int size() { return element_cnt; // return size of array

};

```

samples. The array class named Array in Listing 1 includes two integer members. The first is an elements pointer to members of an array, and the second tracks the array size.

As the main() portion of this code implies, you can use the declaration Array a(6) to create an array object with the name a that contains six elements. The class definition includes several important features such as the constructor code necessary to create the array and to ensure that the size specified is greater than zero.

The constructor is located in the public section of the class definition. It provides a window through which code located outside the class definition can access the elements and element\_ cnt class members.

Each time an array of type Array is created, the compiler automatically calls the constructor function Array (int n). This function assigns the value passed in the array declaration to element\_cnt, checks for a valid size, and allocates space in main memory for the array by calling new.

In this simple example, a bad array size (e.g., zero or a negative number) causes the constructor to call a simple die function that outputs an error message. An embedded system would probably use a more elaborate scheme to handle run-time errors.

The Array class also demonstrates two other key features of classes in EC++ or C++—function definitions within a class and overloaded operators. First, consider the size() function, which illustrates the simpler of the two concepts.

Because element\_cnt is a private member of the class, code outside the class can't directly access the counter. However, the size() function enables the two for loops located in main() to indirectly access element\_cnt for use as an upper limit of the loop.

#### **OVERLOADED OPERATORS**

The class definition also includes an example of overloaded operators. Operator overloading enables you to develop new definitions of standard C/C++ operators such as =, >, or + that are customized for the type of object defined in a class. For example, you could develop a class that defined an object like a circle or sphere. Having done so, you might want to compare the size of two objects (A and B) that were created using the class definition.

The expressions A>B or A==B have understood meanings when A and B are integers, but the compiler won't know how to compare abstract entities such as spheres of a given size or composition. To make it possible to operate on complex user-defined types while using a readable C-like syntax, C++ and EC++ allow operator overloading.

The code in Listing 1 overloads the subscripting operator [] that stores the index for an array. In this case, the overloaded function gets called each time an indexed array reference occurs (e.g., a[i]=i).

Rather than changing the effective meaning of the subscripting operator, the overloaded operator automatically detects out-of-range array indices. Note that, should you execute the sample program, the output statement used in the second loop would generate an Listing 3—This more capable main program uses templates to enable multiple uses for the Array class.

```

main()

{

Array<int> a1(6);

for (int i=0; i<al.size(); i++)

a1[i] = i;

for (int i=0; i<al.size()+1; i++) // error on a[7]

cout << i << ". " << a1[i] << endl;

}</pre>

```

error on the sixth pass through the loop because a[7] exceeds the valid index test.

As you can see, classes significantly streamline the mainline code in an EC++ or C++ program. A C program requires explicit data-structure definitions for every array declared, while EC++ or C++ handles creation of all similar objects with a single class.

Also, C programs require memoryallocation, error-checking, and elementcount code in the main part of the program or in dedicated C functions. The compiled-code overhead of EC++, relative to standard C code, is minimal as well. Adding classes and overloaded operators only marginally increases the generated code size.

Understand that you can't realize these code savings simply by avoiding the memory-hungry C++ features in an application and then compiling the code with a standard C++ compiler. The consequences of this approach are detailed in the sidebar "Why You Need an EC++ Compiler."

#### ADDING TEMPLATE SUPPORT

Despite the advantages offered by EC++, some omitted C++ functions are extremely attractive for certain applications. Compiler vendors can provide programmers some flexibility as to what C++ functions are available for use in each application.

For example, you can use a compiler directive with Green Hills' C++/EC++ compiler to limit the source code to the EC++ subset and get the savings in code size and the boost in efficiency. You can also use compiler switches to add support for one or a few specific C++ functions that are left out of EC++.

The granular support for optional C++ features enables programmers to trade off compiled code size with ease of development and maintainability. Green Hills' C++/EC++ enables the programmer to choose libraries appro-

priate to the application, eliminating significant amounts of unnecessary library code.

Templates are a good example of a C++ feature that isn't included in EC++ but that provides significant advantages in development with only a modest increase in memory requirements. Listings 2 and 3 illustrate the benefits.

#### Why You Need an EC++ Compiler

Because EC++ is a proper subset of C++, you might think you can achieve the efficiency promised by EC++ by avoiding certain C++ features. You can compile EC++ code on a C++ compiler, but you'll find that the resulting code still requires significantly more memory than if you'd used an EC++ compiler.

Three problems arise when you try to increase efficiency using EC++ code and a standard C++ compiler. First, the compiler still uses C++ libraries and links a lot of code that isn't required for your application into the finished product. EC++ uses libraries that are optimized for the new dialect and generates smaller, more efficient code.

As well, EC++ compilers can achieve superior optimization relative to C++ compilers. They opti-

mize code without presuming that complex features like exception handling may be used.

And lastly, standard C++ compilers have no way to enforce EC++ compliance within a programming team. With a standard C++ compiler, one out of many programmers on a team can use an offending feature and spoil the efficiency of the entire code base.

Green Hills Software developed a sample EC++ program to demonstrate memory efficiency. The program solves a form of the classic traveling-salesman problem that's often used to teach programming. When compiled on the Green Hills C++/EC++ compiler using EC++ mode, the total code size is 57 KB. When the same source file is compiled in C++ mode with no exception-handling library, the code size is 322 KB. Adding an exceptionhandling library increases the code size to 378 KB. In Listing 1, Array is defined so that all members have to be integers. With EC++, you need to define additional classes to handle arrays for short, long, char, or floating-point data types. Templates permit a single class definition to support creation of arrays for any valid C++ data type.

Listing 2 shows that the only real addition to the Array class definition with a template is the template construct that precedes the class definition and the use of the T specifier each time the code addresses an element of the array. Consider Listing 3 and you'll see that Array works equally well to instantiate any type of an array.

The example shows an array, a1, that stores integer data types. Simply changing the int to short permits support for the short data types. The main() code segment can reuse the Array class to define multiple arrays with any data type. An embedded system performing data acquisition, for example, could require floatingpoint arrays.

Using the templates shown here would result in little or no increase in compiled code size. But, be aware that the code size you realize depends on your application.

Much of the code bloat in C++ code comes not from using a feature like a template but from referencing templates found in large C++ libraries. Reference a standard template and you end up compiling many unnecessary things in the library.

#### **COMPILER SUPPORT**

EC++ gives embedded-system programmers a valuable path to leverage the most significant aspects of an object-oriented language. With formal approval of the EC++ standard imminent, programmers should demand C++ compilers with EC++ support.

However, to minimize development time and simplify code maintenance, programmers shouldn't automatically dismiss all the C++ features eliminated in EC++. Experienced C++ programmers will be able to use a number of C++ features in an EC++ environment and not decrease efficiency.

EC++ eliminates features such as templates, namespaces, mutable speci-

#### **EC++ Excludes Problematic Features**

Although EC++ retains the most important features of C++ (e.g., classes), it eliminates other features because of inefficient memory, difficulty of use, or lack of popularity. Consider the list of omitted features:

- multiple inheritance and virtual base classes

- new-style casts

- mutable specifiers

- namespaces

- run-time type identification

- exceptions

- templates

Listing 1 illustrates the basics of classes, but multiple inheritance and virtual base classes fall at the complex end of the C++ class concept. Programmers often use a hierarchical structure to define complex classes.

For example, a base class called Shape might define any geometrical shape and have an attribute such as color. Through the concept of inheritance, classes like Circle or Square could be derived from shape with additional attributes such as radius or width.

Both EC++ and C++ enable programmers to build multilevel class hierarchies in a linear fashion. C++ also enables multiple inheritance in which the programmer defines a new class based on two or more peer classes.

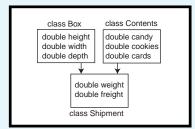

A programmer could define one class called Box and a second class called Contents (see Figure i). A new class called Shipment can be derived from Box and Contents. Multiple inheritance can be valuable in a number of applications and is regularly used in graphical desktop environments.

In Microsoft Windows, a useful object class can be derived based on a Window class with display attributes such as size or borders, a Menu class with attributes like menu names and styles, or a Display class with attributes that describe objects displayed in a window. Virtual base classes can be used with multiple inheritance to share a base class that's inherited multiple times in a derivation hierarchy.

Some embedded applications, including embedded-PC applications, can make use of multiple inheritance and virtual base classes, but they're not nearly as useful as in desktop applications. Supporting multiple inheritance in a compiler carries a significant burden and the technique is tricky. That's why it was omitted in EC++.

#### **Explicit Type Conversion**

While multiple inheritance may be difficult to use, other C++ features were omitted from EC++ because they are seldom used in any application. Good examples are the dynamic\_cast feature that was added as part of the new-style casts, and mutable specifiers.

**Figure i**—Multiple inheritance allows Shipment to use the properties of both Box and Contents.