THE COMPUTER APPLICATIONS JOURNAL

#104 MARCH 1999

## AUTOMATION AND CONTROL

**Build a CEBus Plug-and-Play Relay**

**A Chipset Solution for Vehicle Control**

**Barcode Decoding**

## TASK MANAGER

#### **Archival Alternatives**

m not a terrible packrat, but there are some things I'll just never throw away: my fourth-grade report on "Venus: The Veiled Planet," an English project illustrating Booth Tarkington's quote "It's the land of nowadays that we never discover," a university paper detailing the vocabulary similarities of Russian and Norwegian....

Sure, I know that none of these papers will serve a great purpose for all humankind. It's just for fun. Something to show my daughter someday.

I keep a lot of *useful* information in my bookshelves, too. But, when it comes to keeping useful information, well, that's where the trouble starts.

What am I going to need tomorrow, next month, next year? It's just impossible to tell. I've got to keep it all. But then, how am I going to find what I'm looking for when the situation does arise? Sorting through all those files and books for one piece of crucial information is not my idea of a swell time.

Steve, I have to agree with you. Paper isn't dead. It's alive, well, and taking over my attic!

Seems that a lot of *Circuit Cellar* readers are in a similar bind. Whether you read the magazine in the office or at home, when you're finished with it, you put it on your shelf. According to our latest survey, nearly all *Circuit Cellar* readers keep every issue. We've passed issue 100, so you must be getting buried by now, right?

It's the curse of useful information. You want to keep it, refer to it. You want it to be there when you need it. Of course, when you do need it, you have to search through all those back issues for that one article or even that one schematic that has the answer you're looking for.

And then there's the sheer weight of it all. I can't tell you how many requests we've had over the years for back issues on CD-ROM simply because CDs are so much easier to move than boxes of paper.

So, it's happened at last—Circuit Cellar back issues on CD-ROM! It took us some time, some investigating, some investment, but I think you'll appreciate the result. This spring, two CD-ROMs will be available: one of the first five years (issues 1–30), and one of years six through ten (issues 31–89). These versions will have black and white pdf files of the scanned magazine, and most importantly, you'll be able to search them digitally.

Starting this June with *Circuit Cellar* 1998 (issues 90–101), annual CD-ROMs will be made as well. The annual versions will have full-color pdf files created directly from the layout files (not scanned pages).

As well, on every CD-ROM, we'll include the complete *Circuit Cellar* index and the relevant software for the issues on that disk.

We believe these CD-ROMs will be a boon, even if you're partial to paper. After all, it's a lot easier to stick a CD in the drive and look up that project from who-knows-how-many years ago than it is to go hunting through stacks of magazines. Once you find what you're looking for, you can then read the information off the pdf file or go pull that issue off the shelf.

Of course, CD-ROMs aren't always the answer. If you want to take a walk down memory lane and show all those projects to your kids, isn't it a bit more fun to sift through all the back issues?

Eli.

elizabeth.laurencot@circuitcellar.com

# CIRCUIT CELLAR®

#### THE COMPUTER APPLICATIONS JOURNAL

EDITORIAL DIRECTOR/PUBLISHER

Steve Ciarcia

MANAGING EDITOR

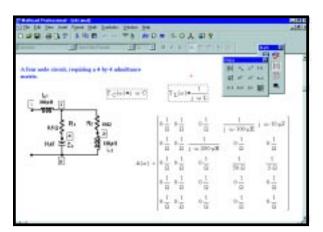

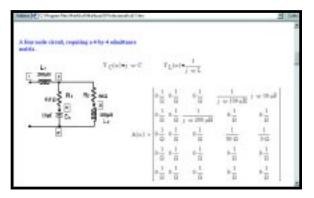

Elizabeth Laurençot

TECHNICAL EDITORS

Michael Palumbo

Rob Walker

WEST COAST EDITOR

Tom Cantrell

**CONTRIBUTING EDITORS**

Ingo Cyliax Ken Davidson Fred Eady

**NEW PRODUCTS EDITOR**

Harv Weiner

ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella

CHIEF FINANCIAL OFFICER

Jeannette Ciarcia

ART DIRECTOR KC Zienka

ENGINEERING STAFF Jeff Bachiochi

PRODUCTION STAFF

Phil Champagne

John Gorsky

James Soussounis

PROJECT EDITOR

Janice Hughes

**EDITORIAL ADVISORY BOARD**

Ingo Cyliax Norman Jackson David Prutchi

Cover photograph Ron Meadows—Meadows Marketing

PRINTED IN THE UNITED STATES

#### **ADVERTISING**

ADVERTISING SALES MANAGER

Bobbi Yush Fax: (860) 871-0411

(860) 872-3064 E-mail: bóbbi.yush@circuitcellar.com

ADVERTISING COORDINATOR

Valerie Luster Fax: (860) 871-0411

(860) 875-2199 E-mail: val.luster@circuitcellar.com

#### CONTACTING CIRCUIT CELLAR INK

#### SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION:

TELEPHONE: (860) 875-2199

FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor. Circuit Cellar INK. 4 Park St., Vernon, CT 06066

AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles, contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA. MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA19043-9613.

Circuit Cellar INK® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions,

or information published in Circuit Cellar INK®. Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

| 12       |                                                   | Bus Plug-and-Play Relay<br>House                                                       |                                                              |    |  |

|----------|---------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------|----|--|

| 18       | In Black and White A Barcode Decoder Craig Pataky |                                                                                        |                                                              |    |  |

| 22       | A Ch                                              | <b>ng in New Directions</b><br>ipset for Vehicle Control Systems<br><i>Bannatyne</i>   |                                                              |    |  |

| 28       | Web-<br>Bob I                                     | Based Circuit Engineering<br>Perrin                                                    |                                                              |    |  |

| 62       | ,<br>1                                            | MicroSeries<br>TPU<br>Part 3: Programming in Microcode<br>Joe DiBartolomeo             |                                                              |    |  |

| 70       | ,                                                 | From the Bench<br>TAG<br>Working with CoolPLD<br><i>Jeff Bachiochi</i>                 | Task Manager<br>Elizabeth Laurençot<br>Archival Alternatives | 2  |  |

| 76       | ]                                                 | Silicon Update<br>Flash Forward                                                        | Reader I/O/<br>Circuit Cellar On-line                        | 6  |  |

|          |                                                   | Гhe 68HC908GP20<br>Tom Cantrell                                                        | New Product News<br>edited by Harv Weiner                    | 8  |  |

|          |                                                   |                                                                                        | Advertiser's Index/<br>April Preview                         | 95 |  |

|          |                                                   |                                                                                        | Priority Interrupt Steve Ciarcia Paper is Dead?              | 96 |  |

| 4        |                                                   | veau PC<br>ed by Harv Weiner                                                           | 797                                                          |    |  |

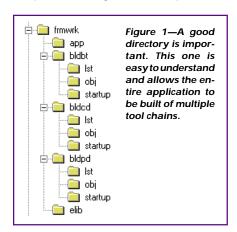

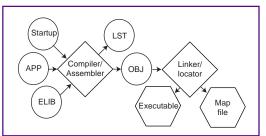

| 43       |                                                   | pedded Framework and Foundations nard Russell                                          |                                                              |    |  |

| <b>7</b> | 9 RPC                                             | <b>Real-Time PC</b> Embedded RT-Linux Part 5: Real-Time Programming <i>Ingo Cyliax</i> | 1.                                                           |    |  |

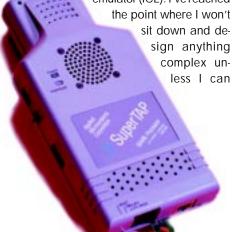

| 5'<br>1  | 7 APC                                             | Applied PCs ICE on Tap Part 1: SuperTAP Setup Fred Eady                                |                                                              |    |  |

## READER I/O

#### MISSING PARTS

In "Mobile Environmental Control" (INK 100), Dan Leland described a great project that enabled his quadriplegic friend to remotely control television, VCR, and other home-control settings.

I was interested in using the technology he mentioned so I contacted Universal Electronic for the remote control. However, I was told that they no longer make the OFA8 remote. Is there a substitute model? A friend asked me to build a similar project and it's only possible if a serial remote is available.

Raymond Lagacé rlagace@cyanic.org

I recently found out myself that Universal Electronics, who manufactures the One-For-All line of infrared remotes, decided to give up the business. I

couldn't believe it! After all, they were the leader in that area.

I've had a few people contact me about this matter, and there are some options. Some OFA8s may still be available from either www.homecontrols.com or www.smarthome.com. These mail-order companies offer all kinds of home-automation technology.

Apparently, Universal Electronics licensed their technology to a company called Impact Merchandise. Impact is going to produce OFA models 8200, 8080, and 8090 only. These units have the necessary serial port but, I've never mapped the command structure so you'll have to figure out the necessary serial commands.

Although the OFA models are not included on their website, you can reach Impact Merchandise at (800) 323-9688 or (925) 373-9700 for more information on the product line.

Dan Leland

## Circuit Cellar

## www.circuitcellar.com

#### Newsgroups

If you miss the Circuit Cellar BBS, then the cci newsserver is the place to go for on-line questions and advice on embedded control, announcements about the magazine, or to let us know your thoughts about Circuit Cellar. Just visit our home page for directions to become part of the newsgroup experience.

> The March **Design Forum** password is: Tools

#### New!

- If the "Web-Based Circuit Design" article in this issue has you interested in online simulation, check out the online hardware simulators hosted in Design Forum.

- Wouldn't it be great if you could remember exactly which issue of Circuit Cellar contained certain projects or applications? And wouldn't it be helpful if there was an easier way to search past articles for certain topics (besides flipping through the pages of 104 back issues)? Stop wishing and start clicking! Head over to our homepage to find out how to get your searchable CD-ROM of the Circuit Cellar back issues. Don't forget to order before April 1 for additional savings.

- All aboard the INFO Express! Loaded with the latest news and information about Circuit Cellar INK as well as any additions or changes to our web site, the INFO Express stops right at your e-mail address. Visit our homepage to sign up for this new service from Circuit Cellar.

- While you're working on your entry for Design99, don't forget to check the Design99 Rules Update section for the latest updates on contest guidelines.

#### Vesign Forum

Be sure to visit the Circuit Cellar Design Forum this month for more great online technical columns and applications. The Design Forum password is your key to great new columns, monthly features, and PIC Abstracts.

Silicon Update Online: Yet Another Architecture?—Tom Cantrell

Lessons from the Trenches: Getting a Head Start on Software Development—In

the Real World—George Martin

Building an Automatic Guitar Tuner: Massimo Porzio Embedded Development Tools: Richard Russell

## NEW PRODUCT NEWS

**Edited by Harv Weiner**

#### UNIVERSAL SIGNAL-CONDITIONING MODULES

The **ADAM-3000** signal-conditioning modules can process a wide range of sensor and transducer signals and provide excellent protection against the harmful effects of ground loops, motor noise, and other types of electrical interference. The modules are ideal for industrial equipment, data acquisition, or control devices that require external signal conditioning.

The ADAM-3000 modules are designed to operate in a wide range of conditions at minimal power consumption. They accept voltage, current, or thermocouple signals as input and provide either voltage or current output to the PLC or controller.

The thermocouple module features built-in linearization circuitry and cold junction compensation to ensure accurate temperature measurement. The modules use optical isolation technology to provide full three-way (input/output/power) isolation to 1000 VDC.

The modules are factory precalibrated for all standard input and output ranges. They can isolate and convert various combinations of user-customized analog and industry-standard signals. DIP-switch range selection eliminates the need to order different modules for different input and output signals.

Modules can be easily mounted on a standard DIN rail. Signal wires are connected through a front-access screw terminal, as is the +24-VDC required power. Two-wire input/output cables help simplify the wiring.

Prices range from \$70 to \$210 in single quantities.

American Advantech Corp. (408) 245-6678 Fax: (408) 245-8268 www.advantech-usa.com

#### **PROTOTYPING TOOL**

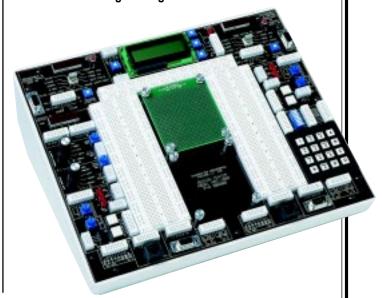

**Design Center** is a stand-alone self-contained design development/training tool that supports students and engineers involved in the prototyping of microcontroller-based electronic circuits. It enables easy testing of software and hardware components in designs that use embedded microprocessors.

Design Center features three adjustable DC voltage supplies, a 60-Hz reference, a frequency generator (to 1 MHz), and a pulse generator. Also included are common peripheral components and test equipment for building and debugging microcontroller-based circuits, such as two RS-485 interfaces, two RS-232 interfaces, a  $4\times 4$  matrix keypad, eight DIP switches, four pushbuttons, six LEDs, and a four-digit alphanumeric LED display. Not to be forgotten are the two SPDT slide switches, five potentiometers, two DE-9 connectors (one male, one female), and a  $2\times 16$  LCD module.

A unique adapter cradle permits current and future components in just about any package to be used. Design Center also has two identical measurement and control modules (MCM), which are intelligent built-in meters that can measure voltage, current, frequency, period, duty cycle, or pulse count of an input signal. Each MCM has an RS-232 port (with female DE-9 connector) which, when connected to a PC, enables monitoring or control of the circuits under test.

Pricing for the Design Center starts at \$997.

Diversified Engineering (203) 876-7408 www.diversifiedengineering.net

## NEW PRODUCT NEWS

#### HIGH-SPEED MICROCONTROLLER

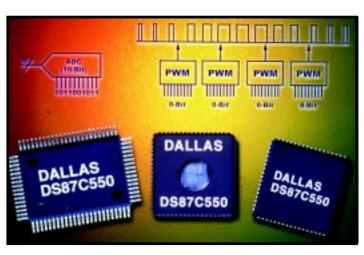

The **DS87C550** is a high-speed microcontroller with an on-chip ADC and PWM. It is 100% code- and pincompatible with the industry-standard 8051. The microcontroller is ideal for battery chargers, industrial and research test or diagnostic instruments, household appliances, TVs, VCRs, stereos, computers and printers, automobile engines, and climate or environmental controls.

The DS87C550 executes 8051 instructions up to three times faster than the original 8051 architecture at the same crystal speed, thanks to an efficient instruction-execution method that eliminates wasted clock and memory cycles. As a result, an instruction typically uses four clock cycles instead of 12, thereby tripling the speed of a standard 8051. A maximum crystal speed of 33 MHz gives the DS87C550 apparent execution speeds of up to 99 MHz, and a single-cycle instruction executes in just 121 ns.

This device includes a 10-bit ADC, four channels of 8-bit PWM, 8-KB EPROM, two full-duplex serial ports, three 16-bit timer/counters, as well as four capture and three compare registers. Also featured are a watchdog

timer, brownout detection, power-fail reset, and 16 interrupt sources.

Pricing for this device starts at \$12.60 each in 1000-piece quantities. It's also available in 68-pin PLCC, 68-pin windowed CLCC, and 80-pin PQFP packages.

Dallas Semiconductor (972) 371-4448 Fax: (972) 371-3715 www.dalsemi.com

## EW PRODUCT NEWS

#### 8051 IN-CIRCUIT EMULATOR

The emulator system

is made up of

The iceMaster-8051-SF ICE provides full-featured real-time transparent emulation at frequencies up to 40 MHz. The unit supports bank switching and timestamp and also includes 512 KB of code memory and 512 KB of XDATA memory. A 64-KB trace buffer reduces debug time.

the user create macro-like routines for repetitive testing. Other features include an elapsed timer and two pass count/delay timers.

The iceMaster-SF has a command window that lets

interchangeable probe cards and a PC adapter connected to an emulator base. Full portability is achieved via a 57.6-kbps serial interface between the emulator base and PC. The probe cards plug directly into a target application or can operate in stand-alone mode.

A Windows-based host interface enables high productivity. The iceMaster-SF supports most third-party assemblers and compilers. It also features full symbolic and source-level debugging. The context-sensitive hyper-

> text and hyperlinked help system make the interface easy to learn and use. The iceMaster-SF can handle any large or complex 8051 project and supports all major C compilers. The complete system costs less than

> > \$5000.

MetaLink Corp. (602) 926-0797 Fax: (602) 926-1198

www.metaice.com

## EW PRODUCT NEWS

#### INDUSTRIAL SMART CAMERA

The VC Series of smart cameras are complete machine vision systems that include up to 8 MB of RAM, 2 MB of flash memory, and a powerful DSP. The  $120 \times 50 \times$ 35 mm camera features optically isolated industrial I/O (four 12-24-V inputs and four 150-mA out-

puts), an RS-232 serial interface, RS-170/CCIR video output, and pixelidentical sensor readout.

They feature shutter speeds from 1/100,000 s to 20 s. CCD sensors with up to  $1280 \times 1024$  pixels provide high resolution and sensitivity, allowing accurate measurements down to 1 µm. Progressive scanning, a color sensor, and flicker-free

SVGA video output are offered as options on some models.

A normalized grayscale correlation (NGSC) software library is available for use in addressing precision registration, alignment, and robot-guidance tasks. The software can be used to create correlation-based OCR, OCV, logo/

mark inspection, IC pin-one indicator detection, and golden template comparison inspection solutions.

VC Series-compatible software decodes the two-dimensional ECC200 data matrix codes used in various industries.

> An integrated Windowsbased development environment, which includes a C cross-compiler, real-time OS, and a large optimized image processing library is available.

Pricing ranges from \$1150 to \$3953.

**Vision Components** (617) 492-1252 Fax: (617) 492-1252 www.vision-components.de/

11

#### **FEATURES**

12

A CEBus Plug-and-Play Relay

FEATURE ARTICLE

**Peter House**

18

In Black and White

22

Driving in New Directions

28

Web-Based Circuit Engineering

## A CEBus Plug-and-Play Relay

Now that prices are falling for a complete receive-only device, it's getting even easier to create a low-cost consumer electronics device. Listen up to see how Peter built this CEBus relay. The secret for its success is in the power line.

y idea of a low-cost device is one that sells for around \$20. This price requires the bill of materials to run between \$5 and \$10, depending on the means of distribution.

Before January 1998, a complete chipset for implementing consumer electronics bus (CEBus) communications cost about \$15 in 100,000-piece quantities and took two or three ICs. That price didn't include the power supply, microcontroller, or application circuit (relay or triac). Today, however, a complete receive-only device can be purchased and imported (in quantity) for about \$12.

#### STARTING THE CEBus

The CEBus standard, originally published in 1992, was updated as ANSI/EIA-600 in 1998. It describes communication between devices in the home over five media—infrared (IR), coax (CX), twisted pair (TP), radio frequency (RF), and power line (PL).

Because we all have power lines in our houses, the power line is the most practical medium for low-cost implementation and universal usage. The CEBus standard for PL describes everything from low-level data transmission to the common application language (CAL), which is the high-level language used to send control information.

Using the CEBus standard as a guide, you can build a device that sends CAL messages to a device made by someone else. And, you have pretty good assurance the message will be understood.

Unfortunately, the CEBus standard doesn't give a clue about which messages to send at any given time. Some messages are easy to figure out, but others aren't so simple.

Well, if you want a light turned on, you send a light control message with the command to turn on the light. Easy.

But, let's say you plug in a new device from one of those home improvement places. What message(s) does it send and how does it link up with other devices? The home plugand-play (HomePnP) standard attempts to answer these questions.

#### WHAT IS HOMEPnP?

Three companies with an interest in CEBus and consumer electronics started the HomePnP specification. Microsoft, Honeywell, and Intel wanted to know how a device interacts with other similar devices on the network as far as addressing and binding to other devices to share control information.

If you look at the CEBus specification, you might conclude that it tells the devices how to communicate with each other. Unfortunately, it doesn't tell devices what to say. That's where the HomePnP specification takes over.

HomePnP is an industry specification managed by the CEBus Industry Council to ensure interoperability at a system level. It's the system-level specification used to tie together individual CEBus-compatible devices.

#### **ONE-WAY SOLUTION**

When you design a device for sales in the consumer electronics market, there are three reasons to do anything—cost, cost, and cost. The choice between a receive-only device and a device that can transmit and receive goes directly to the BOM.

A device that can also transmit requires more code and more electronics. You need the code to implement

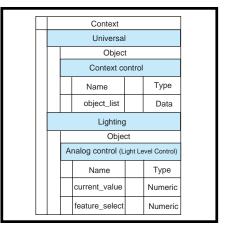

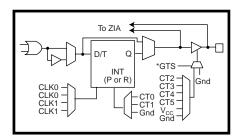

Figure 1—Here's the CEBus context specification for the receive-only relay. Most of a normal context specification is not necessary.

the device transmission and the added electronics to drive the communication signal on the power line. The transmit amplifier and coupling drive the cost up.

To a transmitter, a power line looks like an impedance between 10 and 40  $\Omega$  in a 100–400-kHz transmit band. The complexity surfaces when you look at the power-line environment.

Because this device will occasionally be plugged in next to a computer with a switching power supply, your output amplifier must be able to drive a short circuit without failure. These switchers have a filter on the input to prevent noise from the switcher from getting coupled to the power line. The filter has a capacitor directly across the power line, making for a low-impedance load.

If that isn't bad enough, a simple linear power supply has diodes that turn on and off 120 times per second. And, when they turn on, they connect another capacitor to the power line. Your amplifier has to drive this wildly changing impedance with very little distortion or your signal won't get through.

Did I mention the power supply for the amplifier? It has to provide current for an amplifier trying to drive a low impedance load with a signal of -5 V. How much current does it take to drive a 1- $\Omega$  load with a 5-Vp-p signal?

Fortunately, the device rarely has to transmit. So, you can use an energystorage device like a capacitor to store current for transmit requirements.

But, adding transmit circuitry and beefing up the power supply costs about \$3 on the BOM, or an additional \$12 to the end user. These costs are on top of a BOM that's in the \$5–7 range. By removing the transmit portion, you can sell the device for under \$20.

Keep in mind that there are two ways this relay module will be used—control by a computer and control by a person. So, there are subtle implications regarding the message received and how the device handles certain message situations.

Also, a two-way device needs additional firmware to hail for and track address resources and context instance resources (I'll explain these later). This requirement complicates the user interface and requires a more detailed explanation than I can provide here.

#### **DEMONSTRATION PLATFORM**

I based this project on the EKP300 evaluation kit from Intellon. Intellon uses this kit to provide customer evaluation of the P300 or P200 series of CEBus interface ICs (see Photo 1).

The eval board connects to the power line using a special wall wart providing 10 VAC and signal coupling for the spread-spectrum signal. The board has two switches, two LEDs, a socket for a 68HC05C9A microcontroller, a P300 or P200 CEBus communication IC, a P111 power amplifier/line drive IC, and the necessary power-supply circuitry.

The output of my device is a single LED. Because I did this project for a customer demo, I didn't connect it to a relay.

#### **USER INTERFACE**

Because you save money on the transmit circuitry, you can splurge on the user interface and have a single-character keyboard (one button) and a one-pixel video display (LED).

The HomePnP specification suggests some general functionality for this interface. The button has three actions defined as press, hold, and long hold.

Press is any key press released within 0.75 s. Hold is any key press released after 0.75 s but before 3 s, and long hold is any key press lasting longer than 3 s. The long hold is ignored after 8 s in the case of a stuck switch.

A long hold places the device in setup mode. In setup mode, the device does not respond to control messages but does receive binding messages. The

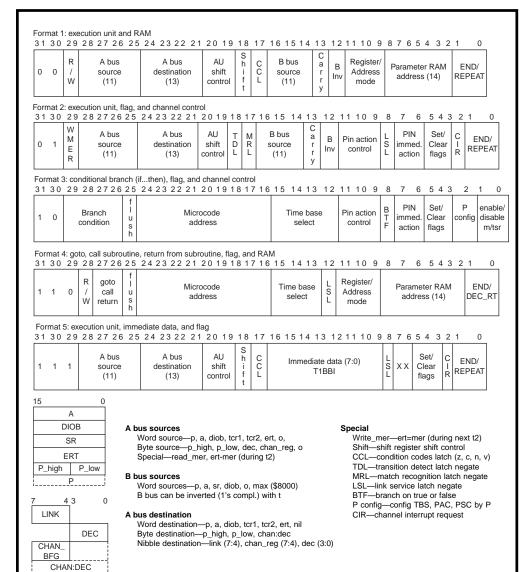

#### Packet type (bits 0, 1, 2) IACK 000 ACK\_DATA 001 UNACK\_DATA 010 011 **FAILURE** 100 101 ADDR\_ACK\_DATA 110 ADDR\_IACK ADDR UNACK DATA 111 Packet priority (bits 3, 4) 00 High 01 Standard 10 Deferred Reserved (bit 5) Service class (bit 6) Basic Extended (undefined at this time) Sequence number (bit 7) Alternates each time a new packet is sent to a destination address

**Table 1—**This data link layer control field shows the bit values used to control how the packet is sent and what happens at the receiver.

user interface LED also blinks while in setup mode. As soon as a binding message is received, the device exits setup mode and the LED stops blinking.

If another long hold is detected during setup mode, the device clears all binding memories, exits setup mode, and stops the LED from blinking. When the device isn't in setup mode, pressing the button toggles the state of the load, which gives the user local control over the controlled output.

#### ADDRESSING REFRESH

A CEBus device has 32 bits of address that's divided into two parts—system address and the MAC address. I'll refer to these two parts by more common names that may be familiar if you have X-10 experience—house code (system address) and unit code (MAC address).

However, unlike with X-10, these are 16-bit values and are stored in EE-PROM. Rotary or DIP switches would be unwieldy and costly.

#### **MESSAGE BASICS**

There are four CEBus data link layer (DLL) services—ACK\_DATA, UNACK\_DATA, ADR\_ACK and ADR\_UNACK. I wrote this code to work with either a P300 or P200 CEBus interface IC.

The P200 only supports the UNACK\_DATA service, but the P300 supports all DLL types. Even though the device cannot acknowledge the acknowledged

service types without transmit circuitry, I couldn't think of a good reason to ignore these messages simply because they used the wrong DLL service.

So, if the sender of the message sent everything else correctly, the code accepts the message and controls the device. Remember this.

The CEBus protocol includes a network layer that's used for segmentation, routing, and brouting control. Segmentation breaks up long messages into many packets, with each packet being a maximum of 32 bytes long.

Routing control enables each packet to control how it is routed (i.e., moved from one network segment to another) around the network. Brouting is like routing except that it takes into account unwired media such as IR.

Because IR is line-of-sight, you'd need an IR router in each room of your house. The problem occurs if you stand in a doorway and press a key on your remote. Two routers receive the IR command and pass it on to the power line. This process causes redundant and potentially harmful results.

Brouters prevent such problems, but my device doesn't accept brouted packets. If you want to control the device using an IR remote, use an intermediary device (gateway) to translate IR commands into appropriate PL commands. The device does not permit the use of extended network services and only responds to devices on PL.

The application layer in the CEBus protocol includes facilities for rejecting duplicate messages and specifying responses from the receiving device. Because they cause no harm in my application, duplicate messages aren't rejected. If my device receives two On messages, it turns on twice. The only command where this is a problem is the toggle command.

But the primary use of the toggle command is for personal control, so I left duplicate rejection to the user. Because this is the receiving device and there are no transmit facilities, you can ignore this part of the application layer.

#### **CAL METHODS**

CAL is object oriented (with certain exceptions) and has methods that operate on objects and pass parameters

(called instance variables [IVs]) based on the method and the object. My device only responds to a subset of CAL methods: SETON (0x42), SETOFF (0x41), and SETVALUE.

SETON and SETOFF turn the device on or off, and SETVALUE sets the relay to something between on and off. If the relay were a light dimmer, being set between on and off would work fine. Instead, SETVALUE sets the value of the relay between 0 and 100 where any nonzero value is On.

A CAL IV is a single variable that models the value of a particular behavior in a CEBus device. I only used the current-value and feature-select IVs. CAL methods are usually directed to an IV. For example, the SETON method, when directed to the current-value IV, sets it to a value of 100s.

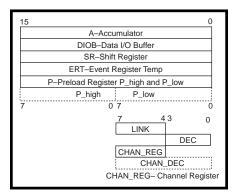

My device has two objects to receive CAL messages. The context-control object handles the address assignment, and the light-control object controls the relay. There are three IVs associated with the light-control object (see Figure 1).

Each CAL object is a list of CAL IVs and represents a functional group of IVs in the CEBus device. As you'll see, you can have objects without associated IVs in a receive-only device.

A CAL context is a group of CAL objects that represents an externally identifiable group of control objects in a CEBus device. Almost every CEBus device has a universal context defining its presence on the network.

The definition takes the form of house and unit codes, group IDs, and other network management information regarding operation on the CEBus network. My device is CEBus compatible but not CEBus compliant, so it doesn't have a universal context or a real address on the CEBus network.

#### **CONTROL FIELD**

Also known as the LPDU header, the control byte instructs the DLL how to handle the packet. The control-byte bit definitions are listed in Table 1.

Because the device is limited to the UNACK\_DATA DLL service, only the sequence-number bit isn't used. The service class is basic, and the reserved bit is 0.

The packet priority can be any of three two-bit combinations, and the packet type should be UNACK\_DATA. If the type is ACK\_DATA, ADR\_ACK, or ADR\_UNACK, the packet is accepted even though the P200 doesn't support these services. If the packet type is an ADR service, the sequence number is examined to reject duplicate packets.

The code doesn't compare sequence numbers. The design decisions I covered are based on the fact that duplicate messages cause no harm to the application and are indistinguishable to the user.

#### ADDRESS FIELDS

The destination address is the current house code of the sending device, and the unit code is the HomePnP broadcast address (0xFFFF). Any Home-PnP device can receive the message, but because you can't send a response, the source address is ignored.

The network-layer header specifies unprivileged, flood or directory route, only packet (for single nonsegmented messages), no extended services, this media only, and no brouter address.

Bit 5 is not affected, so the network header byte must equal 0x70 or 0x50.

The application-layer header specifies basic one byte fixed, explicit or implicit invoke, and a don't-care invoke ID. This means bits 0-3 are don't care and the upper nibble must equal 0xE.

#### RECEIVED MESSAGES

My device can receive messages that fall into either setup or operation messages. The setup message takes the form of a macro sent to the contextcontrol object of the universal context and includes the message DE 21 01 93 31 F5 EC 08.

Here's how to interpret the message: all instances (0xDE) of the lightingcontrol context (0x21) the contextcontrol object (0x01) macro 20 (0x93), with parameters instance 1 (0x31) and  $(0xF5\ 0xEC)$  type 8 (0x08). The 0xDEbyte is a CAL token and uses all instances of the following object.

Macros are defined using the value of 0x80 to mean macro 1. Incrementing to 20 leaves 0x93 as macro 20. The macro system is documented by the

CEBus specification and the meaning of macro 20 is specified by HomePnP.

The instance is any instantiation of the lighting-control object that is controlled and represented by the ASCII value of the desired instance. The 0xF5 is a delimiter, and the EC is a CAL token indicating that a literal expression will follow. Because my device is receive only, the message type 8 is defined in the HomePnP specification and is not used.

When the relay control is in the setup mode and this message is received, the relay control stores the destination house code and the lighting-context instance in a look-up table.

When future control messages are received, their destination house code and instance value are compared to the stored value. If the new message matches the stored value, the control message is accepted. So, it takes three bytes to make a control association.

#### CONTROL MESSAGES

A control message can control the relay using either the current value or

Issue 104 March 1999

feature select. The current value can be set to any value between 0 and 100, where 0 represents off and any other value is on. This range is necessary for the current value to be compatible with a dimmable load control.

A1 21 02 45 43 F5 30 turns off the relay using the current-value IV. This message is read: instance 1 (0xA1) of the lighting-control context (0x21) light level control object (0x02) SET-VALUE (0x45) current value (C or 0x43) to (0xF5) 0 (0x30).

The instance value is added to 0xA0 to create the instance specifier for the context object to follow. SETVALUE sets the value of a CAL IV. C or 0x43 represents the current-value IV, and 0xF5 is a delimiter character followed by the new value for the IV specified by the ASCII character for 0.

To toggle the relay using the feature-select IV, use A1 21 02 45 66 F5 31 30 30. It reads: instance 1 (0xA1) of the lighting-control context (0x21) light level control object (0x02) SETVALUE (0x45) feature select (f or 0x66) to (0xF5) 0 (0x30).

The feature-select IV is represented by f or 0x66. 0xF5 is a delimiter character followed by the new value for the IV specified by the ASCII characters for 100. The feature-select command changes the state of the relay and is the only command I know of (for my device) that is affected by duplicate messages.

A1 21 02 42 43 also turns on the relay using the current-value IV. It reads: instance 1 (0xA1) of the lighting-control context (0x21) light level control object (0x02) SETON (0x42) current value (C or 0x43). SETON sets a CAL IV to an implicit value deter-

mined by the application. For the lighting context, the current value is set to 100.

Note that in the macro 20 message, the instance is specified as an ASCII value, and in the control message, it is added to 0xA0. The instance is specified that way (although it doesn't seem to make sense) because the specifications had many contributors and evolved over more than 10 years.

Thanks to all those contributors, the standard covers almost everything, but not without minor inconsistencies in the implementation.

#### **FEATURE SELECT**

Feature-select messages are sent to the feature-select IV of the light level control object of the lighting-control context. These messages are like macros because they have defined functionality and affect the current value. Table 2 lists feature-select values.

A1 21 02 45 66 F5 31 30 30 changes the state of the relay using the feature-select IV and is read: instance 1 (0xA1) of the lighting-control context (0x21) light level control object (0x02) SET-VALUE (0x45) feature select (f or 0x66). SETVALUE sets the value of a CAL IV. A value of 100 for feature select should toggle the state of the relay.

#### THE SOFTWARE

The software is written in 6805 assembler and the complete code is 1454 bytes long, plus interrupt vectors. The evaluation board is designed around a 68HC05C9A, so the code takes  $\sim 10\%$  of the possible program memory.

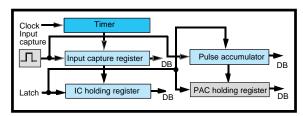

I made one modification to the board for this project. I originally intended to control a triac and made a circuit to get the zero crossings from the power line. I used a simple RC network to connect the 60-Hz signal to the inputcapture input.

Timing in the module is based on the 120 interrupts/s from that source. In retrospect, I should have used the timer to generate 100-ms interrupts. After all, this project is a demo and the triac might have been a distraction.

Seven source-code files make up the project: main.asm, light.asm,

**Photo 1**—The Intellon P300 evaluation board shows the proper implementation of the power-line communication ICs in an easy-to-probe package.

timers.asm, CENode.asm, subs.asm, e2subs.asm, and GLEquates.asm. main.asm is the main program loop including RAM definitions, general initialization, and interrupt vectors.

light.asm contains the message parser and the code to control the relay. timers.asm contains the code for the '05 onboard timers which also includes the input-capture code. CENode.asm is the initialization, messaging, and interrupt routines for communicating with the CEBus Node or Px00 IC.

subs.asm has a couple of routines that didn't fit anywhere else—a timer delay loop (used during power-on) and an ASCII numeric number parser for getting the ASCII numbers out of the HomePnP messages. e2subs.asm has all of the interface code for the EEPROM memory used to store the house codes and lighting context instance numbers. GLEquates.asm contains all of the bit, byte, and register definitions.

Because of the project size and the compiler's speed, I used the assembler to do the linking and bypassed a separate link step. The source files are included in the main.asm file so no linking takes place outside of the assembler program. Unfortunately, this untested (but documented) mode of the assembler led to the following.

#### ASSEMBLER ERRORS

Every now and then, I made a simple change to the code and nothing would work. The change could have been as simple as adding a NOP!

I isolated the problem to an assembler bug that caused the first byte in a subroutine to be swapped with the last byte in the code immediately prior to

the subroutine. I finally identified this bug by tediously comparing the listing and . s19 files.

Fortunately, only the object file was incorrect. Placing NOPs in strategic places was a good workaround.

Unfortunately, Motorola no longer supports this assembler, which is only two years old. Motorola tech support said they'd never heard of this bug when using the separate linker program after assembling to object code.

| Feature-<br>select ID | Description                                                                                                                                      | Action for relay module |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 0                     | No feature selected/stop feature                                                                                                                 | None                    |

| 1                     | Ramp brightness to maximum                                                                                                                       | Set C to 100            |

| 2                     | Ramp brightness to minimum                                                                                                                       | Set C to 0              |

| 3                     | current_value->saved_and turn off                                                                                                                | Set C to 0              |

| 4                     | current_value->saved_value and ramp off                                                                                                          | Set C to 0              |

| 5                     | Turn on to saved_value                                                                                                                           | Set C to 100            |

| 6                     | Ramp on to saved_value                                                                                                                           | Set C to 100            |

| 7                     | Turn on to local brightness level                                                                                                                | Set C to 100            |

| 8                     | Ramp on to local brightness level                                                                                                                | Set C to 100            |

| 9                     | Set current brightness to minimum                                                                                                                | Set C to 0              |

| 10                    | current_value->saved_value and flash                                                                                                             | Flash at 1 Hz           |

| 11–99                 | Reserved for future use. Values >99 are available for manufacturer use.                                                                          |                         |

| 100                   | Toggle—if 0, then set to 100. If nonzero, then Toggle set to 0. Note: De facto standard; used by some manufacturers and not defined in standard. |                         |

Table 2—The feature-select instance variable represents built-in functionality for this lighting-related device.

#### THE PX00 INTERFACE

The interfaces for the P300 and P200 ICs are identical so I'll refer to them as the Px00. The hardware interface to the microprocessor uses six lines—reset, chip select, serial clock, serial data in, serial data out, and interrupt.

The host controls all transactions and each byte transferred generates an interrupt by the Px00. The serial lines and the chip select make up an SPI-like interface that can be clocked up to 2 MHz. The maximum rate that this '05 can run is 500 kHz, and a byte takes only  $16~\mu s$  to transfer.

It may seem like 2 MHz would be four times faster, but because there's an interrupt for every byte transferred, the interface can't run much faster. When the code initiates an SPI read, the read is finished in a couple of spins around a spin loop while waiting for the transfer complete flag to be set. This can be done with a couple NOPs because the transfer is completed in hardware and always finishes in the same amount of time.

Each message is made up of a command byte, length byte, and one or more data bytes. I use these messages to communicate with the Px00: layer management write (LW), interface read (IR), read receive header (RRH), control write (CW), and packet receive (PR).

LW initializes the Px00. Because this application uses the simplest mode of operation for the Px00, it has one parameter to set the mode. Other parameters are passed as nulls. IR interrogates the Px00 to determine its status.

RRH reads the message header so the microprocessor can determine if the destination is correct. CW follows RRH to let the Px00 know what to do after the complete message is received. And, PR retrieves the complete message from the Px00 after it's received.

The Px00 is always host driven so you don't have to poll it, which would waste valuable communications bandwidth over the serial data link. When you have the chip-select line active, each interrupt is part of the current communication session in progress.

If the chip-select line isn't active and the microprocessor receives an interrupt, it's treated as a request for service and the microprocessor responds with an IR to find out what's going on. This is called an attention sequence. Because there's no need for polling with the Px00 parts, polling should be avoided.

#### 20 MS IN THE LIFE...

When the device is powered on, the host sends an LW to initialize the Px00. The next step is to wait for an incoming message or user action. For now, let's focus on an incoming message.

A typical CEBus message of the proper length to control this relay module is  $\sim\!20$  ms long. The preamble and header last for  $\sim\!10$  ms, and the data makes up the rest. When the Px00 receives the last data in the header, it generates an interrupt to let the host know something is going on.

The host responds with an IR and determines if a header is available for transfer. It uses RRH to get the header

and checks the header contents for the correct destination address.

If the destination address House Code was previously stored by receipt of a 20-ms message and the Unit Code is the HomePnP broadcast address, the host sends  $\mathbb{C}\mathbb{W}$  to tell the Px00 to interrupt again when the rest of the message is complete. If the address doesn't match, nothing is done and the Px00 does nothing when this message is completely received.

When the message is complete and if the Px00 was instructed by CW, an attention sequence is generated and the host responds with an IR. The result of the IR indicates a received packet, and the host uses PR to get its contents. The incoming message is then parsed and the relay controlled.

#### **DEVELOPMENT TOOLS**

Development was accomplished using Premia's Codewright editor, a Motorola EVS development system and assembler, and an HP 54645D scope.

I connected the six lines to the logic analyzer inputs and triggered on the chip select. With one of the analog inputs on the power line, I could see the incoming packet and all of the communications between the microprocessor and Px00 in one screen capture, which simplified debugging and made quick work of interface timing issues. I could also zoom in and see bytes transferred serially over the SPI-like interface, which was clocked at 500 kHz.

So, as you can see, designing the hardware and firmware is easier than ever for a high-performance appliance control using the power line for communications.

Peter House spent four years at Intellon as an applications engineer working with power-line communications. He is now a contract engineer and consultant specializing in applications where firmware meets hardware. You may reach him at peter.house@iname.com.

#### **SOURCE**

#### **EKP300**

Intellon (352) 237-7416 Fax: (352) 237-7616 www.intellon.com

## FEATURE ARTICLE

**Craig Pataky**

## In Black and White

#### A Barcode Decoder

Decoders are plentiful and you can certainly buy one, but sometimes you need to build your own for a custom application. That's what happened to Craig. Listen up as he explains how to make sense of the world in black and white.

rom the production line to the checkout line, the barcode reigns supreme.

Look around. There's one on every container, wrapper, and can. Open your computer and you see barcodes on every PCB, disk drive, and power supply. You probably even have one on your driver's license.

A barcode is present on any item that must be read quickly, accurately, and economically. Other technologies exist, but nothing is more cost effective than applying a barcode sticker. And the proliferation of inexpensive scanning equipment practically guarantees the barcode a long and glorious future.

Although there's no shortage of offthe-shelf scanners, I sometimes need to integrate a decoder into a custom application. For example, one client was using a PC-Lite in the field to log rainwater samples. He would go to the site, find the vials, type in the serial numbers, and enter the results of various quality tests. Naturally, typing in all the data was slow and prone to error.

You may encounter such problems, too, so enough with the introduction. Let's get to work and create a decoder of our own.

#### **LINGO**

Every industry has its own jargon, and barcode is no different. So, before I begin, a few general definitions are in order.

First, each different type of barcode is called a symbology, and there are numerous symbologies out there (e.g., Code 39, Code 128, Codabar, UPC, and I2of5). Each symbology has its own niche in one industry or another.

The black bars and white spaces that make up every barcode are called elements. It takes a certain number of elements (the exact number depends on the symbology type) to represent a single character.

A complete barcode of any symbology type is called a symbol. On the cover of this issue, you'll see a UPC symbol in the lower left corner. At the bottom of Figure 1 is a Code 39 symbol.

Every symbol has a leading white space area called a quiet zone. Like a pause between sentences, the quiet zone helps a decoder pick out the symbol from its surroundings.

An input device converts the black bars and white spaces into discrete logic levels called video and feeds it into a decoder. The decoder interprets the video and generates characters that you and I can understand. A decoder is always based around a microprocessor, be it a simple PIC or a Pentium.

#### **CODE 39**

Here, I'd like to focus on Code 39, which is the de facto standard for most industries around the world and is required in many government barcode specifications. Unless your business is strictly retail, I'm certain you'll run across Code 39.

Code 39 is popular because it represents both text and numbers (i.e., A–Z, 0–9, +, –, ., and <space>). Figure 1 shows all the encodation patterns for the Code 39 symbology.

Each Code 39 character is made up of five bars and four spaces, making a total of nine discrete elements. Of these nine elements, three are always about twice as wide as the others. The placement of the wide elements determines which character is represented.

Because Code 39 has only two element widths—wide and narrow—a

binary translation comes naturally. Simply think of every narrow element as a 0 and every wide as a 1.

Using Figure 1, you can easily determine that an encoded letter A is represented by the pattern 100001001b or 109h. Similarly, the pattern for B is 001001001b or 49h.

A Code 39 symbol always begins and ends with an encoded asterisk. Referred to as the start/stop code, this character frames the encoded data. You can think of the asterisk as a preamble and closing it on that lets the decoder know where a Code 39 symbol begins and

#### **MAGIC WAND**

ends.

Now that you can decode a symbol with your own eyes, it's time to give some specialized sight to a decoding platform. There are different types of input devices, but for this project, I used a simple wand. Most wands look like a thick pen and have three signals—+5-V power, ground, and video out.

The internal operation of a wand is rather straightforward. Light from the tip illuminates the symbol, and an internal sensor converts the black bars and white spaces into logic levels.

You can probably build your own wand with an LED, Schmitt trigger, and phototransistor, but I recommend buying one. Hewlett Packard's HBCS-A500 operates at 5 V and draws a mere 5 mA. I bought mine direct for \$110, which I consider to be a small price for a solid product.

| Α | Α | L | L | W         | W | 8           | 8    |

|---|---|---|---|-----------|---|-------------|------|

| В | В | М | М | Х         | Χ | 9           | 9    |

| С | С | N | Ν | Υ         | Υ | 0           | 0    |

| D | D | 0 | 0 | Z         | Z | \$          | \$ < |

| Е | Е | Р | Р | 1         | 1 | /           | / >  |

| F | F | Q | Q | 2         | 2 | +           | +    |

| G | G | R | R | 3         | 3 | -           | -    |

| Н | Н | S | S | 4         | 4 |             |      |

| ı | 1 | Т | Τ | 5         | 5 | <spc></spc> | >    |

| J | J | U | U | 6         | 6 | %           | %    |

| K | K | V | V | 7         | 7 | *           | *    |

|   |   |   |   |           |   |             |      |

|   |   |   |   | * C C I * |   |             |      |

|   |   |   |   | *CCI*     |   |             |      |

Figure 1—Here's the complete Code 39 character set. You may want to enlarge it on a copier so you can better see the ratio of wide to narrow elements.

#### INTO THE PC

The decoding platform I chose to develop for is a '486 running DOS V.6.2. It seemed to be the best middle ground between the embedded world and Windows NT.

My hope is that anyone can quickly adapt a DOS example to suit their needs. Besides, it's a safe bet that you have a PC at your disposal, so here we go.

Wands don't come ready to connect to a PC, so I constructed an interface. I first created an adapter for the parallel port by connecting the wand's ground to parallel port pin 25, video, to pin 15.

For power, I used a 5-V regulator connected to a 9-V power lump on the wall. However, an AC power converter eliminates any possibility for portable applications, and I wouldn't inflict a battery pack on anyone.

A while back, I read some documentation about the comm port and noticed that each pin can source 10 mA—more than enough to drive my 5-mA HP

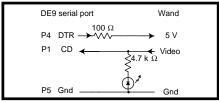

wand. Eureka! I cast aside my AC converter and made the interface depicted in Figure 2.

To apply power to the wand, I set DTR high (+12 V). The  $100-\Omega$  resistor, in series with DTR, works in conjunction with the wand's internal resistance to yield the required 5 V.

Here's something to keep in mind: When you're constructing your own interface, don't overlook the protection diode or you may damage the wand.

#### SOFTWARE SIDE

With the hardware complete, it's time to dig into software.

For this application, I used Borland C V.3.1. You can use another compiler, but my examples and source code may not compile without modification.

Whatever compiler or language you choose, the source code is still your best resource for understanding the decoding process. Nevertheless, I want to cover some important areas that will make the source code more readable.

Any given comm port is controlled by 10 programmable one-byte registers, all of which are accessed through port addresses 3F8h–3FEh for COM1, or 2F8–2FE for COM2. Of these registers, the decoder is only interested in two.

Apply power to the wand by writing a 1 to 3FCh (COM1) or 2FCh (COM2). If you're probing DTR, you should see it jump to +12 V. Turn off the wand by writing a 0, and DTR drops to -12 V. With DTR set to +12 V, you can get the status of the video line by reading bit 7 of port address 3FEh (COM1) or 2FEh (COM2) (see Listing 1).

Do this several times in a loop as you move the wand over a printed page. A little experimentation shows that bit 7 is set when the wand is on a black region and clear when it's on white. Note that lifting the wand away from the white paper produces the same effect as scanning a black region.

When scanning barcodes, most users place the tip of the wand on the quiet zone to the left or right side of the code and then move it across the symbol. When the scan is complete, the user lifts the wand and gets ready for the next scan. The initial placement of

```

Listing 1—Sampling the video couldn't get any easier. Embedding the code to set RTS is a convenient way of ensuring that the wand is always enabled.

```

```

#define COM1

0x3F8

// base address of COM1

#define WHITE

\cap

// bit 7 is low on white

// bit 7 is high on black

#define BLACK

0x80

BOOL SampleWandVideo(void)

BOOL Data;

outp(0x3FC,3);

// be sure to raise RTS!

Data=inp(0x3FE);

// sample the data

if ((Data&BLACK)==BLACK) // if we're on black, return false

Return (FALSE);

else return(TRUE);

// otherwise on white, return true

```

Figure 2—Because the PC serial port is rated to source 10 mA per pin, I can tap more than enough power off DTR. As a bonus, this unorthodox interface leaves the Rx/Tx lines free for other applications.

the wand on the quiet zone provides the decoder with an easily recognizable moment to begin digitizing input.

As the wand moves across the symbol, the decoder records the time spent on each black or white element. The timer that tracks the element widths is usually nothing more than a loop counter. As the decoder hits a black-to-white or white-to-black edge, it saves the count value, resets the counter, and waits to hit another edge.

The wider the element, the more counts it takes to cross it. If the counter overflows or exceeds a processor-dependent value, the wand has probably been lifted from the paper and you can begin decoding the buffer.

#### PATTERN MATCHING

Next, you convert the buffer of counts into discrete element widths. As I mentioned, all Code 39 characters are made up of nine elements—six narrow and three wide. To determine if an element is wide or narrow, compare its width (in counts) against the average of its eight closest neighbors.

If an element is greater than  $1.4\times$  the average, it is definitely wide. By substituting 1s and 0s for wide and narrow, you can build the pattern for a look-up table.

You may wonder, "Why compare against the average of the eight closest neighbors? Why not take the average of all sampled elements and compare against that?" I fell into this trap at first, and wound up with a decoder that didn't work at all.

Fact is, you tend to accelerate as you move the wand across the symbol. So, a narrow element at the start of the symbol may be 10,000 counts, but one at the end will be a miniscule 1000 or even 100 counts. By averaging the element widths on an as-you-go basis, you can factor out most of the error.

When the counts are decomposed into wide and narrow elements, you chunk through the buffer, comparing the binary patterns against a look-up table and appending the decoded characters to a string. That's it!

In the past, you might have resorted to clever look-up methods like hash tables. But, even the slowest processors today provide more than enough horse-power to justify a brute-force sequential-search approach.

#### **CHECK-OUT TIME**

For clarity, I focused on Code 39, but the same principles apply to any symbology type: collect buffer, convert to a binary pattern, and perform a brute-force match. The only thing that varies is the patterns to look for.

I built this decoder on a PC, but you can just as easily apply it to an embedded platform. In fact, an embedded implementation is easier because you have more direct control of pin I/O and timers. Good luck!

Craig Pataky is a systems engineer with over nine years of experience ranging from simple embedded programming to OS design. You may reach him at craig@logical-co.com or visit his website at www.logicfire.com.

#### **SOFTWARE**

Source code for the barcode decoder is available via the Circuit Cellar web site.

#### REFERENCE

R. Palmer, *The Bar Code Book*, Helmers Publishing, Peterborough, NH, 1995.

#### **SOURCES**

#### HBCS-A500

Hewlett-Packard (800) 235-0312 (408) 654-8675 Fax: (408) 654-8575 www.hp.com

#### Borland C V.3.1

Inprise Corp. (800) 457-9527 (831) 431-1000 Fax: (831) 431-9527 www.inprise.com

## Driving in New Directions

## **FEATURE ARTICLE**

**Ross Bannatyne**

### A Chipset for Vehicle Control Systems

Chipsets cut down on development time because there's less of a need to evaluate interacting components. They're even more valuable if they can be applied to a number of related products (ABS, TCS, and ESP come to mind...).

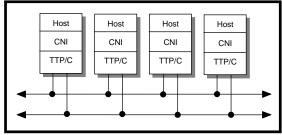

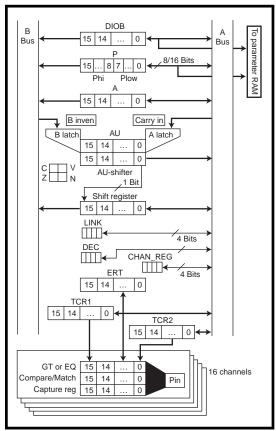

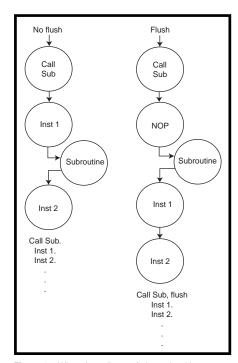

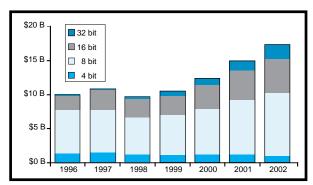

ntilock braking systems, traction-control systems, and electronic-stability programs are all closely related and can often be standardized on one control platform.

In this article, I explain how a chipset optimizes this solution. I also discuss the electronic implementation and basic control strategy of each system.

A chipset's real value is illustrated when it can be applied across several products that are related, as in the case of ABS and vehicle control systems. Chassis-control systems are often based on a single

are often based on a single platform but vary in features and functionality. Basic system requirements can be met with a chipset, and interchangeability with pin-for-pin-compatible variants permits upgradability to higher performance systems.

#### **BRAKE TIME**

Antilock braking systems (ABS) monitor four wheelspeed sensors to evaluate wheel slippage. Slip is determined by calculating the ratio of individual wheel speed to vehicle speed, which is continuously estimated from the four wheel speeds.

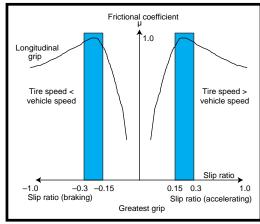

The control system has to maintain maximum possible wheel grip on the road (without the wheel locking) by manipulating the hydraulic fluid via electronically controlled solenoid valves. The relationship between wheel slip and the coefficient of friction on the road surface is shown in Figure 1. By manipulating these solenoid valves to maintain, reduce, or increase pressure at the wheel cylinder, the brake pressure is controlled at each wheel.

The limiting factor on the control cycle time is the actuation time of the hydraulic solenoid valves (~10 ms). Applying Nyquist's theorem determines that the control loop must execute in ~5 ms. In that time, each wheel-speed input must be processed, wheel slip determined, and the appropriate output actuation signals sent to the valves and hydraulic pump motor.

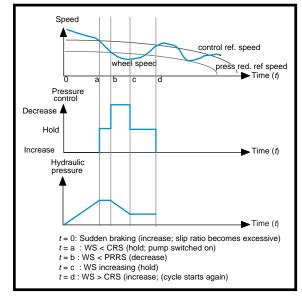

Figure 2 illustrates the relationships between wheel speed, solenoid valve pressure control, and hydraulic pressure at the wheel cylinder. Note that such characteristics exist for each wheel.

At t = 0, the driver applies the brakes. The speed reduces and the hydraulic pressure increases until t = a, at which time the vehicle speed falls below the control-reference speed.

The control-reference speed is determined by the microcontroller executing the control algorithm. When the speed falls below this reference speed, the slip ratio becomes excessive and the solenoid valve is fired into the pressure-hold position by an output of

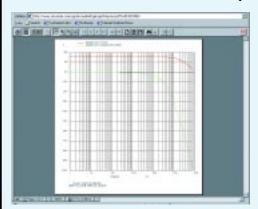

Figure 1—This graph illustrates lateral and longitudinal grip as well as the relationship between slip and the frictional coefficient of the road surface.

the control unit. This position puts a constant high pressure on the wheel so its speed continues to reduce.

At t = b, the wheel speed falls below the pressure-reduction reference speed (also derived by the microcontroller). The solenoid valve is then fired into its pressure-decrease position to reduce the pressure applied to the wheel.

To facilitate the pressure decrease, a hydraulic pump motor switches on to pump the hydraulic fluid from the wheel cylinders back to the master cylinder. This action causes the pulsing feedback on the pedal that the driver feels when ABS is engaged.

When the wheel speed increases again at t = c, pressure hold is reactivated until the wheel speed exceeds the control-reference speed, at which time the cycle starts again.

Incidentally, if the driver relaxes the pressure on the brake pedal, ABS is disengaged. The control system works only when the foot is pressed firmly on the brake pedal.

#### **GET A GRIP**

Traction-control systems (TCS) are like ABS, except that traction control optimizes wheel slippage when the vehicle is accelerating. This principle is illustrated in the right side of Figure 1, where the tire speed is greater than the vehicle speed.

TCS uses almost identical hardware to the ABS system with the addition of minimal hardware (usually two solenoid valves) and some software.

Communication with the powertrain system is required to retard the engine torque while braking. This step is necessary, or the energy from the engine will dissipate in the transmission system.

#### **RIDING STABLE**

ABS improves stability by preventing the wheels from locking. If the front wheels lock, steering control is lost. If the rear wheels lock, the vehicle may yaw longitudinally and spin around. The next generation of ABS may further improve lateral stability using a system known as the electronic stability program (ESP).

ESP requires only slightly more complex hardware and software than a basic ABS. A yaw-rate sensor, lateral low-g accelerometer, and steering-angle sensor are added as inputs. The control algorithm compares the driver's actions (from the steering-angle sensor) with the motion of the vehicle (from the wheelspeed, yaw-rate, and low-g sensors).

If the vehicle becomes unstable, the brakes are automatically applied to

create a yaw movment in opposition to the instability, canceling out the lateral forces that cause the instability.

Taking the concepts of ESP a bit further, a fully integrated chassis-control system would seamlessly handle the suspension, steering, and braking and would require real-time information on all six degrees of freedom of the vehicle as well as information on the status of each systems-control variable and a real-time communication link with relevant systems (e.g., powertrain).

Today, it's normal for the TCS to communicate with the powertrain system to adjust throttle angle while applying braking forces to achieve optimum traction. In the near future,

Figure 2—These graphs demonstrate hydraulic pressure control using solenoid valves.

one system will control the interoperability of these related subsystems.

The only real difference between the basic ABS, TCS, and ESP systems is the relatively small amount of incremental hardware and software, but a chipset approach works well. The software is written in a modular style (i.e., modules for wheel speed, traction control, etc.), and the electronic components' performance is determined with worst-case requirements in mind.

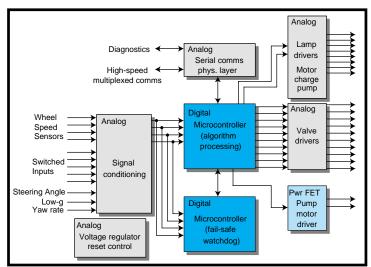

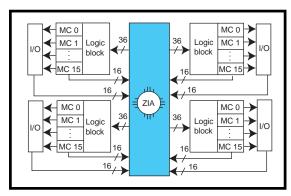

Figure 3 diagrams a chipset solution. There are four basic elements in every automotive electronic control unit—conditioning system inputs, conditioning system outputs, processing, and housekeeping functions (e.g., maintain-

ing a stable power supply).

Three basic semiconductor technologies are applied—HCMOS for the processing portion, analog ASICs for the I/O conditioning and housekeeping, and Power-FETs for driving power stages (in this case, switching the hydraulic pump motor, which can be peak rated at over 100 A). With these basic technologies, infinite partitioning options are possible.

The input portion translates all the analog input signals to clean digital waveforms that can be applied

23

**Figure 3**—This block diagram is generic enough to cover the electronic controls required for two- or four-wheel ABS, ABS with traction control, and electronic stability programs.

Figure 4—In the variable reluctance wheel-speed sensor input circuit, the capacitors protect against electromagnetic interference and electrostatic discharge.

directly to the microcontroller I/O. Figure 3 illustrates all of these sensor inputs grouped together in a single device. Although a single input conditioning device is possible, it is seldom implemented as such.

Because of the interfacing for steering-angle, low-g, and yaw-rate sensors, this device would only be required in the ESP system but would probably not be cost effective in a basic ABS. For this reason, at least two interface devices are usually specified. The second device is added to the basic chipset when the ESP system is developed.

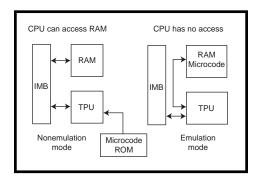

Two processing elements are required in the processing portion of the circuit because a failsafe system is necessary. A failsafe system ensures that any faults in the electrical/electronic system are self-diagnosed and result in the system switching itself off safely, which would leave the conventional hydraulic brakes fully functional (pressure-increase mode) with the absence only of the ABS control.

Theoretically, a single microcontroller can observe and check each part of the system with the exception of itself. So, a second failsafe microcontroller is used to observe the operation of the master micro.

The output-conditioning portion of the electronic control system is, like the input portion, implemented in analog-based technology. SmarTMOS technology permits basic logic to be incorporated onto these devices to enhance performance. This smart functionality is used for diagnostics and to enhance failsafe operation.

For example, if a short or open circuit is detected at an output driver, the SmarTMOS device communicates that status to the microcontroller to ensure that the system remains in a safe operating mode.

#### **FAILSAFE SYSTEM**

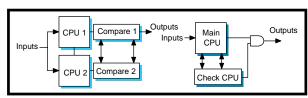

The failsafe configuration is implemented using two microcontrollers (or two CPUs on a

single microcontroller) and can operate in many different ways.

One approach—symmetrical redundancy, shown on the left-hand side of Figure 4—is to run the same software simultaneously on two identical CPUs. Symmetrical redundancy requires only one program to be written, but it's often inefficient in terms of silicon use.

The failsafe function can also be implemented by a less powerful CPU that performs only plausibility checks on key parts of the data. This equally popular approach is known as asymmetrical redundancy.

The chipset approach requires modular software that can be implemented selectively for different related systems such as ABS, TCS, and ESP. So, it's advantageous to use a pin-for-pin-compatible family of microcontrollers that differ only in memory size.

Because the ESP algorithm is more complex than the TCS algorithm, which is in turn more complex than the ABS algorithm, the CPU should be fast enough to execute the most complex algorithm within the minimum loop time of ~5 ms. Conversely, when the chipset is applied to only the basic ABS function, significant

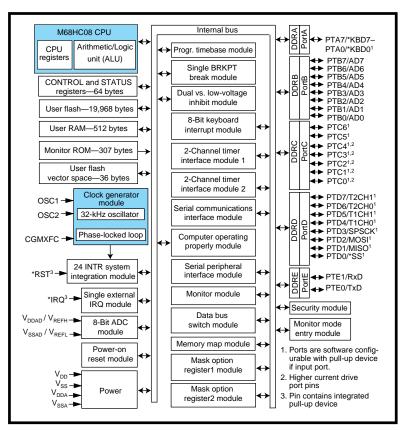

mum loop time of ~5 ms. Conversely, MTB/P3402 MC33389 Dual V<sub>rec</sub> Valve 5/3.3 V Watchdoo CAN 2.0B CAN SPI SPI M68HC12 Signal M•Core Wheel speed Hydraulic

Figure 5—If a master and a slave microcontroller are implemented and the slave only performs plausibility checks, the configuration is asymmetrically redundant.

MC33298

Analog

ASIC

processing headroom is available. The wasted performance is certainly inefficient but is insignificant when microcontroller, hardware development, and software costs are considered.

#### SYSTEM PARTITIONING

The first step in electronic system partitioning is to evaluate system functionality and mapping the functional requirements to the basic technology that can implement these functions. Software must also be considered.

For example, it's possible to implement the wheel-speed timer system as a hardware unit that doesn't interrupt the CPU or as a basic unit that requires significant software control.

For the ABS/TCS/ESP chipset, technology mapping can be summarized as Sensors (wheel speed, steering angle, yaw rate, low-g accelerometer), Analog (signal conditioning, physical layers for mux comms, Vreg, solenoid drivers and charge pumps for high side drivers), Digital (MCU and failsafe), and Power (safety relay driver, pump motor driver).

At least in the near future, it's likely that sensors will continue to be implemented discretely with a conventional twisted-pair coupling directly to the ECU. But before too long, smart sensors that provide onboard diagnostics and communications will be deployed. These sensors will come with signal conditioning and will transmit information digitally on a multiplexed bus.

The high-rated power FET devices requiring current ratings that exceed the capability of a conventional analog

ASIC may be implemented differently as well. One possibility is to remove the pump driver FET from the ECU and mount it mechatronically as part of the hydraulic pump motor assembly.

If the switching transistor and freewheeling diode were mounted inside the motor housing, a Faraday shield would be formed by the motor housing and would reduce radiated emissions. It may then be possible to switch the transistor faster and thus reduce losses as well as device costs.

Figure 6—The M•Core programmer's model is defined separately for two privilege modes—user and supervisor.

The analog ASIC handles output signals and is expected to provide the drive signals for the dashboard lamps indicating ABS, TCS, and brake. In modern vehicles, these lamps are driven directly from an integrated dashboard control unit rather than the ABS unit. The ABS ECU talks directly to the dashboard ECU using the multiplexed serial communications link shown in Figure 3.

Figure 5 shows an implementation of a chipset that gives a tradeoff between standard components and custom devices. In reality, it's impossible to determine an optimal chipset until each of the system specifications for ABS, TCS, and ESP are understood, as well as the production forecasts for each system.

A physical interface for the controller area network (CAN) 2.0B serial communications system is included on the MC33389 device. If the preferred multiplexed communications was SAE J1850, this chip could be replaced by a pin-for-pin-compatible version with a different physical interface. These functions can also be implemented discretely by using stand-alone voltage regulators.

The MC33298 is used as the solenoid valve driver device, which, like the MC33389, includes a serial peripheral interface (SPI). There are eight power switches for the solenoid valves. In a TCS or ESP system, more solenoid valves are likely to be needed, so two MC33298 devices can be used or a custom driver can be implemented.

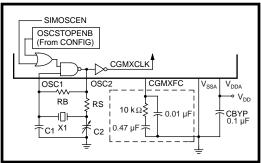

Reducing the chip count can reduce the physical size of the ECU, which lets you mount the control unit directly on the hydraulic valve