# COMPUTER APPLICATIONS JOURNAL

## #105 APRIL 1999 DIGITAL SIGNAL PROCESSING

**PWM Signal Generation and Measurement**

**Interfacing Flash Memory with DSP**

**Build a Video Multiplexer**

Create a Win32

## TASK MANAGER

### School's in Session

hh...the breeze is blowing gently, the air is brisk, the sky is blue—what a refeshing season! It's back-to-school time again!

Well, that's not true for my family here in Connecticut, but some of my friends are already thinking about pencils and notebooks. Did you know that the Japanese start their school year in April?

I remember the first time I heard that, just a few years ago. Seemed odd to me at the time, but maybe I've lived a sheltered life. There's always something new to learn, isn't there?

Truly, we're never so old, so wise, so mature that there isn't something we don't know. Or, what about when it's been so long since you heard about something that it's like learning about it for the first time? Have you ever experienced a familiar excitement when you go back to solving the problems you first tried to tackle years ago? Er...hang on a sec—do you even remember all those formulas and equations?

Perhaps you need to go back to school, too. Here's your chance, and from the comfort of your own chair! Starting this month, the Circuit Cellar academic year begins (and yes, we're in session 12 months a year). Our new quiz—Test Your EQ—lets you test your "engineering quotient."

We begin the monthly quiz in this issue with submissions from Bob Perrin, who I thank for approaching us with the initial concept. These questions are adapted from a much longer test given to all engineering applicants at Z-World. Give these problems the old college try and ask yourself, would you get the job?

As Steve mentioned in Priority Interrupt a couple months ago, our latest survey showed that readers were concerned that EEs don't always know even fundamental electronics. Test Your EQ lets you discover on an ongoing basis whether you make the grade. Maybe you've been involved on the management side of the team for such a long time now, you need a refresher course.

The answers to the problems in Test Your EQ will be posted on our web site (www. circuitcellar.com) each month, so you can check right away how you fared on the problem set. And although we will update the answers each month, past quizzes and their correct answers will be maintained on the site as well.

Of course, we also want you to take a turn on the "teacher side" of the desk. Submit your potential engineering quizzes to me via e-mail, fax, or regular mail, and for each half page of the magazine that we decide to fill with your questions, you will receive \$50.

Wherever you happen to be today, it may look like spring or fall outside, but no matter. It's time to hit the books again. Turn to page 83 to go back to school now!

8 Q.

elizabeth.laurencot@circuitcellar.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella CHIEF FINANCIAL OFFICER

TECHNICAL EDITORS Michael Palumbo Rob Walker

WEST COAST EDITOR Tom Cantrell

**CONTRIBUTING EDITORS** Ingo Cyliax Ken Davidson

Fred Eady **NEW PRODUCTS EDITOR** Harv Weiner

Ingo Cyliax

Jeannette Ciarcia ART DIRECTOR KC Zienka

ENGINEERING STAFF Jeff Bachiochi

PRODUCTION STAFF Phil Champagne John Gorsky James Soussounis

> PROJECT EDITOR Janice Hughes

David Prutchi

EDITORIAL ADVISORY BOARD Norman Jackson

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

ADVERTISING SALES MANAGER Bobbi Yush Fax: (860) 871 (860) 872-3064 E-mail: bobbi.y ADVERTISING COORDINATOR

> Valerie Luster (860) 875-2199

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

Fax: (860) 871-0411 E-mail: val.luster@circuitcellar.com

CONTACTING CIRCUIT CELLAR INK

#### SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor. Circuit Cellar INK, 4 Park St., Vernon, CT 06066

AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR INK®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions,

Direct subscription orders and subscription-related questions to Circuit Cellar INK Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar INK, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613. Circuit Cellar INK<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, Circuit Cellar INK<sup>®</sup> disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in Circuit Cellar INK<sup>®</sup>.

Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

|   | 12 |                                                                                              | <b>grating Flash Memory in an Embedded System</b><br>an Bordeaux and Stefan Hacker        |                                                            |    |  |

|---|----|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------|----|--|

|   | 20 | Embedded PWM Signals<br>Andrew Lillie                                                        |                                                                                           |                                                            |    |  |

|   | 28 | <b>Thermistor-Based Conditional Output Sensor</b><br>R.K. Kamat, G.M. Naik, and G.G. Tengshe |                                                                                           |                                                            |    |  |

|   | 32 |                                                                                              | eo Switch<br>len Jennings                                                                 |                                                            |    |  |

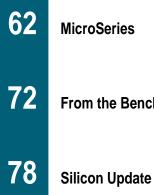

|   | 62 |                                                                                              | <b>MicroSeries</b><br>TPU<br>Part 4: Scheduler and Microcoding<br><i>Joe DiBartolomeo</i> | Task Manager<br>Elizabeth Laurençot<br>School's in Session | 2  |  |

|   | 72 |                                                                                              | From the Bench<br>Dallas 1-Wire Devices<br>Part 1: One on One<br>Jeff Bachiochi           | Reader I/O<br>Circuit Cellar Online                        | 6  |  |

|   | 78 | <b>L</b>                                                                                     | <b>Silicon Update</b><br>Maximicro<br><i>Tom Cantrell</i>                                 | New Product News<br>edited by Harv Weiner                  | 8  |  |

|   |    |                                                                                              |                                                                                           | Test Your EQ                                               | 83 |  |

|   |    |                                                                                              |                                                                                           | Advertiser's Index<br>May Preview                          | 95 |  |

| T |    |                                                                                              | SUH                                                                                       | Priority Interrupt<br>Steve Ciarcia<br>Sitting in the Dark | 96 |  |

|   | 4  |                                                                                              | ouveau PC<br>ited by Harv Weiner                                                          | 175                                                        |    |  |

|   | 4  |                                                                                              | in <b>32 and Real Time</b><br>ter Petersen and Tom Schotland                              |                                                            |    |  |

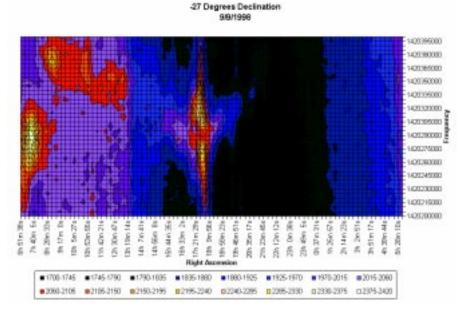

|   |    | 0 RPO                                                                                        | Astronomical Issues<br>Part 1: Introduction to Embedded Astronomy<br>Ingo Cyliax          |                                                            |    |  |

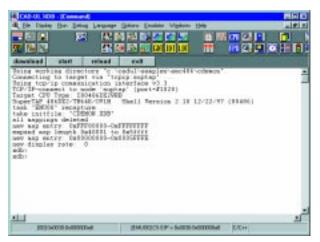

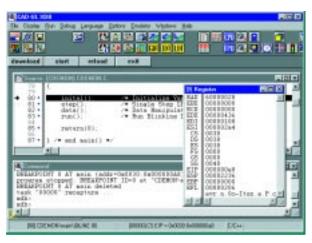

|   |    | <b>6</b> AP0                                                                                 | Applied PCs<br>ICE on Tap<br>Part 2: Emulating over Ethernet<br>Fred Eady                 |                                                            |    |  |

# **READER** I/O

#### **ALTERNATE ROUTE**

In "Digital Frequency Synthesis" (*INK* 99), Tom Napier used a Microchip PIC16C54 microcontroller for signal generation. Scenix Semiconductor makes parts that are improved versions of the PIC for applications such as this.

The SX18AC can replace the PIC and run  $2.5 \times$  faster (50-MHz clock frequency instead of 20 MHz). If the SX is set for turbo mode, the internal divide by four is bypassed and the SX runs at the full 50-MHz clock rate.

Instructions such as GOTO, CALL, and returns take an extra cycle so the final speed is not quite  $10 \times$  as fast. But, with a few changes to the program, there are other features that can make up the difference.

For instance, a fuse bit enables the arithmetic to use the carry flag in multiple precision calculations. This arrangement is faster and saves instructions by reclaiming some of the cycles lost by using turbo mode.

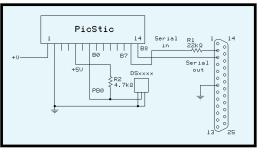

Using an SX series micro with a 24-bit accumulator gives about 1.9 MHz for the update rate, allowing a 600-kHz filtered output signal. A faster DAC and filter amplifier must be used to reproduce the higher frequencies. I used an R-2R DAC made with 120- and 240-W resistors. In case you want to check it out, my Scenix version of the program is available at http://brouhaha.com/ ~eric/scenix/ in SXNCOEX.ZIP.

#### **Richard Ottosen**

ottosen@idcomm.com

#### WHICH NUMBERS COUNT

Steve, thanks for your efforts at *Circuit Cellar INK*. Please don't become big-advertiser driven. *INK* is the one magazine in which I look at every advertisement and read at least 90% of them. In my opinion, you have a good feel for what your readers want.

I know you've voiced your frustrations about advertisers wanting to direct the magazine. I think comments like the one from Eric Sells in Reader I/O (*INK* 98) tell the story for advertisers. What better testimonial than a company that's perceived as small and unknown becoming number two behind one of the giants?

Grant Powell gapowell@gte.net

## Circuit Cellar ONLINE

#### Newsgroups

If you miss the Circuit Cellar BBS, then the cci newsserver is the place to go for on-line questions and advice on embedded control, announcements about the magazine, or to let us know your thoughts about Circuit Cellar. Just visit our home page for directions to become part of the newsgroup experience.

> The April Design Forum password is:

# www.circuitcellar.com

- Wouldn't it be great if there was an easier way to search past articles for certain topics (besides flipping through the pages of 105 back issues)? Stop wishing and start clicking! Head over to our homepage to find out how to get your searchable CD-ROM of the *Circuit Cellar* back issues.

- All aboard the **INFO** *Express*! Loaded with the latest news and information about *Circuit Cellar INK* as well as any additions or changes to our web site, INFO *Express* stops right at your e-mail address. Visit our homepage to sign up for this new service from Circuit Cellar.

- While you're working on your entry for Design99, don't forget to check the **Design99 Rules Update** section for the latest updates on contest guidelines.

Be sure to visit the Circuit Cellar Design Forum this month for more great online technical columns and applications. The Design Forum password is your key to great new columns, monthly features, and PIC Abstracts.

Silicon Update Online: HIPe or Hope?—Tom Cantrell Lessons from the Trenches: Hardware Tips—George Martin Enclosure Fabrication: Ed Zanrosso

# NEW PRODUCT NEWS

**Edited by Harv Weiner**

#### **DSP-CONTROLLED SERVO DRIVES**

UltraDrive's **G Series** servo drives use DSPs that are specifically designed for motor control. The drives provide 1/T velocity loop or torque-mode control, true performance matching with motor RMS horsepower modeling, and extremely low torque ripple. The G Series can be used with any servo motors (including linear brushless servomotors) incorporating either Hall-effect sensors (trapezoidal commutation) or Hall-effect sensors plus encoders (sinusoidal commutation).

The G Series offers PWM-switching frequencies from 10 to 20 kHz, and provides current loop bandwidths from 1 to 2 kHz. Four G Series models deliver from 5 to 20 A continuous current output and continuous output power from 1.2 to 4.8 kW. Integral power supplies can use universal AC input voltages from 90 to 265 VAC.

Software in the DSP's flash memory enables the user to define motor- and application-specific parameters. Parameter adjustments can be commanded on-the-fly to increase application-control flexibility. Windows-based software provides setup, tuning, and diagnostic utilities to reduce system setup time and commissioning. The software includes graphical plotting tools that turn a desktop or laptop computer into an advanced digital storage oscilloscope.

Flash memory provides an easy path for system firmware upgrades and eliminates batteries for parameter storage. Windows software and an upgrade disk are all that's required to update drives with firmware enhancements and customer-specific features for applications.

UltraDrive/Westamp (818) 709-5000 Fax: (818) 709-8395 www.ultra-drive.com

#### 8-/16-BIT MICROCONTROLLER

The **TSC80251G1D** enhances the C251 architecture core with serial communication interfaces. Running up to 24 MHz with an active power consumption as low as 24 mW (3-V version), the TSC80251G1D offers an excellent performance/power-consumption ratio. Applications include smart-card readers, cordless phones, ISDN PABx, networking, backplanes, and routers.

The TSC80251G1D features 16 KB of ROM, 1 KB of RAM, and several on-chip serial communication capabilities such as UART, serial peripheral interface, and multimaster I<sup>2</sup>C. The device comes with three 16-bit timers, a keyboard interface, and complete programmable counter array with five modules including PWM, input capture, output compare, and timer/counters. It also includes an enhanced power-management unit with power-on reset, brown-out, and prescaler functions.

Available in commercial and industrial temperature ranges, the product is offered in 44-pin PLCC, 40-pin DIP, and space-saving 44-pin Thin QFP packages. The device operates from 2.7 to 5.5 V.

Pricing for a 44-pin PLCC in commercial temperature range starts at **\$4.40** in quantities of 10,000.

#### Temic Semiconductors www.temic-semi.de/nt/micro

# NEW PRODUCT NEWS

#### PC REMOTE CONTROL

The **KeyRF PC** remote control enables you to receive signals from a keychain remote control transmitter (like a garage door opener) on your PC. It can be used for overhead-projection presentations, to flip channels on your built-in PC TV, or for home automation systems. The RF technology is superior to infrared units, allowing 360° transmissions over longer distances and through walls and objects. The receiver can be programmed to assign custom keyboard keys to all five transmitter-button combinations. The KeyRF plugs between the keyboard and the PC, and it does not require additional software to be installed on the PC.

The KeyRF kit comes with a two-button keychain remote control transmitter, a radio-frequency receiver, a cable to connect to the PC keyboard port, and a user manual.

List price for the KeyRF kit is \$150.

L3 Systems, Inc. (425) 836-5438 Fax: (425) 868-8706 www.L3sys.com

# NEW PRODUCT NEWS

#### SINGLE-BOARD COMPUTER

The **BasicBox** is an SBC system designed for education, experimentation, and embedded applications. The design is adopted from Jan Axelson's *Microcontroller Idea Book*.

The standard board configuration contains an 8052 microprocessor with built-in BASIC-52 interpreter, 8 KB of RAM, 8 KB of EEPROM, a UART for RS-232 serial communications, and 35 lines of parallel I/O. The board is programmable in BASIC-52 or 8051 assembly language with either a PC or a Macintosh via a modular telephone type cable. The BasicBox is capable of expanded I/O via its DIN connector.

The BasicBox (BB-1) is packaged with a copy of Axelson's book, terminal software, power supply, serial cable (PC or Macintosh), demo pro-

grams, documentation, and the "Board of Education" (BB-2)—an experimentation board that gives the user an interactive learning environment.

The BB-2 contains a variety of devices designed to give feedback as the user becomes more familiar with the BasicBox. The devices include a speaker that gives audible tones when exercising the PWM, a seven-segment LED that can be manipulated both bit- and byte-wise, a pushbutton for experimenting with debounce algorithms, a DIP switch for discrete inputs, and an oscillator for measuring frequency and bit times.

The BasicBox is priced at **\$249** plus shipping for single quantities.

Advanced Graphics Systems (530) 887-1619 Fax: (530) 887-0107 www.ags-gv.com

#### **GPS-BASED NETWORK TIME SERVER**

The **NTS-90** network time server from TrueTime distributes time to precisely synchronize client computer clocks over a network. Using the GPS as its primary source, NTS-90 transfers the time over the network to client computers using the well-established network time protocol (NTP). Synchronization accuracy over the network is typically 1–10 ms. With near plug-and-play operation, installation is easy and ongoing maintenance and support costs are very low. Client computers can continually be added to the network and directed to retrieve time from the NTS-90. An RS-232 command set provides versatile control and a single command configures the unit for immediate use. Other commands give status information, precision timing, and total control.

The NTS-90 is also a source for accurate serial time broadcasts and time on demand. A once-per-second time broadcast (accurate to the millisecond) is available via the serial port. The NTS-90 can also timestamp external events with millisecond accuracy.

The NTS-90 comes in a rackmountable configuration. The rear panel supports the synchronization input connector (GPS or ACTS), a 15-pin AUI network connector, and a 9-pin RS-232 communications/initialization connector.

TrueTime, Inc. (707) 528-1230 Fax: (707) 527-6640 www.truetime.com

## FEATURES

12 Integrating Flash Memory in an Embedded System

20 Embedded PWM Signals

28 Thermistor-Based Conditional Output Sensor

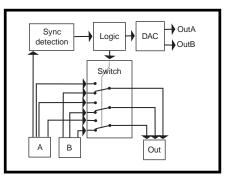

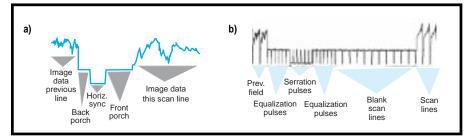

Video Switch

32

Turn on to the power and ease of flash! Ethan and Stefan show us the best uses for flash memory, and create an interface between a DSP and flash. It's easy to tie into your system, and you can't beat having in-system programmability.

## FEATURE ARTICLE

Ethan Bordeaux & Stefan Hacker

## Integrating Flash Memory in an Embedded System

ntil recently, the most flexible external boot memory was an EPROM. But, if you needed to erase or update the data, you had to remove the EPROM from the system, expose it to ultraviolet light, place it in an EPROM burner, and insert it back into the design.

A better solution is to update code and data while the nonvolatile memory is in the system. This is the type of functionality built into flash memory.

We're sure you can imagine lots of applications and system configurations where such functionality is useful.

One application is an embedded speaker-independent voice-recognition unit, as in a hands-free car kit or voiceactivated appliance. The user programs a number of keywords to perform operations like dialing a phone number or turning on and off a device. The processor would need to store these voice patterns in external nonvolatile memory and be able to retrieve them for comparison purposes.

Flash memories are also an asset in systems that need to save data during a power outage or brownout. The processor moves its code and data contents from volatile internal memory to an external nonvolatile memory and, on revival of the system, continues at the last saved state. In this article, we explain some of the benefits and basic functionality of flash memories. We cover an example interface between an ADSP-218*x* DSP and an Am29F040 flash memory as well as hardware and software structure.

#### FLASH VS. EPROM

Even with the in-system programmability (ISP) of flash memory, there are times when a conventional EPROM may be a better choice for your design. Table 1 is a partial list of considerations for choosing a byte memory.

EPROMs cost less than flash memory with similar storage capabilities, but there are many reasons to consider using flash memory. ISP is an obvious advantage. They can potentially offer all of the functionality of an EPROM and an SRAM in a single package.

Because flash memory is such a hot commodity in today's semiconductor market, many manufacturers are focusing research and development, along with their advanced manufacturing processes, on the flash market. This translates into flash memories with low power consumption during operation and powerdown, more aggressive operational voltages, and faster access times (e.g., Intel's Strato flash family).

So, if your design requires the absolute lowest power consumption, a flash memory may be the best nonvolatile solution. And because operational voltages on flashes have now reached 1.8 V, they can gluelessly interface to systems that operate below LVTTL levels.

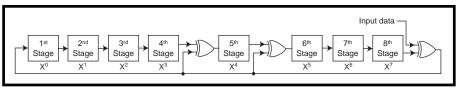

**Figure 1**—A tale of two programming models: the lefthand side (Am29F040B) requires an unlocking sequence after every byte is programmed, and the right-hand side (AT29C040A) requires an entire sector of memory to be programmed each time you write to the flash.

|                                                                                                                   | EPROM | Flash memory                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Price per megabit<br>Typical packages<br>Typical operational voltages<br>Power consumption<br>Typical access time |       | \$2–10, depending on features<br>BGA, PDIP, PLCC, TSOP<br>1.8 V, 2.5 V, 3.3 V, 5 V<br>15–50 mW (read), 45–200 mW (write/erase)<br>18–150 ns |

Table 1—Even though flash memories are typically more expensive than EPROMs, a wide range of voltages, fast access times, low power consumption, and inherent ISP can make them powerful and flexible memory ICs.

#### FLASH ROBUSTNESS

Flash memories are given a rating for the number of write cycles they can sustain before the part is not guaranteed to operate properly. Flash memories from a few years ago sustained ~10,000 write cycles. Assuming your design is supposed to last 10 years, this translates to ~2.7 memory rewrites a day.

Some systems are deterministic enough to guarantee this rate, but often it's unknown exactly how many times the flash memory will be programmed or erased in its lifetime. Some flash memories now guarantee upward of 1,000,000 write cycles (or 270 rewrites a day) before failure. This alleviates some of the flash programming concerns and enables them to fit into a wider variety of designs.

#### INTERNAL VS. EXTERNAL

There's been a lot of talk recently about embedding flash memory on processors, microcontrollers, or DSPs and the increased level of system flexibility that would provide.

The strongest argument for including flash memory on a processor is for prototyping. If a manufacturer provides a processor with both a ROM and flashmemory variant, the user can use the flash device for prototyping and the ROM-coded processor for production.

But, processors with embedded flash memory cost 2–10<sup>-/</sup> more than their flash-less counterparts and are aimed at prototyping environments. And, flash memories frequently can't operate as fast as onboard SRAM or ROM. The entire processor speed can be compromised by including flash memory.

Lastly, the size of a flash memory embedded with a processor is typically 10–30k words. Although this is often adequate for a portion of program or data memory, many times, a design needs access to a much larger memory space, where it can grab many code and data overlays or use a nonvolatile memory source as a virtual hard drive.

Applications like digital cameras require many megabytes of nonvolatile storage for saving each "roll" of digital film. Algorithms such as voice recognition need large external memories for voice look-up tables. To store 30 words for a speaker-independent voicerecognition system, up to 512 KB of external memory is needed.

These applications can't be supported by processors with on-chip flash memory. These systems require a simple and flexible method of gluelessly connecting an external flash for the optimal solution.

#### EMBEDDED ALGORITHMS

The simplest way to understand a flash memory is to think of an SRAM programmed via a finite state machine (FSM). When reading information from the flash memory, you have normal access to all memory locations, much like an SRAM or EPROM.

But, when specific operations need to be performed on the flash, whether it's erasing, writing information, or protecting memory segments from erroneous erasure, the processor must use the flash's embedded programming algorithms (EPAs).

A series of commands are written from the processor to the flash. These commands unlock the flash so it can accept data, erase sectors, or perform other programming tasks. We explain a few of the common functions here.

#### BYTE/SECTOR WRITE

Byte/sector write lets the host processor place data into flash memory. The processor first writes the unlock sequence to the flash and then writes the address and data for the first value to be programmed.

|               |                 |         | 1                 |

|---------------|-----------------|---------|-------------------|

| $\rightarrow$ | A0–A18          | DQ0–DQ7 | $\leftrightarrow$ |

| $\rightarrow$ | *WE             | *CE     | ←                 |

| $\rightarrow$ | V <sub>CC</sub> | *OE     |                   |

| $\rightarrow$ | Gnd             | OL      | -                 |

|               | Am29            | LV040B  |                   |

|               |                 |         | •                 |

Figure 2—The Am29LV040B has memory strobes similar to an EPROM, with the exception of a write pin (WE).

Depending on the programming methodology implemented on the flash, additional unlocking commands need to be written for each word, or a sector (typically between 64 bytes and 64 KB) of memory can be written in a burst fashion, as you see in Figure 1.

In both types of flash memories, the processor writes the unlocking sequences and data to be programmed into the flash and the flash latches the data into memory. This sequence enables the processor to continue executing algorithmic data while the flash memory handles programming itself.

Keep in mind that the contents of the block you want to program must be erased beforehand. A convenient feature of sector-programmed flash memories is that they usually erase the sector before programming it with data.

One methodology is not inherently better than another, but each is better suited for certain systems. Consider these points before choosing a flashwriting architecture.

First, decide what type of data you're writing. Will your data be partitioned as a large chunk of information (e.g., a JPEG file for a digital camera) or will the external memory save single bytes of information?

If you're only making small incremental changes to the flash memory, it might make sense to choose a flash with a byte-programming protocol. But, if you write large pieces of data from the processor, a sector-programmed flash may be more efficient.

Second, what kind of processor is writing to the flash? Low overhead DMA and fast byte-port accesses are available in some embedded processors.

For example, the ADSP-218*x* DSPs integrate a byte-wide DMA port that supports a variety of ICs, including flash memories. Knowing how your processor will interface with a flash and its EPAs is useful.

#### SECTOR/CHIP ERASE

Flash memories are partitioned into a number of sectors, which enables the programmer to erase one sector of the memory at a time.

In general, a series of commands is written out to the flash to start the erasing procedure. Even though the commands are latched into the flash in a few microseconds, actually erasing the flash takes a couple seconds.

Some flash memories don't allow the processor access to the flash during a sector erase. Others, however, have simultaneous read/write architectures that permit memory accesses to one block while the other block is erased.

#### AUTOSELECT/PRODUCT ID

This EPA determines specific information about the flash in your system. The information includes the manufacturer ID (necessary because many companies make pin-for-pin-compatible flash devices), device ID, and sectorprotection feedback. This data is useful for external flash programmers/burners.

#### SECTOR PROTECT

The sector-protect EPA disables both the programming and erasing of a particular memory sector. This feature is useful in systems where you both boot and continually write/erase the flash. You can set the boot sector to be protected and leave other memory segments unprotected for a chip erase.

#### DATA POLLING

The time it takes a specific EPA to finish varies greatly, even on the same device. For example, the Am29F040B flash memory takes from 7 to 300  $\mu$ s to program a byte of data, and sector erase time can vary from 1 to 8 s. There are provisions for the flash memory to signal when an operation completes.

Data polling is a common method for determining when an EPA is finished. Once the processor writes the data into the flash, it is latched inside the part and the processor isn't needed to control the actual writing of data into memory. But, the flash still needs to place the new information into its memory bank and signal when it's ready to handle another EPA.

One method is to poll the status of one of the data bits to see if the EPA has completed. For example, the Am-29F040 provides data-polling capability on data pins DQ7 and DQ6.

By reading back DQ7's value during a byte write, you can determine if the programming is done. If DQ7 has the inverted value of the programmed value (e.g., the byte value programmed into the flash is 0x0F [DQ7 = 0] and DQ7 is read back as a 1), the EPA is not complete. If DQ7 reads back as the value programmed on that bit, the EPA is done and the next byte can be programmed.

DQ6 can be used in a similar way. While the flash is still in a byte-programming EPA, successive reads of

```

Listing 1—This code shows you the function PROG_BYTE.

Flash application server

int error PROG_BYTE(char c_byte, char d_byte, int addr_lo, int

addr_hi);

*

Byte program:

c_byte : 0xA0

// Third input to AMD EPA

*

// holds data to be programmed to flash

d_byte : value to program

addr_lo: low 16bit

// lower part of 22-bit address

*

addr_hi: high 6bit

// higher part of 22-bit address

*

Register usage summary:

*

modify : addr_lt, addr_ht, d_btmp

*

destroy: ar, ax0, ay0, af

*

calls : init_seq, cmd_write, calc_adr, DQ7_poll

prog_byte:

// EPA unlock sequence

call init_seq;

call cmd write;

// EPA command word write

11

fetch byte from input register

ar = dm(d_byte);

// store byte in destination register

dm(d_btmp) = ar;

call calc_adr;

// compute registers from address

call DQ7_poll;

// check for internal completion

rts;

// return from function call

```

DQ6 cause the value to toggle. When the EPA finishes, DQ6's value stops toggling and reads as the same data value. The data-polling scheme you choose depends on your processor and whichever method is easier to implement in software.

#### **READY/\*BUSY PIN**

A lower-overhead method of much determining EPA completion is via a READY/\*BUSY pin. Some newer flash memories include this pin to signal the status of the flash at any moment. Essentially, the pin is at a logic low when the flash is in any EPA and at a logic high when it's ready to read data or in standby.

This method is useful on processors where the status of external flag pins can be easily tested. ADSP-218x DSPs provide a variety of I/O pins and support for externally generated interrupts, which can be connected to test the status of READY/\*BUSY.

The tradeoff is that this method ties up an additional pin and increases the total number of signals in your design.

#### FLASH TO DSP

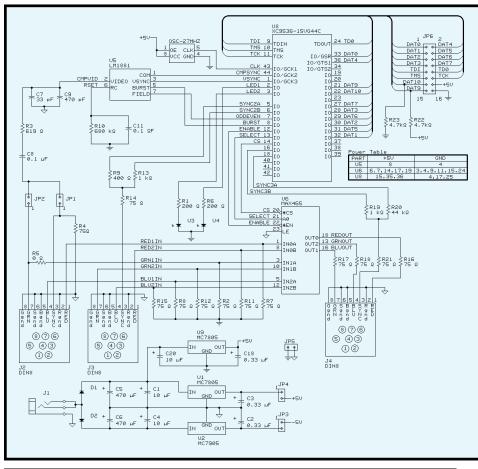

Now that you're acquainted with some typical flash EPAs, here's an example using an ADSP-2184L DSP and Am29LV040B flash memory.

The Am29LV040B (see Figure 2) has a basic set of memory strobes. Other flashes may provide READY/\*BUSY strobes, hardware pins for locking the contents of the memory, or methods of reading information for synchronous burst transfers. We chose this memory primarily for its simple hardware and software interfaces.

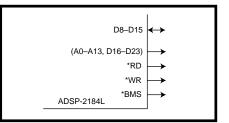

The ADSP-2184L is a 16-bit fixedpoint DSP. This processor family contains a number of external interfaces including an external byte-wide DMA port that can be configured to support 8-bit memories, including flash. Figure 3 shows the pins that the DSP uses to connect to an external memory.

There are 14 address and 24 data lines available externally on the DSP. This configuration enables direct externalprogram memory execution because its opcodes are 24 bits wide. But, when the DSP accesses external byte space,

| Function   | Purpose                                                        |

|------------|----------------------------------------------------------------|

| BDMA_SETUP | Initializes the byte-wide memory port for<br>flash transfers   |

| PROG_BYTE  | Write one byte of information to flash                         |

| READ_BYTE  | Read one byte of information                                   |

| SECT_ERASE | Erase one sector of information                                |

| MEM_IDENT  | Identify the manufacturer                                      |

| AUTO_INC   | Automatic incrementing of address for multiple-burst transfers |

Table 2—In our software, we adopted a function-calling scheme that hides much of the underlying protocols and architecture of the flash memory.

> only D8–D15 are connected to the flash memory data bus, allowing D16–D23 to become address bits and creating a total address reach of 4 MB.

> The DSP can supply the necessary chip-, read-, and write-select strobes to the flash. Because the ADSP-2184L operates at speeds up to 40 MHz and flash memory may be just 5–6 MHz, the on-chip wait-state generation logic enables a flash interface without external glue logic.

> The ADSP-2184L does not operate out of external byte-wide memory. That memory is typically too slow to support the processor's operational speeds. Instead, the DSP transfers the information from the byte-wide memory into internal SRAM and operates from this memory space.

> There are hardware provisions for packing data and program-memory words (16 and 24 bits) into internal memory. Byte memory space is intended to be a large region of memory where the processor can fetch instructions or data to be operated on or to save externally to the chip for later use. Software development tools let code and data be saved as memory overlays, which can be loaded into the DSP under control of an overlay manager.

#### FLASH SOFTWARE

The code modules of our ADSP-2187L flash software enable the programmer to access flash memory via function call APIs. Table 2 lists the base functions, along with their purpose.

Each function expects input data to be located in specific registers and output data to be placed into specific registers. Once you understand the rules, it's simple to tie the function calls into your software. An example of the assembly code used to program one byte of memory on the ADSP-2184L is in Listing 1.

The code shows the first layer of the software interface between the flash and DSP. Because many of the basic building blocks for each of the EPAs are similar, an additional set of functions (INIT\_SEQ, CMD\_WRITE, CALC\_ADR, and DQ7\_POLL) were written for PROG\_BYTE to call.

This function assumes that the flash software housekeeping function (BDMA\_SETUP), which configures the DSP for byte transfers, has already been called.

There are several steps to the basic program flow for PROG\_BYTE. First, place the appropriate values into the addresses pointed to by c\_byte, d\_ byte, addr\_lo, and addr\_hi.

Be sure that the values contained in the ar, ax0, ay0, and af registers are no longer needed. If they are needed after PROG\_BYTE completes, the background register set on the ADSP-2184L can be used for programming operations and then switched back when the function ends.

PROG\_BYTE calls two functions, INIT\_SEQ and CMD\_WRITE, which write the first three bytes of information into the Am29F040B's FSM to unlock the memory.

The third step is a memory transfer between the input data location and the API. This transfer is necessary to save the value of the data word for use later when polling the data.

CALC\_ADR creates the address where the data is stored in the flash. It performs the last byte transfer to the flash.

Lastly, DQ7\_POLL (which continually tests the status of the DQ7 bit) is called to determine when the flash has transferred the data into memory and when it's free to enter a new EPA.

Figure 3—The ADSP-2184L provides all the memory strobes required to control the flash memory.

#### NOW IT'S YOUR TURN

This flash interface is easy to tie into your application code. With a set of reference functions for interfacing these devices, you can add new functions as your system needs change and flash technology develops.

Ethan Bordeaux works for Analog Devices as a 16-bit DSP product line applications engineer. He has worked with embedded speech processing applications including speaker identification, speech recognition, and adaptive echo cancellation systems. You may reach him at ethan.bordeaux@analog.com.

Stefan Hacker is a DSP applications engineer at the European DSP support center for Analog Devices. His focus is on OEM accounts using 16- and 32-bit DSP products in consumer and industrial applications. You may reach him at stefan.hacker@analog.com.

#### SOFTWARE

The functions described here and instructions for linking them into your design are available via the Circuit Cellar web site.

#### REFERENCES

Advanced Micro Devices, Am29-F040B, Datasheet, 1998.

Analog Devices, ADSP-2100 Family Users Manual, 1995.

Atmel, AT29C040A Datasheet, 1998.

C. Leidigh, "Flash Memory Buyer's Guide," Communications Systems Design, March 1998.

#### SOURCES

#### Am29F040B, Am29LV040B

Advanced Micro Devices, Inc. (408) 732-2400 Fax: (408) 732-7216 www.amd.com

#### ADSP-218x

Analog Devices (781) 329-4700 Fax: (781) 329-1241 www.analog.com/dsp

#### AT29C040A

Atmel Corp. (408) 441-0311 Fax: (408) 436-4200 www.atmel.com

## FEATURE ARTICLE

**Andrew Lillie**

## **Embedded PWM Signals**

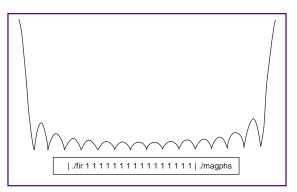

Andrew shows that embedded microcontrollers are quite capable signal generators and measurement tools. The modular design of the MPC555 enables the mixing and matching of submodules, so you can get the I/O you need. pplications have grown in complexity over recent years, and microprocessor suppliers have responded with more sophisticated embedded controllers. Today's microcontrollers have on-chip peripherals that control everything from automobiles to electronic xylophones.

One microcontroller application is PWM, a process used to control devices such as stepper motors, communication systems, battery management, audio applications, and thermal write/erase heads. The auto industry uses PWM to generate control signals.

The MPC555 embedded processor was designed for automotive applications like electronic throttles, regulator valves, and position motors. It carries a modular I/O system (MIOS) that is capable of eight PWM channels and 10 period- and pulse-measurement channels. MIOS1 is the implementation of the MIOS architecture used in the MPC555.

In this article, I outline the initialization of the MIOS module and explain the clock management and programming necessary to generate a 25% duty cycle, 2.5-MHz waveform. I also give you programming examples in assembly and embedded C. Let's look at how the MPC555 submodules are integrated and how they communicate with each other and the PowerPC core.

#### SIGNAL GENERATION

The MIOS consists of a library of flexible I/O and timer functions including counters, input capture, output compare, pulse and period measurement, and PWM. It's easily configured for different kinds of applications because it is composed of submodules.

The PWM can be initialized and programmed by setting up the appropriate registers. The eight PWM channels are controlled by one system register and three registers that are unique to each channel.

| Bit           | Name     | Function                    | Description                                                                                                                                                                                                                                                                                                               |

|---------------|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | PREN     | Prescaler enable            | This active high read/write control bit enables the<br>MCPSM counter. PREN is cleared on reset:<br>0 = MCPSM counter disabled<br>1 = MCPSM counter enabled                                                                                                                                                                |

| 1             | FREN     | Freeze enable               | When set, this active high read/write control bit makes it<br>possible to freeze the MCPSM counter if the MIOB freeze<br>line is activated:<br>0 = MCPSM counter not frozen<br>1 = Selectively stops MIOS1 operation when the<br>FREEZE signal appears on the IMB3                                                        |

| 2–11<br>12–15 | —<br>PSL | Reserved<br>Clock prescaler | This 4-bit read/write data register stores the modulus value<br>for loading into the clock prescaler. The new value is<br>loaded into the counter the next time the counter equals<br>one or when disabled (PREN bit = 0). Divide ratios are:<br>0000 = 16<br>0001 = No counter clock output<br>0010 = 2<br><br>1111 = 15 |

Table 1—Here are the bit settings for the MCPSM, address 0x306816. This register controls the MIOS counter prescaler submodule. The MIOS counter is the common clock between the eight PWM channels on the MPC555.

#### STARTING THE MIOS COUNTER

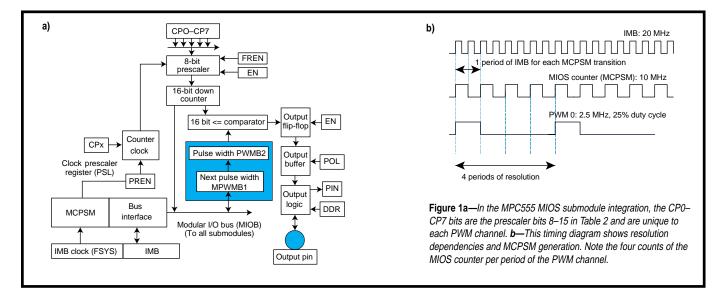

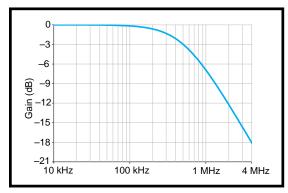

To use the PWM channels, start the MIOS counter, which is slaved to the intermodule bus (IMB). The IMB runs at half the system clock, so let's assume it's operating at 20 MHz. Figure 1 explains the MIOS submodule integration.

The MIOS counter prescaler submodule (MCPSM) divides the system IMB clock to generate the counter clock. It also synchronizes all the submodules with the same division of the system clock. The clock signal is prescaled by loading the value of the clock prescaler register into the prescaler counter every time it overflows. This arrangement permits all prescaling factors between 2 and 16. The MCPSM is controlled by the MCPSM status/control register. Counting is enabled by asserting the PREN bit in the control register (see Figure 1a and Table 1).

Because the PWM uses one count of the MIOS counter per transition of the PWM signal, the maximum fre-

| Bit  | Name | Function                     | Description                                                                                                                                                                                                                                                                                                                        |

|------|------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | PIN  | Pin input status             | PIN bit reflects the state present on MPWMSM (MIOS PWM<br>(Submodule) pin. Software can thus monitor the signal on<br>pin. The PIN bit is read-only. Writing to it has no effect.                                                                                                                                                  |

| 1    | DDR  | Data direction register      | When the PWM function is used, the DDR bit has no effect.                                                                                                                                                                                                                                                                          |

| 2    | FREN | Freeze enable                | <ul> <li>This active high read/write control bit enables the MPWMSM to recognize the freeze signal on the MIOB:</li> <li>0 = MPWMSM not frozen even if MIOB freeze line is active.</li> <li>1 = MPWMSM frozen if MIOB freeze line is active.</li> </ul>                                                                            |

| 3    | TRSP | Transparent mode             | <ul> <li>TRSP bit indicates that the MPWMSM double buffers are transparent: when the software writes to either the MPWMA or MPWMB1 register, the value written is immediately transferred to respectively counter or register MPWMB2:</li> <li>0 = Transparent mode deactivated</li> <li>1 = Transparent mode activated</li> </ul> |

| 4    | POL  | Output polarity control      | POL bit works in conjunction with the EN bit and controls<br>whether MPWMSM drives the pin with the true or the<br>inverted value of the output flip-flop.                                                                                                                                                                         |

| 5    | EN   | Enable PWM signal generation | The EN bit defines whether MPWMSM generates a PWM<br>signal or is used as an I/O channel:<br>0= PWM generation disabled (pin can be used as I/O)<br>1= PWM generation enabled (pin is output only)                                                                                                                                 |

| 6–7  | _    | Reserved                     |                                                                                                                                                                                                                                                                                                                                    |

| 8–15 | СР   | Clock Prescaler              | This 8-bit read/write register stores the two's complement of desired modulus value for loading into the built-in 8-bit clock prescaler. The value loaded defines the divide ratio for the signal that clocks the MPWMSM period counter. Table 3 gives the clock divide ratio according to the CP values; also see Figure 1.       |

quency that the MIOS modulators can generate is half the MIOS counter clock frequency. Later you'll see that this affects the resolution of the generated waveform. Figure 1b shows the interaction of the clock signals between MPC555 modules.

Following the register description in Table 1, set the first bit high to enable the counter and write 0010 to bits 12–15 to set the divider to 2 for the fastest counter possible. A faster counter results in faster waveforms and more

accurate measurements. All other bits should be 0.

In hexadecimal, write 0x8002 to register 0x306816 (MCPSMCR). If you program this register using a background debug mode tool, enter something like write -w 0x306816 = 0x8002. -w indicates that a 16-bit word is to be written.

To automate the programming process further or include the PWM in an application, you can write a header file in C similar to Listing 1. In the application code, the command for bit-wise programming is mcpsmscr.fren = 0;. To write the whole register at once, use MCPSMSCR =  $0 \times 8002$ ;.

Programming in C makes it easy to identify the bits and their functions. But for realtime debugging and testing, assembly is faster because the code doesn't need to be compiled and loaded each time.

Table 2—Here are the bit descriptions for the PWM status/control register (0x306006). Each of the eight PWM channels has a

PWM status/control register, allowing independent programming. Bits 8–15 determine the clock divider for each PWM channel.

| Prescaler Value | MIOS prescaler                                                                  |

|-----------------|---------------------------------------------------------------------------------|

| (CP in hex)     | clock divider                                                                   |

| FF              | 1                                                                               |

| FE              | 2                                                                               |

| FD              | 3                                                                               |

| FC              | 4                                                                               |

| FB              | 5                                                                               |

| 02<br>01<br>00  | <br>254 (2 <sup>8</sup> –2)<br>255 (2 <sup>8</sup> –1)<br>256 (2 <sup>8</sup> ) |

Table 3—These clock prescaler bits determine the prescaler used to divide the MIOS counter clock for each PWM channel.

#### CHANNEL PROGRAMMING

The next step is to program the individual PWM channels. Each channel is controlled by the period, pulse, and status/control registers.

The PWM period register sets the number of divisions per period of the waveform (i.e., the resolution of a single period). Choosing the resolution of the wave requires special consideration because it involves a compromise.

The resolution of the wave is inversely proportional to the maximum frequency that can be produced. A higher resolution requires more cycles of the MIOS counter per period and therefore a lower overall frequency.

The period register contains the binary value corresponding to the number of MIOS clocks allocated to the period of the waveform. The lowest possible resolution is two bits, with one clock each for high and low transitions.

Why would you want a higher resolution? Higher resolutions allow finer control over the signal's duty cycle. With 2-bit resolution, you're limited to a 50% duty cycle. With 16-bit resolution, you have almost 65,000 possible duty cycles. Continuing this example, you can program the PWM channel with a period resolution of four with write -w 0x306000 = 0x0004.

The PWM pulse register sets the number of divisions of the period register that are high. That means the ratio of the pulse register to the period register determines the signal's duty cycle.

The pulse-register value must be less than the value contained in the period register. In this example, enter write -w  $0 \times 306002 = 0 \times 0001$  for a 25% duty cycle on channel 0. The third register is the PWM status/ control register. The last eight bits of this register set the clock divider for the particular PWM channel. This clock divider operates on the MIOS counter submodule programmed earlier.

Each PWM channel uses a divider to slow the MIOS counter clock, but remember that this also affects the period and pulse-width registers. Table 2 describes the bit assignments for the PWM status/control register. Bits 8–15 determine the clock prescaler, whose values are shown in Table 3.

#### PUTTING IT TOGETHER

With the 20-MHz IMB divided in half for a 10-MHz counter, you need to program the PWM channel to divide the MIOS counter by 1. Now there's room to split the period into four parts and allow a 25% duty cycle at 2.5 MHz. Here, use write -w  $0 \times 306006 =$  $0 \times 54$ ff for PWM channel 0.

#### SUBMODULE CONFIGURATION

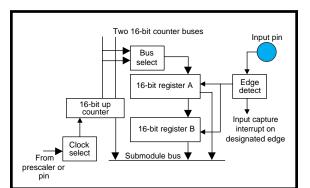

The MPC555 includes a MIOS dualaction submodule (MDASM) that makes pulse-width and period measurements. It can also be used to capture waveforms and generate single and continuous pulses. Let's use the MDASM to measure the period of the waveform that was generated earlier using the PWM.

To measure the output of the PWM with the MDASM, you need to get the signal from the PWM channel (here, channel 0) to the first MDASM channel. You can do this with a jumper wire and the pins available on the eval board.

The chosen MDASM channel must be configured to measure the period of the signal. You can calculate the period of the waveform by reading (from the register) the number of counts that occur during the period of the signal.

#### SETTING UP THE COUNTER

The MPC555 MIOS has a modulus counter submodule (MMCSM) that works as a free-running counter to which events can be referenced when they are detected. It can also be used for complex counting and timing functions.

The MDASM and the MMCSM work together to measure inputted waveforms. For this example, set the counter to be free-running and to automatically roll over when it reaches its maximum value. The counter is con-

Listing 1—This C header file for the MIOS counter prescaler module provides two methods to address the register: bit-wise in lowercase or word-wise in upper case.

| #ifndef _MIOS_H<br>#define _MIOS_H<br>//MIOS Counter Prescaler Submo                                                                                                                       | dule Status/Control Register(MCPMSCR)// |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| <pre>typedef struct {    unsigned pren:    unsigned fren:    unsigned reserved_bit2_11    unsigned ps1: } Mcpsmscr; #define mcpsmscr (*(Mcpsmscr #define MCPSMSCR (*(volatile #endif</pre> |                                         |

**Listing 2**—The MDASM module outputs the value of the MMCSM counter in a long word when the read - 1 command is used with register 0x306058. There are four counts of the 10-MHz clock between ABCD and ABC9.

| > | read -1 0  | x306058  |          |

|---|------------|----------|----------|

|   | (0x306058) | )        |          |

|   | 00306058   | ABCDABC9 | 00028002 |

|   |            |          |          |

trolled by the MMCSM status/control register described in Table 4. The MDASM can be referenced directly to an external clock if one is available.

I set up the MDASM to count on rising edges (register bits 3–4) and to use the MMCSM clock. The clock prescaler is programmed by the same values as the PWM prescaler bits listed in Table 3, and I set it up to follow the MMCSM clock with a prescaler division of 1. Therefore, the counter will run at 10 MHz, or 100 ns per count.

According to Table 4, you enter 0x0eff into register 0x306036 to set up the MDASM counter by using write -w 0x306036 = 0x0eff.

To ensure that the counter starts properly, reset it by loading all zeros into the modulus latch register. The modulus latch register is a read/write register that contains the 16-bit value of the counter used by the MDASM. write -w  $0 \times 306032 = 0 \times 0000$ resets the counter. With the clock running, you can set the MDASM to detect the waveform periods and reference them to the MDASM counter.

| Bit  | Name          | Function                                          | Description                                                                                                                                                                                                                                                                                                                                                                            |  |

|------|---------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0    | PINC          | Clock input pin status                            | This read-only status bit reflects the logic state of the clock input pin.                                                                                                                                                                                                                                                                                                             |  |

| 1    | PINL          | Modulus load<br>input pin status                  | This read-only status bit<br>reflects the logic state of the modulus load pin.                                                                                                                                                                                                                                                                                                         |  |

| 2    | FREN          | Freezeenable                                      | This active high read/write control bit enables the MMCSM to recognize the MIOB freeze signal.                                                                                                                                                                                                                                                                                         |  |

| 3, 4 | EDGN,<br>EDGP | Modulus load<br>falling/rising<br>edge sensitvity | MMCSM to recognize the MIOB freeze signal.<br>These active high read/write control bits set<br>falling/rising edge sensitivity, respectively.<br>00 = Disabled<br>01 = MMCSMCNT load on rising edges<br>10 = MMCSMCNT load on falling edges<br>11 = MMCSMCNT load on rising and falling<br>edges                                                                                       |  |

| 5,6  | CLS           | Clock select                                      | These read/write control bits select the clock<br>source for the modulus counter.<br>00 = Disabled<br>01 = Falling edge of pin<br>10 = Rising edge of pin<br>11 = MMCSM clock prescaler                                                                                                                                                                                                |  |

| 7    | _             | 0                                                 |                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 8–15 | СР            | Clock prescaler                                   | This 8-bit read/write data register stores the two's complement of the desired modulus value for loading into the built-in 8-bit clock prescaler. The new value is loaded into the prescaler counter when the next counter overflow occurs or the CLS bits are set to select the clock prescaler as the clock source. Table 3 gives the clock divide ratio according to the CP values. |  |

Table 4—The MMCSM status/control register (0x306036) controls the counter used by the MDASM to reference transitions on the inputted waveform.

#### **CHANNEL CONFIGURATION**

Next, initialize the MDASM to perform input period measurement. Like the PWMs, the MDASM channels have their own configuration registers. Each is programmed and read using the data A, data B, and status/control registers.

The data A register contains a value for the counter when the last event occurred. The data B register contains the previous value of data A or an independent measurement.

The status/control register has a readonly bit reflecting the status of the MDASM pin as well as read/write bits related to its control and configuration.

The MDASM status/control register (MDASMSCR, address 0x30605E) initializes the first MDASM channel. Table 5 defines the bits in this register.

Bit 0 is a read-only status pin that toggles according to the status of the incoming waveform. For input period measurement, let's write 0 to the unused bits (1, 3, 5, 6, 7, 8, and 11).

Because you don't want the MDASM to freeze in background debug mode, bit 2 is left as 0. Bit 4 is set to 0 to trig-

| Bit   | Name  | Function         | Description                                                                                                                                                                                                                                      |

|-------|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | PIN   | Pin input status | Reflects the status of the corresponding pin.                                                                                                                                                                                                    |

| 1     | WOR   | Wired-OR         | Not used in DIS, IPWM, IPM and IC modes.                                                                                                                                                                                                         |

| 2     | FREN  | Freeze enable    | This active high read/write control bit enables the<br>MDASM to recognize the MIOB freeze signal.                                                                                                                                                |

| 3     | _     | 0                |                                                                                                                                                                                                                                                  |

| 4     | EDPOL | Polarity         | In IPM and IC modes, the EDPOL bit selects the<br>input capture-edge sensitivity of channel A.<br>0 = Channel A captures on a rising edge.<br>1 = Channel A captures on a falling edge.                                                          |

| 5     | FORCA | Force A          | Not used in DIS, IPWM, IPM, and IC modes, and writing to it has no effect.                                                                                                                                                                       |

| 6     | FORCB | Force B          | Not used in DIS, IPWM, IPM, and IC modes. Writing<br>to it has no effect. FORCA is cleared by reset and<br>is always read as zero. Simultaneously writing a<br>one to FORCA and FORCB resets output flip-flop.                                   |

| 7, 8  | _     | Reserved         |                                                                                                                                                                                                                                                  |

| 9, 10 | BSL   | Bus select       | Selects which of the four possible 16-bit counter buses passing nearby is used by the MDASM.                                                                                                                                                     |

| 11    | —     | 0                |                                                                                                                                                                                                                                                  |

| 12–15 | MOD   | Mode select      | Selects the MDASM's mode of operation. To avoid<br>spurious interrupts, MDASM interrupts should be<br>disabled before changing the operating mode. It's<br>also imperative to go through the disable mode<br>before changing the operating mode. |

**Table 5**—The MDASM status/control register (0x30605E) is programmed using these bits. To measure the waveform's period and frequency, program it to perform input period measurement by writing 0010 to bits 12–15.

ger the MDASM counter on the rising edge. Figure 2 shows the MDASM submodule for input period measurement. Bits 9 and 10 select which 16-bit counter bus the MDASM uses. Writing 00 to these two bits selects the default.

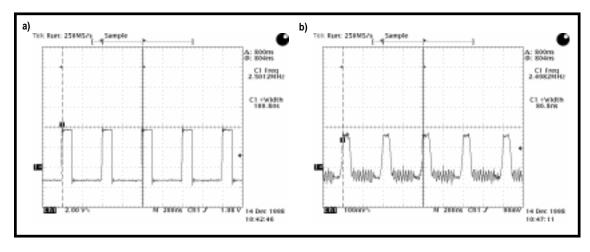

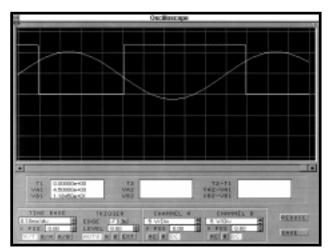

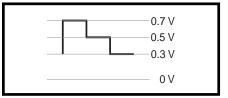

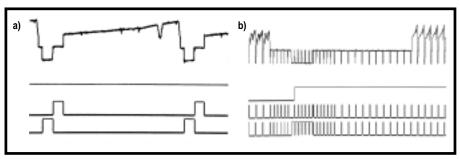

Photo 1a—The scope capture of the MPC555 MIOS PWM output shows a 2.5-MHz 25% duty cycle signal with a fast slew rate. The pulse width is measured at 100 ns or 25% of the 400-ns period. b—This scope capture of the MPC555 MIOS PWM output shows a 2.5-MHz 25% duty cycle signal with a slow slew rate. Note the volts per division scale compared to Photo 1a.

Other buses are available to the MDASM, depending on the frequency to be measured. To perform frequency measurement, you need to measure the input period (MOD 0010) and convert the time measurement into a frequency. It's also possible to measure the pulse width (IPWM) of the inputted signal by changing MOD 0010 to 0001.

To measure the input period, load write -w = 0x30605E = 0x0002 into the MDASM status/control register.

#### **OBTAINING MEASUREMENTS**

When the MDASM channel detects a rising edge, it writes the MMCSM counter value to its data A register. On detection of the following rising edge (one period later), the MDASM moves the first counter value into data B register and puts the new value in register A.

My MMCSM runs at 10 MHz, or counts at 100-ns intervals. Subtracting register B from register A gives the number of 100-ns counts during one period of the input waveform. To read the data in the data A and B registers, type read -1 0x306058 into the

Figure 2—Here's a MIOS double-action submodule configured for input period measurement mode. There are two 16-bit buses between the 16-bit up counter and data registers A and B.

command window of the background debug programmer.

To ensure that you read the contents of the two consecutive MDASM data registers at the same time, use a long read (-1). Otherwise, you might miscount because of the time it takes to read the data in two successive word reads.

The software tool returns eight hex characters in one long word. Listing 2 shows a measurement I made. Results from subsequent applications will differ from the example because the values are read from a free-running counter.

The long word ABCDABC9 contains the contents of the data registers. Data A contains ABCD, and ABC9 is in data B. By subtracting register B from register A (D – 9 in hex), you get 4. To calculate the frequency, multiply by 100 ns and take the reciprocal to get 2.5 MHz.

#### RESULTS

Photos 1a and 1b show the 2.5-MHz 25% duty-cycle waveform. An interesting feature of the MPC555 MIOS submodules is its ability to enable a

> slower slew rate on the generated waveforms. Photo 1a shows the faster setting and Photo 1b shows the slower one.

The slower transitions use less power because the keepers that pull the output high or low are turned off. This setup is useful in power-sensitive applications that require only slower waveforms to allow ample time for the gates to fully open. A slower rise/fall time may also be useful in analog applications involving audio where low-pass filtering needs to be kept to a minimum. Notice that the volts per division are turned down to detect the slower rise times in Photo 1b.

This adjustment was needed because, at 2.5 MHz, the 200-ns rise time in the slow slew mode isn't enough time for the signal to reach its final level because the pulse is only 100-ns wide (see Photo 1a). For a slower signal and a greater duty cycle this wouldn't be an issue and you could take advantage of the gradual rise and fall times.

Now, you've seen how embedded microcontrollers with modular chip design can serve as capable signal generators and measurement tools for different types of applications.

At Motorola, Andrew Lillie has worked in the powertrain systems and advanced media platforms divisions. He is now involved with system-on-a-chip design technologies. You may reach him at ra8334@email.sps.mot.com.

#### REFERENCES

A. Lillie, Using the MIOS on the MPC555 Evaluation Board, App note AN1778, Motorola, www.mcu.motsps.com.

Motorola, MPC555 User's Manual, www.mcu.motsps.com.

#### SOURCE

MPC555 Motorola (800) 521-6274 Fax: (512) 895-4465 www.mot-sps.com

## FEATURE ARTICLE

R.K. Kamat, G.M. Naik, & G.G. Tengshe

## Thermistor-Based Conditional Output Sensor

Conventional sensors can cause bottlenecks in many applications, so enter the world of smart sensor technology. These authors created a thermistorbased temperature sensor with built-in hysteresis to minimize sensitivity to noise and glitches. ver the past decade, we've seen a revolution in microelectronic circuits and devices. Today's microprocessors and microcontrollers are powerful and affordable, and they have revitalized the instrumentation world.

But, the modest suitability of conventional sensors used in microprocessor-based data-acquisition systems is becoming a bottleneck in diverse application fields.

This problem is being overcome by the rapid development of digital-output sensors that are compatible with microprocessors [1]. These so-called smart sensors have advantages like auto-

matic calibration, automatic linearization, insensitivity to interference, elimination of cross-sensitivity, and improved frequency response.

There's no question that the hardware is becoming more complex inside these sensors but the external hardware is more simple. This new arrangement saves the cost of extra signal conditioning and conversion [2]. One application for the smart sensor is a flip-flop sensor [3]. A flip-flop sensor has a circuit that's sensitive to the measurand and, in order to sense, changes the flip-flop between a stable and an unstable state by counting the number of ones and zeros. Such sensors offer advantages like possible integration with ADCs and access by addressing a matrix of a sensor as in SRAM [1].

The most striking fault of these sensors is their sensitivity to glitches or noise impulses. In this article, we recommend a new type of thermistorbased temperature sensor with hysteresis that minimizes the drawbacks of a conventional flip-flop sensor.

#### IC SENSORS IN THERMAL DOMAIN

IC temperature sensors can be divided into two groups—on-chip signal conditioning with a built-in sensor and on-chip signal conditioning with an external sensor. Integrating the modules on one chip results in minimal pick-up noise, adaptive processing, the possibility of wireless interfaces, on-chip linearization, calibration, and cross-sensitivity compensation.

The drawbacks of single-chip integration include nonstandard processing steps, nonstandard initial wafer sizes, and difficulty in predicting the behavior of the material after fabrication. Choosing a package that permits optimal interaction between the sensor and measurand can be difficult, and because of the measurand, there's the possibility of damaging the sensing core and conditioning circuitry.

As early as 1966, Si and GE were predicted to be the leaders in IC temperature sensors [4]. GE's poor temperature characteristics enabled Si to take over the IC market.

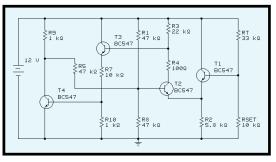

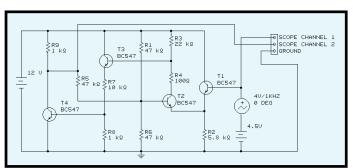

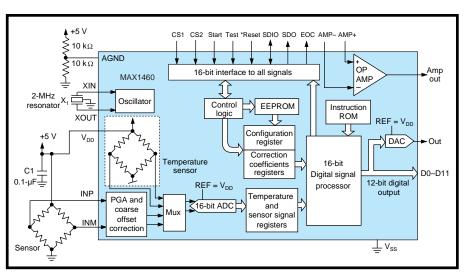

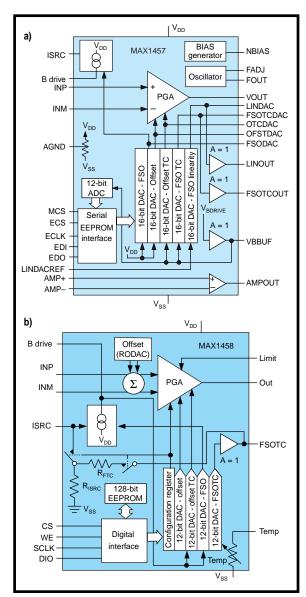

Figure 1—Here's the full schematic of the Schmitt-trigger sensor which features high input impedance and full output swing along with less current burden on the thermistor.

Drift in junction potential along with temperature sensing, in the case of P-N junction diodes, was the basis of first-generation IC temperature sensors and is still used today. A programmable temperature-monitoring chip with P-N junction as the temperature-sensing core was even used for tagging Atlantic salmon [5].

The transistor, which is the basic unit of the IC, exhibits good temperature sensing when connected in the negative feedback loop of an op amp. This performance seems to be the reason for the dual transistor structures found in many IC temperature sensors. These ICs use temperatureproportional delta VBE (also known as PTAT) that results from operating similar bipolar transistors at different current densities.

With the growing need for portable instruments, the focus has shifted toward low-power designs for IC temperature sensors. CMOS transistors are being used to reduce power consumption.

Other techniques, such as extensive switching of the circuit, on/off-keyedtype transmission to other modules, putting the possible number of submodules in standby mode, and hardware/ software partitioning, are being implemented in the effort toward lower power. Techniques like multithreshold CMOS (MTCMOS), super cut-off CMOS (SCCMOS), and variable threshold CMOS (VTCMOS) are also being used to reduce power dissipation [6].

A CMOS monolithic temperature sensor based on compatible lateral bipolar transistors for the sensor and reference parts was developed with all CMOS circuits for ADC, control, and calibration [7]. However, the current gain of the lateral bipolar transistor and the leakage current to substrate depend on the IC processes, so the desired results are hardly feasible. That's why vertical bipolar substrate transistors are used in recent CMOS sensors [8].

The sensing is based on the PTAT mechanism with the output chopped suitably for offset reduction and then passed through a sigma-delta A/D module for digitization. The chip is

Figure 2—The output response of the sensor was checked on Electronics Workbench. Here, the thermistor RT is replaced by a sine-wave generator to facilitate simulation.

1.5 mm<sup>2</sup> with a temperature measurement range of  $-40^{\circ}$  to  $+120^{\circ}$ C, a supply voltage as low as 2.2 V, and power consumption as low as 7  $\mu$ W.

IC-based temperature setpoint switches are also popular in control applications. Switching the output of an IC takes place when a sum of PTAT and its complementary CTAT pass through zero at a selected temperature set by external resistor [9]. This lowcost IC has an open-collector output and works in the range of  $-40^{\circ}$  to  $+150^{\circ}$ C with an accuracy of  $1^{\circ}$ C.