# REAL STREET OF THE STREET OF T

#### THE MAGAZINE FOR COMPUTER APPLICATIONS

## #108 JULY 1999 ROBOTICS

**Electronic Odor Perception**

The Stiquito/PC Link

**Internet Appliance How-To**

**On Call—Pagers and Embedded Control**

ActivMedia

| 12 Sniffing Robot—Robotic Odor Perception<br>Silvio Tresoldi |                                                                                                               |                                                               |          |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|

| 18                                                           | <b>A PC-Based Controller for the Stiquito Robot</b><br>James M. Conrad and Jonathan W. Mills                  |                                                               |          |

| 24                                                           | Internet Appliance Interface<br>Myron Loewen                                                                  |                                                               |          |

| 56                                                           | <b>Low-Cost Data Acquisition System</b><br>Michael Bading                                                     |                                                               |          |

| 64                                                           | <b>Turn the Page</b> —Pager Technology in Embedded Control <i>Ingo Cyliax</i>                                 |                                                               |          |

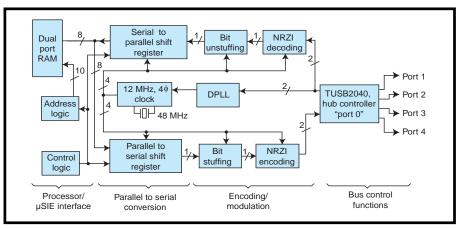

| 70                                                           | MicroSeries<br>USB Primer<br>Part 3: Low-Speed USB Host Controller<br>Glen Reuschling                         | Task Manager<br>Elizabeth Laurençot<br>Is the Head Screwed on | 6        |

| 74                                                           | From the Bench<br>Demystifying LCD Muxing<br>Jeff Bachiochi                                                   | Straight?                                                     |          |

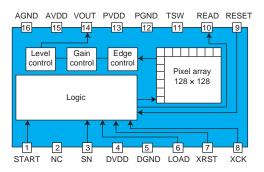

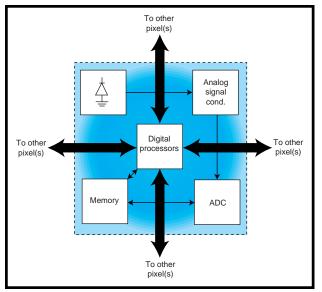

| 78                                                           | Silicon Update<br>Eye Candy—Camera Chips                                                                      | New Product News<br>edited by Harv Weiner                     | 8        |

| 1                                                            | Tom Cantrell                                                                                                  | Test Your EQ<br>Advertiser's Index                            | 82<br>95 |

|                                                              |                                                                                                               | August Preview                                                |          |

|                                                              | 36 NOUVEAU PC                                                                                                 | Priority Interrupt<br>Steve Ciarcia<br>Circuit Cellar Online  | 96       |

| edited by Harv Weiner                                        |                                                                                                               |                                                               |          |

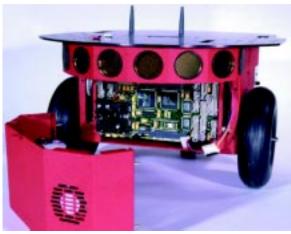

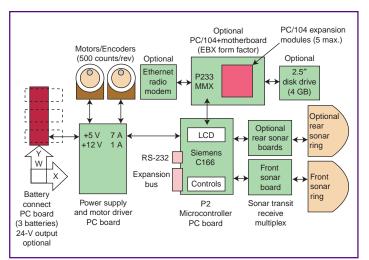

|                                                              | 38 PC/104 Takes a Ride<br>Embedding a PC in a Robot<br>Jeanne Dietsch, William Kennedy, John Belanger, and Ku | urt Konolige                                                  |          |

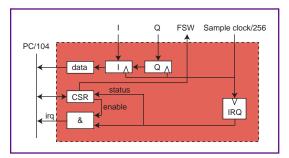

| Ý                                                            | 42 RPC Real-Time PC<br>Astronomical Issues—Part 4: Digital Radio Softw<br>Ingo Cyliax                         | vare                                                          |          |

|                                                              | 50 APC Applied PCs<br>Easy DOS it<br>Fred Eady                                                                |                                                               |          |

## TASK MANAGER

#### Is the Head Screwed on Straight?

s if you didn't know this already: robots are cool. When I asked a friend why he enjoys robots, his response was "because they're cool!" And when Ken proofed this issue, several times the articles were returned with the comment, "This is cool!" or even "This is *very* cool!" Indeed. No doubt. But, robots seem kind of like some of the teenagers I've met. You know, definitely "cool" but lacking common sense.

Of course, robots are fun. Robots are interesting. Robots are educational. And importantly, robots are useful. Let me mention just a few of the thousands of possible applications.

Robots build cars. They can map the ocean floor and report on whale pod migration. Devices such as the Stiquito, which James Conrad and Jonathan Mills discuss, help us conduct research on sensors, machine vision, and cooperative behavior.

Robots entertain us. They make cute little beep-beep sounds like R2-D2 and they smash cars at monster truck rallies. They play robo-soccer, as Jeanne Dietsch and her colleagues mention in their article on Pioneer robots.

Robots can even save lives. In this issue, Silvio Tresoldi presents an odor-perceiving robot that detects certain gases and follows a path to their source, which allows humans and animals (with their perceptive noses but vulnerable lungs) to stay out of danger.

Clearly, these are all good things, all good reasons to have robots as part of our daily lives. The problem is that robots do exactly what they're created to do. We program them to go forward, they go forward. We tell them to put that box there, and well, they put that box there.

What if there's a cliff? Or a puddle of water on the warehouse floor? Do they walk off the cliff? Drop the box in the puddle? Admittedly, these situations are simplistic, and sure, you can tack on a lot of sensors and program the robot to evaluate the relative safety of every next step. But that seems like overkill for some applications, doesn't it?

Although we humans have plenty of problems making contingency plans for ourselves, when the unexpected happens, we do adjust. We use our common sense and make the best choice we can. But is it remotely possible that we can plan for all the situations our robot might encounter? No way.

It's not an issue of hardware. The circuits are capable. But the software gets in the way. That's because, in order to write the code for the robot to make the best choice given the circumstances, we have to think about how we think—and that's tough. And then there's the difficulty of explaining how we think to someone else. Philosophers and psychologists having been grappling with this for centuries!

I may be too optimistic, but given all the artificial intelligence research happening in the world, perhaps the day will come when we can teach a robot common sense like we (try to) teach our kids. Now, *that* will be cool!

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot

TECHNICAL EDITORS Michael Palumbo Rob Walker

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Ingo Cyliax Ken Davidson Fred Eady

NEW PRODUCTS EDITOR Harv Weiner

Ingo Cyliax

ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> ART DIRECTOR KC Zienka

ENGINEERING STAFF Jeff Bachiochi

PRODUCTION STAFF Phil Champagne John Gorsky James Soussounis

> PROJECT EDITOR Janice Hughes

David Prutchi

EDITORIAL ADVISORY BOARD Norman Jackson

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

ADVERTISING SALES MANAGER Bobbi Yush Fax: (860) 871 (860) 872-3064 E-mail: bobbi.y

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

Fax: (860) 871-0411

E-mail: val.luster@circuitcellar.com

#### CONTACTING CIRCUIT CELLAR

SUBSCRIPTIONS:

Valerie Luster

(860) 875-2199

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199

GENERAL INFORMATION: TELEPHONE: (860) 875-2199 INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor. Circuit Cellar. 4 Park St., Vernon. CT 06066

EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St. AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box

Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellal<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, *Circuit Cellal*<sup>®</sup> disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published in *Circuit Cellal*<sup>®</sup>.

Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

elizabeth.laurencot@circuitcellar.com

6

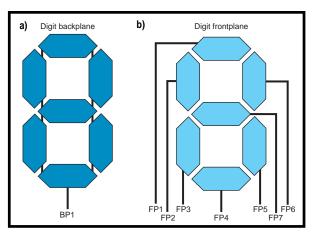

# NEW PRODUCT NEWS

#### PICmicro EDUCATION BOARD

The **Qik Start PICmicro Education Board** is a prewired hardware platform based on the Microchip PIC-16C74 microcontroller. Designed specifically to support educators in teaching embedded control design, the board can be used to demonstrate subroutines, port

configuration, interrupts, A/D conversion, and other microcontroller functions.

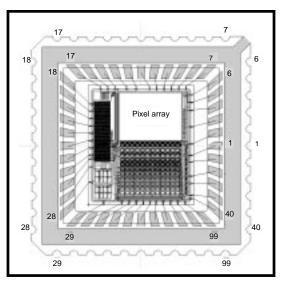

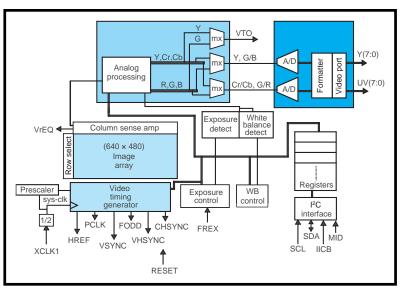

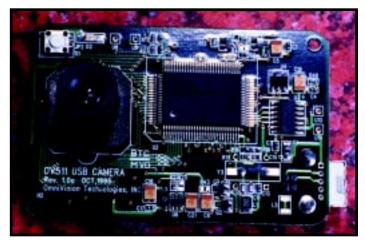

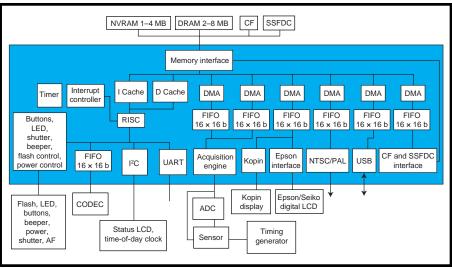

Software routines can be written to test a  $4 \times 4$  matrixed keypad, display information on  $2 \times 16$  alphanumeric LCD, and track A/D inputs from three potentiometers. Other routines include storing and retrieving information in memory, interfacing to the temperature sensor, measurement of rotary encoder signals, and communicating on an RS-232 buffered serial port.

The board comes complete with a UVerasable PIC16C74 microcontroller (including demo software), 4-MHz crystal, keyboard, a  $2 \times 16$  LCD display, eight LEDs, three potentiometers, and a regu-

#### **Edited by Harv Weiner**

lated power supply. A breadboarding area is also provided for building custom circuits (such as a CAN interface or motor controller), and it also incorporates an RJ connector for interfacing to the in-circuit debugger (ICD) available on the new Microchip products.

The product is available in three packages: the standard board (905170); the fullfeatured board (905171), which includes memory, RS-232, and ICD interface; or the whole-course solution (905175), which includes the standard board, textbook, and lab manual.

Diversified Engineering (203) 799-7875 Fax: (203) 799-7892 www.diversifiedengineering.net

# NEW PRODUCT NEWS

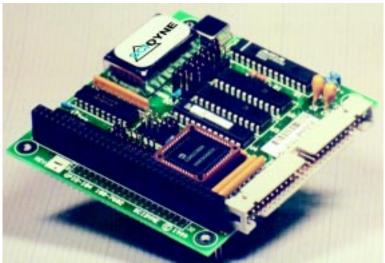

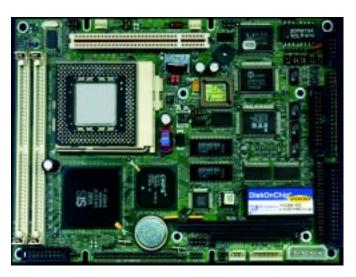

#### SINGLE-BOARD COMPUTER

The **MMT-51/251** is an SBC designed around the Intel 8051 core. Although designed with the Intel 8*x*C251 in mind, it supports any of the '51 core processors and many of the Philips and Dallas derivatives.

The MMT-51/251 provides all

the interfaces needed for a wide variety of OEM control applications. Features include two RS-232 serial ports (third RS-232 port available with the D580C320), 24 lines of parallel I/O, up to 64 × 8 of batterybacked SRAM/flash memory, and up to 64 × 8 ROM (EPROM, flash 5 or 12 V). Also featured are lowpower modes, a watchdog timer, a power-fail-detection option, two external interrupt sources, and 3–6 counter/timers.

Options for the board include RS-422/-485 levels for communication up to 5000', a clock/calendar, seven-position DIP switch, indicator LEDs, and  $\rm I^2C$  bus (Access. bus connector). Other options include eight channels of

10000

12-bit ADC (four channels differential), four channels of 12-bit voltage out DAC, 128– 512-KB serial EPROM, and a monitor/ debugger in ROM with 8-KB SRAM. The MMT-51/251 can be ordered in several different configurations. Pricing starts at **\$104/\$199.20** in quantities of 100.

> Midwest Micro-Tek (605) 697-8521 Fax: (605) 692-5112 www.midwestmicro-tek.com

# **NEW PRODUCT NEWS**

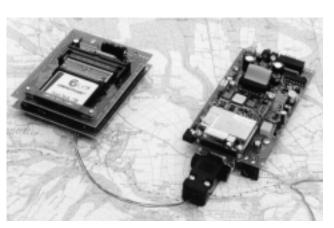

#### GPS DATALOGGING SYSTEM The TDS2020GDL GPS Data-

**logging System** makes it easy to build a custom datalogger to store position and other information on PCMCIA or CompactFlash cards for later retrieval and examination. After the module has run for minutes or months on a small battery,

the data-storage cards can be removed for easy data transfer into a PC. Applications range from satellitefed position information on latitude, longitude, date and time, to pressures, temperatures and rotation rates.

The TDS2020GDL GPS Datalogging System consists of two parts—the TDS2020C logger module and the GPS receiver. Data is recorded on CompactFlash cards in a Windows-compatible format so a PC can directly read the data into an Excel spreadsheet or Access database.

Interactive design enables an engineer with little programming knowledge to tailor the module to exact requirements, and supplied high-level Forth programs can be user-customized. Data and GPS logging in .CSV format is provided as a ready-made program, but sampling rate and sleep times can be changed.

With a keypad and graphics display, the module is a complete portable instrument or controller.

> Two serial ports and an optional CAN-bus interface enhance its communications capability.

> The TDS2020GDL GPS Datalogging Starter Pack, which includes the Rockwell Jupiter GPS Receiver, sells for **\$999**.

Saelig Co. LLC (716) 425-3753 Fax: (716) 425-3835 www.saelig.com

#### FEATURE ARTICLE

Silvio Tresoldi

# Sniffing Robot Robotic Odor Perception

Silvio's robot can perceive odor concentrations and follow a trail, which could be useful in situations where there are harmful gases or other toxic substances. Watch out, bloodhounds; this robot smells better than you! he continuing improvements in electronic technology have resulted in machines and robots with incredible characteristics. Every day, new robots with human-like abilities are being designed.

Until now, one of the human senses not yet implemented in a robot was the sense of smell. This article presents a possible application of odor sensing in mobile robots. The robot estimates the maximum gas concentration point and moves toward it or can also follow a smelling path on the ground.

A typical application for this kind of detector would be location of gases or dangerous substances. The smelling path follower can be used as a navigation system by allowing the robot to follow an odor trail on the ground or detect it to divert its trajectory [1].

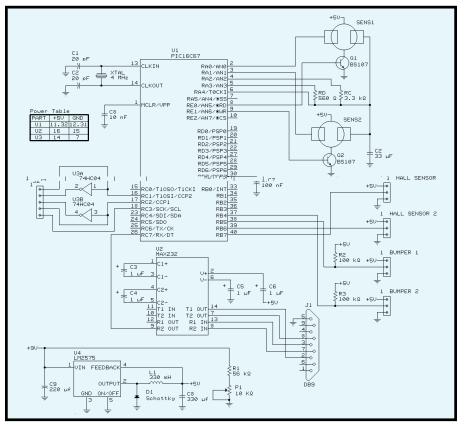

This application is an example of how a midrange microcontroller (a 40-pin DIP Microchip PIC16C67) can be used in robotics. Particular care was spent on electronic design and power consumption.

The robot includes two gas sensors (to measure gas concentration), two Hall-effect sensors (to control the motor rotation), and a serial interface. By using the information derived from gas sensors, the robot recursively calculates concentration gradients and decides which direction to go, thereby defining the duty-cycle values of the square waves driving the motors.

Two DC motors driven by PWM signals directly derived from the micro provide movement. A fuzzy-logic control monitors the correct movement.

#### GAS SENSORS AND CONCENTRATION MEASURE

With today's technology, it's possible to build an electronic nose with two gas sensors. In this application, I used Figaro TGS822 solvent sensors that are tin-dioxide  $(SnO_2)$  semiconductor gas sensors [2]. When a gas is present, an oxido-reduction reaction occurs on the sensing element and the surface resistance changes.

The sensor can be seen as a concentration variable resistor described by:

$$R_s = R_0^{\alpha}$$

where  $R_s$  is the sensor resistance,  $R_0$  is the sensor resistance with no gas, and  $\alpha$  is the sensibility.

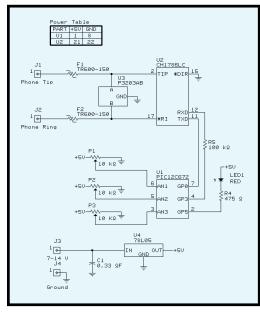

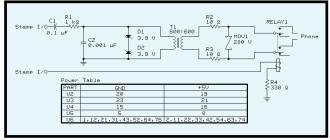

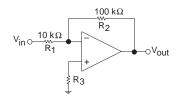

I chose to measure the concentration by means of a technique based on capacitor-charge timing. As shown in Figure 1, two sensors and two resistors are connected to a capacitor. When a pin is configured as an output and is set to a logic high, C begins charging.

All the other pins must be configured as inputs. If the pin is connected to the reference resistor  $R_{C}$ , C charges up to  $V_{thH}$  (high-threshold voltage of internal Schmitt trigger) in a time  $T_{C}$ :

$$T_{C} = C \times R_{C} \times 1n \! \left( \frac{V_{ref}}{V_{ref} - V_{th}} \right) \label{eq:Tc}$$

If the pin is connected to a sensor  $(R_s)$ , *C* takes a time  $T_s$  before reaching  $V_{thH}$ .

$$\Gamma_{\rm S} = {\rm C} \times {\rm R}_{\rm S} \times 1n \left( \frac{{\rm V}_{\rm ref}}{{\rm V}_{\rm ref} - {\rm V}_{\rm th}} \right)$$

You can use a micro timer to monitor these delays. To guarantee the same initial condition on *C*, define a sampling period and use  $R_d$  to discharge the capacitor (configure the connected pin as an output and reset it to a logic low). By dividing  $T_c$  and  $T_{s'}$  you get:

$$\frac{T_{\rm C}}{T_{\rm S}} = \frac{R_{\rm C}}{R_{\rm S}}$$

By knowing  $R_c$  and measuring  $T_c$  and  $T_s$ , you can determine  $R_s$  and then the gas concentration. This technique can use the micro's 16-bit internal timer, which improves the measure resolution.

Even though it's possible to delete undesirable effects of capacitor and resistance tolerances, the obtained resolution is limited to 11 or 12 bits because of the electronic noise and the pins' leakage current. When pins are configured as inputs, they absorb a current that causes the capacitor to charge more slowly.

Let's say  $i_{leak}$  is the typical pin leakage current (1 µA) [3]. Because four pins are configured as inputs and one as output, it's possible to demonstrate that the *C* voltage raising time is:

$$T_{S} = C \times R_{S} \times 1n \left( \frac{V_{ref} - 4i_{leak}R_{S}}{V_{ref} - V_{thH} - 4i_{leak}R_{S}} \right)$$

Let's use a particular algorithm to calculate the concentration gradient. In order to work properly, sensors must be heated. A heater is implemented into the sensor and presents a low value resistance (30–40  $\Omega$ ) that must be connected to a power supply. The corresponding high current (150 mA) increases power consumption.

Instead of a DC current flow, I used dynamic driving by means of a switching-mode transistor (BS107) driven by a square-wave signal with a duty cycle of 50%. A sensible decrease in power consumption was obtained and robot autonomy increased.

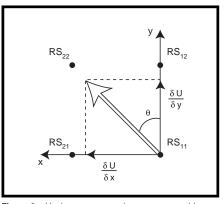

By using the gas-concentration measures, the robot decides to go toward the maximum gas concentration point. Using two gas sensors mounted on the robot at a proper distance, you can obtain information about the spatial distribution of gas.

Note that the direction where the gradient is null describes the maximum increasing direction of function U. Therefore, by sampling the gas concentration U using two sensors, it's possible to determine the gradient:

$$\overrightarrow{grad}U = \overrightarrow{u_x} \times \frac{\delta U}{\delta x} + \overrightarrow{u_y} \times \frac{\delta U}{\delta y} + \overrightarrow{u_z} \times \frac{\delta U}{\delta z}$$

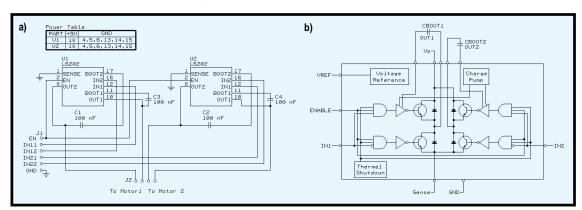

Figure 1—Here are the electronics for gas measurement and fuzzy control. You can see the voltage regulator, two gas sensors, serial interface (with ICL232) and inverter 74HC04 (to have antiphase signals drive DMOS), and the connection to the second PCB and Hall-effect sensors.

As shown in Figure 2, by estimating the direction where the gradient is null, you can find angle  $\theta$ , which is the steering angle in the robot motion.

To calculate the gradient, I implemented an algorithm (the Crank-Nicholson differentiator) [4] in which each directional difference is determined as:

$$\begin{split} \frac{\delta U}{\delta x} &= \frac{\frac{T_{S22} + T_{S12}}{2T_C} - \frac{T_{S21} + T_{S11}}{2T_C}}{\frac{T_{S22} + T_{S12}}{2T_C} + \frac{T_{S21} + T_{S11}}{2T_C}} \\ &= \frac{T_{S22} + T_{S12} - T_{S21} - T_{S11}}{T_{S22} + T_{S12} + T_{S21} + T_{S11}} \\ \\ \frac{\delta U}{\delta y} &= \frac{T_{S22} + T_{S21} - T_{S12} - T_{S11}}{T_{S22} + T_{S21} + T_{S12} + T_{S11}} \end{split}$$

where time  $(T_g)$  is a concentration measure (in fact, it's directly proportional to the sensor's resistance,  $R_g$ ). Thanks to this equation of the directional difference, it's possible to demonstrate that the effect of leakage currents is deleted.

By having the gradient expression, the robot can determine the angle  $\theta$  and, knowing the direction, move toward it. This method can be used when the robot is a maximum concentration point detector or a smelling-path follower.

#### **ROBOT CHARACTERISTICS**

The robot must have small dimensions to move in restricted spaces, so small motors were a necessity. I used two 3–6-VDC motors that provided low price, good characteristics, and easy driving control.

These motors are sources of strong electromagnetic emissions that could compromise the micro's functionality, so mechanical shielding and two different PCBs were introduced. On the first PCB, there are gas sensors, a micro, a serial interface, and the circuitry for the Hall-effect sensors and driving bumpers (see Figure 1). The motor drivers are on the second PCB.

A PIC16C67 with a 4-MHz quartz oscillator was used and the PCB has a 5-VDC voltage supply obtained by a 9-VDC battery and a DC/DC stepdown voltage regulator (a National Semiconductor LM2575), which can decrease power losses and assure the correct voltage even when the battery voltage drops.

A resistive partitor was introduced to monitor battery charge. A micro pin is connected to the central point and when the voltage reaches the low threshold voltage of the internal Schmitt trigger ( $V_{thl}$ ), the robot is stopped. This technique ensures that the correct input value is sent to the voltage regulator and then to all the circuitry.

I chose pulse-width modulation to drive the motors. Modulating the duty cycle of square-wave signals enables you to change average motor voltages  $(V_{Ln})$ , as shown by:

$$V_{Lm} = V_{S}(2D - 1)$$

where  $V_s$  is the voltage supply and D is driving signal duty cycle.

Driving a motor with different voltages permits different rotation velocities. The robot is steered by rotating the driving wheels. It's possible to vary motor rotation and have the robot steering only work on duty-cycle values.

It's also possible to guarantee negative average voltages (which reverses the motor rotation). During gas-concentration measurement, the robot switches off the motor (working on the ENABLE pin) to reduce noise effects.

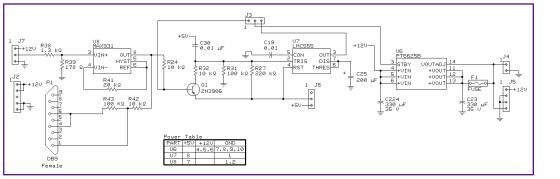

Full-bridge DMOS drivers (L6202 SGS-Thomson) are mounted on the second PCB (see Figure 3). Thanks to the switching unipolar devices, power losses are strongly reduced and because of internal implementation, the DMOS driver can connect directly to the micro.

A locked anti-phase control is used, and with a single PWM input signal, it's possible to drive a diametrically

**Figure 2**—Having a concentration measure enables you to calculate the direction where the gradient is null, thus estimating the steering angle  $\theta$  of robot motion.

opposite pair of DMOS switches together. The two pairs of switches are driven by the anti-phase signal obtained by the 74HC04 on the first PCB. For avoiding cross-conduction (two DMOS on the same side switching on contemporary and then short-circuiting the power supply), an internal deadtime logic is implemented.

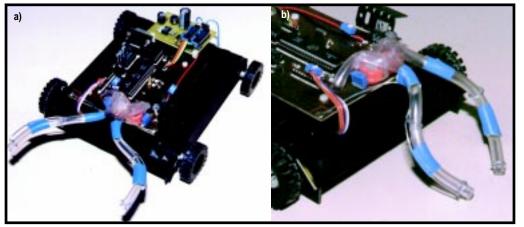

By having two separate voltage supplies for the PCBs, you remove the effect of conducted noise from the motors, which are directly mounted on the robot chassis. The chassis is made of aluminum (to have a light structure) and consists of a plane under which the motors are mounted (see Photo 1a). The metal plane can serve as an electromagnetic shield to reduce the motors' electromagnetic emission.

After estimating the direction to follow (and the angle  $\theta$ ), it's possible to determine the difference of the duty cycle, thus giving the proper signals to the motors. The robot is monitored to ensure it doesn't get diverted because of mechanical or dynamic phenomena. Sensors track the wheel rotation and estimate the robot's direction. Hall-effect sensors and eight little magnets were put on each wheel. Every time a magnet passes the sensor, it generates a signal and the micro increments a counter (if the signal is derived from the right wheel) or decrements it (if the signal is derived from the left wheel). Optical sensors were not used because any powder or dust along the path influences the sensors' response.

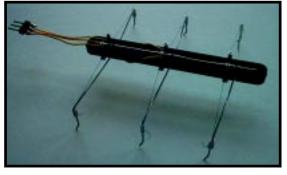

The gas sensors must be positioned in different places when the robot is working as a maximum-concentrationpoint detector and when it is working as a path follower. As a maximumconcentration-point detector, the sensors must be as far apart as possible to provide more information about the gas distribution. When following a path, the sensors must be as near as possible to the smelling path.

To ensure a correct operation without moving the sensors, I used an aspiration system, which lets me choose where the robot "sniffs" by simply bending two tubes (see Photo 1b). Fuzzy logic is used to link information about the gradient estimation and the direction of travel.

#### **ROBOT LEARNING**

Because of differences among motors and sensors, a learning function is used to reach two goals—to determine both the  $R_0$  and duty-cycle values for each gas sensor to guarantee identical motor rotation.

As I mentioned,  $R_0$ s are different from sensor to sensor. It's possible to delete this undesirable tolerance by performing lots of measures without gas and calculating the average value of  $R_s$  for each sensor (without gas,  $R_0 =$  $R_s$ ). The measure with gas ( $R_s$ ) is then compared with this value.

Figure 3—These schematics show the PCB (a) and internal electronics (b) of the SGS-Thomson L6202 DMOS driver. It is possible to bootstrap the capacitor, which is directly connected to the outputs and the internal charge pump, voltage reference, and thermal shutdown.

Photo 1a—Note the two PCBs on the sniffing robot. While the robot is working as a maximum gas point detector, the aspirator tubes are far from each other. b—When the robot works as path follower, all you have to do is bend the tubes down toward the ground and the sensors can follow the odor trail.

When the same voltage is supplied to the two DC motors, because of internal electrical and mechanical differences, different rotations are noted. To delete this effect and guarantee identical rotation, the duty-cycle value must be measured. This measurement is obtained via signals from Halleffect sensors and a continuing variation of duty-cycle values.

At the beginning of the process, a threshold value is loaded into the micro's counter and the same dutycycle values are supplied to the motor drivers. Rotations are measured as different signals from the Hall-effect sensors and thus different values of the micro's counter (remember, its value is increased or decreased each time a signal from the left or right wheel is sensed). This value is used to estimate the difference of the duty cycle to apply to motor drivers.

When no difference between the counter and threshold values is detected, the duty-cycle values are loaded into memory cells and added to the gradient information. When the angle  $\theta$  is null, you have a linear trajectory even though there are strong differences in the motors' characteristics. This procedure annuls the intrinsic motors' diversity and guarantees that steering is a result of gradient estimation, not dynamic or mechanical problems.

#### **FUZZY-LOGIC CONTROL**

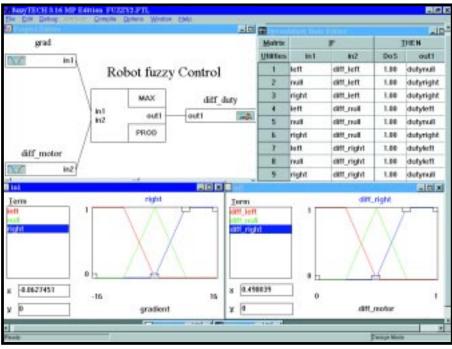

After you estimate the direction the robot needs to go, you have to combine gradient information and Hall-effect signals to control the correct movement. Fuzzy-logic control helps solve this problem. I used *fuzzy*TECH-MP devel-

opment tools (see Photo 2) to combine fuzzy variables gradient and diff\_ motor to have the output fuzzy variable diff\_duty.

The variable gradient comes from gradient estimation and presents three MBFs—left is activated if the gradient estimation gives a left direction to follow, null if the direction is straight, and right if the gradient is to the right.

diff\_motor derives from the Halleffect signal (and represents differences of rotation). It is also described by three MBFs. Each MBF is activated if the robot is going toward the left (diff\_ left), the right (diff\_right), or straight (diff\_null). The output variable diff\_duty represents the difference of the duty cycle to apply.

Typical fuzzy rule structure makes control easy. By introducing three MBFs for each fuzzy variable (as shown in the lower side of Photo 2), it's possible to have nine activation rules (as shown in the upper right side of Photo 2). A typical activation rule is made of:

Photo 2—This is what the fuzzy-logic controller, spreadsheet rule editor, and MBF of the input fuzzy variables gradient and diff\_motor look like.

IF cond1 AND cond2 THEN cond3

where cond1 is a condition of the variable gradient, AND is a Zadeh logic operator, cond2 is a condition of diff\_ motor, and cond3 is the activation diff\_duty.

It's possible to use human thought to write activation rules. The gradient information is compared with the diff\_motor information. If they match, the regulation action is light. In fact, this situation means a correct robot direction, and dutynull is activated to ensure a light regulation.

If the gradient and diff\_motor information contrast, regulation is strong. In this case, the robot isn't going in the correct direction and has to divert, so the fuzzy variables dutyleft or dutyright are activated.

Defuzzification is obtained by the CoM (Center of Maximum or Sugeno) algorithm to ensure good resolution and easy calculation. Thanks to the RS-232 serial interface, it's possible to adjust the fuzzy parameters as MBF or index of activation of each rule.

#### RESULTS

This project required many tests. Initially, the robot had to learn in a gas-free environment. At first, the robot moved chaotically, but because of the dynamic regulation of the duty cycle, it soon began to follow a linear trajectory.

To test the robot as a maximumgas-concentration-point identifier, a plate with alcohol and naphthalene was set up to simulate a gas source. Given the solvent sensors, the electronic-nose response was good even though we didn't use gas. At 4–5 m from the source, the robot came close to the plate (less than 15 cm away) and even touched it several times.

To test all possible behaviors, different starting positions were tried. The main setback was airflows, which tend to spoil the spatial distribution of gas and divert the robot from the gas source.

To test the robot as a path follower, we drew a path using the same alcohol and naphthalene mixture but more concentrated. The odor trails had different shapes to test the robot's ability to follow paths.

If the trail contained an angle less than 120°, the robot had problems following the path. A better aspiration system and mechanical structure may solve this problem.

In other tests, we found that by using a switching voltage regulator and unipolar motor driver, it's possible to decrease power losses and increase robot energy autonomy. Using a micro, we integrated all the work into one device. Good software development decreases the number of components on the PCB, lowering cost.

An electronic nose may seem strange, but an odor-sensing robot can be useful when the presence of gas or toxic substances is dangerous to humans.

Silvio Tresoldi works as an electronics designer in microcontroller applications. You may reach him at set\_electronics@usa.net.

#### REFERENCES

- R.A. Russell, "Laying and sensing odor marking as a strategy for assisting mobile robot navigation tasks," *IEEE Robotics and Automation*, Sept. 1995.

- [2] Figaro Engineering, TGS 822 for solvent vapor detection, Technical Information, 1996.

- [3] Microchip Technology, Microchip PIC16/17 Handbook, 1997.

- [4] M. Proakis, Digital Signal Processing: Principles, Algorithms and Applications, Prentice-Hall, Englewood Cliffs, NJ, 1991.

#### SOURCES

#### **PIC16C67**

Microchip Technology, Inc. (602) 786-7200 Fax: (602) 899-9210 www.microchip.com

#### LM2575

National Semiconductor (408) 721-5000 Fax: (408) 739-9803 www.national.com

#### L6202

SGS-Thomson (617) 259-0300 Fax: (617) 259-4421 www.scp.sidex.ro/stonline/index.htm

#### TGS822

Figaro USA, Inc. (847) 832-1701 Fax: (847) 832-1705 www.figarosensor.com

#### *fuzzy*TECH

Inform Software (630) 268-7550 Fax: (630) 268-7554 www.inform-ac.com

#### FEATURE ARTICLE

James M. Conrad & Jonathan W. Mills

# A PC-Based Controller for the Stiquito Robot

Small. Inexpensive. Easy to develop. The Stiquito meets all of these requirements. If you've never worked with one before, listen up as James and Jonathan explain how they made this little robot walk with a tripod gait. Simple. he typical legged robot is large, complex, and expensive. Naturally, such factors have limited the use of legged robots in research and education.

Few universities can afford to construct robot centipedes or 100 six-legged robots to study emergent cooperative behavior. Even fewer universities can give each student in a robotics class their own walking robot.

The introduction of the Stiquito, which is shown in Photo 1, changed all of that. The Stiquito was developed from a larger and more complex robot called Sticky (because it looked like an insect commonly called a "walking stick"). The Stiquito is a small, simple, and inexpensive six-legged robot that has been used as a research platform to study computational sensors, subsumption architectures, neural gait controllers, emergent behavior, cooperative behavior, and machine vision. It has also been used to teach science in primary, secondary, and high school curricula.

Jonathan Mills announced the availability of the Stiquito in 1992. For \$10, you could order a kit from Indiana University to build the small robot. Jonathan didn't envision the number of requests he would receive, which by 1996 had reached more than 3000. The volume of orders strained his personal ability to fulfill them and he soon stopped supplying the kits.

At the same time, we were finishing the book *Stiquito: Advanced Experiments with a Simple and Inexpensive Robot.* The book contains instructions on building the Stiquito and its control circuits as well as a robot kit.

One of the most flexible ways to control the walking gait of a Stiquito robot is by using a PC and writing a program. The program controls the contractions of the nitinol wire, thus making the Stiquito walk.

This article contains the instructions for making a circuit that can be plugged into the parallel port of a PC. We also discuss the concepts of the PC parallel port and provide instructions on how to write a program to make the Stiquito walk with a simple tripod gate.

#### THE BIG PICTURE

The PCB plugs into the PC's parallel port and generates enough current to light up LEDs on the board and make the Stiquito walk. The LEDs help you develop your computer program, and

Photo 1—The stiquito is an inexpensive hexapod robot that uses nitinol wire for propulsion. When nitinol is heated by running current though it, the wire contracts, moving the legs back, and the robot forward. Watch out! Nitinol has a tendency to eat batteries in no time, so an external power supply is suggested.

the board provides an easy-to-see report on how your program is executing. Once your program correctly works and the LEDs show a viable gait, you can plug the Stiquito control wires into a socket on the board.

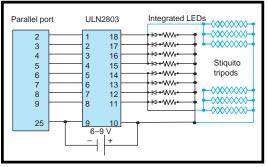

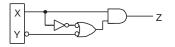

The black lines in Figure 1 show the logic on the circuit board when the Stiquito isn't attached. The ULN-2803 driver chip inverts the value of the input so the LED will light up when current is drawn towards the ULN2803.

The addition to Figure 1, shown in blue, illustrates the attachment of the Stiquito robot. In this circuit, the LEDs light and the nitinol legs contract.

The circuit in Figure 1 should be used without the Stiquito attached to test your hardware and software. This precaution protects the Stiquito's nitinol actuators from damage while you are developing your circuit.

The parts needed to build this simple board are readily available from electronics suppliers and cost about \$5. In addition to the circuit board, we made a tether to connect the board to the Stiquito robot.

#### MAKING THE PCB

Although there are many circuits you can build to attach to the parallel port, we recommend using a circuit that doesn't draw current from the PC. We recommend a dedicated power supply, a 5–6-VDC transformer, or a 9-V battery.

To make the parallel port board, simply insert the sockets, integrated LEDs, and connector into the board and start soldering. After that, insert the ULN2803 chip into the socket and solder your power source to the two-pin jumper post. Make sure you insert the LEDs into the board in the correct orientation. We used integrated LEDs, which have a diode and resistor combined in one package.

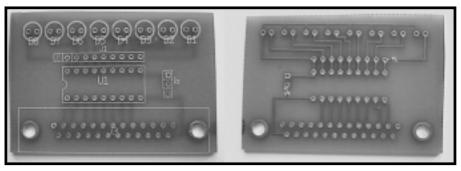

The component and solder sides of the PCB are shown in Photo 2. Although we made a custom PCB, we have also used a Radio Shack perf board 276-150, which is particularly handy because it has board holes electrically connected like a breadboard.

Your PC parallel PCB is now complete. Using your ohmmeter, put one

Photo 2—This board was custom made for this circuit, but you can use perf board material as well. We also recommend socketing the ULN2803 instead of soldering the chip to the board in case the chip fails.

contact on the pin labeled 1 or 9 of the header and the other contact on each of the other eight pins, one at a time. Make sure the ohmmeter registers some resistance, but not infinite resistance. Check your work to make sure you have no shorts or broken traces.

#### **GETTING ATTACHED**

Now that you've built the parallel port controller board, you need to prepare the Stiquito robot and make its control tether.

Cut a small length of wire-wrap wire and solder it to the center Stiquito bus bar and then to the center pin of the three-pin jumper. Solder the other two Stiquito tripod control wires to the two outside pins of a three-pin jumper.

Sand all six ends of the three wires of the magnet wire group. Next, you need to solder the three wires at one end of the magnet wire to the three pins of a three-pin socket. Identify the wire soldered to the center of the three-pin socket and solder it to the first pin of a nine-pin jumper post.

Solder one of the remaining wires of the tether to the next four pins of the nine-pin socket and use some of the wire-wrap wire to connect these four pins together (repeat this step with the remaining wire of the tether).

Plug the tether into Stiquito, but don't plug it into the parallel port card yet. Use the board to test your Stiquito walking

Figure 1—Only nine of the parallel port pins are used. The ULN2803 Darlington transistor array is a common chip used as a current driver. The integrated LEDs are used to help program Stiquito's walking gaits. Four transistors drive three Stiquito legs. program by observing the LEDs (perhaps preventing damage to the nitinol wires because of a programming error).

#### THE PARALLEL PORT

The parallel port was designed to serve as an output port from a PC and attach to a printer. Some parallel ports allow both input and output, but we only used the port as an output.

Although there are 25 pins for a parallel port, we only use nine. Eight lines are used as data output lines and one line serves as the electrical ground.

When using the parallel port, computer programmers usually write information to two locations. One register location controls the port, and the other contains the data to send. We used only the data register.

Some computers have more than one parallel port, generally labeled LPT1, LPT2, and LPT3. Each has a different data register. You can access them by using a different register address.

Typically, the register address for the single parallel port (or LPT1) is &H378, but your PC may use another address like &H278 or &H3BC. You can verify this by using the Microsoft diagnostics program (MSD.EXE) and examining the port address.

We use all eight of the parallel port output lines to control our Stiquito

robot, and we control each line with a binary digit, or bit. A response of 1 means turn on the line, and a response of 0 means turn off the line.

To write to the parallel port, write eight bits of data to the parallel port's data register. For example, to write the signal 1 to the top four bits and 0 to the lower four bits of the register, send the eight bits 11110000 to the port. In QBASIC, this is written as OUT &H378, *data*, where *data* is the bit pattern 11110000.

Unfortunately, we can't represent the bit pattern 11110000 as data in the QBASIC language. But, we can convert it to hexadecimal representation.

For our Stiquito control application, we only used nibble values of 0000 (0) and 1111 (F). To define the value in a hexadecimal number, we put &H in front of the digits. The line is now written OUT &H378, &HF0.

#### **GAIT PROGRAMMING**

The mechanisms of arthropod locomotion are complex and have been extensively studied. The structure of Listing 1—This program makes Stiquito walk with a tripod gait. This code assumes that the upper nibble controls one tripod, and the lower nibble controls the other. We allow the nitinol to rest after it is activated.

```

REM "OUT &H378" sends an 8-bit value to the printer port.

The

REM data sent is hexadecimal.

DELAY = 14000

10 OUT &H378, &HF0 : REM &HF0 is binary 11110000

FOR x = 1 TO DELAY : NEXT x

OUT &H378, 0

FOR x = 1 TO DELAY : NEXT x

OUT &H378, &HF : REM &HFO is binary 11110000

FOR x = 1 TO DELAY : NEXT x

OUT &H378, 0

FOR x = 1 TO DELAY : NEXT x

REM If a key on the keyboard was pressed, then end.

REM Otherwise, walk some more!

a = INKEY$

IF a = "" THEN GOTO 10

END

```

an insect leg is also quite complicated. But even though the Stiquito is simple, small programs can demonstrate the fundamental features of arthropod locomotion. Later on, you can develop more realistic models of gait controllers based on neural networks or central pattern generators and feedback from strain gauges or other sensors that

```

Listing 2—This code piece shows how to keep nitinol contracted with a 33% duty cycle.

```

```

REM High-frequency pulses initially contract actuators

FOR a = 1 TO 20

OUT &H378, &HF0

: REM &HFO is binary 11110000

FOR x = 1 TO 100 : NEXT x

OUT &H378, 0

FOR x = 1 TO 100 : NEXT x

NEXT a

REM Low frequency pulses maintain actuator contraction

FOR a = 1 TO 40

OUT &H378, &HF0

: REM &HFO is binary 11110000

FOR x = 1 TO 100 : NEXT x

OUT &H378, 0

FOR x = 1 TO 200 : NEXT x

NEXT a

```

mimic the sensorimotor loop in a real insect.

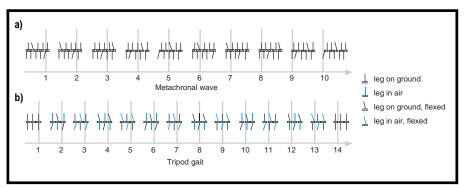

The gaits of insects are believed to be a result of central pattern generators that vary the animal's gait from a metachronal wave to a tripod gait and all the variations in between. Each gait conserves energy as it preserves the balance of the insect. As the sequences in Figure 2 indicate, the insect is always in a stable position with at least three legs (and often more) on the ground at all times.

The metachronal wave is the slowest and most stable gait. It's seen when a "wave" of leg movement ripples down each side of the insect or arthropod. The animation sequence in Figure 2a shows two waves flowing down each side of a ten-legged insect robot. The tripod gait is the fastest stable gait, with two legs on one side of the insect and one on the other side alternately on the ground or in the air, as shown in an animation of an advanced six-legged insect robot (see Figure 2b).

This tripod gait relies on a leg that has two degrees of freedom. The Stiquito assembled using our book has only one degree of freedom.

Our Stiquito walks with a simpler form of the tripod gait shown in Figure 2b. The legs only flex and relax while they are on the ground. This is the same way it is controlled using the manual controller explained in our book.

Using QBASIC to control the walk, you'll need to use the OUT statement to activate and deactivate the legs. You should add a delay in your program to hold the activation signal for about 1 s, then hold the deactivation signal for 1 s. The code to perform this task for one tripod is shown in Listing 1.

The number 14000 is an arbitrary value that is computer dependent. You may have to make this number

higher if your computer is faster than a '486-based machine (66 MHz).

#### SAVING POWER

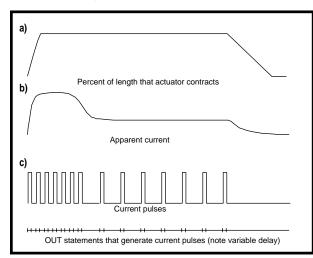

Driving the nitinol actuator with the same amount of current is unnecessary after the nitinol contracts. Only enough current to keep the nitinol contracted (i.e., just enough to replace the energy that escapes as heat) is needed. The current and the voltage supplied to the nitinol cannot be changed dynamically, but the power can be varied using a technique called pulse frequency modulation (PFM).

PFM means that the number (frequency) of pulses is varied over time. The PC parallel printer port and the interface card can generate a PFM signal because the nitinol reacts slowly compared to the speed with which a BASIC program can turn the ULN2803 driver chip on and off.

By varying the length of time that the driver chips are left off, the frequency of the pulses can be increased or decreased. This arrangement allows the power used to drive the robot to be varied dynamically.

The nitinol actuator behaves as a leaky integrator of the current pulses sent to it and responds to the heat generated by the current pulses and lost to convection from the wire. Figure 3 shows how a PFM driver program works, and Listing 2 shows how to use PFM to control one tripod of the Stiquito robot.

#### JUST THE BEGINNING

The purpose of the Stiquito robot kit is to enable you to create a platform

Figure 2—The robot walks best on a slightly rough surface, like linen tablecloths or roughly sanded wood. Compare the metachronal wave gait (a) versus the tripod gait (b). Check out the Stiquito supplemental web site for BASIC programs used to make the robot walk in a tripod gait.

from which you can start experimentation for making the robot walk. The instructions in the book show how you can create a Stiquito that walks in a tripod gait. The circuitry and computer programs we've shown in this article enable you to control this tripod gait via a PC parallel port.

If your plans include independent control of each of the Stiquito's legs, you should modify the assembly of your robot such that you attach control wires to each leg individually. If the design of your robot includes putting something on top (e.g., a circuit that enables it to walk on its own), you should consider how you want it to walk.

If you simply want the robot to walk, a tripod gait may be sufficient. But, if you plan to put complex circuitry like a microcontroller on top, you may want the flexibility of being able to control all six legs.

James Conrad is an engineer at Ericsson Inc., and an adjunct professor at North Carolina State University. He

> has written on the topics of robotics, parallel processing, artificial intelligence, and engineering education. You may reach him at jconrad@stiquito.com.

Figure 3a—The nitinol wire will contract and stay contracted until it cools. b—To stay contracted, nitinol wire needs only 25–35% of the current needed to initially heat it. c—Pulsing current with a 25– 35% duty cycle will keep the wire contracted. Jonathan Mills is an associate professor in the Computer Science Department at Indiana University and director of Indiana University's Analog VLSI and Robotics Laboratory, which he founded in 1992. Jonathan invented the Stiquito to use in multirobot colonies and to study analog VLSI implementations of biological systems. You can reach him at stiquito@cs. indiana.edu.

#### SOFTWARE

Software for this article is available via the Circuit Cellar web site. The parts list and photos of the finished product are posted there as well.

#### REFERENCES

- J.M. Conrad and J.W. Mills, Stiquito: Advanced Experiments with a Simple and Inexpensive Robot, IEEE Computer Society Press, Los Alamitos, CA, 1997.

- J. W. Mills, Stiquito: A Small, Simple, Inexpensive Hexapod Robot. Part 1: Locomotion and Hard-wired Control, Technical Report 363a, Computer Science Department, Indiana University, Bloomington, IN, 1992.

- Stiquito information, www.computer.org/books/ stiquito; www.stiquito.com

#### SOURCE

Stiquito books IEEE Computer Society (800) 272-6657 (714) 821-8388 Fax: (714) 821-4641 www.computer.org/cspress/catalog/bp07408.htm

#### FEATURE ARTICLE

# Internet Appliance Interface

Internet appliances still aren't the most reasonable things out there. (Why pay hundreds more for a \$20 toaster?) But, Myron uses a PIC and a 2400-bps modem to make an Internet interface that leads the way to less-expensive Internet appliances. or years, we've been hearing about the promises of everything from coffee makers to lawn sprinklers being connected to the Internet for remote control and monitoring. Yet, none of these devices ever became a commercial product.

Two major roadblocks have prevented this dream from coming true the cost of connecting to the Internet and the cost of an Internet terminal. No one wants to pay an extra \$300 for a \$40 appliance, plus \$25 a month for the Internet service, just to have the ability to check on their home appliances from work.

But, things are changing in the market that could clear this roadblock forever. Cable modems are bringing continuous Internet connections into homes without the hassles of extra telephone lines and hourly billing.

Another recent change is free web access by local telephone numbers in some cities, if you can tolerate a little advertising. A dumb terminal like a coffee maker could care less how many banner ads it has to ignore. And the cost of the Internet interface is dropping to under \$50 with the introduction of systems-on-a-chip complete with TCP/IP stacks.

In this article, I show how the Internet interface can be made even cheaper and simplified to run on a \$2 PIC processor and a retired 2400-bps modem. The PIC dials and establishes a point-to-point protocol (PPP) connection with an ISP and exchanges data with remote servers. I don't have a cable modem or access to free web browsing yet, but there are many other applications that already need a small or cheap Internet interface.

Even though this project was conceived solely for the Circuit Cellar Design98 contest, it has since found use in everything from industrial controls to surveillance cameras. It's most suited for remote data collection, where the samples are stored until an alarm trigger point and then dumped to a central database through a local ISP. This has huge cost savings over leased lines.

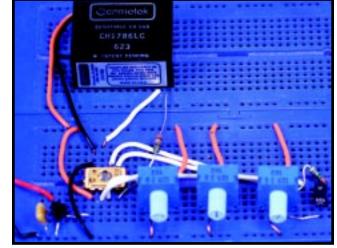

My design, shown in Photo 1, uses the PIC12C672 to emphasize how small the device can be—only eight pins and under \$2. Even with such a simple processor, I managed 2400-bps serial communications with the modem, three analog inputs, one digital output, and some of the Internet protocols.

The serial communications had to go through a software-emulated serial port (bit banging) because this device has no USART. The result was a demo Internet node with a remote-controlled red LED indicator and remote monitoring of three potentiometer settings with 8-bit resolution.

#### SIMPLE INTERNET

Packing this kind of functionality into such tiny resources required a lot of tradeoffs. I studied a ton of Internet Request for Comment (RFC) documents, the public source code to Wat-TCP and Linux TCP/IP stacks, and *TCP/IP Illustrated* Volumes I, II, and III. Then, I whittled it down to the bare essentials, making many assumptions and forfeiting universal compatibility.

Here's a summary of how I implemented the Internet protocols and a description of the software. If you want to learn more, read a book like the one in the references and download some of the Internet documentation listed in the Digging Deeper sidebar.

If you've read this far, you probably have quite an interest in TCP/IP protocols, but bear with me as I cover the basics. If it doesn't make sense to you, remember that this protocol stack is far from conventional. Try instead to focus on the flow of data instead of what software layers and state machines are missing.

I justify this reckless abandon of standards as necessary to shrink the code to the point where connections can barely be made with a majority of ISP servers. This will not endanger the standards of the Internet because these are end-user devices that perform no routing and are tweaked until they satisfy the end user. There are already inconsistencies between products from major brand names, which prevent the appliance from being able to log into some ISP servers.

Let's first look at how the Internet works and how data can cross such a maze of distant computers with varying physical connections and operating systems. Each computer gets a unique IP address, much like your mailing address. The data to be sent is broken into chunks that are stuffed in specially marked small envelopes that indicate the type of data (e.g., web page, e-mail).

Each of these goes into a mediumsized envelope, specially marked to get it to the right program on the remote computer. The type of data determines if the medium-sized envelope is a simpler UDP type or more robust TCP type. The TCP packet generates extra packets to open and close transmissions and resends packets that get lost.

The medium envelopes go into larger envelopes with source and destination Internet addresses on them. This is called the IP packet. It's like international mail; the address gets it to any destination on the Internet.

But, the Internet works more like passing notes in class. The large envelope goes in a bigger one with your friend's name on it. Your friend opens the big envelope, sees where the large envelope wants to go, and puts it into a new big one.

Your friend then passes it to another friend who is closer to the final desti-

nation, and the process repeats. The mail doesn't always take the same path and sometimes it gets lost along the way. With luck, the large envelope eventually ends up at its destination.

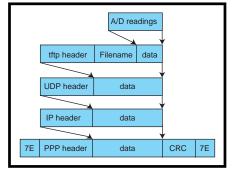

When it arrives, it is opened and the medium envelope is removed to see what program gets the data. That program then opens the little envelope to gets its data. Most OSs do this with a TCP/IP stack like WinSock. To save all the envelope handling, my algorithm puts on x-ray glasses and looks through all the layers for the data in the middle. The format of the envelopes or packets is shown in Figure 1.

There are protocols for the data following the IP header (e.g., ICMP for pinging, TCP for web browsing, and UDP for voice over Internet). You need to implement ping to test the Internet connection and send keep-alive packets to prevent the server from disconnecting. You also need a way to send data to the appliance and receive data back.

You're probably familiar with ftp for transferring files. It runs over TCP, which handles opening a high-level connection across the Internet with error detection and retransmission.

TCP has large RAM and ROM requirements to keep track of open connections and packets that have not yet been acknowledged by the remote computer. It turns out that there's another less popular file transfer protocol, called tftp, which runs over UDP. UDP is much simpler to implement than TCP because each packet is sent in response to the last one received and there is no retransmit buffer or table of connections to keep track of.

**Figure 1**—The tftp packet shows how the A/D readings are wrapped in layers of packets to get a PPP packet.

I couldn't choose tftp without client software for people to access their new appliances. With a quick search, I found several freeware, shareware, and demo tftp servers and clients for various OSs. The http links to these packages are available via the Circuit Cellar web site.

Another protocol I considered was SNMP. It is much more popular, has built in remote alarm monitoring and reporting, and lots of shareware clients, but is a little more complicated.

If you need it to be even simpler, just return data appended to pings. But then, you need to write a custom ping routine.

tftp has another advantage over ping and SNMP. It provides simple data logging of daily uploads on a central tftp server. tftp clients just have to upload files with unique filenames and they are stored on the server.

#### NEGOTIATING PPP

A modem connection to the Internet is used because it's the most common method for remote data collectors. If we go back to the envelope analogy, the Internet appliance and the ISP

Photo 1—The first prototype of the Internet Appliance uses three potentiometers for remote inputs and an LED to test remote control. The 2400-bps Cermetek modem provides a fast enough Internet connection to exchange the control packets. modem server are the close friends exchanging the big envelopes. The envelopes used in dialup connections come in two forms—SLIP and PPP. More acronyms are listed in Table 1.

I only had room for one protocol, so I chose PPP because some ISPs prevent SLIP from establishing a connection. The PPP connection can also go straight to a local server's serial port to save the cost of a modem.

PPP is a protocol to encapsulate IP packets on a serial link. On an asynchronous link (like the modem serial connection), it requires the data format to be 8 data bits with no parity.

The sample packet in Figure 1 shows that character 0x7e starts and stops a packet. All other instances of 0x7e must be changed to the two-byte sequence 0x7d 0x5e to prevent false starts. The character 0x7d becomes an escape character that means complement bit 6 in the following byte.

Any original instance of 0x7d, 0x7e, or bytes inclusively between 0x00 and 0x1f, must be changed to 0x7d followed by the original XORed with 0x20. This bit stuffing eliminates false packet breaks, false characters, and RS-232 control characters under 0x20.

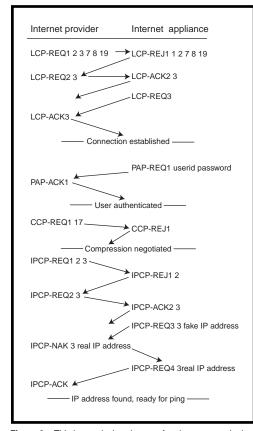

The PPP connection procedure can be broken into several phases. First, if the link is dead, carrier detect is one of the stimuli that moves us to the next phase. The link establishment phase uses LCP to detect and negotiate link options with the remote computer.

Next, the authentication phase verifies your password using PAP. Although it is not one of the phases, this is where ISPs generally configure data compression with CCP packets.

The final phase is the networklayer protocol (e.g., IP). Each protocol is configured with its protocol; IPCP in the case of IP. Of course, there's also the terminate phase to close the link.

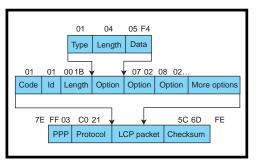

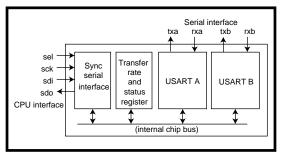

The LCP, PAP, CCP, and IPCP packets look similar and negotiate options in the same way. Only the protocol field and the meanings of the options are different. Figure 2 illustrates what an LCP packet looks like and how options are negotiated across the serial link.

Basically, the packet can request, deny, and accept options. Both sides

must issue an accept before the LCP negotiation is complete. Figure 3 depicts the packet exchanges.

Negotiation starts with one side requesting a list of options in a REQ request packet. Each option consists of a length byte, option number, and option parameters. The other side responds with an ACK if it accepts all the options. If it doesn't like an option's parameters, it responds with a NAK and a list of the options that it rejected with parameters that would be acceptable.

If required options are missing, it adds those to the rejected list in the NAK reply. If some options are not recognized or are considered nonnegotiable, the other side should respond with a REJ reply and list the bad options.

The first side resubmits updated option lists until it gets an ACK reply.

#### **Digging Deeper**

Anyone trying to build an Internet appliance will find that this article barely scratches the surface of the Internet protocols. Fortunately, the Internet is fairly well documented and, best of all, the standards are free in the form of request-for-comments documents (RFCs).

RFCs are the working notes of the Internet research and development community. RFCs can be written by anyone to introduce a new protocol, modifications, new methods, or explanations. They are often updated by later RFCs with higher numbers, so make sure you use the latest revision and refer back to updated RFCs.

You can find RFCs on several Internet sites including www.cis.ohiostate.edu/hypertext/information/rfc.html or by emailing:

To: rfc-info@ISI.EDU Subject: getting rfcs Message body: help: ways\_to\_get\_rfcs

Here are some helpful RFCs to get you started:

| RFC 768  | UDP specification                                          |

|----------|------------------------------------------------------------|

| RFC 791  | IP specification                                           |

| RFC 792  | ICMP specification, updated by RFC 950                     |

| RFC 867  | Getting time and date from the server                      |

| RFC 1055 | Serial link IP (SLIP)                                      |

| RFC 1071 | Internet checksums                                         |

| RFC 1144 | Compressing TCP/IP headers                                 |

| RFC 1157 | Simple network management protocol (SNMP)                  |

| RFC 1332 | PPP Internet protocol control protocol (IPCP)              |

| RFC 1334 | PPP authentication protocols (PAP)                         |

| RFC 1350 | tftp version 2                                             |

| RFC 1547 |                                                            |

| RFC 1570 | LCP extensions, updates RFC 1548                           |

| RFC 1624 | Internet checksum via incremental update; updates RFC 1141 |

| RFC 1661 | PPP, the protocol itself; obsoletes RFCs 1548, 1331, 1172, |

|          | 1171, 1134                                                 |

| RFC 1662 | PPP framing, the CRC checksum; obsoletes RFC 1549          |

| RFC 1663 | PPP reliable transmission                                  |

| RFC 1700 | Assigned numbers, parameters, and keywords                 |

| RFC 1962 | Compression control protocol (CCP)                         |

| RFC 1989 | PPP link quality monitoring; obsoletes RFC 1333            |

| RFC 1990 | PPP multilink protocol (LCP stuff)                         |

| RFC 1994 | PPP challenge handshake authentication protocol (CHAP)     |

| RFC 2153 | PPP vendor extensions                                      |

| RFC 2484 | LCP international extension                                |

|          |                                                            |

The other side can start negotiating its options at any time. The resulting link may have different options for each direction.

I didn't implement the terminate, code reject, protocol reject, echo, and discard packets. The terminate packets can be replaced by disconnecting the modem. The code and protocol reject packets are possibly required to connect to updated servers in the future. The echo and discard packets are for testing the serial path and can be ignored for most ISP connections.

The only LCP option that I accepted and required was number three for authentication using PAP. Authentication with PAP is as simple as sending a PAP request with a user ID and password and then waiting for an acknowledge. I had to force this option to avoid the alternative (CHAP), which appeared more complicated and required more RAM and ROM.

The MRU option was omitted because, although my receive buffer was only 49 bytes, all the packets I used were small. On top of that, I didn't have enough RAM or ROM to reconstruct fragmented packets.

My ISP wanted to negotiate the character-map option to reduce the number of characters under 0x20 that had to be bit-stuffed and sent as two bytes. They also wanted to compress the protocol, address, and control fields. Although these would have been good at the low 2400-bps bandwidth, it was not worth the extra software.

The magic-number option may be required by a few ISP servers, but I ignored it because it needed four extra bytes of RAM and a lot of ROM. There are a lot more options, and this is definitely one area where you'll need to play with the code to make it more compatible with your ISP servers.

Once the LCP options are agreed on, the PAP authorizes your user ID and password as I described. Then, the CCP compression options are negotiated. These options compress the entire serial stream and could easily use up the entire memory space by themselves. Because my packets are

| ACKacknowledgementCRCcyclic redundancy checkCHAPchallenge-handshake authentication protocolftpfile transfer protocolICMPInternet control message protocolIPInternet protocol control protocolISPInternet service providerLCPlink control protocolMRUmaximum receive unitNAKnegative acknowledgementPAPpassword authentication protocolPPPpoint-to-point protocolREQrequestREJrejectRFCrequest for commentSLIPserial line Internet protocolSNMPsimple network management protocolTCPtransmission control protocolUDPuser datagram protocolUDPuser datagram protocolUSARTuniversal synchronous asynchronous receive<br>transmitter |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

Table 1—These are the acronyms used in this article. Check the Digging

Deeper sidebar for where to find full descriptions and technical details.

tiny and traffic is low, I chose to disable them and go under the puddle-jumper option number three.

The final group of options configure the IPP settings with IPCP. I disabled the TCP/IP header-compression option to keep the software simpler and because I don't intend to transmit any TCP packets. I do, however, use this protocol to get the IP address of the Internet appliance. After this, only IP packets are sent and there is no harm in ignoring the server's rare LCP packets.

#### **IP PACKETS**

The IP packets start with a 20-byte header followed by data. The data is either an ICMP, UDP, or TCP header followed by its data. The IP header directs the data to the destination and keeps multiple data packets from arriving out of order.

The first four bits are the IP version. The next four bits are the header length, always equal to 20 in this application. The 8-bit type of service field sets the routing priority to minimize delay and cost as well as maximize throughput and reliability. Then comes the total 16-bit length of the header plus data, about 40 for most of the Internetappliance packets.

The 16-bit identification identifies each packet and is used with the following flags and fragment offset to reassemble fragmented packets. Following all that is the time-tolive byte, which sets the maximum number of hops this packet can be routed toward the destination before giving up. The next byte indicates what type of protocol is riding in the IP data.

Next, comes a 16-bit checksum of the 20-byte IP header. Be careful—this is a 16-bit one's complement checksum, not your ordinary math (described later). After that is the 32-bit source IP address and finally the 32-bit destination. You're probably used to seeing these addresses in a form like 10.97.123.67.

The easiest to understand protocol that rides the IP header is ICMP, which is used to ping Internet nodes. Named after the sonar method for locating objects, it sends out a packet and waits for a reply.

You need ICMP in this application to keep the Internet connection alive and respond to others that are looking for the health of your Internet node. The test is usually repeated several times indicating pass or fail and response time.

The ping packet is 20 bytes of IP header, then 8 bytes of ICMP header and some data to echo. The first two bytes of the ICMP header are type=8 and code=0 for the ping request. Type is 0 for the ping reply.

After that comes a 16-bit one's complement checksum of the ICMP header and echo data. Then, an identifier for multiprocessing systems and a sequence number increment each iteration.

The other protocol essential here is UDP, which is used to send data over tftp. Because of its simplicity, this protocol is used for everything from H.323 multimedia applications to SNMP network management.

Each output operation produces only one packet. Like IP headers, it can't ensure that the data gets to the destination, but it does check the data for errors.

The protocol simply takes the IP header, adds four 16-bit parameters and a string of data. The four parameters are a source-port number, destinationport number, length, and one's complement checksum.

process gets the data in a multiprocessing system. The length is redundant with data in the IP header-eight for the UDP header plus the number of data bytes. You may want to bury your own CRC checksum in important data because UDP and TCP only use an inferior checksum.

TCP is the protocol for transferring web pages and e-mail across the Internet. TCP negotiates a connection, transfers the data, does error checking, retransmits bad or missing packets, and closes the connection.

A more complex protocol has to handle a lot of special cases and keep track of lots of data. which takes more RAM and ROM than is available in the PIC. But, it would be an interesting project to see just how small TCP could be implemented in another processor.

### The port numbers identify which

EXCHANGING DATA

I already indicated how data could be transferred using the echo data on the ping command and why I chose tftp instead. This section is a look at how tftp works and how the Internet appliance uses it.

tftp is intended for bootstrapping diskless workstations, so it is small and easily fits on a ROM. Each data exchange begins with the client asking the server to read or write a file. There are five packets used to transfer the data, Read Request (RRQ), Write Request (WRQ), Data, Acknowledge (ACK), and error.

The packet is laid out as 20 bytes of IP header, 8 bytes of UDP header, and the opcode for type of packet. Opcode 1 is for RRQ and is followed by a nullterminated filename, and a null-terminated ASCII or binary transfer mode. Opcode 2 is for WRQ and it has the same format as an RRQ packet.

Opcode 3 indicates a data packet and is followed by the block number and up to 512 data bytes. Opcode 4 is for ACK and is followed by the block number being acknowledged. Opcode 5 indicates an error and is followed by the error number and a null-terminated error message.

All data packets must have 512 bytes of data except the last packet in the file. A packet length under 512 bytes indicates the end of the file. Lost packets are detected when the sender has a time-out and the last packet is resent.

Just like ftp, there is no security. Instead, the tftp server usually limits transfers to files with worldread and world-write permissions.

For this Internet appliance, you want to read three analog inputs and set one digital output. There's even a way to do both in one operation.

Reading a filename that ends with a 0 clears the output. If the filename ends with a 1, the output is set; otherwise the output is unchanged. The returned file contains the output setting and the three A/D readings in ASCII format.

Many variations of this process can be implemented. If the output was a PWM analog output, the digit in the filename can be extended to

Figure 2—The LCP packet shows how the configuration options are sent in a PPP packet. This example highlights the MRU option.

a three-digit value. The digits can be moved anywhere in the filename. The number of outputs and inputs is only limited by the transmit buffer size and maximum filename length.

The appliance can dump its data to the server by writing a file with a unique filename based on date. The server would have a directory of files logging the daily data of the appliance. The appliance doesn't need a real-time clock because the date and time can be retrieved from most Internet servers from UDP port 13 [1].

#### THE HARDWARE

I chose to implement this project in the smallest processor I could find (the 8-pin PIC12C family) to emphasize how compact the code is. In the PIC12C family, I chose the device with the most RAM and ROM (at the time), the PIC12C672. Although it only has 128 bytes of RAM, that should be enough for the variables, a small transmit buffer, and a small receive buffer.

At first I was scared that the code wouldn't fit and it would force me to a larger processor. The 2 KB of ROM turned out to be plenty and left the possibility of a more robust PPP stack, EEPROM routines, SNMP routines, and other options. If I could start over, I'd choose a processor with a USART to simplify and speed up the serial I/O.

The other main component is the modem. I had plenty of old 2400-bps modems to choose from, but I went with the Cermetek for its small size (and because there were several laying around the lab from old projects). If you're not as lucky, you should still be able to locate a 2400-bps external modem. You could add RS-232 drivers to the circuit or, even better, bury the

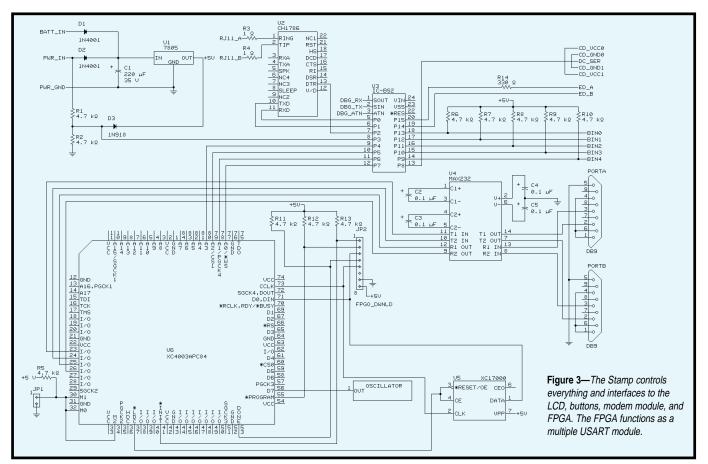

whole circuit inside the modem case. The schematic for this project is shown in Figure 4.

Open the external modem case, remove the RS-232 driver chip, attach the circuit, connect the Tx and Rx pins to the correct driver chip pins, and connect power and ground. Be sure to stay away from the high voltages on the incoming power and telephone lines.

Also, use potentiometers that fit and mount nicely on the modem case. You won't need the resettable fuses and overvoltage limit components because the modem already has them.

I used 10-k $\Omega$  potentiometers from Tocos. These are nice for breadboarding because they have through-hole leads and a nice knob for days when you can't find your pot tweaker. You can use any LED to indicate the digital output, including one already in the case if you use the modified external modem.

The circuit is quite simple so I breadboarded it instead of waiting for a PCB. You could go even smaller and make it all surface mount.

Don't worry about finding the exact components. Any 1–10-k $\Omega$  potentiometer will do, as will any normal LED. You can even omit sidactor U3 and replace the resettable fuses with 5- $\Omega$  resistors. Note that this circuit is not FCC approved and thus should not be connected directly to your local telephone service.

#### THE SOFTWARE

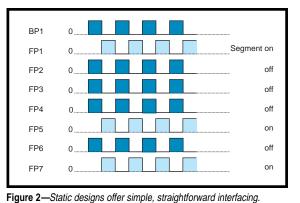

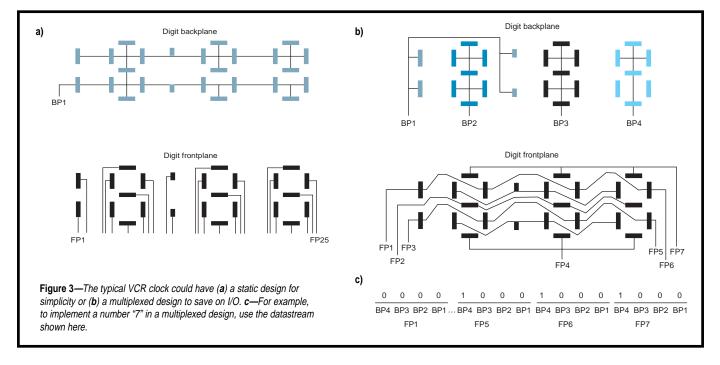

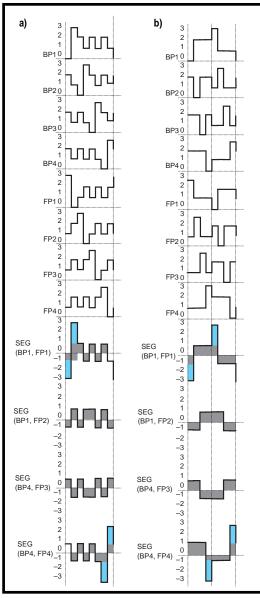

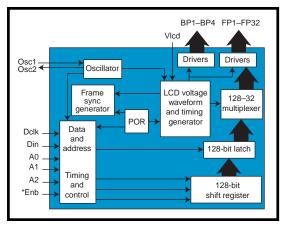

I wrote the software in C because the contest deadline was approaching. I intended to rewrite it in assembler to squeeze in some more options. After working with the AN555 serial I/O app note from Microchip, I decided that future implementations would have to have a serial port.