# REAL OF THE OFFICE OFFI

# THE MAGAZINE FOR COMPUTER APPLICATIONS #109 AUGUST 1999 DEVELOPMENT AND DEBUGGING

Designing with Virtual Components

In-Circuit Debuggers— Shorten the Cycle

**Building a USB Host Controller**

**Embedded GPS**

# **CIRCUIT CELLAR**

Double your technical pleasure each month. After you read Circuit Cellar magazine, get a second shot of engineering adrenaline with Circuit Cellar Online, hosted by ChipCenter.

# — FEATURES —

# A \$25 Web Server

Steve Freyder, David Helland, and Bruce Lightner

"See the world's smallest web server." There are no age or height restrictions but we're talking real excitement. Step right up and see how these guys put together a stand-alone web server that includes an Ethernet controller, real-time networking kernel, TCP/IP stack, and a PCB smaller than a business card.

# **Electromagnetic Radiation**

# and Severe Weather

# Richard W. Fergus

Unfortunately, not all severe storms turn out to be just a bad dream. So, if you're running toward the root cellar, you might want to bring Richard's electromagnetic radiation sensor so that you can directly monitor the severity and distance of approaching storms.

# The Art and Science of RS-485

# Bob Perrin

WWW.CHIPCENTER.COM/CIRCUTCELLAR Table of Contents for July 1999

# -COLUMNS-

# **Considering the Details Pedigree Protection: Understanding Watchdog Applications**

Bob Perrin

A motion-triggered recording of vicious canines may keep the average cat burglar off of your property, but it takes more than just the presence of a watchdog circuit to keep embedded-system failures at bay. Sit, stay, and listen while Bob explains how effective watchdog timers are implemented in hardware and software.

# **Lessons From the Trenches**

# **Logging In the '90s**

George Martin

Rest easy all you spotted owl fans, George isn't headed for the old growth forests; he's headed toward the new market for data-acquisition systems. As desktop spreadsheet and data-graphing applications become more user friendly, the market for custom data-logging systems is becoming tighter. George takes a data-acquisition module and Visual Basic, and whittles down some code to form a general-

# Testing 1, 2

Part 1: Enduring Challenges George Novacek

According to George, product testing should be more like a torture chamber than a sound check. In this series, he explains how the value of extreme test routines is more important than the cost of those routines. Before this set is over, you will understand why not running electrostatic discharge, electromagnetic immunity, or power and operational shock tests can leave you singing the blues over smoldering electronics.

Forum. Come to a complete stop and listen as he discusses the latest in embedded microprocessors and even gives some insight as to what kinds of products will be crossing our paths down the road.

# **Resource Links**

Hall Effect / Magnetoresistive (MR) Sensors Bob Paddock The 8051 Microcontroller Benjamin Day

# Test Your EQ **8** Additional Questions

2 Issue 109 August 1999

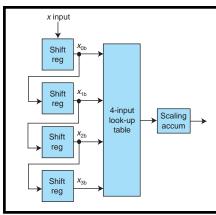

| 12                    |                                                  | n-Chip Design with Virtual Components<br>Anderson                                          |                                                               |    |  |  |

|-----------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------|----|--|--|

| 20                    |                                                  | <b>rg, In-Circuit Style</b><br>Irews and John Day                                          |                                                               |    |  |  |

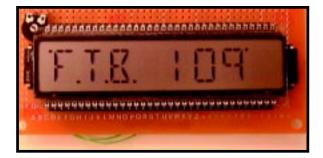

| 26                    | <b>Induction</b><br>Part 1: A<br><i>Gordon I</i> | Different VFD                                                                              |                                                               |    |  |  |

| 32                    |                                                  | mories Do Double Duty<br>Ciszewski                                                         |                                                               |    |  |  |

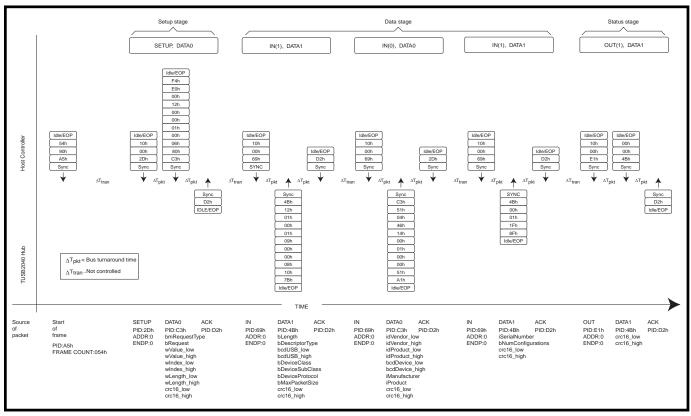

| 60                    | USB<br>Part                                      | <b>roSeries</b><br>9 Primer<br>4: Building a USB Host Controller<br>19 <i>Reuschling</i>   | <b>Task Manager</b><br>Elizabeth Laurençot                    | 6  |  |  |

| 70                    | A Fa                                             | <b>n the Bench</b><br>amiliar Face—Driving 144 LCD Segments I²C Style<br><i>Bachiochi</i>  | Persistence Pays<br>New Product News<br>edited by Harv Weiner | 8  |  |  |

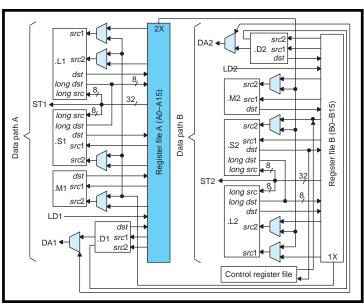

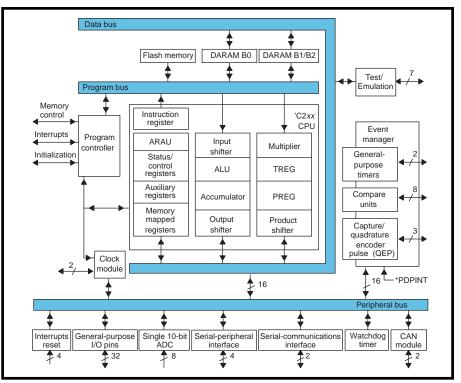

| 76                    | DSP                                              | c <b>on Update</b><br>9 Doings<br>1 <i>Cantrell</i>                                        | Reader I/O                                                    | 11 |  |  |

|                       |                                                  |                                                                                            | Test Your EQ                                                  | 82 |  |  |

|                       |                                                  |                                                                                            | Advertiser's Index<br>September Preview                       | 95 |  |  |

|                       |                                                  |                                                                                            | Priority Interrupt<br>Steve Ciarcia<br>All in the Family      | 96 |  |  |

|                       | 8 Nouvea                                         | u PC                                                                                       |                                                               |    |  |  |

| edited by Harv Weiner |                                                  |                                                                                            |                                                               |    |  |  |

|                       | Stewart                                          | the 'x86 1-MB Memory Address Limit<br>Christie                                             | V                                                             |    |  |  |

| <u>S</u> E            |                                                  | <b>Real-Time PC</b><br>Where in the World—Part 1: GPS Introduction<br>Ingo Cyliax          |                                                               |    |  |  |

| 5<br>1                |                                                  | <b>Applied PCs</b><br>Data Serving via the Internet—Part 1: Setting Up<br><i>Fred Eady</i> |                                                               |    |  |  |

# TASK MANAGER

# Persistence Pays

t's often said that showing up is half the battle. And if it gets you 50% of the way toward your goal, well, then that's great. In fact, maybe if you can get that far ahead so quickly, then you get to save up all your energy for what is, in my opinion, the hardest part—sticking it out until the end.

Whether it's developing a marketable embedded system, pulling together another magazine's worth of quality editorial, or starting a business venture, the process is pretty much the same. Design it, do it; tweak it, do it again; fiddle with it, do it some more.

The necessary ingredients are similar, too. There are the moments of inspiration, the months of headaches, and of course all those times when you can't figure out what could possibly be the problem with that one part that just won't come together the way you want it.

In this issue, with its focus on development and debugging, our concern is on not only the how-we-do-it (the trademark *Circuit Cellar* article) but on how-we-circumvent-all-the-obstacles-that-keep-us-from-doing-it. Of course, I'm not talking here about how to budget your time more effectively so you can accomplish two tasks at once or how to tell the guy in the next cubicle to turn his radio down so you can even begin to think.

But the willingness to keep plugging away on a project—that's a characteristic we all can benefit from. Think about it: how many people do you know who will start a project but never finish? And how many people do you know who, once they set their mind to a task, will never quit? (Which number is higher? Who do you admire more?)

On a rare occasion, it may be worthwhile to throw in the towel. But it's more likely that you just need a different approach. There's a big difference between quitting and changing direction.

More often than not, regardless of what you're working on, the original ideas need to be changed around a bit. Nobody starts a project with the perfect plan. And nobody executes a task perfectly from beginning to end.

But we are always encouraged to hear stories about beating the odds, overcoming setbacks, or finding the new approach that leads us more effectively to the goal. We have such articles in abundance in this issue.

First off, Thomas Anderson examines how virtual components ease the task of designing for reuse. Next, the debugger comparison presented by John Andrews and John Day helps you choose the appropriate system that enables you to get your latest project to market faster.

In our third feature, Gordon Dick tackles a variable frequency drive project that's been haunting his workbench for years. And Kenneth Ciszewski explains how flash memory can be a cost-efficient solution when you've got tough design requirements in front of you.

8 li

### elizabeth.laurencot@circuitcellar.com

# CIRCUIT CELLAR® THE MAGAZINE FOR COMPUTER APPLICATIONS

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot

TECHNICAL EDITORS Michael Palumbo Rob Walker

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Mike Baptiste Ingo Cyliax Fred Eady George Martin Bob Perrin

NEW PRODUCTS EDITOR Harv Weiner ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> ART DIRECTOR KC Zienka

GRAPHIC DESIGNER Jessica Nutt

ENGINEERING STAFF Jeff Bachiochi Ken Davidson John Gorsky

PRODUCTION STAFF James Soussounis

> PROJECT EDITOR Janice Hughes

EDITORIAL ADVISORY BOARD Ingo Cyliax Norman Jackson

David Prutchi

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

# ADVERTISING

ADVERTISING SALES MANAGER Bobbi Yush (860) 872-3064

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster (860) 875-2199

Fax: (860) 871-0411 E-mail: val.luster@circuitcellar.com

CONTACTING CIRCUIT CELLAR

SUBSCRIPTIONS: INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION: TELEPHONE: (860) 875-2199 FAX: (

FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066 AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR<sup>®</sup>, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (680) 675-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$35, all other countries \$84.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$86. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-5301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar<sup>®</sup> makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects, *Circuit Cellar<sup>®</sup>* disclaims any responsibility for the safe and proper function of readerassembled projects based upon or from plans, descriptions, or information published in *Circuit Cellar<sup>®</sup>*. Entrie contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and *Circuit Cellar* NK are registered

Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# NEW PRODUCT NEWS

**Edited by Harv Weiner**

# **MICROCONTROLLER CHIP**

The **BasicX** microcontroller was designed for rapid development of control applications using an easy-tolearn BASIC language compiler. Its controller features an on-chip multitasking OS with IEEE single-precision floating point and networking. The chip supports compiled code up to 8 MB and RAM up to 128 KB in external storage. A built-in network allows multiple BasicX processors to communicate with each other over an RS-485 multidrop connection at speeds up to 460 kbps.

BasicX also features on-chip peripherals and functions like real-time clock/calendar, timers and counters, analog comparator, watchdog timer, dual PWMs, and SPI peripheral bus. It offers high-power I/O lines and low-power sleep modes as well. BasicX has up to 32 programmable I/O pins. Routines are provided to communicate with LCD, servos, ND converters, and other typical applications.

The **BasicX development kit** (**\$99.95**) includes an RS-485 network, RS-232 COM port, in-circuit emulator/ expansion connector, 32-KB code EEPROM, and 256 bytes of on-chip RAM. The development system is connected to a PC parallel port for downloading, and a complete BasicX compiler and editor allow easy development.

BasicX is currently available in three packages: 40-pin DIP, 44-pin PLCC, and TQFP. Quantity pricing is **\$9.95** in 1000s.

NetMedia, Inc. (520) 544-4567 • Fax: (520) 544-0800 www.netmedia.com

# POINTING STICK CONTROLLER

The USAR **PixiPoint Z encoder IC** is a strain-gauge miniature joystick with *z*-axis functionality. The device is equipped with an advanced motion algorithm that provides smooth and accurate cursor control in all directions.

The IC implements the Tap (select), Double Tap (execute), and Press Hold (drag) functions in firmware with no need for special drivers. Additionally, the track stick IC enables Scroll as well as the anchor functions of Autoscroll and Panning. Panning allows for both horizontal and vertical movement.

Other features include a PS/2 port for the hot-plug connection of an additional pointing device and Clean-Stop and EasyDrag technology. USAR's proprietary CleanStop technology ensures that the cursor stops the instant the user needs it to. The EasyDrag function reduces the cursor's speed when the user drags an object on the desktop, making it simple to accurately handle the object.

The USAR PixiPoint Z IC uses a sophisticated highprecision signal-conditioning circuit. Simple to implement, the complete circuit requires few components, so it is cost effective and saves real estate.

The USAR PixiPoint Z IC is \$3 in OEM quantities.

# USAR Systems, Inc. (212) 226-2042 • Fax: (212) 226-3215 www.usar.com

# NEW PRODUCT NEWS

# SINGLE-BOARD COMPUTER

The **ipEngine-1** is a miniature SBC and associated software designed to significantly reduce the complexity required to networkenable embedded products. It incorporates a PowerPC processor, 16 MB of DRAM, and 2 MB of flash memory. It features an LCD controller, USB and Ethernet interfaces, 16,000-gate FPGA, and switching power supply onto a board the size of a credit card.

Complementing this highly integrated board is a choice of two preintegrated OS environments. The first is BSE's real-time pKernel POSIX-based network OS. The second option is an embedded version of Linux that contains the full kernel plus network utilities, the Apache Web server, and a Java Virtual Machine. Both provide full TCP/IP networking and web-server support.

Unlike traditional board-level products with fixed interfaces, the

ipEngine-1 can adapt itself to the user's hardware requirements. The external connection to the ipEngine hardware is via an FPGA-based "virtual interface" that can be configured on-the-fly to adapt to the user's needs. The FPGA can emulate a variety of bus architectures, and it can also implement peripheral functions like UARTs, PWM control, memory emulation, data capture and synthesis, and interfaces to a variety of input devices.

Developer's toolkits for both the Embedded Linux and pKernel operating-system environments contain all of the hardware and software needed for a developer to start building applications. The toolkits include an ipEngine-1 board, case and power supply, the Linux or pKernel distribution, a GNUbased PowerPC cross-compiler tool suite, sample FPGA code, documentation, and technical support. Pricing for the ipEngine-1 is **\$895** for quantities 1–4 and from **\$350 to \$795** in OEM volumes. The pKernel and Embedded Linux developer's kits have an introductory price of **\$1995**, and they include six months of maintenance support.

Bright Star Engineering, Inc. (978) 470-8738 Fax: (978) 470-8878 www.brightstareng.com

# **FUZZY-LOGIC ROBOT**

OWI has introduced the **WAO-G** robot. This limitededition device attempts to dethrone the traditional method of control and problem solving by using fuzzylogic principles. These principles exploit imprecise decisions, such as "getting close is generally OK!" By building and programming WAO-G, you can set up membership functions and learn basic fuzzy control

principles. WAO-G can draw straight lines, circles, and even words by putting a pen in its pen-holder.

WAO-G will help in understanding the new control methods being used in washing machines, vacuum cleaners, video camcorders, cameras, and automobiles. You can learn how to input data using eight kinds of membership functions. Simple operations are commanded in Direct mode, and complicated operations are

commanded in Program mode. The robot uses sensor feelers to detect its movement, and an optional interface enables the user to program the device through a PC. Three demonstration programs (Dice, Roulette, and Timer) are included for illustration.

The robot measures  $9.5'' \times 6.25'' \times 3.5''$  and is powered by three AA batteries and one 9-V battery. Power

consumption is 12.5 mA for the electronics and 600 mA for the mechanics. The unit includes 48 (max.) program steps and 16 (max.) for-next loops.

The WAO-G robot sells for **\$89.95** and is available as a kit or fully assembled.

OWI, Inc. (310) 638-4732 Fax: (310) 638-8347 www.owirobot.com

# **NEW PRODUCT NEWS**

# SINGLE-CHIP DATA LOGGER

The **DS1615 Temperature Recorder** is an integrated temperature recorder that combines a Y2K-compatible real-time clock with temperature data-logging and histogram capabilities. It is designed for applications that require temperature profiling over a given period of time.

The DS1615 can operate in a stand-alone system as a complete data logger or in an embedded system to track environmental conditions during system powerdown or minimal power periods. Its digital thermometer measures temperatures from  $-40^{\circ}$ C to  $+85^{\circ}$ C in 0.5° increments

with  $\pm 2^{\circ}$  accuracy. The data can be used in calibration, maintenance, and warranty applications. Also, the DS-1615's real-time clock and temperature sensor are available to the system.

Both standard three-wire synchronous and RS-232 interfaces with a built-in CRC generator are available. Nonvolatile memory can record 2048 consecutive

temperatures, which the user can program to start at specified times and be taken at selected rates. Alarms and interrupts can be programmed for user-determined out-of-spec conditions, including expiration dates and extreme temperatures. The separate histogram memory allows for longer term data collection and distribution analysis.

A **DS1615K evaluation kit** enables designers to program and retrieve data from the DS1615. The kit has a self-contained data-logger board, RS-232 cable, Win-

dows-driven software, source code, and documentation.

The DS1615 Temperature Recorder costs **\$5.43** in 1000-piece quantities. The DS1615K Temperature Recorder evaluation kit costs **\$75** in single quantities.

Dallas Semiconductor Corp. (972) 371-4448 Fax: (972) 371-3715 www.dalsemi.com

# **READER** I/O

# **GETTING A MOUTHFUL**

Steve's "Servings Per Issue" editorial (*Circuit Cellar* 107) generated plenty of responses with regards to the editorial direction of the magazine. Here are a few of your responses:

*Popular Science* is one of my favorite publications also and I hadn't been able to put a finger on why it seemed less satisfying now than in the past. As an instructor of electronics technology (mostly DC, AC, transistors, and digital), I use *Circuit Cellar* as a tool to introduce first-year students to the applications part of the technology with hopes that during their second year they will go beyond the textbooks with their projects.

The new-product quickies are important, but it's the complete projects with in-depth coverage that makes this magazine unique. The touchless sensor ("Look Ma, No Hands"), working with accelerometers ("XLR8R"), and the "USB Primer" Microseries are three excellent examples of what's needed in today's classrooms and labs. Don't make too many changes.

# George Shaiffer

gshaiffer@uswest.net

As a subscriber since *Circuit Cellar*'s first issue, I enjoy the in-depth articles. Even though I don't always have time to read them all, I know the meat is there in case I get really hungry. Better than the other way around, isn't it?

Last year, MIT's *Technology Review* magazine made the sort of transition that you described regarding *Popular Science*. I hate the result to the point that I no longer look forward to reading the publication.

Why is everyone trying to copy *Wired* magazine's practice of bombarding the reader with trivia? Engineering is not a trivia quiz. When I need snippets of information, there are plenty of publications and trade journals available.

If anything, I'd like to see *Circuit Cellar* articles offer more theory along with the nuts and bolts. Like many people, I learn best from a happy marriage of theory and practice. Please don't stop selling steak and offer just sizzle. Leave the glitz to the others, and keep helping us become better designers as you've been doing all along.

Phil Doucet pjdoucet@aol.com "Servings Per Issue" doesn't have a single numerical answer. I need about one hundred new ideas a week to feel satisfied. At the same time, I also have a need to learn the detail behind those ideas.

Product announcements and sound bytes don't teach much, but full-length articles do. For example, where else would I find out how to create a web-based strip recorder? Sure, I could find out where to buy one. But I derive my satisfaction from learning how to build things, not just where to buy them.

The web is great if you know what you're looking for so the needle in a haystack problem becomes trivial. The problem is that you'll never find the stapler, thread, or any of the thousands of possible substitutes for the needle.

Short paragraphs arranged in a special-interest magazine can show those alternatives, but it's not enough to present other people's products and inventions. A magazine article should have in-depth content that teaches how to build new products and how things work. It should present different approaches to a problem and point out how others have solved similar problems. A vendor has no desire to teach people how to build their products, but a magazine article can teach the underlying technology of new products and concepts, and that's something that appears nowhere else.

# Paul Hittel

phittel@microtest.com

I have been an avid reader of Steve's work for many years dating back to the *BYTE* days. I go all the way back to the 4004, 8008, and 6800 micros and have enjoyed watching and applying the changes in technology to the hardware interface world.

In my opinion, don't change anything about *Circuit Cellar*. It's the last great hope to us aging hardware junkies who rely on you and your team to help guide the way through uncharted waters. And don't let whatever happened to *BYTE* happen to *Circuit Cellar*.

James J. Aschberger jaschbrg@memphis.edu

# FEATURE ARTICLE

**Thomas Anderson**

# System-on-Chip Design with Virtual Components

Here in the Recycling Age, designing for reuse may sound like a great idea. But with increasing requirements and chip sizes, it's no easy task. Thomas explains how virtual components help suppliers get more mileage out of their SOC designs. esign reuse for semiconductor projects has evolved from an interesting concept to a requirement. Today's huge system-on-a-chip (SOC) designs routinely require millions of transistors. Silicon geometry continues to shrink and ever-larger chips are possible.

But, the enormous capacity potential of silicon presents several challenges for designers. Design methodology and EDA tools are being severely stressed by SOC projects at the same time that narrowing time-to-market requirements demand more rapid and frequent introduction of new products.

SOC projects present another problem—how to design enough logic to fill up these devices. Few companies have the expertise to design all the intellectual property (IP) needed for a true SOC, and few have enough engineering resources to complete such a massive project. Even those with the required knowledge and plentiful resources may still be unable to finish a complete chip design in time to meet accelerated market demands.

The net result: SOC projects require design reuse. Only by leveraging off

past designs can a huge chip be completed within a reasonable time. This solution usually entails reusing designs from previous generations of products and often leverages design work done by other groups in the same company.

Various forms of intercompany cross licensing and technology sharing can provide access to design technology that may be reused in new ways. Many large companies have established central organizations to promote design reuse and sharing, and to look for external IP sources.

One challenge faced by IP acquisition teams is that many designs aren't well suited for reuse. Designing with reuse in mind requires extra time and effort, and often more logic as well requirements likely to be at odds with the time-to-market goals of a product design team.

Therefore, a merchant semiconductor IP industry has arisen to provide designs that were developed specifically for reuse in a wide range of applications. These designs are backed by documentation and support similar to that provided by a semiconductor supplier.

The terms "virtual component" and "core" commonly denote reusable semiconductor IP that is offered for license as a product. The latter term is promoted extensively by the Virtual Socket Interface (VSI) Alliance, a joint effort of several hundred companies to set standards for VC design, verification, and use. In this article, I describe the major virtual component (VC) types and discuss their use in SOC designs.

# FORMS OF VC

VCs are commonly divided into three categories—hard, soft, and firm. A hard VC or hard macro is a design that is locked to a particular silicon technology. Such macros are fully placed and routed and are available in a fixed size and format.

They can be easily dropped into the floorplan for a chip in the same target technology, because the silicon technology is known, and they usually have predictable timing. However, they can't easily be mapped to another silicon vendor (e.g., a second source) or even to a different technology from the same vendor. The VC user also has little or no choice in terms of feature set modification or customization.

Hard macros are most often provided by ASIC and FPGA vendors as part of their library. Such macros are a natural extension to the basic cell library used to implement the VC user's design. Because the silicon vendor sells chips, there's no incentive to provide a VC in a more portable form that makes it easier for the customer to switch to another supplier.

Some IP vendors, especially those supplying microprocessor and DSP designs, also provide a VC in hard form. This option shows that the key elements of processors, especially data paths for arithmetic computation, are often designed at the transistor level for maximum performance.

Some processors, as well as many other kinds of VC products, are available from IP vendors in soft (or synthesizable) form. A VC described in Verilog RTL or VHDL code gives the user maximum flexibility. It can be mapped to virtually any target ASIC or FPGA technology using commercial logic synthesis tools.

The user may also be able to control the VC feature set, for example, by setting variables in the code or by running a utility that modifies the code under user control. Of course, because the user licenses the actual Verilog or VHDL source code, it can always be modified directly.

One issue with a synthesizable VC is that the precise timing is not known until the VC is mapped to a target technology. Accordingly, soft VC suppliers must synthesize to a range of representative target libraries and ensure that timing is satisfied.

The supplier may also have to supply guidelines to assist the user in laying out the chip containing the VC so that the postroute timing is still correct. Such guidelines may include recommendations for target technology, pin assignments for external I/O, floorplanning for key modules, and routing of critical paths.

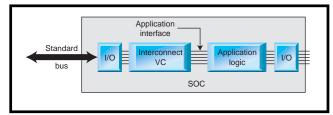

The definition of a firm VC varies widely. The term is used most commonly to refer to a soft VC accompanied by an example Figure 1—A soft VC interconnect fits between the application logic and the I/O signals. Implementation instructions generally include guidelines for connecting the interconnect to the external chip pins.

layout-level implementation, although some people refer to a VC as firm whenever it comes with layout guidelines. The term also refers to a netlistlevel VC that has been mapped by synthesis to a target technology but is not yet placed and routed.

It is possible, although difficult, to make customizations to a VC in netlist form. Synthesis tools can also provide some degree of portability to new technologies, but the range of optimizations available when synthesizing from the netlist level is more limited than from Verilog or VHDL.

# **VC FUNCTIONS**

Numerous factors can lead to a decision to license a commercial VC for inclusion in an SOC design. The expertise and resources available and the time-to-market requirements for the end product must be balanced against the expense of the VC license. Even a company with vast, expert resources may be able to produce a better product faster by leveraging external IP.

This is especially true if the VC implements a common function because little is gained by designing and optimizing such a function rather than focusing on product-differentiating features. For example, the VC may duplicate the function of existing stand-alone chips (e.g., a UART or a floppy disk controller) or implement a common arithmetic function such as a multiplier.

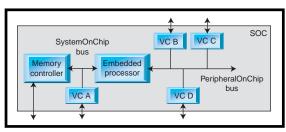

Figure 2—System-on-chip designs may contain both a system bus connect and a peripheral bus connect. Custom I/O blocks that provide functions not commercially available may also be included.

Perhaps the highest leverage is provided by a VC that implements a formal or de facto standard. Because many types of chips and end products must meet a standard, a VC that implements this standard is ideal as a commercial IP product. It's rare that an end user can add enough value with an in-house design to offset the time savings and standards expertise embodied in a well-designed VC.

The standards provided by VCs range from formal IEEE, ANSI, and IEC specifications to new technologies. Examples include communications protocols like Ethernet and ATM, computational functions such as MPEG and JPEG, parallel interconnect standards such as PCI and AGP, and serial interconnects like USB and IEEE 1394. These examples have wide applicability to many different types of SOC-based products, and the standards themselves are well enough defined to allow implementation as a VC.

A VC implementing an interconnect technology probably has the widest range of application. For example, PCI is used in diverse types of electronic products. Although it was developed as a personal computer peripheral bus, PCI has now been adopted for workstations, mainframe computers, military applications, and networking/ telecommunications systems. USB is following a similar expansion of scope beyond the PC, as it is used to connect peripherals to gaming systems, set-top boxes, and PDAs.

> The widest penetration of all may occur with 1394, which is designed to interconnect both computers and diverse consumer electronics devices. Products available today with 1394 support include video cameras, digital televisions, digital VCRs and professional audio equipment. Although it is not yet supported in mainstream PC chipsets,

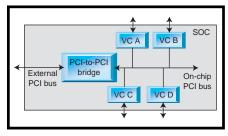

Figure 3—A multiprotocol I/O controller can be enabled using PCI as an on-chip bus. In this application, a PCIto-PCI bridge supports multiple I/O technologies using a single PCI load or slot.

many desktop and laptop computers offer 1394 support and such peripherals as disk drives and videoconferencing cameras are starting to appear.

# **USING A VIRTUAL COMPONENT**

The path for a chip designer to use a VC depends on both form and function. A hard macro can be dropped into a chip layout fairly easily, as long as the macro and chip use the same silicon technology. But, simulation and timing analysis with a hard macro is not as simple.

Generally, the VC supplier must provide separate simulation and timing models. Correlation of these models to the hard-macro implementation may be a difficult problem for the VC provider and a potential issue for the user. A VC at the netlist level has fewer problems, although the inefficiency of gate-level simulation may require the VC supplier to provide a high-level model in addition to the netlist.

A soft VC has several advantages in terms of design flow because it can usually follow the same design process as the rest of the chip. The user runs synthesis to map the RTL design to the target technology, uses static timing analysis to verify timing, lays out the chip following the supplier's guidelines, and reruns static timing analysis with back-annotated postroute delays.

The VC also has the same advantages as any RTL design in that the source code also serves as the simulation and timing model. The lack of perturbation to the user's design methodology is a key attraction for a synthesizable VC.

A VC with no requirements for connection to chip pins,

such as a fully embedded processor, is wired into the chip design like any other module. An interface VC, however, generally has some I/O signals that need to connect to external chip pins. The implementation and layout instructions for a soft interconnect VC generally include guidelines on how to connect to the pins.

As shown in Figure 1, such a VC essentially fits in between the chip pins and the user's application logic. The set of VC I/O signals to which the user connects is often referred to as the application interface.

# MULTIPLE VC APPLICATIONS

It's becoming common for an SOC design to use more than one VC. Although there may be no direct interaction between one VC and another, in other cases they may be linked on a common bus. The term "on-chip bus" (OCB) describes a formally specified bus that interconnects multiple VC blocks within a single chip.

An OCB is likely to fall into one of two categories—system or peripheral bus. A system bus connects an embedded processor or DSP with the memory controller and higher speed I/O devices. A peripheral bus connects to lower speed I/O technologies.

An interface block generally bridges these two buses, although some embedded processors directly drive both buses. In SOC designs with multiple embedded processors, the processors generally communicate over the system bus.

Figure 2 shows an SOC that has both system and peripheral OCBs. In an actual chip, the system bus might link to a 400-Mbps 1394 interconnect VC and the peripheral bus would support slower I/O technologies such as USB, RS-232, and IrDA (infrared). It's

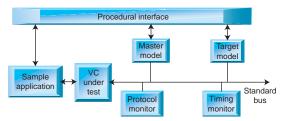

Figure 4—A verification environment provides behavioral models and test scripts to verify the functionality of the VCs. This approach can be used in full SOC verification as well as stand-alone VC verification.

also possible for the SOC designer to create custom I/O blocks that connect to an OCB to support functions not available from commercial VC sources.

It would be nice if widely adopted OCB standards existed, but this is not the case. Nearly every embedded processor has its own proprietary system bus; some have defined proprietary peripheral buses as well. This situation can make it difficult to take a VC designed for an SOC with one embedded processor and move it to a different chip. A few buses (e.g., AMBA buses for ARM processors) are supported widely enough to be considered a de facto standard in some application spaces.

One interesting option for a peripheral OCB is an on-chip version of PCI. Several popular embedded processors are available in versions that provide PCI support, and many interconnect VC families include an option for PCI support on the application interface. Using a PCI OCB also enables existing PCI-based chips to be easily transformed into macros for use in larger SOC designs in newer technologies.

The size of a PCI VC, which usually ranges from 7k to 15k gates, is not a major issue in the context of a milliongate SOC. Other objections to PCI as an OCB (e.g., its use of tristates and multiplexed address/data lines) can be addressed by using a PCI derivative.

In fact, a number of SOC designers use PCI or a derivative bus as an OCB. Figure 3 shows one interesting application, a multiprotocol I/O controller.

This design allows multiple I/O technologies (e.g., USB, 1394, and Ethernet) to be combined by using a VC with PCI for each and then using a PCI OCB to link the VCs together. A PCI-to-PCI bridge permits this wide range of I/O support while using only

> a single PCI load on the motherboard or a single PCI slot in the system.

VSI is tackling the OCB issue by defining the virtual component interface (VCI), a standard application interface for VC designs done in-house or available from commercial IP suppliers. VCI is not an OCB but a standard VC interface that enables OCB usage.

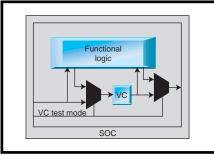

Figure 5—One test method for legacy VCs is a parallel access test process. This process uses multiplexers to bring all inputs and outputs to the external pins and plays a predefined set of test vectors.

The idea is that the SOC designer needs to develop only a bus translator from VCI to the chosen OCB. With this translator, any VCI-based block can easily be connected to a given OCB. VCI has been defined for easy translation to popular OCBs (including PCI) and translators for such buses will be available as licensable IP.

# VC VERIFICATION ISSUES

One area common to both single-VC and multiple-VC SOC designs is the need to verify and test the complete chip. The SOC design and test engineers want to leverage and build on the verification and test done for each individual VC, and accordingly they expect the VC provider to assist in this process.

As previously noted, each VC is accompanied by some sort of simulation model that enables the SOC designer to run chip-level tests that involve the VC. But, that doesn't provide any support for determining whether the VC is connected properly in the design and is operating correctly in the context of the full SOC. A VC with a miswired application interface will simulate, but the results may not be correct.

Many suppliers address this problem by providing a verification environment along with the VC itself. Such an environment provides behavioral models (usually in Verilog, VHDL, or C) that interact with the VC and a set of test scripts that use these models to verify the functionality of the VC. Figure 4 shows a sample verification environment for an interconnect VC such as PCI or 1394. Key components of this approach include:

- master model to address the VC as a target

- target model to respond to VC as a master

- sample application code to stimulate VC

- tests written as scripts of procedural calls

- monitors for protocol and timing correctness

As a stand-alone test for the VC, a verification environment lets you verify a postsynthesis netlist or a customized version of the VC to ensure that protocol and timing rules are satisfied. A simple set of test vectors performs much the same function for stand-alone VC verification, but debug is harder without monitors and readable test scripts.

One of the main advantages of the verification environment approach is that many of its components can be used in the full SOC verification in addition to the stand-alone VC verification. The master and target models can be connected to the SOC bus interface while the protocol and timing monitors can continue to be used.

It may be possible to continue to run the same test scripts on the SOC, requiring the chip designer to modify the procedural interface to stimulate the VC from the actual SOC logic rather than from the sample application.

A verification environment can be provided with any VC, whether in hard or soft form. Synthesizable-VC suppliers usually provide verification environments and hard-macro suppliers often provide some components such as bus models to aid in SOC verification.

Many of these components are useful to a designer developing a custom implementation of an interface or processor. So, it's quite common for IP providers to license a verification environment even to customers who do not license the VC itself.

# VC TEST CHALLENGES

By its nature, a VC is embedded into the SOC design by the VC user. Once a VC is inside the larger chip design, it's no longer accessible as a standalone functional block. Whatever test vectors or methods the VC supplier provides can no longer be used without special considerations to design-for-test (DFT) approaches during chip design.

The challenges of embedded VC tests depend on the nature of the VC itself. A synthesizable VC is the easiest case. The VC user runs synthesis to map the Verilog or VHDL code to the target technology, lays out the chip following the supplier's guidelines, and runs timing analysis with back-annotated postroute delays.

The result, as I noted, is that the VC follows the same design process as the rest of the chip. The same is generally true for chip test methodology, since virtually all test insertion tools run on the postsynthesis netlist. Whatever approach the VC user takes for the rest of the chip—full scan, partial scan, built-in self test (BIST), or JTAG—is usually applied to the soft VC also.

To ensure that the user has no problems, a soft-VC supplier should use a clean design style with DFT in mind. Typically, soft VC designers use simple clocking schemes, avoiding latches and gated clocks unless they are required.

For example, the USB protocol has suspend and resume commands that put a peripheral device into a minimalpower state. Some amount of clock gating is unavoidable in a USB device VC because of this requirement.

In contrast, a hard macro user is stuck with whatever test technique (if any) is built into the VC. If the VC includes full scan, partial scan, or BIST technology, it's helpful if the remainder of the chip also uses this approach. Integrating a VC scan chain into the full-chip scan chain is usually a simple matter of running scan insertion and stitching tools.

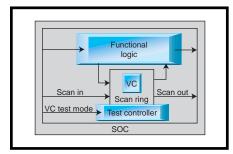

**Figure 6**—Another approach for testing legacy VC involves serial access to the virtual-component I/O signals. The legacy VC is surrounded with a JTAG-like register chain that can drive VC inputs and read VC outputs. The disadvantage of this method is that test times can be very long for complex blocks.

Sometimes the hard macro includes no internal DFT at all (often called legacy VCs because the user needs to treat them as black boxes in terms of testing). Generally, the VC supplier provides a set of test vectors, perhaps guaranteed to provide a certain level of coverage as defined by the single stuck-at fault (SSF) model. Of course, running this exact set of tests on the VC once it's embedded in a chip can be a challenge for the VC user.

When the only test method available for a legacy VC is "playing" a set of predefined test vectors, two approaches are common. The first is simply to bring all VC inputs and outputs out to external chip I/O pins using multiplexers as shown in Figure 5.

The parallel test-access process can be automated by test-insertion tools and requires only a VC test-mode pin setup prior to running functional vectors on the VC. This approach is attractive for interconnect VCs like PCI because some VC inputs and outputs will already be connected to chip I/O pins for functional reasons.

This method breaks down if there are more VC inputs and outputs than chip pins available. Staging registers may be needed to accrue each complete VC vector over several clock cycles. If the test vectors are also intended to check VC timing, inserting multiplexers into the path adds delays and may require changes to the timing vectors.

This approach doesn't work at all for analog VCs unless some sort of analog multiplexer is available. Intervening digital logic makes it impossible to apply or measure continuous analog values.

The second approach, called internal boundary scan or VC isolation, surrounds the legacy VC with a JTAGlike register chain that can drive the VC inputs and read the VC outputs. As shown in Figure 6, this setup requires some form of TAP-like test controller to run the scan chain.

Because this technique relies on serial access to the VC I/O signals, test times can be long for complex blocks like embedded microprocessors. So, IP suppliers are developing methods to test complex VCs using existing functional datapaths, including on-chip buses.

# **CORES IN FPGA DEVICES**

As I mentioned, it's common for FPGA and ASIC vendors to provide hard macros for common core functions. Traditionally, these offerings have been limited, but the increasing speed and size of FPGAs means a broader scope of core offerings.

For example, 33-MHz PCI cores are readily available, and some FPGA vendors even claim fully-compliant 66-MHz cores. Such cores require a great deal of hand-tuning during the design and layout stages so they are optimized for a particular technology.

Like their ASIC counterparts, FPGA designers may desire flexibility and portability and can therefore benefit from synthesizable designs. There's no reason that synthesizable cores can't be targeted to FPGA designs, but mapping a core to an FPGA technology does present challenges.

In general, commercial synthesis tools are less efficient at mapping to complex programmable logic blocks than to relatively simple ASIC cell libraries. The effect of routing length is usually greater for FPGAs, producing unanticipated delays on critical paths.

The design-tool flows for most FPGA vendors do not have a tight loop from layout back to synthesis. So, the synthesis process usually can't take into account useful layout information (e.g., a chip floorplan specifying the location of timing-critical blocks.

The result: less correlation between the preroute timing estimates from the synthesis tool and the accurate postroute timing results. When it comes to final chip timing, surprises are usually negative rather than positive.

Finally, the gate capacity of even the largest FPGA devices is far below that of ASICs and custom chips, which limits opportunities for multicore designs. So, on-chip buses aren't common in FPGAs.

Combinations of a few cores are possible in large programmable devices: for example, including several Ethernet cores to implement a network repeater, or pairing a PCI core and a USB host core for an adapter chip to add USB to a PC without chipset support.

# WORKS IN PROGRESS

Design reuse, including licensing of commercial IP, is key to SOC design. And a significant industry has arisen to provide a wide range of VC products. Several industry initiatives are addressing the needs of VC suppliers and users.

The IEEE Test Technology Technical Committee Embedded Core Test Study Group has also been working on VC test issues, and this has led to the proposed IEEE P1500 specification.

It's important not to minimize the issues and concerns involved in VC use. Recognizing this, two industry groups focus on the business and legal aspects of VC license and use.

Many VC suppliers are members of the RAPID trade association, which works on common VC license agreements and catalog methods. RAPID cooperates with the Virtual Component Exchange (VCX), which is developing a structure for simplified VC transactions.

The immaturity of EDA tools for VC integration and SOC design is one challenge to design reuse. Also, new suppliers may underestimate the difficulty of designing for reuse across a diverse customer base. Some VC types (e.g., interconnect cores, embedded processors) need a vertically integrated supplier that supports software and hardware.

Despite these issues, virtually every major system and semiconductor manufacturer has licensed external IP and employs internal reuse. Commercial VC products are incorporated into thousands of chip designs, and the many successful products on the market prove the value of this approach.

Thomas Anderson is director of engineering in the Semiconductor IP Group at Phoenix Technologies. He is also a member of the PCI special interest group steering committee and chairperson of the 1394 Developers' Conference. You may reach him at tom\_ anderson@phoenix.com.

# REFERENCES

T.L. Anderson, "Interconnect Solutions for Embedded Systems," *Microsoft Embedded Review*, 1 Mar. 1999.

- T.L. Anderson, "The Reality of Using Cores as Virtual Components," *Electronic Engineering*, July/Aug. 1998.

- T.L. Anderson, "Make vs. Buy: A Case for Licensing Cores," *Silicon Strategies* 1, Feb. 1998.

- T.L. Anderson and C. Stahr, "ASIC Design Flow with Synthesizable Cores," Proc. of Design, Automation and Test in Europe: User's Track, Feb. 1998.

- T.L. Anderson, "Thoughts on Core Integration and Test," Int'l Test Conference 1997 Proc., Nov. 1997.

- T.L. Anderson, "CPLD Cores can Speed Design Turnaround," *EE Times*, 21 Apr. 1997.

- T.L. Anderson, "The Challenge of Verifying a Synthesizable Core," *Computer Design*, July 1996.

- T.L. Anderson, "RTL Cores Promote Design Flexibility," *EE Times*, 15 May 1996.

- S. Brandt, "Building a Multimedia Video Conferencing Chip with a Synthesizable PCI Core," *Integrated System Design*, Sept. 1997.

- S. Davidmann, "Using Pre-designed Components in PCI Bus-based Systems," *Electronic Engineering*, May 1996.

- IEEE, "A D&T Roundtable: Testing Embedded Cores," *IEEE Design and Test of Computers*, May/June 1997.

- IEEE P1500 Standards for Embedded Core Test, grouper.ieee.org/ groups/1500.

- A. Oldham, M. Knecht, and T.L. Anderson, "IP Cores in AGP Busbased Systems," *Electronic Product Design*, May 1998.

# SOURCES

VSI Alliance (408) 256-8800 Fax: (408) 356-9018 www.vsi.org

# RAPID

(408) 341-8966 www.rapid.org

Virtual Component Exchange +44 1506 404100 Fax: +44 1506 404104 www.vcx.org

# FEATURE ARTICLE

John Andrews & John Day

# Debugging, In-Circuit Style

Looking for a tool that will shorten the development and debug cycle? Ask John, or John, and they'll point you to incircuit debuggers. Listen in as they compare emulators, simulators, and other tools that can reduce your time to market. hanks to the amazing Turing machine, embeddedsystem designers can create an endless array of different end products using the same simple, finite instruction set of their choice.

This freedom means that a generic tool that supports the features of a specific processor can address the needs of developing a flight-control system or a toaster oven. For those of us in the business of creating flight-control systems, toaster ovens, or any other electronic systems, this is a good thing.

Arguably, the strongest advantage of basing a design on programmable digital logic, as opposed to fixed function digital or analog devices, is the ability to bring these generic tools to bear. There's no doubt that, in practice, every system must be brought to life in a test bed as unique as itself. Thanks to the theoretical advances of people like Mr. Turing and the practical experience of generations since, a lot of the work has been done for us.

The standard tools of the trade for embedded-system design range from purely software monitors and simulators to custom silicon for in-circuit emulation. The main objective of all these tools is to provide a window into the operation of the software inside the embedded processor.

A software simulator is independent of the hardware under development, and an in-circuit emulator seamlessly replaces the target processor for maximum hardware control. Other tools range between these approaches in cost and performance. The benefit of a tool in shortening the product development cycle increases with its level of integration with the end-product hardware.

# SIMULATION

Many embedded processors are supported with software instruction simulators. Some of these only simulate instruction execution. Most offer breakpoints, which allow fast execution until a specified instruction is executed. Many also offer trace capability, which shows the instruction-execution history.

All simulators provide read and write access to the internal processor registers and control of simulated program execution. Although instruction simulation is useful for algorithm development, embedded systems (by their nature) require access to peripherals, including I/O ports, timers, ADCs, PWMs, and so on.

More advanced simulators (such as MPLAB-SIM) implement many peripheral features including I/O pins, interrupts, as well as status and control registers. These peripheral simulators help you verify timing and basic peripheral operation.

They provide various stimulus inputs, ranging from push buttons connected to I/O pin inputs, to logic vector I/O input stimulus files, to regular clock inputs and internal register value injection for simulating A/D conversion data or serial communication input. Many embedded systems can effectively be debugged using the proper peripheral stimulus.

Simulators also offer you the lowest cost development environment. In many cases, they're available free of charge. Peripheral implementations help debug peripheral interaction and are more effective than instructionset-only simulators. Unfortunately, it's rather difficult to simulate all possible external conditions, so many real-time systems are tough to debug with simulation only. Also, simulators typically run at speeds  $100-1000 \times$  slower than the actual processor, so long timeout delays must be eliminated when simulating.

# **IN-CIRCUIT EMULATION**

In-circuit emulators (ICEs) offer real-time code execution, full peripheral implementation, and breakpoint capability. High-end emulators also offer real-time trace buffers, and some will timestamp instruction execution for code profiling. Emulators plug into your target system in place of the embedded processor.

ICEs are sometimes implemented with a special ASIC or FPGA that imitates the core processor code execution and peripherals. Although this approach can yield an emulator that supports more processor families, behavioral differences between the actual device and emulator can crop up.

Some manufacturers have lockstepped the behavior of emulated and real processors by designing special bond-out emulation devices. These devices use the same circuit technology as the target processor and provide the emulator access to the internal data registers, program memory, and peripherals. This process is accomplished by eliminating the processor's internal program memory and providing this memory through emulation RAM. The microcontroller firmware is downloaded into the emulation RAM, and the bond-out processor executes these instructions while using the same data registers and peripherals as the target processor. The I/Os of the bond-out silicon are made available on a socket that's plugged into the system under development instead of the target processor being emulated.

Emulator systems provide the most direct connection between the user interface host and the system being developed. Direct I/O and peripheral access is provided by the bond-out chip. The emulation RAM supports fast "single button" code revision downloads.

State-of-the-art emulators provide additional aids, like multilevel conditional breakpoints and instruction trace including date- and timestamp. For example, the MPLAB-ICE 2000 trace analyzer permits system debugging without halting the processor.

With development tools, like anything else, you get what you pay for. The complexity of trace buffers, highspeed emulation RAM, and specialty bond-out chips make emulators more expensive.

Some manufacturers also place restrictions on maximum processor clock speed or operating voltage. Cabling to the system can be clumsy or cause RF interference. Also, a system with close mechanical constraints may have difficulty accommodating the emulator probe instead of the target processor.

# DEBUGGING WITHOUT AN EMULATION SYSTEM

The price/performance gap between the emulation's total replacement of the target processor and interpreting hints from a software simulator leaves a lot of room for intermediate solutions. The simulator provides the basic user interface required for embedded hardware cross-development (breakpoints, single-stepping, watching variables, etc.). Its main limitation is its complete isolation from the target hardware.

If you're simulating, you're also probably using the burn-and-learn method of run-time firmware development. First, you burn a chip with a device programmer, then plug it into the target hardware and watch the system crash. After much head scratching and reproducing the symptoms in simulation, you change the source code, rebuild the executable, and burn another chip.

Without access to internal processor RAM, the program counter, and quick program-memory downloads and breakpoints, this debugging method can be inefficient, slow, and tedious. Routines can be added to dump vital debugging information to a serial port for display on a terminal. I/O pins can be toggled to indicate program flow.

Obviously, if more symptoms are provided by the target system as it runs, you can make more logical changes to the source code. Otherwise, it's frustrating to wonder why certain things are happening when you use this method.

| Feature                                          | Burn and<br>learn | Software simulation | In-circuit simulation         | In-circuit<br>emulator | In-circuit<br>debugger                              |

|--------------------------------------------------|-------------------|---------------------|-------------------------------|------------------------|-----------------------------------------------------|

| Real-time execution                              | Yes               | No                  | No                            | Yes                    | Yes                                                 |

| Low cost                                         | Yes/free          | Yes/low/free        | Yes/low                       | No/high                | Yes/low                                             |

| Full device peripheral implementation            | Yes               | No/limited          | Yes/limited                   | Yes                    | Yes                                                 |

| Automatic download<br>of new program             | No                | Yes                 | Yes                           | Yes                    | Yes                                                 |

| No loss of target device I/O pins when debugging | Yes               | Yes/sometimes       | Yes/sometimes                 | Yes                    | No                                                  |

| View and modify RAM<br>and peripherals           | No                | Yes                 | Yes/limited                   | Yes                    | Yes                                                 |

| Resources needed to support debugging            | None              | None                | Serial port,<br>some I/O pins | None                   | Two or less I/O,<br>minimal program<br>and data RAM |

| Simple connectivity of<br>debugger to target     | None              | None                | No/complex                    | No/complex             | Yes                                                 |

| Real-time trace buffer                           | None              | No/limited          | No/limited                    | Yes                    | No                                                  |

| Single-stepping                                  | None              | Yes                 | Yes                           | Yes                    | Yes                                                 |

| Hardware breakpoints                             | None              | Yes/unlimited       | Yes/limited                   | Yes/unlimited          | Yes/one                                             |

Table 1—Choose the appropriate development tool by comparing the features and tradeoffs of the various options available.

# **IN-CIRCUIT SIMULATORS**

When simulating code where branches are conditional on the state of an input pin or other hardware condition, a simulator needs to know that state from the target hardware. Usually, you can manually provide this information in the form of simulator stimulus. If the simulator can ask the target hardware for the stimulus directly, it takes one step away from being software-only and enables a certain amount of hardware debug.

This approach is taken by the SIM-ICE development tool for the PIC16C5*x* 8-bit microcontroller family. SIMICE integrates the capability of the MPLAB-SIM simulator with a communication module that acts as the target processor.

The module stimulates the simulation directly from the target processor's digital input pins and enables the simulator to set binary values on the output pins. This compromise gets the simulator one step closer to the hardware and overcomes the expense of an emulator.

If a well-developed software simulator exists, providing it with a means of gathering stimulus, via communication with target hardware, makes it more valuable. But, there are a few hurdles that SIMICE doesn't overcome.

It runs at the speed of a simulator so it can't set and clear output pins fast enough to implement timing-critical features like a software UART. It also doesn't support the more complex peripheral features (e.g., ADCs, PWMs) of higher integration microcontrollers.

# **RUN-TIME MONITORS**

One important feature present with in-circuit simulators is a communication channel between the host development system and the target hardware.

Once this channel exists, the next logical step takes execution of the target code out of the host system's simulator and cuts it loose on its native target hardware. This multiplexed execution of code under development and communication of debug information with a cross-development host is referred to as a run-time monitor.

Such tools typically consume something like a UART in the target hardware to provide the communication. The host can then issue commands to the target processor so it performs debug functions like setting or reading memory contents.

Some code-execution control is also possible. Software breakpoints are implemented by inserting GOTO instructions in locations where you want code execution to vector to the monitor and provide control and data to you. If the

Careful comparison of the wide variety of development tools available today is the best way to figure out how to get your product to market in a timely fashion.

features of an existing host-system simulation tool can provide the user interface, then existing technology may be leveraged into greater functionality.

Software breakpoints can be built in at compile time. Other features, such as hooking into a periodic timer interrupt to copy data from the target to the host, can also be included when building the executable. These techniques don't require writing to program memory at runtime, so they can be used with burnand-learn debug using OTP devices.

It's amazing that the time spent waiting for windowed devices to UV erase didn't get included in "crash, erase, and burn." If changes are being made quickly and only a few devices are available, the erasing can be the most time consuming. So, monitors that can be written quickly and without a UV erase cycle are often found in systems with RAM or flash program memory.

The routines that transfer debug data to the host or download a new executable (i.e., the monitor code) occupy a certain amount of program memory on the target. They also require data memory and consume some of the target processor's bandwidth in addition to the UART or other communication device.

The bandwidth consumption is largely mitigated by the fact that most

of this overhead occurs when target code execution is not in progress. Uploading data values to a watch window while servicing a software breakpoint or downloading a new target code revision both occur when the target code isn't running.

A run-time monitor is a great step forward from simulating in isolation from the target hardware. But because it's a purely software tool running on the target processor, there are some limitations on how much control it can get over program execution. Adding a few simple support features in the silicon of the target processor can turn a software monitor into a system with all the basic features of an emulator.

# **IN-CIRCUIT DEBUGGERS**

The widespread advent of reprogrammable flash program memory has made in-circuit debugger tools practical for single-chip embedded microcontrollers. In-circuit debuggers enable the embedded processor to self-emulate.

It's hard to describe a debugger's capabilities and tradeoffs of a debugger without referring to a example. So, let's take a look at MPLAB-ICD, which is based on the PIC16F877 8-bit flash memory microcontrollers and can be used to develop various PIC16Cxx controllers. It's also a programmer for the flash PIC16F87x family.

MPLAB-ICD uses the in-circuit debugging capability built into the PIC-16F87*x*. This feature, along with the in-circuit serial programming (ICSP) protocol, offers in-circuit flash programming and debugging from the GUI of MPLAB'S IDE.

You can develop and debug source code by watching variables, singlestepping, and setting breakpoints. Running at full speed enables you to test hardware in real time.

The in-circuit debugger consists of three basic components—the ICD module, ICD header, and ICD demo board. Your serial port connects the MPLAB software environment to the ICD module. When instructed by MP-LAB, this module programs and issues debug commands to the target '16F87x using the ICSP protocol, which is communicated via a 9" six-conductor cable using a modular plug and jack. A modular jack can be designed into a target circuit board to support direct connection to the ICD module or the ICD header can be used to plug into a DIP socket. The ICD header contains a target '16F877, a modular jack to connect to the ICD module, and provides 40and 28-pin male DIP headers to plug into a target circuit board.

You can plug the ICD into custom hardware or use the included ICD demo board, which provides 40- and 28-pin DIP sockets that accept a '16F87*x* device or the ICD header. The board also offers LEDs, DIP switches, an analog potentiometer, and prototyping area. Even if your hardware isn't available, PICmicro prototype development and evaluation of the MPLAB-ICD are feasible with this board.

# **RUN-TIME OPERATION**

The debug kernel is downloaded along with the target firmware via the ICSP interface. A nonmaskable interrupt vectors execution to the kernel when the program counter equals a preselected hardware breakpoint address, after a single step, or when a halt command is received from the host.

As with all interrupts, this interrupt pushes the return address onto the stack. On reset, the breakpoint register is set equal to the reset vector, so the kernel is entered immediately when the device comes out of any reset.

The ICD module issues a reset to the target '16F877 immediately after a download. So, after a download, the kernel is entered and control is passed to MPLAB running on the host.

You can then command the target processor as you choose. All RAM registers including the PC and other special-function registers can be modified or interrogated. You can singlestep, set a breakpoint, animate, and start or stop full-speed execution.

Once started, a halt of program execution causes the PC address prior to kernel entry to be stored, which enables MPLAB to display (in source code) where execution halted. When

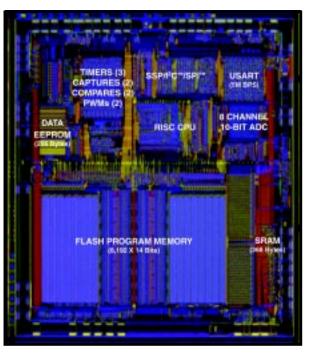

Photo 1—The Si area that implements the ICD feature is very small compared to the major peripherals labeled in this die photo of the PIC16F877.

you command the target host to run again, the kernel executes a return from interrupt instruction and execution continues at the address that pops off the hardware stack.

# SILICON REQUIREMENTS

The breakpoint address register and comparator, along with some logic to single-step and recognize asynchronous commands from the host, make up most of what's needed in silicon. The ICSP interface is in place to support programming and doesn't constitute an additional silicon requirement.

When this channel is used for incircuit debug, these I/O pins may not be used for other run-time functions. Photo 1 shows the device's major functional blocks. The ICD uses very little Si area because it connects the existing features of the ICSP interface and ICE support with only a little extra logic.

# **RUN-TIME REQUIREMENTS**

Besides the I/O pins of the ICSP interface, the ICD consumes several other processor resources. The debugger kernel must reside and execute in the target processor, so it consumes a small amount of what's available:

- $\bullet$  ~256 words of program memory

- ~10 bytes of general-purpose RAM

- one level of hardware subroutine stack

- two general-purpose I/O pins

The processor bandwidth considerations are the same as those for a run-time monitor. All debugging processing is done at a time when target code isn't running anyway (e.g., between single steps or after hitting a breakpoint).

We're fortunate that the days of hand-assembling source code and keying it into a bootloader are long gone. Make sure the development tool you choose has full source-level debugging and all the other modern creature comforts. Table 1 summarizes the important features of emulators, simulators, and incircuit debuggers.

With basic run-time features of single step, hardware breakpoint, full-speed execution, and full access to all RAM and peripherals, an incircuit debugger is a reasonable alternative to in-circuit emulators.

A five-wire cable can give a clear window into the device code execution and peripheral state. Such tools may shorten your development cycle and get your product to market sooner.

John Andrews has more than 15 years of experience as an embedded system hardware and software design engineer. He is currently a principal field applications engineer at Microchip. You may reach him at john.andrews@ microchip.com.

Also a principal field applications engineer, John Day has worked for Microchip for six years and was previously senior hardware design engineer for Digital Equipment Corporation's Alpha Workstations Group. You may reach him at john.day@microchip.com.

# SOURCE

**MPLAB-SIM/-ICE/-ICD** Microchip Technology, Inc. (888) 628-6247 (480) 786-7200 Fax: (480) 899-9210 www.microchip.com

# FEATURE ARTICLE

**Gordon Dick**

# Induction Motors

# Part 1: A Different VFD

If at first your variable frequency drive project doesn't succeed.... Fueled with the desire to make a VFD project work and armed with an embedded controller, Gordon charged through the setbacks and reached his objective at last. Here's how. everal years ago, I started a variable frequency drive (VFD) project. The circuit came from an applications book and it produced a variable frequency squarewave whose amplitude also varied to keep the voltage-to-frequency ratio constant.

To get the variable amplitude, I built a variable supply that used a phase-controlled SCR bridge feeding an LC filter. The high-voltage electrolytic for the filter was quite expensive and the inductor was made from a microwave oven transformer rewound. The squarewave was produced by connecting the motor to a power FET bridge supplied from the variableamplitude supply.

I have no doubt that the circuit would have eventu-

Photo 1—Here's the complete system. The wirewrap board contains the 'HC11 and the SA828, and the speed knob is the red pot in the corner. The IRPT-1059C is mounted to the vertical heatsink. The motor is a ½-hp 1725-rpm unit and the isolation transformer is a 10-kVA unit—big and heavy. ally worked, but during the prototyping I managed to blow all four devices in the bridge drive section twice. I can't remember my exact mistakes, but the frustration and anger are still fairly vivid in my mind.

After the second blowout, the project sat on my bench for a long time and was eventually dismantled to make way for something else. It always bothered me that I let that project beat me.

The project I'm going to describe here is also a VFD, but it's implemented in quite a different way. An embedded controller is a significant component to this project, which was not the case the first time around.

That makes this project more difficult in some ways (there's all that code to create, debug, and test) but it certainly makes it more powerful. If you want to add a feature, just create the code and reblast the EPROM.

I believe I've vindicated myself. I eventually did get a VFD project to work, albeit many years later. And, in many ways, this VFD is superior to the one I first tried to build.

# **CURRENT STATE OF VFD**

Many semiconductor manufacturers produce complete lines of power modules suitable for driving induction motors, and modules capable of driving motors in the 20- to 50-hp range are available. IGBTs are the usual power devices used in a power-module drive bridge.

A power module only gives you the muscle; there's still quite a bit of circuitry required before you have a motordrive unit. For example, there's the drive circuits for the IGBTs as well as the circuitry to monitor the motor-

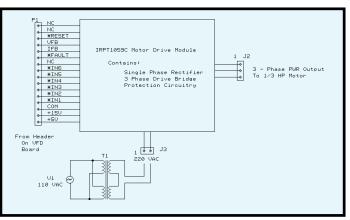

drive current, voltage, and temperature. International Rectifier produces a reasonably priced motor-drive module for three-phase motors up to 1 hp (they make modules for larger motors, too).

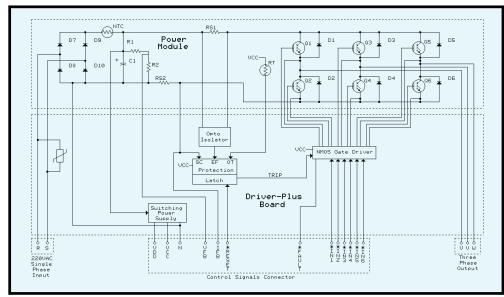

The IRPT1059C PowerIR-Train does everything I mentioned above and also has the rectifier/filter unit to produce the inverter supply voltage. The functions contained in the IRPT1059C are shown in Figure 1. In Photo 1, the green PCB with two large black electrolytics standing on the board mounted to a vertical heatsink is the IRPT1059C.

There may be other folks

that make PWM waveform generators, but I came across Mitel first, and after they sent me evaluation samples, I had no need to look for others. Certainly, another device may have features that make it more attractive in a particular application, but the Mitel SA828 has an impressive list of features:

- MOTEL interface that enables it to be used with most micros

- wide power frequency range

- 12-bit speed control accuracy

- carrier frequency selectable to 24 kHz

- sinusoidal waveform data stored in internal ROM

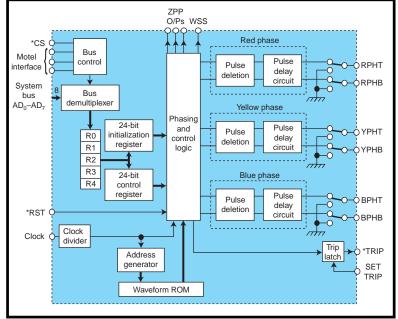

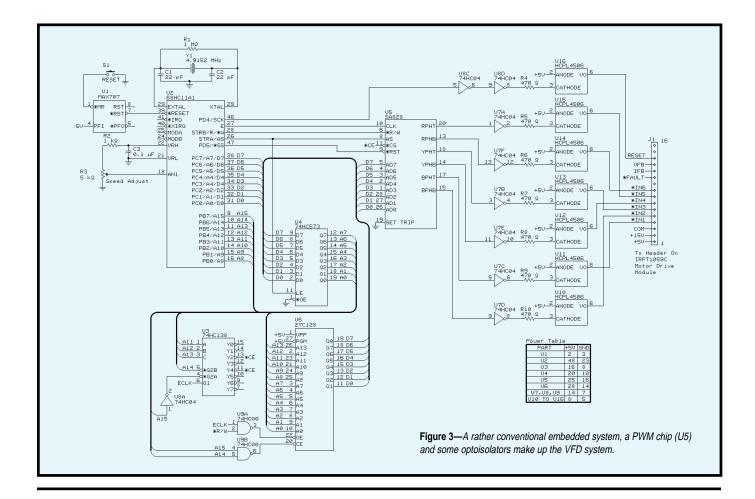

The block diagram of the SA828 is shown in Figure 2. From the programmer's perspective, there are five registers to be written to. Unfortunately, like many micro peripherals, this device is write-only.

# PROGRAMMING THE SA828 BLOCK

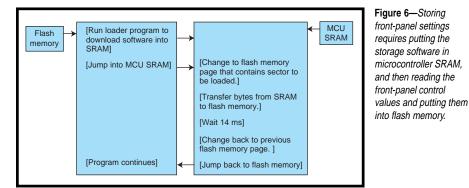

There are two 24-bit registers that need to be written to 8 bits at a time to use the SA828. One of the registers receives initialization data and the other receives operating data.