# CERTIFICATIONS

## #110 SEPTEMBER 1999 EMBEDDED APPLICATIONS

Implementing Voice Recognition

**Sprucing Up HCS-II**

PIC18Cxxx— A New Micro Poised for Action

Inside SmartMedia, the Latest in Memory Cards

CIRCUIT CELLAR

# CIRCUIT CELLAR

Double your technical pleasure each month. After you read Circuit Cellar magazine, get a second shot of engineering adrenaline with Circuit Cellar Online, hosted by ChipCenter.

#### **— FEATURES —**

#### Looking Through the Internet—A Prototype **Security System**

Skylar Lei, Jim Haslett, and Michael Smith If you've ever arrived somewhere and wondered, "What happened here?" you might want to look into this design team's low-cost remote video system. Whether it's your company's remote site or your cabin by the lake, their Internet-based system can help you keep an eye on things.

#### **Testing 1, 2**

#### Part 2—Standards: Prepping Your Prototype

George Novacek

Just when you think your prototype is ready to take on anything, it's thrown into the environmental chamber and exposed to more conditions than you ever imagined. George walks you through the standards that help equip you for the test.

#### **Out of Your Hands—A PC Interface for Hand-held Devices**

Kock Kin Ko

Data in a hand-held device can be better processed once uploaded to a PC, so Ko takes some WWW.CIRCUITCELLAR.COM/ONLINE of the information from "Electric Vehicle Performance Analyzer" (Circuit Cellar 110) and shows us how easy it is to use C Virtual Instrument to build a PC interface for hand-held products.

#### **Resource Links**

• IrDA TCP/IP for Embedded Systems Benjamin Day

Noise/Linear Feedback Shift Register/Chaos Pointers to Standards and Like Organizations Bob Paddock

**Test Your EQ**

**8** Additional Questions

#### - COLUMNS -

#### **Considering the Details**

#### Mixed-Logic Notation—A Tool for Concise Expression Bob Perrin

In these days of VHDL and Verilog, universities may be short-changing students by not teaching them how to schematically communicate digital logic. Get out your notebooks as Bob explains how important mixedlogic notation is and how easy it is to learn and use.

#### **Lessons from the Trenches** Working With a Little EE

George Martin

When it comes to data-logging projects, it's important to be able to store data and settings, even when the power cycles off. Electrically erasable memory offers a solution. This month, George shows how to interface with an electrically erasable device to support your data logger's requirements.

#### Silicon Update Online **Expo Musings**

Tom Cantrell

With the embedded PC market changing so rapidly, it's tough to keep on top of it. Tom gives us a hand by highlighting some of the notable advancements on display Table of Contents for August 1999

CONNECT YOUR PIC TO THE INTERNET

NTERNET

PIC<sup>®</sup> 29 NOW, GETTING CONNECTED TO THE **INTERNET CAN EARN YOU CASH** www.circuitcellar.com/pic2000

| 12 | 12 Talking Back—Adding Speech to Embedded Applications<br>Rodger Richey                       |                                                                                                                 |                                                                                 |     |  |

|----|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|--|

| 18 |                                                                                               |                                                                                                                 |                                                                                 |     |  |

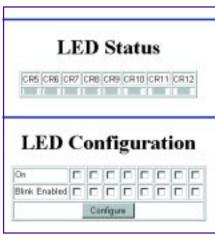

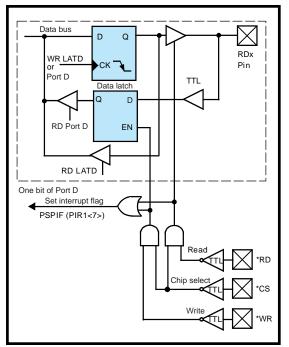

| 28 | <b>Embedded Living</b><br>Expanding the HCS-II—Making Network Modules<br><i>Mike Baptiste</i> |                                                                                                                 |                                                                                 |     |  |

| 36 | <b>D</b> Internet Control<br>Jacob Apkarian                                                   |                                                                                                                 |                                                                                 |     |  |

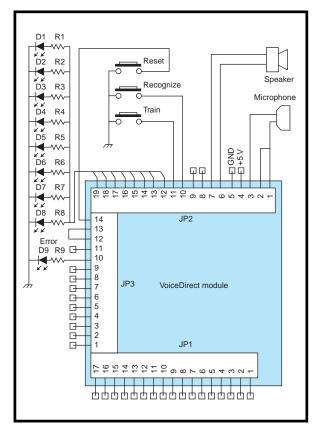

| 62 | 2 Taking Orders—A Speech-Recognition Module<br>John Iovine                                    |                                                                                                                 |                                                                                 |     |  |

| 68 | 68 Induction Motors<br>Part 2: Working with Output<br>Gordon Dick                             |                                                                                                                 |                                                                                 |     |  |

| 76 | *                                                                                             | <b>MicroSeries</b><br>Rolling Your Own Microprocessor<br>The Design and Debug Process<br><i>Monte Dalrymple</i> | Task Manager<br>Elizabeth Laurençot<br>On the Home<br>(Automation) Front        | 6   |  |

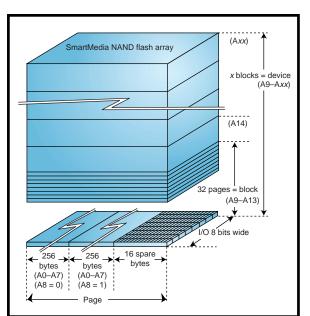

| 80 |                                                                                               | <b>From the Bench</b><br>Get SmartMedia—What's It All About?<br><i>Jeff Bachiochi</i>                           | New Product News<br>edited by Harv Weiner                                       | 8   |  |

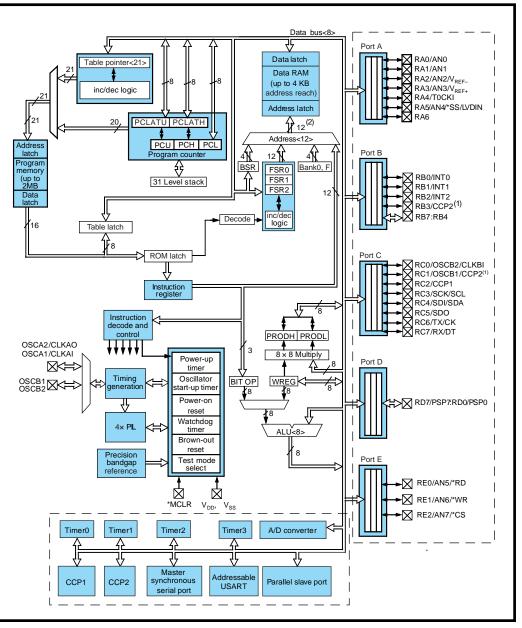

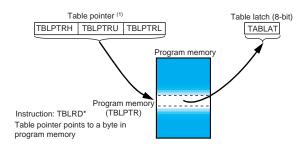

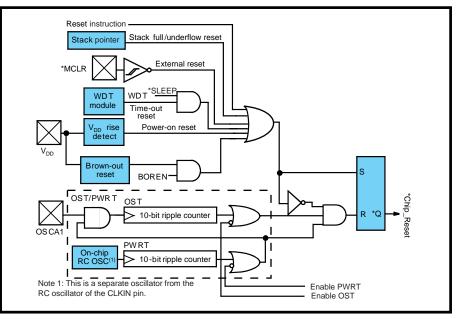

| 84 | <b>*</b>                                                                                      | <b>Silicon Update</b><br>PIC Up the Pace<br><i>Tom Cantrell</i>                                                 | Reader I/O                                                                      | 11  |  |

|    |                                                                                               |                                                                                                                 | Test Your EQ                                                                    | 89  |  |

|    |                                                                                               |                                                                                                                 | Advertiser's Index<br>October Preview                                           | 103 |  |

|    | S                                                                                             | SUFT                                                                                                            | Priority Interrupt<br>Steve Ciarcia<br>A Heavy Experience<br>in List Management | 104 |  |

|    |                                                                                               | ouveau PC<br>lited by Harv Weiner                                                                               | <b>' 70</b>                                                                     |     |  |

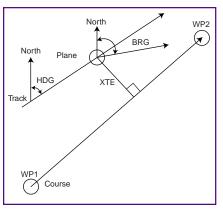

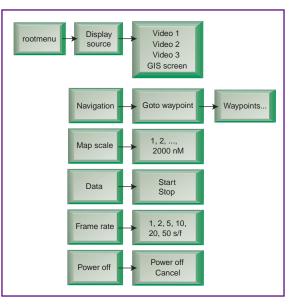

|    | 50 RP                                                                                         | C Real-Time PC<br>Where in the World<br>Part 2: Data Collection in Flight<br>Ingo Cyliax                        | . ( )                                                                           |     |  |

|    | 57 AP                                                                                         | C <b>Applied PCs</b><br>Data Serving via the Internet<br>Part 2: Forms<br><i>Fred Eady</i>                      |                                                                                 |     |  |

## TASK MANAGER

### On the Home (Automation) Front

t's easily one of the most popular Circuit Cellar newsgroups. Focused on the HCS-II, the home automation system developed by Steve, Ken Davidson & Co. in the early '90s, the cci.hcs2 news-

group is a hotbed of advice and information on this popular system.

I wonder what the draw is. Is it the ability to get advice from people in the know? Is it the atmosphere of online camaraderie? Or is it just that people like to relate their own experiences?

For years, the HCS and HCS-II have served as a source of Circuit Cellar articles because people have wanted to share their stories. For example, one author, John Morley, has told us about his solid-state barometer, a wind direction and speed monitor, as well as an automatic lawn sprinkler controller (check your bookshelves [or back-issues CD-ROMs] for Circuit Cellar 63, 68 & 80).

It's been more than features, though. In fact, HCS introduced our first MicroSeries column in 1996 ("Applying the HCS II," Circuit Cellar 77 & 78), when two of its creators described how they'd taken the system further. Ken started us off in Part 1 with a look at simulated activity (e.g., "smart" automatic lighting), and the following month, Steve got us interested in how he built a weather station using Micromint's Answer MAN network module.

More specifically, Steve got Mike Baptiste interested. According to Mike, he has always enjoyed learning about electronics and home automation, but Steve's article tipped the scales. Now he just had to do something about it.

Although he has been a significant contributor to the discussions on the cci.hcs2 newsgroup for a long time now, and although we've been able to hear about how things have gone in Mike's own HCS-II installation, we haven't been privy to all the in-depth stories. There just isn't the opportunity or inclination to type everything out in a newsgroup situation. As you may know, it's more of a back-and-forth Q&A experience.

In other words, what hasn't been seen on the cci.hcs2 newsgroup yet is the kind of in-depth information presented in Mike's new Embedded Living column. Every other month, he will be bringing us the whats, the whys, and more importantly, the hows of implementing home automation. To begin the column, this month, Mike relates how he made his own network modules.

Mike's column reaffirms Circuit Cellar's commitment to home-automation coverage. As you probably well know, Circuit Cellar is by engineers, for engineers-in other words, by the readers, for the readers. If you decide to implement some new part of your home automation system and want to tell us how you did it, do get in touch (editor@circuitcellar.com). The welcome mat is always out.

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Elizabeth Laurençot

**TECHNICAL EDITORS** Michael Palumbo Rob Walker

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Mike Baptiste George Martin Ingo Cyliax Bob Perrin Fred Eady

NEW PRODUCTS EDITOR Harv Weiner

PROJECT EDITOR Janice Hughes

ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> CUSTOMER SERVICE Elaine Johnston

> > ART DIRECTOR KC Zienka

**GRAPHIC DESIGNER** Jessica Nutt

**ENGINEERING STAFF** Jeff Bachiochi Ken Davidson John Gorsky

EDITORIAL ADVISORY BOARD Ingo Cyliax Norman Jackson

David Prutchi

Cover photograph Ron Meadows-Meadows Marketing PRINTED IN THE UNITED STATES

#### ADVERTISING

ADVERTISING SALES MANAGER Bobbi Yush (860) 872-3064 ADVERTISING COORDINATOR Fax: (860) 871-0411

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

E-mail: val.luster@circuitcellar.com

Valerie Luster (860) 875-2199

ADVERTISING CLERK

Sally Collins

CONTACTING CIRCUIT CELLAR

#### SUBSCRIPTIONS: INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION: TELEPHONE: (860) 875-2199

FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066 AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article. ARTICLE FILES: ftp.circuitcellar.com

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR®, THE COMPUTER APPLICATIONS JOURNAL (ISSN 0896-8985) is published monthly by Circuit Cellar Incomporated 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751, Periodical rates paid at Vernon, CT and additional offices One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA. MasterCard, international postal money order, or check drawn on U.S. bank Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-assembled projects. Circuit Cellar® disclaims any responsibility for the safe and proper function of readerassembled projects based upon or from plans, descriptions, or information published in Circuit Cellar® Entire contents copyright © 1999 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered

trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# **NEW PRODUCT NEWS**

**Edited by Harv Weiner**

#### WIRELESS RADIO MODEMS

The **MT and MS Radio Modems** are designed for data transmission in a local environment (e.g., a factory). Their range is typically ¾ mi. (line of sight) with a standard stubby antenna. Real-time, commercial, and industrial applications include data collection, industrial scales, crane control, computer cable replacement, and manufacturing systems (PLCs).

The modems operate in point-to-point, network, or multidrop (RS-422/-485) mode. Point-to-point mode replicates the use of an RS-232 "extension cord," and network mode allows the connection of up to 99 remote radios with a single network controller. Multidrop is a drop-in replacement for the dual twisted pair used with many manufacturers' multidrop protocols.

MT and MS radios operate in the UHF narrow band (450–470 MHz). FCC site licensing enforces interference-free use. Transmit/receive frequency stability is better than ±5 ppm. Transmitter output power is typically 120 mW. Receiver sensitivity is 0.5- $\mu$ VdB/12-dB SINAD or better. Operating temperature range is from -30°C to +60°C.

Modems are available in portable and fixed mounted radios. The portable version's built-in batteries provide over 8 h operating time. Higher gain antennas are available to extend range or overcome unusual obstructions.

Pricing starts at **\$895** for a point-to-point radio.

Monicor Electronic Corp. (954) 979-1907 • Fax: (954) 979-2611 www.monicor.com

#### SPEECH-RECOGNITION CHIP

The **RSC-364** is a complete speech-recognition system-on-a-chip for consumer electronic products and telephony applications. The system uses Sensory Speech 5.0 technology. With the RSC-364, a complete highaccuracy speech-recognition system can be built for less than \$5.

Sensory Speech 5.0 technology, as implemented in the RSC-364, includes new noise-immune algorithms, new speech technologies, and significantly improved recognition accuracy. Current algorithms deliver accuracy rates of greater than 97% for speaker-independent recognition and greater than 99% for speaker-dependent recognition in various noise environments.

Sensory Speech 5.0 features Fast Digit Recognition, providing speaker-adaptive recognition for consecutivedigit dialing applications, where accuracy requirements per digit must be above 99.5%. Sensory's 5.0 algorithms reduce response time to under 290 ms with a 32-word speaker-dependent vocabulary.

The RSC-364 has a 4-MIPS microcontroller, audio preamplifier, ADCs and DACs, watchdog timer, 64 KB of ROM, and 2.5 KB of RAM. The 8-bit microcontroller provides programming flexibility while supporting a complete suite of speech and audio technologies including speech recognition, speech and music synthesis, speaker verification, and audio record and playback. The RSC-364 permits on-chip storage of speaker-dependent or -independent vocabularies.

The device sells for under **\$5** in quantities of 100,000.

#### Sensory, Inc. (408) 744-9000 Fax: (408) 744-1299 www.sensoryinc.com

# **NEW PRODUCT NEWS**

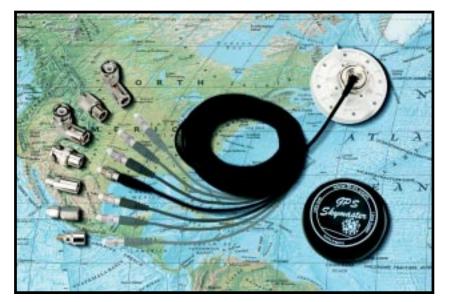

#### **GPS ANTENNA**

The **Skymaster** permanent-mount GPS antenna integrates a high-performance (26-dB gain) GPS patch antenna with a state-of-the-art, lownoise amplifier. It is packaged into a low-profile, extremely compact, fully sealed enclosure that is available in either black or white.

With its universal FME connector, Skymaster can easily attach to one of seven popular connectors: SMA, SMB, TNC, BNC, MCX, right-angle TNC, or right-angle BNC. A bulkhead mount with threaded nut, as well as an ample 5-m detachable cable, allows for quick and easy mounting.

Skymaster is 100% waterproof

and designed to perform in hostile environments. This antenna features an operating temperature range of -30°C to +85°C in addition to strong bulkhead mounting. Skymaster is priced at **\$99**. Tri-M Systems,Inc. (604) 527-1100 Fax: (604) 527-1110 www.tri-m.com

# **NEW PRODUCT NEWS**

#### DIGITAL SOUND BOARD

The **DM3000A Digital Sound Board** is Windows WAV compatible and can play back up to 32 sound segments stored in its onboard EPROM chip. Sound files can be created by using any digital audio authoring system, as long as they are in the WAV format. As well, 8-bit mono PCM sampling at 11, 22.05, and 44.1 kHz is supported.

The board provides the cleanest sound possible because the sound file is used directly for programming, without going through any extra digitization steps. Applications for the sound board include message repeaters, talking displays/exhibits, and amusement game sound effects.

Sound playback is activated by either a dry contact closure (e.g., a push-button switch or a relay) or a logic pulse from a microcontroller. The built-in power amplifier can deliver 5-W output directly to a speaker, or a line-level output can be obtained to drive an external power amplifier. The unit is totally selfcontained on a  $3.7'' \times 5.6''$  circuit board and requires only a single 12–24-VDC power supply.

The DM3000A is priced at \$78 in single quantity.

Eletech Electronics, Inc. (626) 333-6394 Fax: (626) 333-6494 www.eletech.com

# **READER I/O**

#### **BULLS-EYE**

Now you've gone and done it! The July issue takes the cake! I love robotics and you have ensured that I will keep subscribing to *Circuit Cellar*. The magazine is interesting and provides a variety of real-world projects and covers areas that other magazines rarely touch. I subscribe to all the major electronics magazines and all of them serve a useful purpose, but *Circuit Cellar* piques my interest every month.

Promise me (and the rest of us) more articles on robotics and the circuits used to interface them with the real world. "Electronic Odor Perception" by Silvio Tresoldi (*Circuit Cellar* 108) is outstanding and really helped me in my efforts to learn, develop, and have fun with mobile robots.

Would it be too much to ask for some articles dealing with software that controls robots? For example, some information on using encoders and how to actually make them work or how to use compilers and C/C++ to create hex files to be downloaded to microcontrollers.

If I continue to see issues like this, you will have a reader for life! Thank you for not forgetting the robotics crowd. Keep up the fine articles.

#### **David Jackson**

Pomona, California

#### FORGOT ONE

"Embedded OSs for Internet Appliances" by David Brooks in *Circuit Cellar* 107 was an extremely informative analysis of the Internetappliance market. However, the discussion of available operating systems for embedded devices excluded one.

A company called e.Digital has developed a flash-memory file management system called the MicroOS. This file management system implements a small footprint in a digital device and it provides scalable functionality for editing and file management. The MicroOS is particularly suitable for applications involving dictation, voice, image, video and CD quality music.

MicroOS manages voice/video/data by means of compression. The maximum effectiveness of the OS is most noticeable when functioning with flash memory. Its architecture uses optimizable C code to manipulate the compressed data in flash memory. The MicroOS is an architecture-independent OS, which means it can recognize and play a range of secure audio formats while reducing product development time. The MicroOS features a reduced chip count resulting in lower cost and power requirements for digital-device OEMs. For more information, visit www.edig.com.

#### James LaBoda

jimee11@hotmail.com

#### SETTING THINGS STRAIGHT

Editor's note: A special thanks to Richard Johnson and Dale Yarker who pointed out some errors in Figure 2 of the "Low-Cost Software Bell-202 Modem" article (Circuit Cellar 107).

[1] The TX signal is shorted to the RING signal. [2] In the "RS-232 Transceiver" section, Q2 has its emitter and collector reversed. The emitter should connect to +5V. [3] Pin 2 of P1 connects to Q2's collector (after Q2 is corrected) and not at the diode as shown.

Richard also suggested hooking up a large cap (22  $\mu$ F) from the junction of R29 and D5 to ground to help the circuit's performance.

Dale commented that if the device won't go off-hook, the polarity of the line probably reversed somewhere between the telco and J3. To correct the problem, simply reverse the green and red wires. Other ways of making the hook switch insensitive to polarity would increase the parts count too much.

The updated code, an app note that includes a corrected schematic, and some information about licensing the DTMF code is now posted on the Circuit Cellar web site.

Editor's note: Although there was no mention in the "Turn the Page" article (Circuit Cellar 108) that code would be made available, the software for Ingo's pager project is now available for download via the Circuit Cellar web site.

Editor's note: In "Astronomical Issues" (Circuit Cellar 108), Ingo mentioned a "freely available PCB layout program," but the URL was left out of the Sources section at the end of the article. Go to ftp.linuxppc.org/linuxppc/users/ harry/PCB/ to download the software.

# Talking Back

## FEATURE ARTICLE

#### **Rodger Richey**

## Adding Speech to Embedded Applications

Training embedded apps to process speech may be as easy as finding the right 8-bit micro. Don't let what Rodger has to say about using an ADPCM algorithm and PWM output to generate speech go in one ear and out the other. he ultimate form of feedback from a product is through speech. A product that reacts to stimuli with a verbal response is more likely to grab your attention than one without the capability.

In most cases, adding speech recording and playback requires extra processor bandwidth or an additional device such as a DSP or specialized audio processor. The cost, complexity, or lack of additional bandwidth, however, can prevent the speech features from being integrated into the product.

Now, if the words "8-bit microcontroller" were mentioned with respect to speech, some might chuckle to themselves, others might break into a fit of uncontrollable laughter, but certainly all would read on. Yes, it's true: a simplified Adaptive Differential Pulse Code Modulation (ADPCM) algorithm can be implemented on an 8-bit micro.

In this article, I explain the tradeoffs between bit rate and quality that are important in determining if you can use an 8-bit controller in the product. I also present the details of the origin as well as features of the ADPCM algorithm. Finally, I cover methods of integrating the microcontroller into the application as a speech encoder/ decoder peripheral or as a complete speech-processing subsystem.

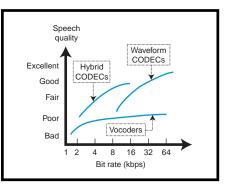

#### **BIT RATE VS. QUALITY**

When choosing a speech processor, you must first determine the desired quality of the speech reproduction. A speech-processing system attempts to balance the quality of the reconstructed speech with the bit rate of the encoding/decoding. In most cases, speech quality degrades as the bit rate drops.

The search for a happy medium between bit rate and quality has filled volumes. A high bit rate, high-quality speech processor implies a sophisticated algorithm that is computationally intensive with long encoding/decoding delays (i.e., requires the use of a DSP or special audio processor device).

This would also imply that an 8-bit microcontroller is not a solution for all applications but can provide reasonably good quality at medium-to-low bit rates. These tradeoffs between bit rate, quality, and system complexity can be summarized by the following questions:

- What level of speech degradation can be tolerated?

- What is the highest bit rate a system can tolerate (in terms of bandwidth)?

- What are the limitations on operating frequency, printed circuit board area, and power consumption?

- How much can you afford to spend on the speech subsystem?

Unfortunately, one answer can't satisfy all these questions. However, cost seems to drive most decisions.

Cost is the main factor behind bit rate. Lower bit rates are desirable because they lower operating bandwidth as well as memory storage requirements. It also means less mem-

Figure 1—A designer must make tradeoffs between bit rate and quality of reconstructed speech. After defining these two parameters, the selection of a speech coding algorithm can be made.

ory to store, a fixed amount of speech, and lower cost. Figure 1 shows a graph of speech quality versus bit rate.

A typical system might sample speech with a 12-bit ADC at a rate of 8 kHz, which is more than sufficient to preserve signal quality. At this rate (i.e., 96 kbps), 1 min. of storage requires 720 KB.

To transmit the information over a communications channel requires something higher than 96 kbps to permit supplemental information (e.g., startof-frame indicators, channel number). These requirements are beyond the scope of most applications and can be reduced by using speech coding.

Speech-coding techniques for reducing the bit rate fall into two categories. The first method is waveform coding.

There is a higher probability of a speech signal taking a small value rather than a large value. So, a speech processor can reduce the bit rate by quantizing the smaller samples with finer step sizes and the large samples with coarse step sizes.

The bit rate can be reduced further by using an inherent characteristic of speech—there is a high correlation between consecutive speech samples. Rather than encode the speech signal itself, the difference between consecutive samples can be encoded. This relatively simple method is repeated on each sample with little overhead from one sample to the next. An example of a waveform algorithm is ADPCM.

The other way to reduce bit rate is to analyze the speech signal according to a model of the vocal tract. The speech remains relatively constant over short intervals, and a set of parameters (e.g., pitch and amplitude) can define that interval of speech. These parameters are then stored or transferred over the communication channel.

This technique requires significant processing on the incoming signal as well as memory to store and analyze the speech interval. Examples of this type of processor (called a vocoder or hybrid coder) are linear predictive coding (LPC) or code-excited linear predictive coding (CELP).

| Coder<br>name | Algorithm<br>type | Bit rate       | MOS              |

|---------------|-------------------|----------------|------------------|

| G.711         | log PCM           | 64             | 4.3              |

| G.721         | ADPCM             | 32             | 4.1              |

| G.723         | CELP              | 5.6 & 6.4      | 3.9              |

| G.726         | ADPCM             | 16, 24, 32, 40 | -, 3.7, 3.9, 3.9 |

| G.727         | ADPCM             | 16, 24, 32, 40 | -, 3.7, 3.9, 3.9 |

| G.728         | Low delay CELP    | 16             | 4.0              |

| FS 1015       | LPC-10            | 2.4            | 2.3              |

| FS 1016       | CELP/MELP         | 4.8/3.2        | 2.4/3.5          |

| GSM           | RPE-LTP           | 13             | 3.5              |

| —             | MBE               | 4.8            | 3.7              |

**Table 1**—To help reduce the decision-making process, designers should rely on speech coder test results such as MOS, DAM, or SNR. Typically, the lower bit rate algorithms are significantly more complex than the higher bit rate ones.

Quality is difficult to define or even measure. The goal of a measurement is to completely describe the quality of a speech processor in a single number. This measurement should be reliable across all measurement platforms as well as speech algorithms.

Unfortunately, however, measurements are broken up into subjective and objective. Subjective tests measure how a listener perceives the speech. Objective tests compare the original speech against the reconstructed output and make measurements based on signal-to-noise ratio (SNR).

The goal of a subjective test is to represent a listener's personal opinions about the reconstructed speech in a single number. The listener evaluates speech segments based on the intelligibility or signal degradations (e.g., nasal, muffled, hissing, buzzing). Several subjective tests exist such as diagnostic rhyme test (DRT), mean opinion score (MOS), and diagnostic acceptability measure. Table 1 shows

the MOS score and bit rate for some common speech processors.

As I said, objective testing usually involves SNR measurements.

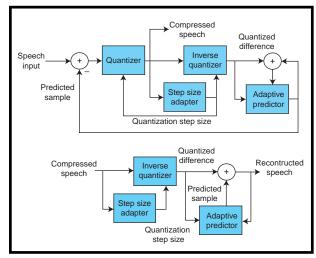

Figure 2—Because the decoder block is embedded in the encoder, the ADPCM algorithm does not need to send or store any additional side information with the compressed data. SNR is a measurement of how closely the reconstructed speech follows the original signal. The signal is broken up into smaller segments, and the SNR is measured. All the SNR measurements are averaged together to get an overall SNR measurement for the speech signal.

Although this measurement is sensitive to variations in gain and delay, it can't account for the prop-

erties of the human ear. The input to the speech processor is usually a sine wave or narrow-band noise waveform to maintain a repeatable test for all systems.

Because determining the quality of the speech processor is not as easy as picking the best number, both kinds of tests should be used to identify the best processor for your application. The best method may be to sit and listen to the outputs of the speech processor and simply select the one you like the best. After all, quality is not a measured parameter but rather a listener-perceived parameter.

#### WHAT IS ADPCM?

ADPCM is a waveform coding technique that attempts to code signals without any knowledge about how the signal was created. This implies that a waveform coder can be applied to other forms of data besides speech (e.g., video). In general, these coders are simple, with bit rates above

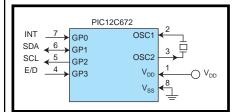

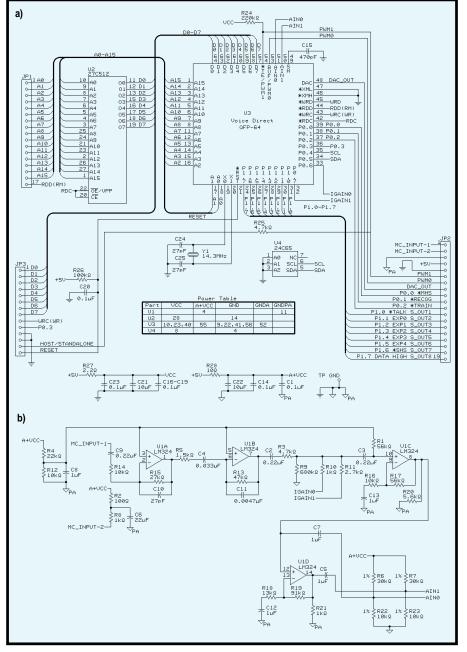

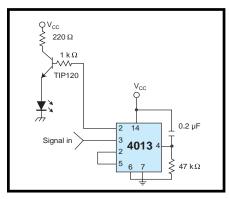

**Figure 3**—The PIC12C672 provides the smallest solution for a serial coder peripheral. In addition to the *I*<sup>2</sup>C signals SDA and SCL, this device features an interrupt and encode/decode select signals.

16 kbps. Anything lower degrades the reconstructed speech.

ADPCM is based on two principles of speech. Because there is a high correlation between consecutive speech samples, a relatively simple algorithm could be used to predict what the next sample might be, based on previous samples.

When the predicted sample was compared to the real sample, it was found that the resulting error signal had a lower variance than the original speech samples and could therefore be quantized with fewer bits. It was also found that no side information about the predictor would have to be sent if the predictor was based on the quantized samples rather than on the incoming speech signal.

The result was differential pulsecode modulation, formerly named ITU-T G.721. Further studies showed that if the predictor and quantizer were made to be adaptive (i.e., that smaller samples are quantized using smaller steps and larger samples with larger steps), the reconstructed speech more closely matched the original speech.

This adaptation helps the speech processor handle changes in the incoming speech signal more effectively. Thus the creation of ADPCM standardized to be ITU-T G.726 and G.727. Figure 2 shows a diagram of the encoder and decoder portions of ADPCM. Note that both the encoder and decoder share the same quantizer and predictor.

Most DSP manufacturers can show some type of speech algorithm that has been implemented for their architecture. Very few 8-bit microcontroller manufacturers can say the same, due to the horsepower required to implement the speech coding algorithms.

The ADPCM algorithm discussed in this article was developed by the

now defunct Interactive Multimedia Association (IMA) based on an Intel DVI variation of the standard G.726. Normally, this algorithm is quite rigorous in the computation category, but the IMA version reduces the floatingpoint math and complex mathematical functions to simple arithmetic and table lookups.

A 16-bit 2's complement speech sample is converted into a 4-bit AD-PCM code. The algorithm uses about 600 words of program memory and 13 bytes of data memory. Almost any 8-bit microcontroller can implement this algorithm, thanks to the small amount of resources required.

The code available for this article gives the complete ADPCM encode and decode routines written for use in Microchip's assembler (MPASM). The missing piece to the source code is that before each message is recorded or played, all the registers (PrevSampleL, PrevSampleH, and PrevIndex) must be cleared.

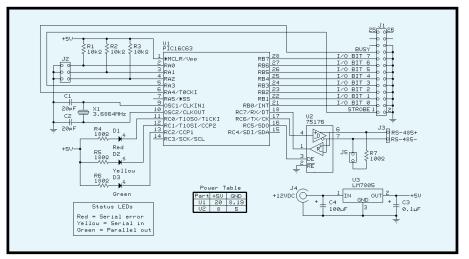

#### PERIPHERAL SPEECH CODER

A simple encoder/decoder peripheral can be implemented around a PIC12C672 or a '16C556A. The first thing to consider is the communication interface between the PIC and the main processor.

Lower end micros don't have any type of serial or parallel peripherals but they can be easily implemented in firmware. The complete code shows routines that can perform I<sup>2</sup>C, SPI, and RS-232 communications with a host processor, and Figure 3 shows a

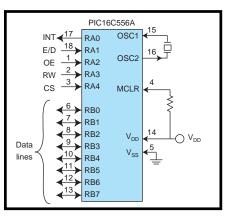

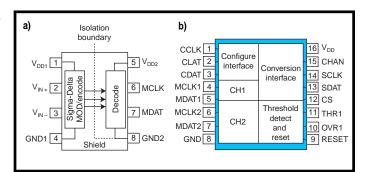

Figure 4—The PIC16C556A provides a cost-effective parallel-interface solution to a speech coder peripheral. In addition to the standard parallel interface signals, it provides an interrupt and encode/decode select signals.

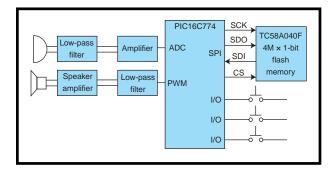

Figure 5—For those applications requiring a complete speechprocessing subsystem, the PIC16C774 with integrated 12-bit ADC, SPI, and 10-bit PWM provides the most integrated solution.

block diagram for an I<sup>2</sup>C implementation on a PIC12C672.

Because the microcontroller implements the serial interface in firmware, the application must ensure a good handshaking method to keep the micro from overflowing. A parallel interface routine is much easier to develop than the serial protocols, and Figure 4 shows an example of the parallel interface to a PIC16C556A.

The master I<sup>2</sup>C routine uses approximately 77 words of program memory and 5 bytes of data memory. MPASM must be used to assemble this file.

One consideration when designing a system based around this routine is the transfer rate. If the PIC is the master of the interface, then the transfer rate is solely determined by the clock source to the microcontroller. If the PIC is a slave on the interface, then the transfer rate depends on the clock source as well as the firmware overhead to sample the incoming data.

The SPI slave routine uses approximately 16 words of program memory and 2 bytes of data memory. The same consideration concerning clock rate applies to this routine as well. Because of the overhead of sampling the SDI pin, the maximum clock frequency for the SPI slave is at least 18 instruction cycles, where one instruction cycle is the oscillator frequency divided by four.

The RS-232 routine uses approximately 54 words of program memory and 3 bytes of data memory. Although you should check to make sure that the micro has plenty of overhead, the transfer rate of RS-232 is usually much less than the PIC's oscillator frequency.

This routine only requires the user to define the oscillator frequency and the transfer rate. Several equations allow MPASM to calculate the necessary delays for bit times. After the communication protocol is chosen, you have to put all the pieces together. First, you need to implement some type of data request from the main processor to the micro (for master) or from the PIC to the main processor (for slave).

The micro must control the flow of data to/from the main processor because the communication interface is implemented in firmware, not hardware. Otherwise, data may be lost. For a slave implementation, a single I/O line from the PIC connected to an external interrupt pin on the host processor easily accomplishes this.

The other important piece of information is the type of operation to be performed: encode or decode. This step can be accomplished two ways. First, a unique command from the host processor to the microcontroller can set the operation to follow. The host processor then initiates an encode or decode sequence by sending the command for encode or decode.

For an encode sequence, the host sends two 16-bit, 2's complement samples to the PIC. The PIC then responds with two 4-bit ADPCM codes packed into one byte. A decode sequence reverses the order. One byte of ADPCM codes is sent to the PIC, which responds with two 16-bit, 2's complement samples.

The second method is to use an I/O line from the host to the PIC to indicate an encode operation (I/O pin pulled low) or a decode operation (I/O pin pulled high). Note that encode and decode operations should not be mixed together.

All of the data to encode or decode should be sent consecutively to the micro. Once all of the data is processed, the host processor can change the type of operation to be performed. This requirement is due to the fact that the ADPCM algorithm processes the next data based on previous data. Anytime the operation is switched, the encoder or decoder is initialized to a cleared state.

One other consideration is the selection of clock source to drive the PIC. The PIC's oscillator structure is flexible so either an external clock from the host processor or a local oscillator can be connected to it.

If your application has one system clock that drives all devices on the board, this same signal can be driven into the oscillator input on the PIC. Otherwise, a standard oscillator circuit can be used to provide the clock signal.

#### SPEECH SUBSYTEM

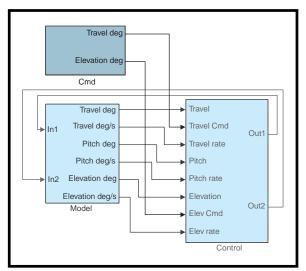

You can also use a PIC as a complete speech-processing subsystem. The PIC16C77*x* devices are ideal for this because of the 12-bit ADC and 10-bit PWM peripherals. The new PIC-18C*xxx* architecture can implement stereo record and playback at an 8-kHz sample rate because of its optimized instruction set, architecture, and 40-MHz operation.

The PIC can communicate to the host processor via any serial interface or even a simple keypad that implements play, record, next message, and previous message. Figure 5 shows a simplified block diagram of the speech subsystem based on a PIC16C77*x*.

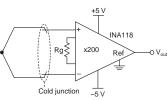

The microphone input must be both filtered and amplified before entering the microcontroller. This input might be designed in two stages.

First, an amplifier stage with some limited automatic gain control provides between 40 and 60 dB of gain. The filter stage might be a fourth-order filter centered at 4 kHz for an 8-kHz sample rate. The PIC samples the incoming signal at 8 kHz and compresses the 12-bit sample down to four bits.

The memory size is determined by the amount of record time desired. At 8 kHz, the system requires 4 kbps of storage (8000 samples/s  $\times$  4 bits/sample). Therefore, 1 min. of record time requires 240 KB.

An ideal match for this type of system is the Toshiba TC58A040F  $4M \times 1$  NAND flash-memory device.

It stores approximately 131 s of speech at an 8-kHz sample rate and uses SPI as the communications interface.

You now have a choice to make on the speech output circuit. Although a DAC makes sense in some applications, the PIC's onboard 10-bit PWM peripheral can also be used to lower cost without giving up quality.

Admittedly, the DAC has better quality, but with the right filtering, the PWM module can provide good results. This filter can be a fourthorder filter centered at 4 kHz (and can be a copy of the input filter).

The final circuit—the speaker amplifier—is extremely application dependent. You may want to drive a speaker or a set of headphones. Many companies, like National Semiconductor and TI, make amplifiers specifically for driving speakers or headphones.

#### TALK ABOUT POTENTIAL

Although some applications need high bit rate and high-quality speech algorithms, most can use one like mine. Don't underestimate the power of an 8-bit micro. Given the right device, the medium bit-rate algorithms can be implemented successfully without a DSP or specialized audio device.

Improvements to the 8-bit architecture, operating speed, instruction set, and memory sizes have allowed the migration of low-end DSP applications to the 8-bit world. If you've never used a PWM module to generate speech, try it. You might be surprised.

Rodger Richey has worked for Microchip for more than four years in principal engineer and senior applications engineer positions. You may reach him at rodger.richey@microchip.com.

#### SOFTWARE

The software for this article may be downloaded via the *Circuit Cellar* web site.

#### REFERENCES

N.S. Jayant and P. Noll, *Digital Coding of Waveforms, Principles and Applications to Speech and Video*, Prentice Hall, Englewood Cliffs, NJ, 1984.

- P.E. Papamichalis, *Practical Approaches to Speech Coding*, Prentice Hall, Englewood Cliffs, NJ, 1987.

- IMA Compatibility Project, *Recommended Practices for Enhancing Digital Audio Compatibility in Multimedia Systems*, V.3.00, Oct. 1992.

- R. Richey, Adaptive Differential Pulse Code Modulation using PIC-16/17 Microcontrollers, AN643, Embedded Control Handbook, Microchip Technology, 1996.

- J.D. Tardelli, E.W. Kreamer, P.A. La Follette, and P.D. Gatewood, A Systematic Investigation of the Mean Opinion Score (MOS) and the Diagnostic Acceptability Measure (DAM) for Use in the Selection of Digital Speech Compression Algorithms, ARCON, www.arcon.com/dsl/sl24a.html.

#### RESOURCES

- Comp.speech FAQ, www.speech. cs.cmu.edu/comp.speech

- Dynastat Inc., Subjective Testing and Evaluation of Voice Communications Systems, www.bga.com/ dynastat/index.html

- T. Robinson, Speech Analysis, Cambridge University Engineering Dept., Speech Vision Robotics Group, www-svr.eng.cam.ac.uk/ ~ajr/SA95/SpeechAnalysis/ SpeechAnalysis.html

- J. Woodard, *Speech Coding*, Dept. of Electronics and Computer Science, University of Southampton, rice.ecs.soton.ac.uk/ speech\_codecs/index.html

#### SOURCES

**PIC12C672**, **'16C556A, '16C774** Microchip Technology, Inc. (480) 786-7200 Fax: (480) 899-9210 www.microchip.com

#### Amplifiers

National Semiconductor (800) 272-9959 (408) 721-5000 Fax: (408) 739-9803 www.national.com

Texas Instruments, Inc. (508) 236-3800 www.ti.com

## FEATURE ARTICLE

Kock Kin Ko

## Electric Vehicle Performance Analyzer

Ko takes us through the design steps of a Hitachi-based device that measures and analyzes electriccar speed, distance, fuel consumption, and travel time. All this information is available to the driver at the touch of a button. henever I dropped in to see the staff in the electric car workshop at the Electrical Engineering Department of Ngee Ann Polytechnic, I left with an urge to get involved. I fancied the vehicle, and the principal lecturer was a good friend.

Although I didn't know much about the hardware stuff, our gurus knew every single electrical part of the vehicle and had even publicized the vehicle hardware a couple years ago in the *Straits Times* of Singapore. The hardware publicity was good, but no one ever wrote any embedded code to optimize the vehicle's performance.

Having driven a Ford Telstar for years, I looked at the bank of batteries packed on the electrical vehicle and had to ask myself if it was really economical to drive

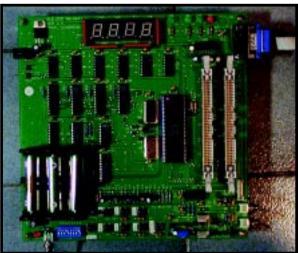

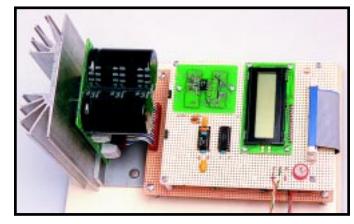

Photo 1—Here's the prototype (courtesy of Hitachi Micro Systems Asia) that I used for software development. CPU H3644 is located at the center, the seven-segment display and LEDs at the top, button keys at the bottom, RS-232 cable at the upper right corner, and DIP switch in the lower left corner. an electric vehicle. How could its performance be optimized?

Before figuring out how to optimize performance, I'd need a system analyzer to monitor or calculate its performance. This was my chance to get involved with the electric car project, and that's how I got started designing the performance analyzer.

The analyzer was developed using a Hitachi microcontroller. Three sets of performance data are collected in real time—fuel consumption (in amp-hours from the car battery) versus speed (in kilometers per hour), distance (in kilometers) versus speed, and time traveled (in hours and minutes, or minutes and seconds) versus speed.

Keys on the analyzer enable the driver to scroll through the recorded performance data. Any driver who starts a new trip can erase the performance data record or let the data accumulate over time and then download it to a PC at the end of the trip.

A graphical display of the performance data is shown on the PC screen. Indirectly, this display helps drivers convert their thinking from miles-pergallon of gasoline to hours-per-amp of battery power. It also helps them estimate how many amp-hours are required to travel to a destination, or the optimum speed with the least amp-hours spent.

In this article, I present the software design of the analyzer and cover both the microcontroller and PC software (both in C). The micro's software was developed with a Hitachi C compiler, and the software for the PC was

developed with CVI (C for Virtual Instrument) from National Instrument.

The Hitachi H8/3644 8-bit micro used in this project is a dream machine for an embedded C programmer like me. It consists of 32-KB flash memory and a 1-KB RAM that's big enough for a C program. Sure, C is big, but I like its readability, portability, and reusability.

The H8/3644 has a number of special functions that I took advantage of. The Timer A interrupt provides realtime ticks in milliseconds. Timer B captures pulses generated from a rolling wheel, and analog channel 1 measures fuel consumption. Five external interrupts are used for sensing five keys, and the on-chip UART is used to download data to PC.

#### SYSTEM DESIGN

The four basic system measurements are real-time ticks in seconds (for measuring time), wheel pulses (for measuring distance), pulses per second (for measuring speed), and milliamps per second (for measuring fuel consumption). The Timer A interrupt schedules these four system measurements.

The real-time clock accumulates travel-time duration from seconds to hours. Distance is calculated by converting the total number of wheel pulses into kilometers. Speed calculation converts pulses per second into kilometers per hour. To calculate fuel consumption, milliamps per second are converted to amps per hour.

These conversions are done only on user request. When requested, the conversion results are displayed on a seven-segment display with four digits.

The raw speed data is accumulated to form statistical records. Speeds are divided into 13 ranges: <20 km/h, 20– 30 km/h, 30–40 km/h, and so on up to >130 km/h. Timer A also schedules these accumulations.

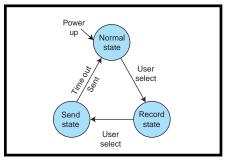

Figure 1—The driver selects one of the three states available with the system. Data records are shown on the seven-segment display in the Record state and are sent to the PC in the Send state.

The driver selects one of the three states available with the system— Record, Send, or Normal. Figure 1 shows the state transition diagram.

In the Record state, drivers can scroll through and view all records. In the Send state, the micro waits for the password to be sent from the PC before dumping the records to the PC. In the Normal state, drivers can view

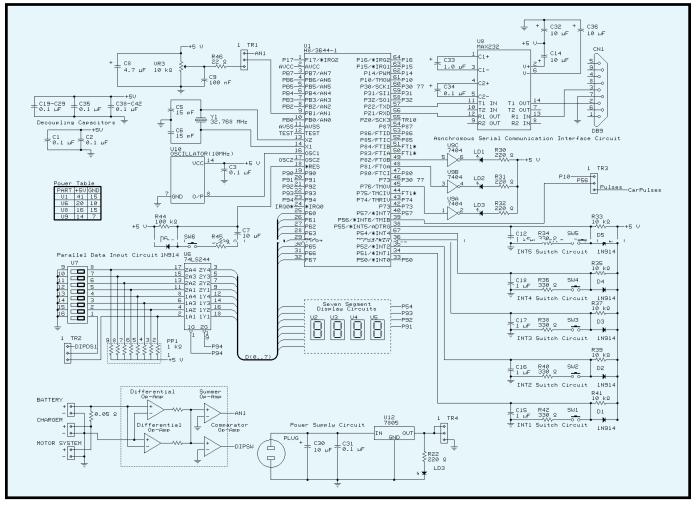

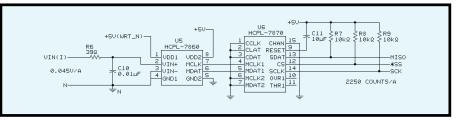

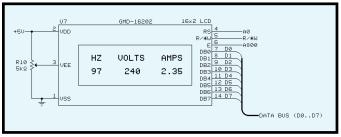

Figure 2—Here's the schematic for the electric vehicle performance analyzer. Shown on the right-hand side of the CPU is the circuitry designed for the RS-232 connection, the LEDs, the car pulse input, and the button keys. The circuitry on the left-hand side includes the analog input, the seven-segment display, and the current measurement.

| S/N | File name  | Purpose                                                                                           | CPU<br>dependent |

|-----|------------|---------------------------------------------------------------------------------------------------|------------------|

| 1   | Adlpfc.c   | Low-pass filter to average 32 samples                                                             | No               |

| 2   | Car. c     | Main program                                                                                      | No               |

| 3   | DispMesg.c | Routines for showing all messages on four-digit display                                           | / No             |

| 4   | Elecpara.c | Gets electrical system configuration and calculates conversion gain factor                        | No               |

| 5   | Fourdigi.c | Algorithm for fitting any four-byte variable onto a<br>four-digit display                         | No               |

| 6   | Hardware.c | All hardware-specific codes including CPU initializa-<br>tion, driver for seven-segment display   | Yes              |

| 7   | INTR.c     | All interrupt routines including Timer A interrupt,<br>ADC interrupt, and INT external interrupts | Yes              |

| 8   | Math.c     | Converts short integer into five BCD digits                                                       | No               |

| 9   | Serial.c   | Routines for serial communication with PC                                                         | Yes              |

| 10  | Statdata.c | Routines for defining and updating statistical records                                            | No               |

| 11  | UserIF.c   | Routines for scrolling through menu for user selection                                            | No               |

Table 1—Listed here are the 11 software modules and their purposes. Modules that are CPU-dependent are also indicated.

current speed, total distance and time traveled, total fuel consumption, and energy left in the battery. Regardless of what state the system is in, data measurement is done in real time.

#### HARDWARE DESIGN

Each of the five keys of the user interface are connected to external interrupt pins (see Figure 2). The five external interrupts for sensing keypress are INT1–INT5. They sense driver selection of data for fuel consumption, distance traveled, speed, time traveled, and system states, respectively.

A four-digit seven-segment display is connected to a data bus (port 6) and a control bus (port 9 pins 1–4). Four 8-bit data latches (74LS273) are used for latching data for the display's four digits. To latch data into the data latch, set the control line high, place the data on the data bus and reset the control line to low.

A differential op-amp measures the current drawn from the battery by the motor system. The differential gain is scaled to provide a 5-V output at maximum system current.

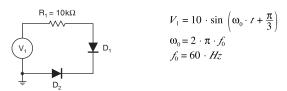

With its input across a  $0.05-\Omega$  resistor, the op-amp output AN1 is connected to analog channel 1. The op-amp circuitry also provides a digital output (DIPSW1) to signal whether current is charging into or discharging from the battery.

An eight-way DIP switch provides the system configuration. The switch is connected to the data and control buses as a parallel input port. Bits 2–3 of the DIP switch indicate four possible maximum system-current loads, and bits 4–5 indicate four possible battery sizes. CPU software reads these 4 bits at powerup to determine the conversion gain factor for calculating system current and a new battery's original energy.

Some hardware aids make software debugging easier. For example, a 5-V

variable source (VR3) is used during software debugging rather than the op-amp voltage output. Through a jumper (TR1), VR3 is connected to analog channel 1.

The DIP switch also provides debugging features. Bit 0 simulates current direction (charging or discharging). To simulate the change in speed during software debugging, bits 6–8 simulate eight possible speeds while Timer A output is jumpered through TR3 to the Timer B input. CPU software reads these bits in every timer tick to determine the number of pulses transmitted at the Timer A output.

Three LEDs (LD1, LD2, and LD4) are used for burn-in testing. Their continuous flashing indicates that the main program, the Timer A interrupt routine, and the ADC interrupt routine are alive.

#### SOFTWARE DESIGN

To maintain modularity and portability, I wrote 11 files. Table 1 lists the purposes of each. On powerup, the

```

Listing 1a—INT() sets INTx menu change to indicate that a specific key was pressed. b—The

main program main() calls the routine user_change_menu to determine user selection op_menu.

a)

#pragma interrupt INT

void INT(void)

{

if(IRR3.BIT.B1)

/*if interrupt flag set?*/

{

IRR3.BIT.B1=0;

/*clear interrupt flag*/

INT1_menu_change = 1;

/*set semaphore*/

new_menu = INT_1;

if(IRR3.BIT.B5)

/*similarly for INT2, INT3, and INT4*/

IRR3.BIT.B5=0;

INT5_menu_change=1;

/*set semaphore*/

new_menu = INT_5;

3

b)

main()

system_engine_start_up_sequence();

do {

user_change_menu();

/*determine op_menu*/

switch (op_menu)

case INT1_MENU_ADC_VOLTAGE:

adc_main();

break:

case INT1_MENU_CURRENT:

current_main();

break;

....

}while(1);

```

main program, car.c, calls routines in hardware.c to initialize the CPU, routines in elecpara.c to determine system hardware parameters, and routines in statdata.c to initialize system variables (e.g., statistical records).

After interrupts are enabled, routines in INTR.c are called to handle the Timer A, ADC, and external interrupts. INTR.c also includes routines for updating the raw data for distance and speed. The lowpass filter routine in Adlpfc.c is called to get the average raw data for fuel consumption.

Besides scheduling data updates, Timer A also schedules when to update statistical records (done by calling routines in statdata.c). After initialization, the main program enters a forever do-loop. First, it calls routines in UserIF.c to determine what menu the user selected. Then, the main program executes routines in car.c to serve the user.

Routines in UserIF.c scroll through all the menus. These routines then call routines in DispMesg.c to dump menu messages on seven segments.

To best serve the user, three things need to be done. Conversion routines in car.c convert raw data into distance, speed, and fuel consumption. The autoscaling algorithm in Fourdigi.c scales large numbers (four-bytes long integer) into two-byte short integer. BCD conversion routines in math.c convert the short integer into five BCD digits.

Finally, the auto-scaling algorithm puts the five BCD digits on a four-digit display with the decimal point automatically shifting across the display to indicate the scale of the data. If the user sends the data to a PC, serial.c handles the serial communication.

#### **USER MENU**

Each key has a menu that consists of a sequence of selection choices. Pressing and holding a key enables the user to scroll through the selection choices.

The INT1 menu offers these options: A (analog voltage from the ADC), Curr (current drawn from the battery by the motor system), AH-d (total amount of amp-hour discharging from battery), AH-C (total amount of amp-hour charging to battery), and Engy (remaining energy stored in the battery).

The INT2 choices are Cout (number of pulses accumulated for 1 km), onE (1 km dial, accumulated distance up to 1 km), and diSt (total distance traveled). The INT3 menu offers CPS (number of pulses per second generated by the rolling wheel) and SPEd (speed in kilometers per hour).

INT4 provides five choices—tinE (time in HH.MM or MM.SS), StAr (to start or continue to accumulate raw data), StoP (temporarily stops accumulating raw data), CLEA (clears all raw data and records), and oFF (off display and stop accumulating raw data). The three system states for the INT5 menu are rECd (enters record state), send (for sending records to the PC), and roFF (to turn the record state off and return to the normal state).

| Listing 2—user_change_menu calls change_IN<br>INTx menu. The latter calls display_INTx_menu                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|

| void display_INT1_menu(void)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |  |  |  |

| <pre>switch (INT1_op_menu) {     case INT1_MENU_ADC_VOLTAGE :</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |  |  |  |

| show_A();<br>break;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /*display A*/                                  |  |  |  |

| <pre>case INT1_MENU_CURRENT :     show_Curr();</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | /*display curr*/                               |  |  |  |

| break;<br>case INT1_MENU_AMP_HR_DISCHARGE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |  |  |  |

| <pre>switch (record_data_display_on){ case RECORD_MODE_ON:     if (INT1_down)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /*Record State on*/<br>/*if key is held down*/ |  |  |  |

| {<br>INT3_speed_index = inc_INT3_speed_<br>amp_hr_discharge_record_on(INT3_sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | index(INT3_speed_index);                       |  |  |  |

| INT1_down = 0;<br>}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |  |  |  |

| else show_AH_d(); /*key is pressed<br>break;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | but not yet held down*/                        |  |  |  |

| <pre>case RECORD_MODE_OFF:     show_AH_d();     break;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /*Normal State*/<br>/*display AH-d*/           |  |  |  |

| }<br>break;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |  |  |  |

| <pre>case INT1_MENU_AMP_HR_CHARGING :     show_AH_C();     break;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | /*display AH-c*/                               |  |  |  |

| <pre>case INT1_MENU_ENERGY:<br/>show_Engy();<br/>break;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /*display Engy*/                               |  |  |  |

| }<br>display(dispdat);<br>}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | /*to display on 7 segments*/                   |  |  |  |

| void change_INT1_menu(void)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |  |  |  |

| {<br>do {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |  |  |  |

| <pre>switch (record_data_display_on ) {     case RECORD_MODE_OFF: /*in Normal State*/     /* if 1st time to switch back to this menu, do not increase     /* INT1_op_menu. So that when switching between keys, user     /* menu preference is kept */     if (new_menu ==old_menu)INT1_op_menu += 1;     else old_menu = new_menu; /*update menu choice*/     if (INT1_op_menu &gt; INT1_MAXMENU) INT1_op_menu = 0;         break;     case RECORD_MODE_ON: /*in Record State*/     INT1_op_menu = INT1_MENU_AMP_HR_DISCHARGE;     break;</pre> |                                                |  |  |  |

| <pre>} INT1_menu_change = 0; display_INT1_menu(); wait_and_see_display(); INT1_down = test_INT1_button_down();</pre>                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                |  |  |  |

| <pre>} while (INT1_down); /*while mode button being held down*/ op_menu = INT1_op_menu;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |  |  |  |

| }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |  |  |  |

In the Record state, the user holds key INT1 to scroll through records of fuel consumption for different speed ranges. Key INT2 gives records of distance versus speed, and key INT3 scrolls through different speed ranges. Pressing key INT4 shows the user records of time traveled versus speed.

#### DETECTING USER SELECTION

The external interrupt routine INT() sets semaphore INTx\_menu\_ change to indicate that a specific key was pressed (see Listing 1a). The main program main() calls routine user\_ change\_menu() to determine the user selection op\_menu (see Listing 1b).

When a key is held, user\_change\_ menu() calls change\_INTx\_menu() to scroll through the choices of INTx menu (which then calls display\_ INTx\_menu() to show the menu choices) (see Listing 2).

op\_menu is set to a numerical value when the user releases the key. According to op\_menu value xyz, main() executes xyz\_main() as shown in Listing 1b.

Notice three things in Listing 2. First, in routine change\_INT1\_menu(), new\_menu and old\_menu are used to keep the user preferences by not increasing the INTx\_op\_menu value when the user switches back to an old key. This way, when switching between keys, the driver can keep his preference choice for each key.

Second, display\_INT1\_menu() puts up a display depending on the state the system in. In the Normal state, AH-d (for fuel consumption) is shown on seven segments. If the system is in Record state, the user can scroll through the records of fuel consumption versus speed by holding the INT1 key down. amp\_hr\_discharge\_record\_on (INT3\_speed\_index) is called to show the fuel-consumption records.

Note that INT3\_speed\_index increases as the user holds down the INT1 key to look at the fuel-consumption records. Should the user switch to INT2, the record of distance traveled at the latest speed index set before the key was switched is displayed. That's how the four keys (INT1-INT4) coordinate to show recorded data with respect to the same speed range.

#### **REAL-TIME SCHEDULER**

The Timer A interrupt schedules all events. Two main events are scheduled to take place at different time slots. Updating statistical records is done at real time "quad\_sec" = HALF\_SEC and updating the raw data is done at "quad\_sec" = ONE\_SEC, as shown in Listing 3.

Scheduled in real time, for every 31.25 ms, one ADC sample is saved in ring buffer adc\_buf\_ch0[32] by the ADC() routine in Listing 4a. At real time "quad\_sec" = ONE\_SEC, a low-pass filter routine is called to get the average of 32 ADC samples. This is done by adc\_average = lpf(adc\_buf\_ ch0);. This value is added into raw data milli\_amp\_sec (see Listing 3). Timer B counts the pulses generated from the rolling wheel. At real time "quad\_sec" = ONE\_SEC, update\_ 1sec\_TMB\_counts()reads the counts in Timer B and calculates the counts in 1 s (inc\_count). The routine also accumulates inc\_count into sum\_inc\_ count. When sum\_inc\_count exceeds COUNT\_PER\_1KM, total\_distance increases by 1 km (see Listing 4b).

At "quad\_sec" = ONE\_SEC, update\_time() updates the time traveled from seconds into minutes and from minutes into hours. At "quad\_sec" = HALF\_SEC, the function update\_statistics() is called to update statistical records. Raw data versus speed is calculated into a data structure called struct statistic\_

**Listing 4a**—*ADC()* stores an analog sample in a ring buffer. **b**—Updating wheel pulses per second is done by  $update\_1sec\_TMB\_counts()$ . **c**—Record format is defined by the data structure  $statistic\_form$ . **d**—Statistics are updated with respect to speed index in  $update\_statistic()$ .

| a) | #pragma interrupt ADC<br>void ADC(void)                                                                                                                                                                                                            |                                                                                                                     |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

|    | <pre>{     IRR2.BIT.B6=0;     adc_cur_result=ADRR.BYTE;     bptr++ = adc_cur_result;     if (bptr == (unsigned char )tail) {         bptr = (unsigned char *)head;         first_round_adc = 1;     } }</pre>                                      | /* clear Interrupt hardware flag*/<br>/*read ADC result*/<br>/*put inside ring buffer*/<br>/*pointer wraps around*/ |  |  |  |

|    |                                                                                                                                                                                                                                                    | *toggle LED2 to indicate ADC alive*/                                                                                |  |  |  |

| b) | <pre>void update_1sec_TMB_counts(void) {</pre>                                                                                                                                                                                                     |                                                                                                                     |  |  |  |

|    | <pre>new_count = TCB1.BYTE;<br/>inc_count = new_count - old_count;<br/>/*get difference for counts per sec<br/>old count = new count;</pre>                                                                                                        | /*read Timer B*/<br>cond*/                                                                                          |  |  |  |

|    | <pre>sum_inc_count += inc_count; if (sum_inc_count &gt; COUNT_PER_1KM)</pre>                                                                                                                                                                       | /*add into 1-km count*/<br>/*check if more than 1 km*/                                                              |  |  |  |

|    | <pre>sum_inc_count -= COUNT_PER_1KM;<br/>tota1_distance++;<br/>}<br/>}</pre>                                                                                                                                                                       | /*total distance in kilometers*/                                                                                    |  |  |  |

| c) | <pre>struct statistic_form {     char elapse_time[3];     unsigned long int milli_amp_sec;     unsigned int total_distance;     unsigned int sum_inc_count;</pre>                                                                                  |                                                                                                                     |  |  |  |